Automatic Linearity IP 3 Test with Builtin Pattern

Automatic Linearity (IP 3) Test with Built-in Pattern Generator and Analyzer Foster Dai, Charles Stroud, Dayu Yang Dept. of Electrical and Computer Engineering Auburn University Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 1

Purpose • Develop Built-In Self-Test (BIST) approach using direct digital synthesizer (DDS) for functionality testing of analog circuitry in mixed-signal systems • Provides BIST-based measurement of – Amplifier linearity (IP 3) – Gain and frequency response • Implemented in hardware – IP 3, gain, and freq. response measured Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 2

Outline • Overview of direct digital synthesizer (DDS) • 3 rd order inter-modulation product (IP 3) • BIST architecture – Test pattern generator – Output response analyzer • Experimental results – Implementation in hardware – IP 3 Measurements Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 3

Linear vs. Nonlinear Systems • A system is linear if for any inputs x (t) and x (t), x 1(t) y 2(t), x 2(t) y 2(t) and for all values of constants a and b, it satisfies 1 2 a x 1(t)+bx 2(t) ay 1(t)+by 2(t) • A system is nonlinear if it does not satisfy the superposition law. Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 4

Time Invariant vs. Time Variant Systems e invariant if a time shift in input results in the same time shif shi en x(t-t) y(t-t), for all value of t hen variant if it does not satisfy the condition. Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 5

Memoryless Systems • A system is memoryless if its output does not depend on the past value of its input. • For a memoryless linear system, y(t) = αx(t) whereα is a function of time if the system is time variant. • For a memoryless nonlinear system, y(t) = α + α x(t) + α x²(t)+ α x³(t) + ······ where aj are in general function of time if the system is time variant. 0 Oct. 7, 04 1 2 3 ELEC 5970 -003/6970 -003 (Guest Lecture) 6

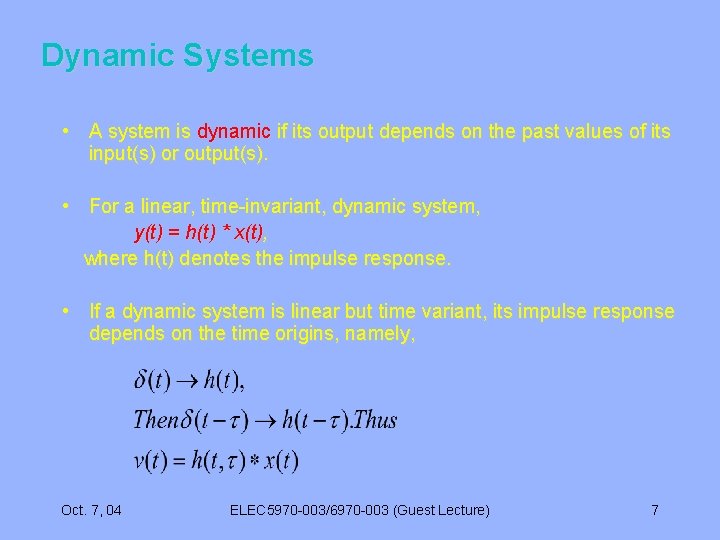

Dynamic Systems • A system is dynamic if its output depends on the past values of its input(s) or output(s). • For a linear, time-invariant, dynamic system, y(t) = h(t) * x(t), where h(t) denotes the impulse response. • If a dynamic system is linear but time variant, its impulse response depends on the time origins, namely, Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 7

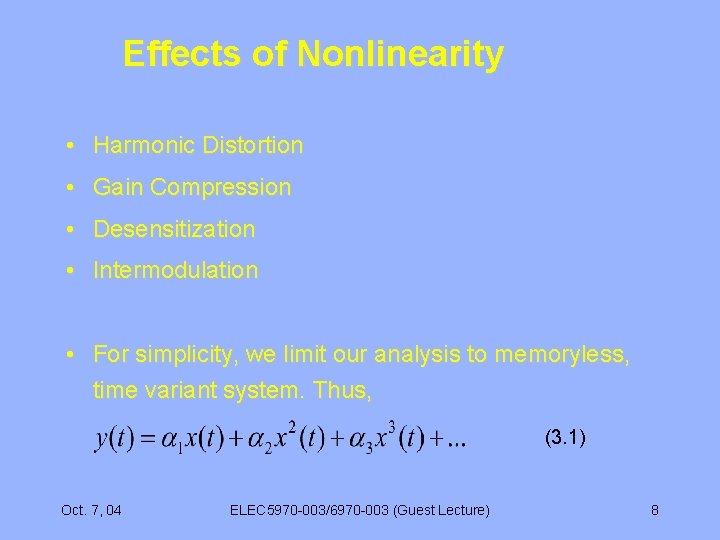

Effects of Nonlinearity • Harmonic Distortion • Gain Compression • Desensitization • Intermodulation • For simplicity, we limit our analysis to memoryless, time variant system. Thus, (3. 1) Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 8

Effects of Nonlinearity -- Harmonics If a single tone signal is applied to a nonlinear system, the output generally exhibits fundamental and harmonic frequencies with respect to the input frequency. In Eq. (3. 1), if x(t) = Acosωt, then Observations: 1. even order harmonics result from αj with even j and vanish if the system has odd symmetry, i. e. , differential circuits. 2. For large A, the nth harmonic grows approximately in proportion to An. Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 9

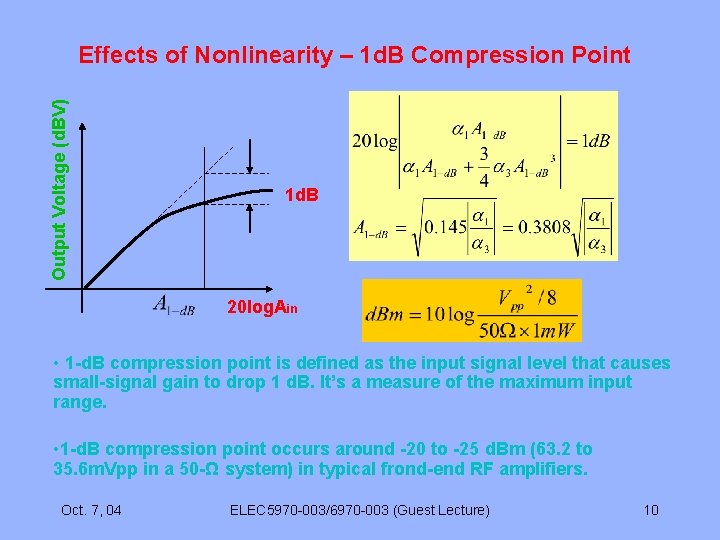

Output Voltage (d. BV) Effects of Nonlinearity – 1 d. B Compression Point 1 d. B 20 log. Ain • 1 -d. B compression point is defined as the input signal level that causes small-signal gain to drop 1 d. B. It’s a measure of the maximum input range. • 1 -d. B compression point occurs around -20 to -25 d. Bm (63. 2 to 35. 6 m. Vpp in a 50 -Ω system) in typical frond-end RF amplifiers. Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 10

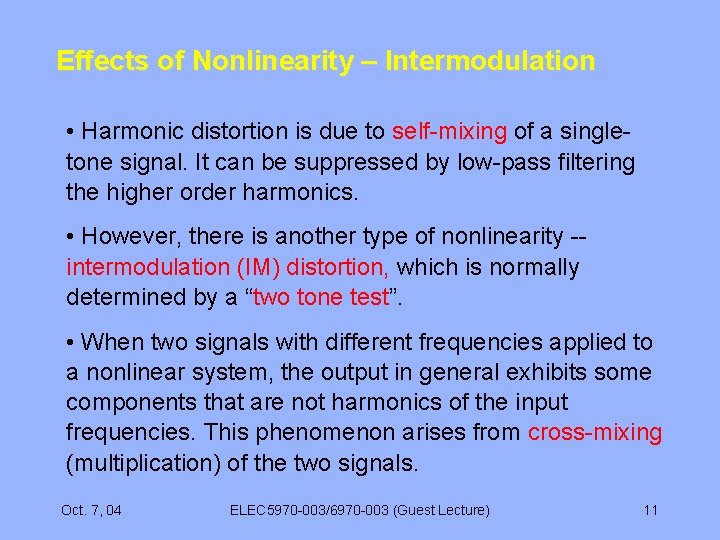

Effects of Nonlinearity – Intermodulation • Harmonic distortion is due to self-mixing of a singletone signal. It can be suppressed by low-pass filtering the higher order harmonics. • However, there is another type of nonlinearity -intermodulation (IM) distortion, which is normally determined by a “two tone test”. • When two signals with different frequencies applied to a nonlinear system, the output in general exhibits some components that are not harmonics of the input frequencies. This phenomenon arises from cross-mixing (multiplication) of the two signals. Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 11

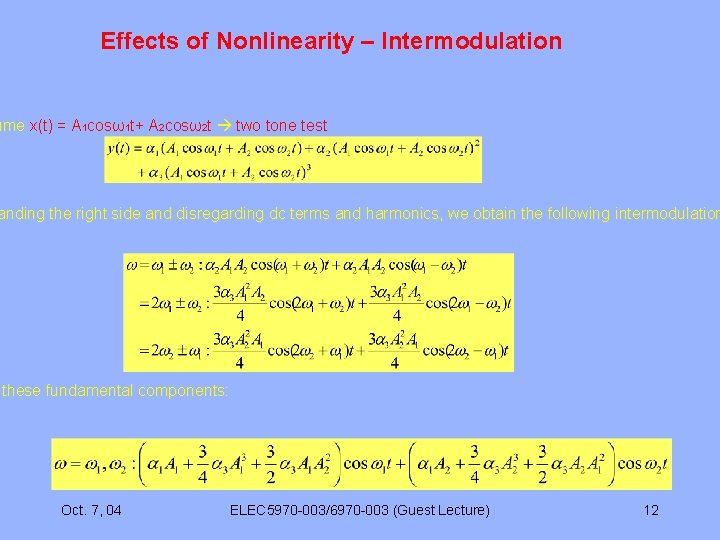

Effects of Nonlinearity – Intermodulation ume x(t) = A 1 cosω1 t+ A 2 cosω2 t two tone test anding the right side and disregarding dc terms and harmonics, we obtain the following intermodulation these fundamental components: Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 12

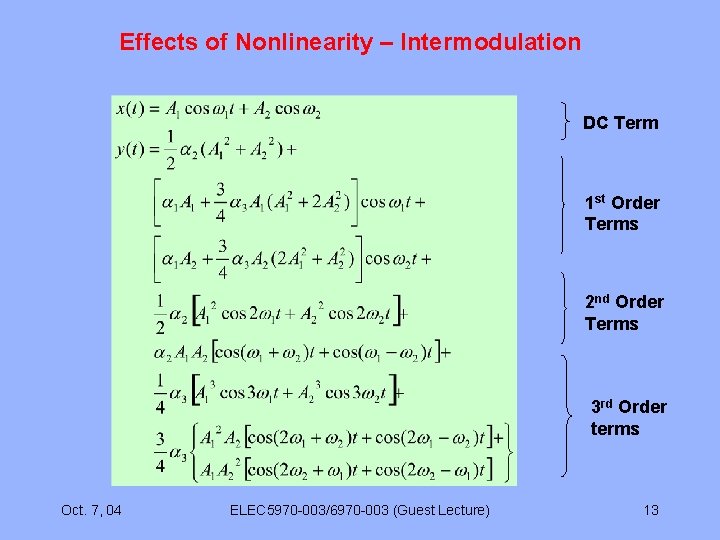

Effects of Nonlinearity – Intermodulation DC Term 1 st Order Terms 2 nd Order Terms 3 rd Order terms Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 13

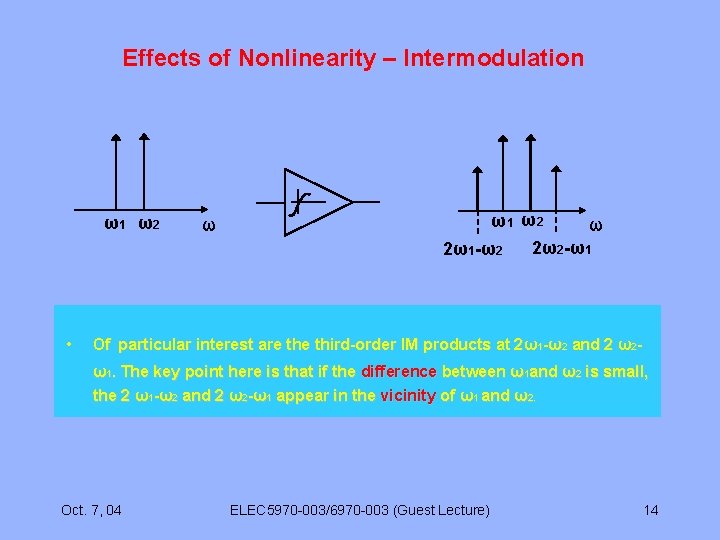

Effects of Nonlinearity – Intermodulation ω1 ω2 ω 2ω1 -ω2 • ω 2ω2 -ω1 Of particular interest are third-order IM products at 2ω1 -ω2 and 2 ω2ω1. The key point here is that if the difference between ω1 and ω2 is small, the 2 ω1 -ω2 and 2 ω2 -ω1 appear in the vicinity of ω1 and ω2. Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 14

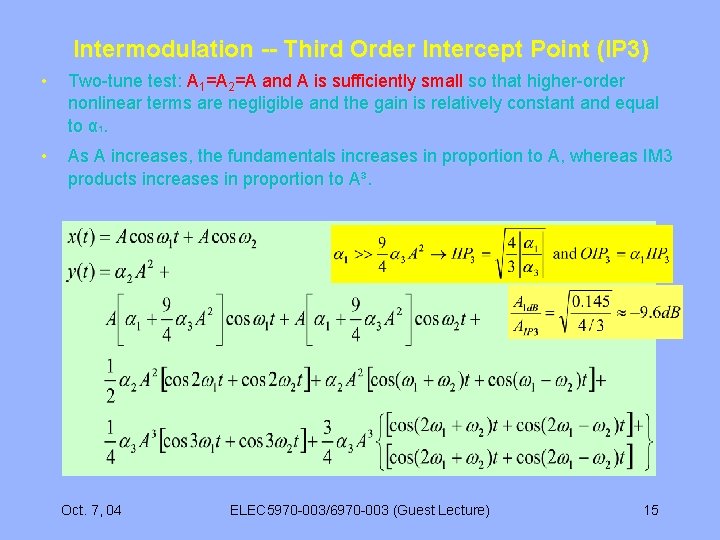

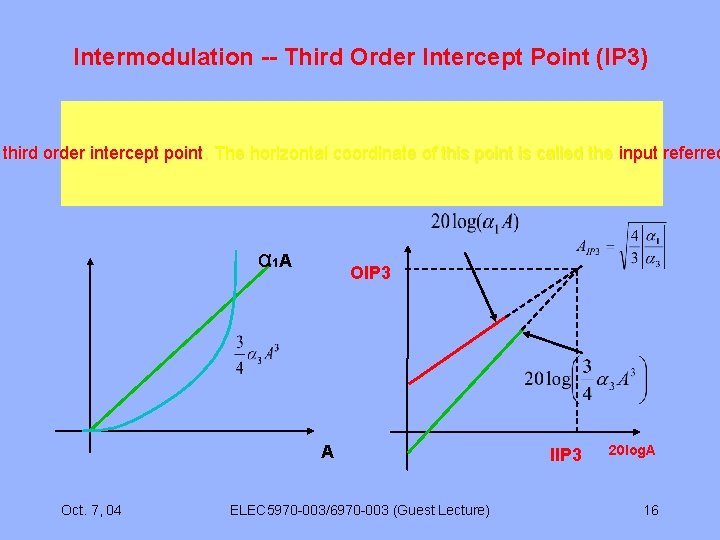

Intermodulation -- Third Order Intercept Point (IP 3) • Two-tune test: A 1=A 2=A and A is sufficiently small so that higher-order nonlinear terms are negligible and the gain is relatively constant and equal to α 1. • As A increases, the fundamentals increases in proportion to A, whereas IM 3 products increases in proportion to A³. Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 15

Intermodulation -- Third Order Intercept Point (IP 3) third order intercept point. The horizontal coordinate of this point is called the input referred α 1 A OIP 3 A Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) IIP 3 20 log. A 16

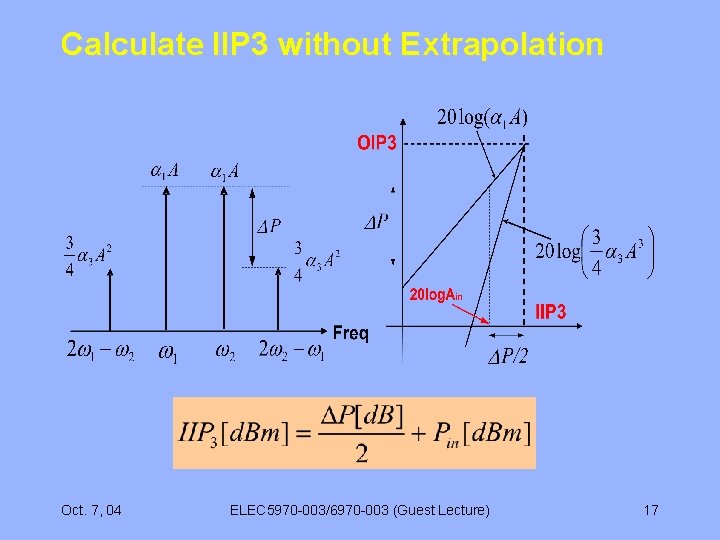

Calculate IIP 3 without Extrapolation Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 17

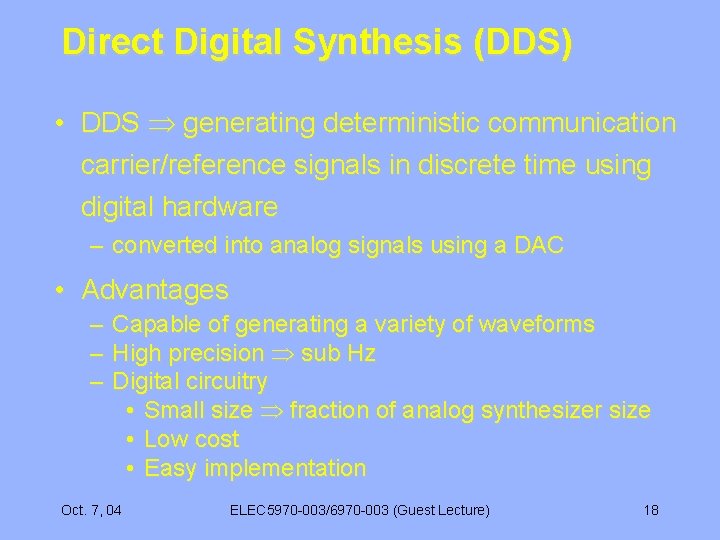

Direct Digital Synthesis (DDS) • DDS generating deterministic communication carrier/reference signals in discrete time using digital hardware – converted into analog signals using a DAC • Advantages – – – Capable of generating a variety of waveforms High precision sub Hz Digital circuitry • Small size fraction of analog synthesizer size • Low cost • Easy implementation Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 18

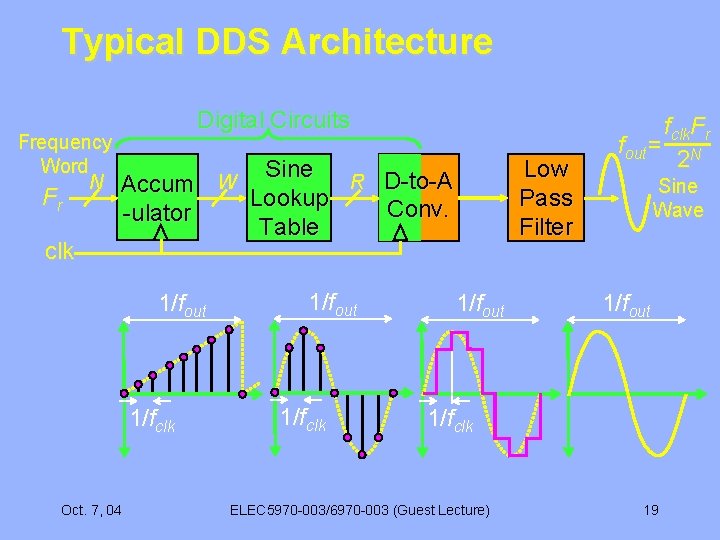

Typical DDS Architecture Frequency Word N Fr clk Digital Circuits Sine R D-to-A Accum W Lookup Conv. -ulator Table 1/fout 1/fclk Oct. 7, 04 1/fout 1/fclk Low Pass Filter 1/fout fclk. Fr fout= N 2 Sine Wave 1/fout 1/fclk ELEC 5970 -003/6970 -003 (Guest Lecture) 19

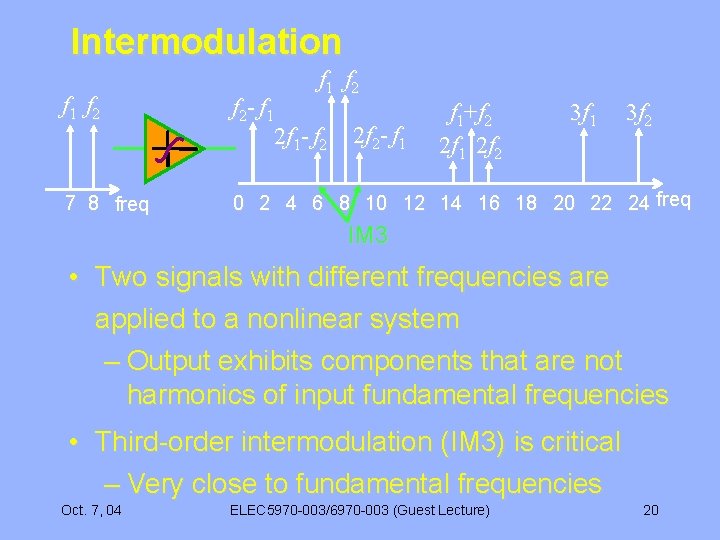

Intermodulation f 1 f 2 f 2 - f 1 2 f 1 - f 2 7 8 freq 0 2 4 6 8 10 12 14 16 18 20 22 24 freq 2 f 2 - f 1+f 2 2 f 1 2 f 2 3 f 1 3 f 2 IM 3 • Two signals with different frequencies are applied to a nonlinear system – Output exhibits components that are not harmonics of input fundamental frequencies • Third-order intermodulation (IM 3) is critical – Very close to fundamental frequencies Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 20

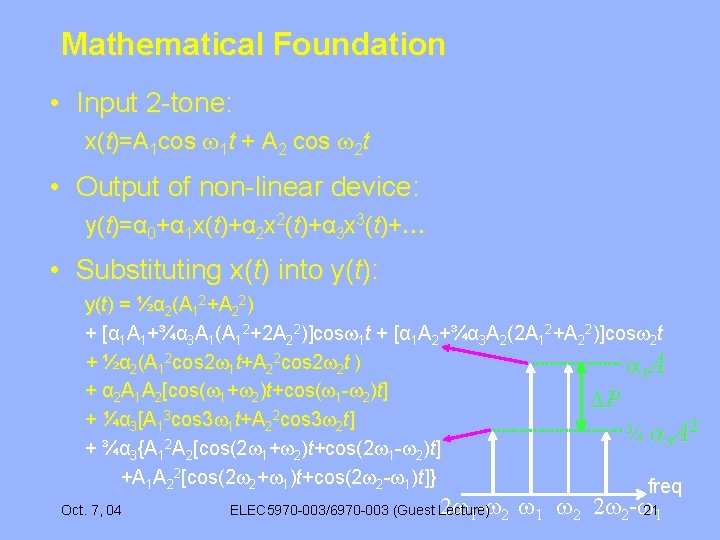

Mathematical Foundation • Input 2 -tone: x(t)=A 1 cos 1 t + A 2 cos 2 t • Output of non-linear device: y(t)=α 0+α 1 x(t)+α 2 x 2(t)+α 3 x 3(t)+ • Substituting x(t) into y(t): y(t) = ½α 2(A 12+A 22) + [α 1 A 1+¾α 3 A 1(A 12+2 A 22)]cos 1 t + [α 1 A 2+¾α 3 A 2(2 A 12+A 22)]cos 2 t + ½α 2(A 12 cos 2 1 t+A 22 cos 2 2 t ) 1 A + α 2 A 1 A 2[cos( 1+ 2)t+cos( 1 - 2)t] P + ¼α 3[A 13 cos 3 1 t+A 22 cos 3 2 t] 2 ¾ A 3 + ¾α 3{A 12 A 2[cos(2 1+ 2)t+cos(2 1 - 2)t] +A 1 A 22[cos(2 2+ 1)t+cos(2 2 - 1)t]} freq Oct. 7, 04 2 - 1 2 2 2 - 211 ELEC 5970 -003/6970 -003 (Guest Lecture) 1 2

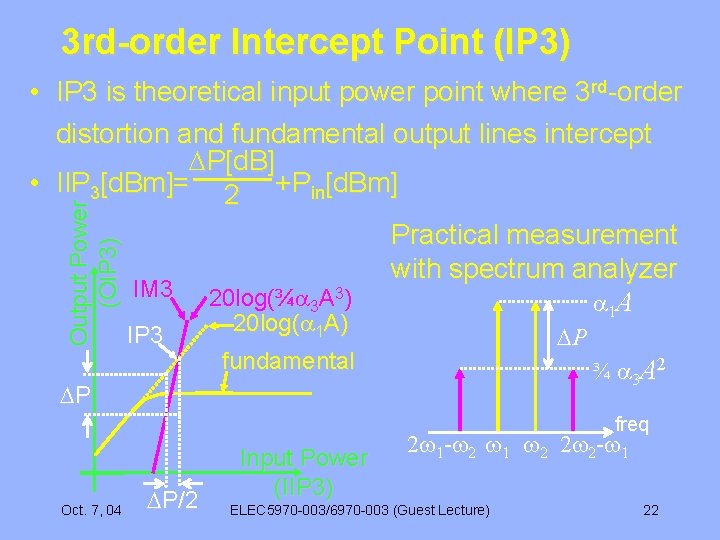

3 rd-order Intercept Point (IP 3) Output Power (OIP 3) • IP 3 is theoretical input power point where 3 rd-order distortion and fundamental output lines intercept P[d. B] • IIP 3[d. Bm]= 2 +Pin[d. Bm] Practical measurement with spectrum analyzer IM 3 20 log(¾ A 3) 1 A 3 IP 3 20 log( 1 A) P fundamental ¾ 3 A 2 P freq Oct. 7, 04 P/2 Input Power (IIP 3) 2 1 - 2 1 2 2 2 - 1 ELEC 5970 -003/6970 -003 (Guest Lecture) 22

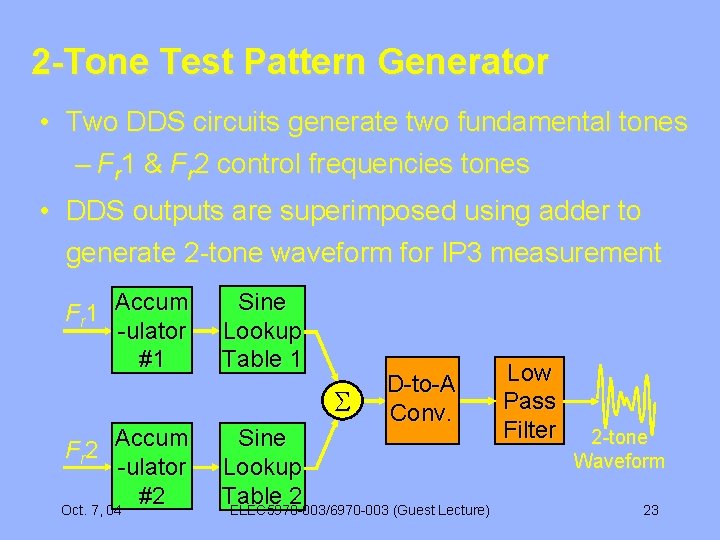

2 -Tone Test Pattern Generator • Two DDS circuits generate two fundamental tones – Fr 1 & Fr 2 control frequencies tones • DDS outputs are superimposed using adder to generate 2 -tone waveform for IP 3 measurement Fr 1 Accum -ulator #1 Sine Lookup Table 1 Fr 2 Accum -ulator #2 Oct. 7, 04 D-to-A Conv. Sine Lookup Table 2 ELEC 5970 -003/6970 -003 (Guest Lecture) Low Pass Filter 2 -tone Waveform 23

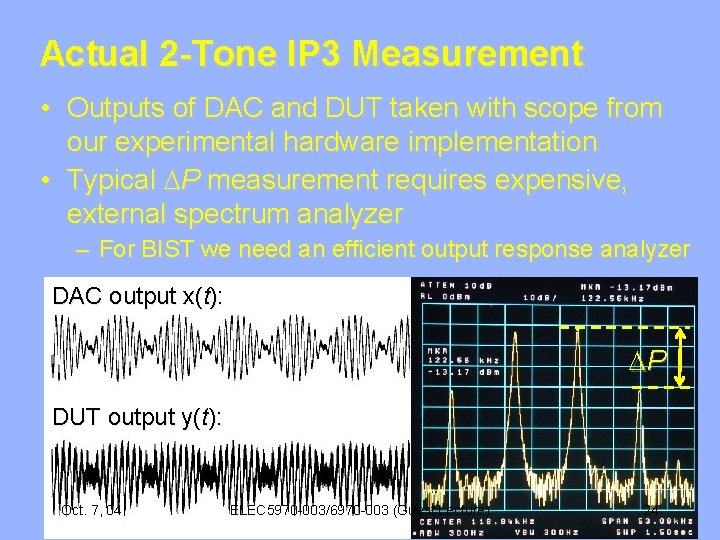

Actual 2 -Tone IP 3 Measurement • Outputs of DAC and DUT taken with scope from our experimental hardware implementation • Typical P measurement requires expensive, external spectrum analyzer – For BIST we need an efficient output response analyzer DAC output x(t): P DUT output y(t): Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 24

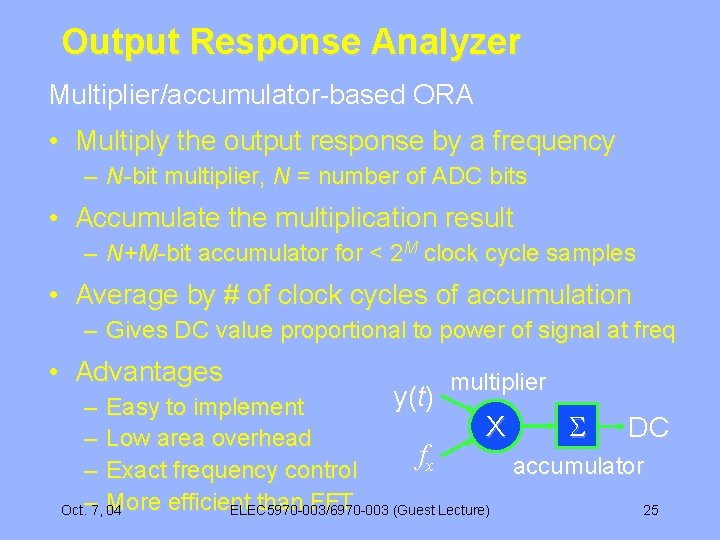

Output Response Analyzer Multiplier/accumulator-based ORA • Multiply the output response by a frequency – N-bit multiplier, N = number of ADC bits • Accumulate the multiplication result – N+M-bit accumulator for < 2 M clock cycle samples • Average by # of clock cycles of accumulation – Gives DC value proportional to power of signal at freq • Advantages multiplier y(t) – Easy to implement X DC – Low area overhead fx accumulator – Exact frequency control efficient than FFT Oct. – 7, More 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 25

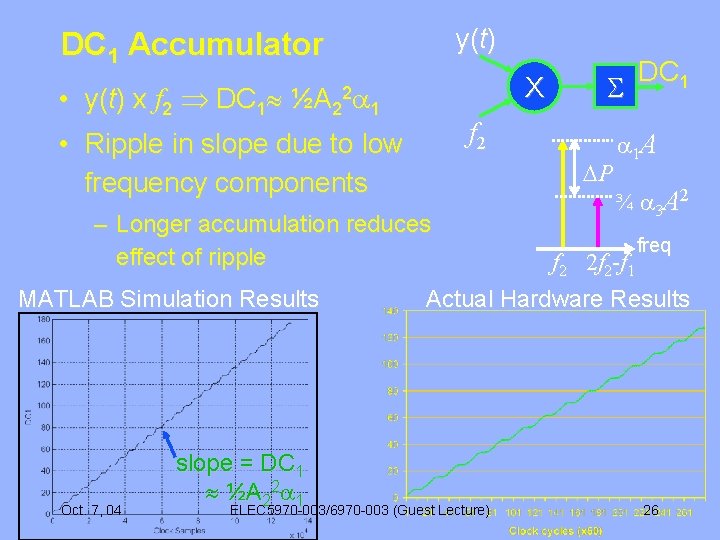

y(t) DC 1 Accumulator X • y(t) x f 2 DC 1 ½A 22 1 f 2 • Ripple in slope due to low frequency components P – Longer accumulation reduces effect of ripple MATLAB Simulation Results Oct. 7, 04 slope = DC 1 ½A 22 1 DC 1 1 A ¾ 3 A 2 f 2 2 f 2 -f 1 freq Actual Hardware Results ELEC 5970 -003/6970 -003 (Guest Lecture) 26

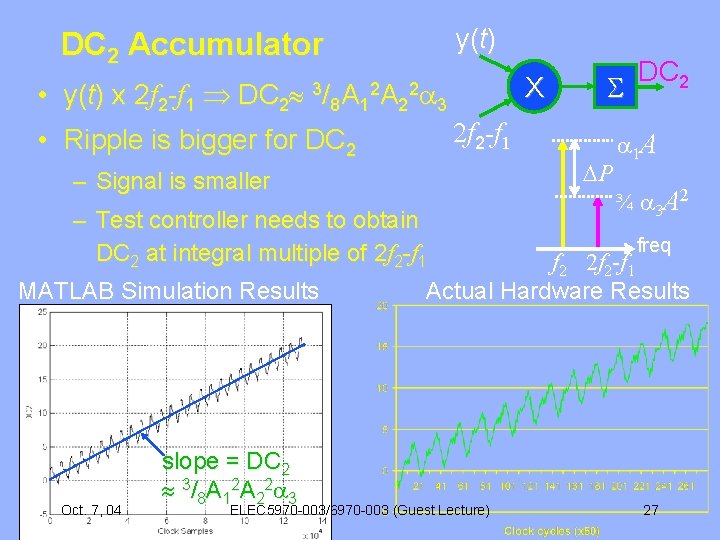

y(t) DC 2 Accumulator • y(t) x 2 f 2 -f 1 DC 2 X 3/ A 2 A 2 8 1 2 3 2 f 2 -f 1 • Ripple is bigger for DC 2 P – Signal is smaller – Test controller needs to obtain DC 2 at integral multiple of 2 f 2 -f 1 MATLAB Simulation Results Oct. 7, 04 slope = DC 2 3/ 8 A 12 A 22 3 DC 2 1 A ¾ 3 A 2 freq f 2 2 f 2 -f 1 Actual Hardware Results ELEC 5970 -003/6970 -003 (Guest Lecture) 27

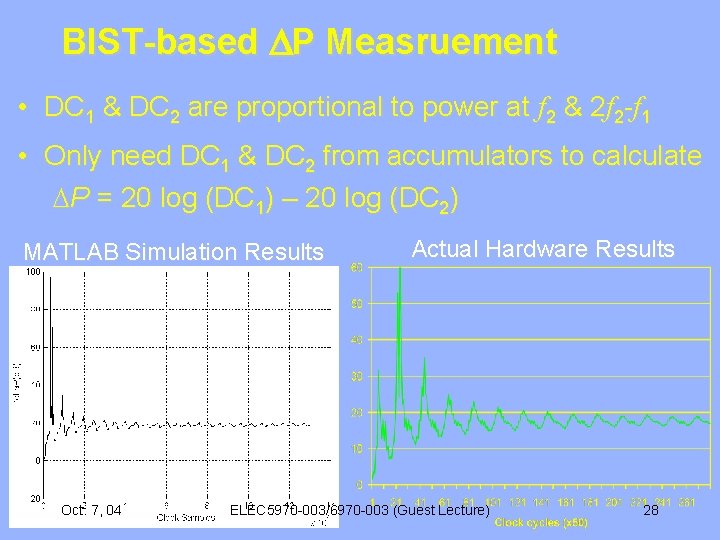

BIST-based P Measruement • DC 1 & DC 2 are proportional to power at f 2 & 2 f 2 -f 1 • Only need DC 1 & DC 2 from accumulators to calculate P = 20 log (DC 1) – 20 log (DC 2) MATLAB Simulation Results Oct. 7, 04 Actual Hardware Results ELEC 5970 -003/6970 -003 (Guest Lecture) 28

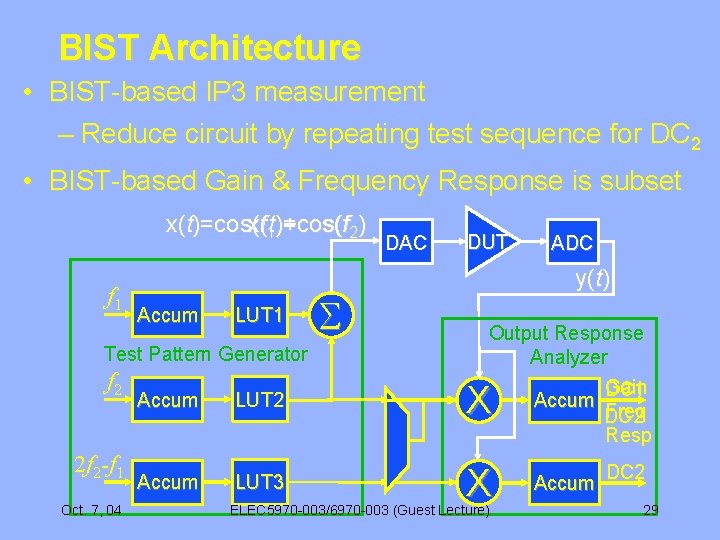

BIST Architecture • BIST-based IP 3 measurement – Reduce circuit by repeating test sequence for DC 2 • BIST-based Gain & Frequency Response is subset x(t)=cos(x(f 1 t)=cos( )+cos(f 2) f 1 Accum LUT 1 Test Pattern Generator f 2 2 f 2 -f 1 Oct. 7, 04 DAC DUT ADC y(t) Output Response Analyzer Gain DC 1 Accum Freq DC 2 Resp Accum LUT 2 X Accum LUT 3 X ELEC 5970 -003/6970 -003 (Guest Lecture) Accum DC 2 29

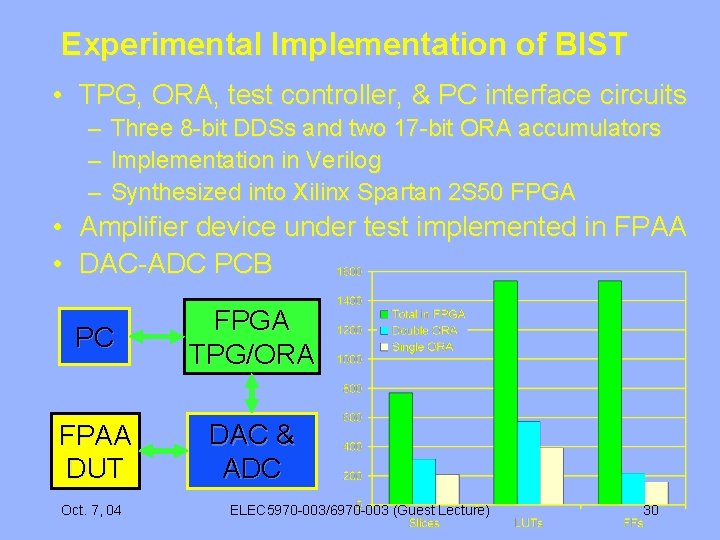

Experimental Implementation of BIST • TPG, ORA, test controller, & PC interface circuits – – – Three 8 -bit DDSs and two 17 -bit ORA accumulators Implementation in Verilog Synthesized into Xilinx Spartan 2 S 50 FPGA • Amplifier device under test implemented in FPAA • DAC-ADC PCB PC FPGA TPG/ORA FPAA DUT DAC & ADC Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 30

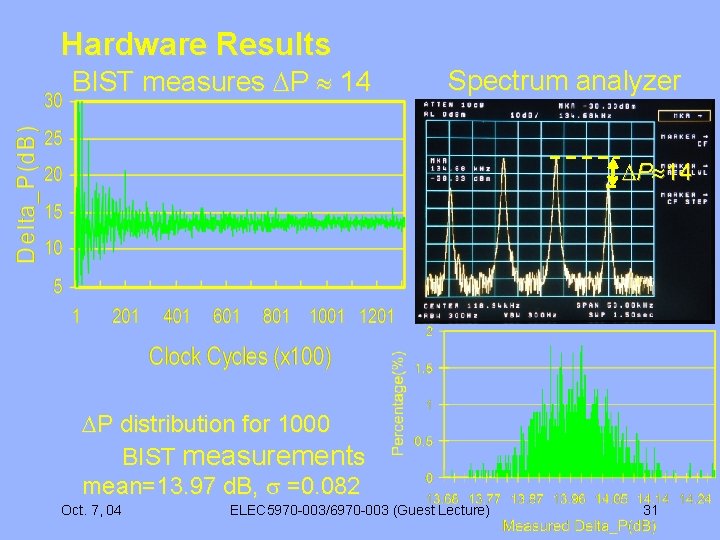

Hardware Results BIST measures P 14 Spectrum analyzer P 14 P distribution for 1000 BIST measurements mean=13. 97 d. B, =0. 082 Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 31

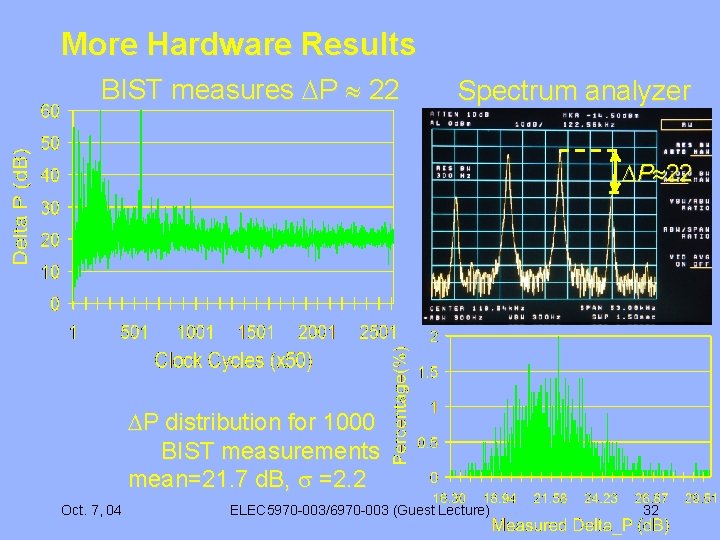

More Hardware Results BIST measures P 22 Spectrum analyzer P 22 P distribution for 1000 BIST measurements mean=21. 7 d. B, =2. 2 Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 32

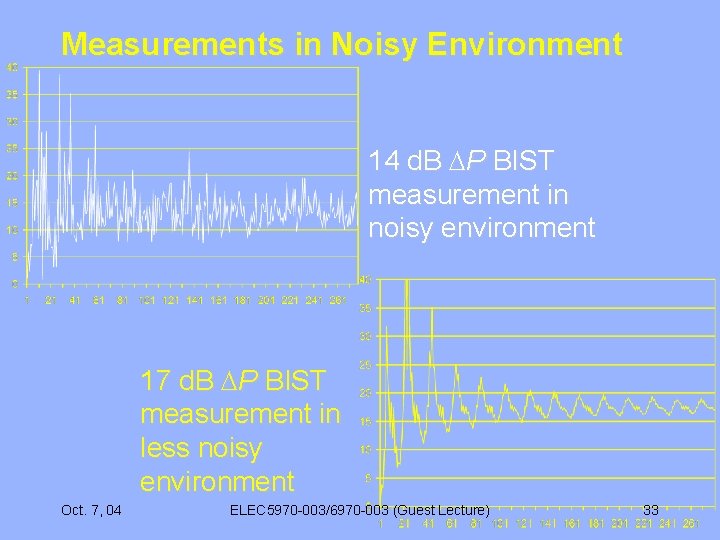

Measurements in Noisy Environment 14 d. B P BIST measurement in noisy environment 17 d. B P BIST measurement in less noisy environment Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 33

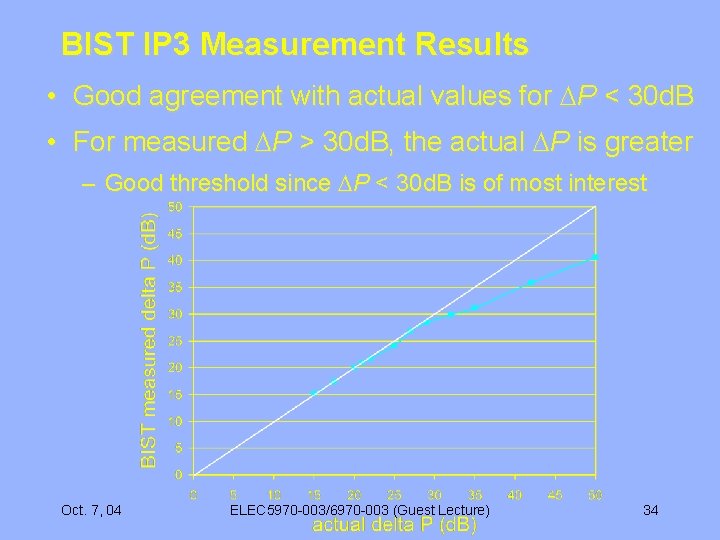

BIST IP 3 Measurement Results • Good agreement with actual values for P < 30 d. B • For measured P > 30 d. B, the actual P is greater – Good threshold since P < 30 d. B is of most interest Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 34

Conclusion • BIST-based approach for analog circuit functional testing – DDS-based TPG – Multiplier/accumulator-based ORA • Good for manufacturing or in-system circuit characterization and on-chip compensation – Amplifier linearity (IP 3) – Gain and frequency response • Measurements with hardware implementation – Accurately measures IP 3 < 30 d. B – Measurements of IP 3 > 30 d. B imply higher values Oct. 7, 04 ELEC 5970 -003/6970 -003 (Guest Lecture) 35

- Slides: 35