Automated Logic Minimizer For Electronic Digital Circuit Using

- Slides: 19

Automated Logic Minimizer For Electronic Digital Circuit Using Logic Programming Mariza Wijayanti 11407050

Table of Contents Introduction Design of kmap minimizer Result and Discussion

Introduction Background. The function of the hardware and software computer device are currently expanding. The facilities provided in a computer device are designed to assist people in complete the work that cannot be done by human hands, or just facilitate. The karnaugh map is a table that serves to simplify the digital circuits. Based on the core of the problem above the authors design program kmap to simplify the digital circuit with short time Problem Statement. How to make the program karnaugh map with few variables to simplify the digital circuits in a short time. Scope of The Research. System program karnaugh map with 2, 3, and 4 variables using the language Programming Logic. Objective of The Research. Know more in about the use of software Swi-Prolog 5. 10. The produced program can be used as a means to support jobs for people working in the fields of digital circuit either directly or indirectly.

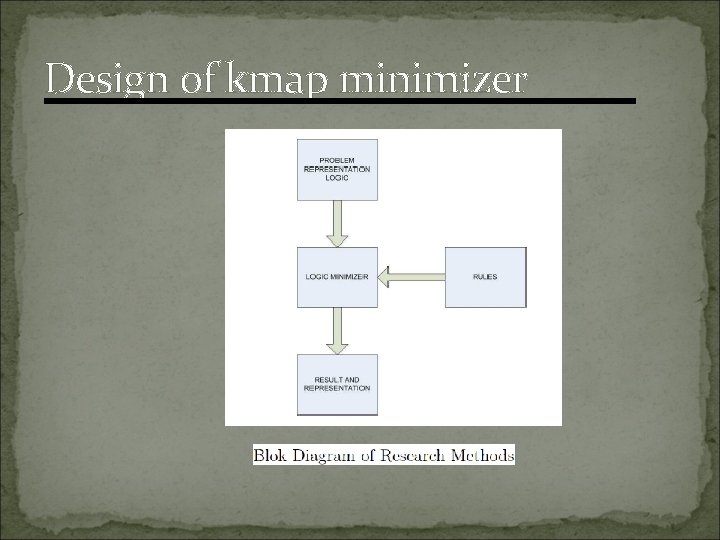

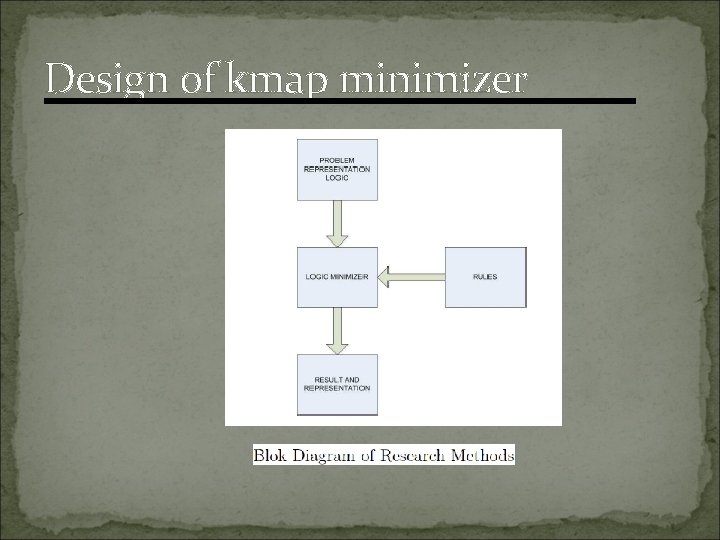

Design of kmap minimizer

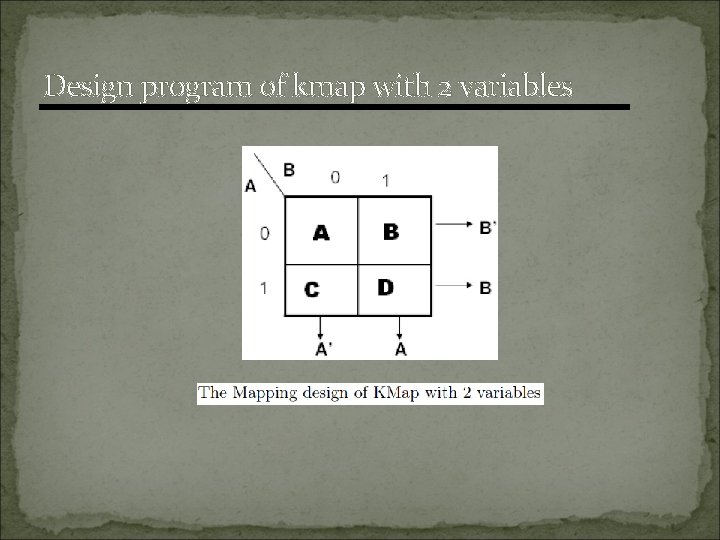

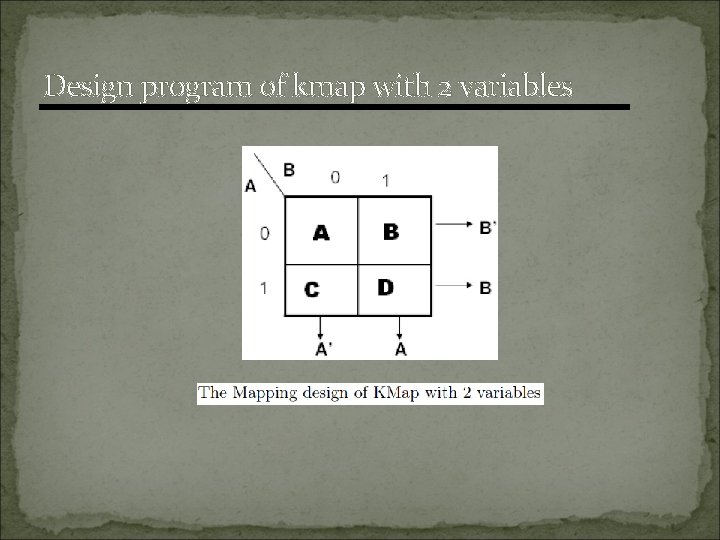

Design program of kmap with 2 variables

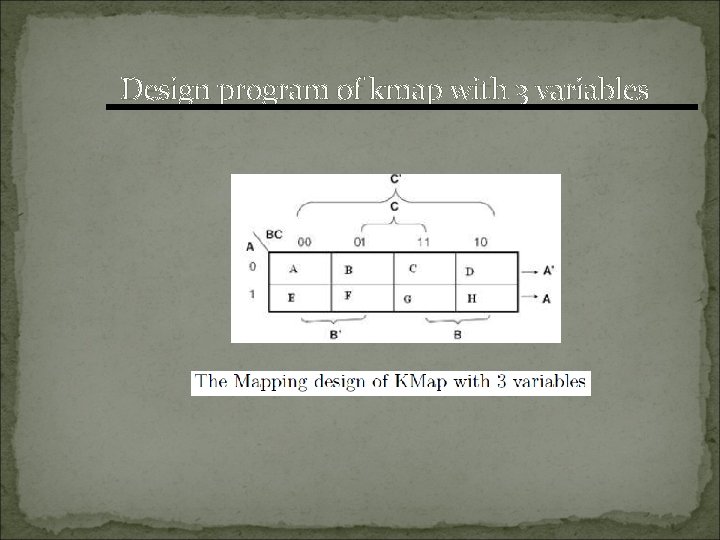

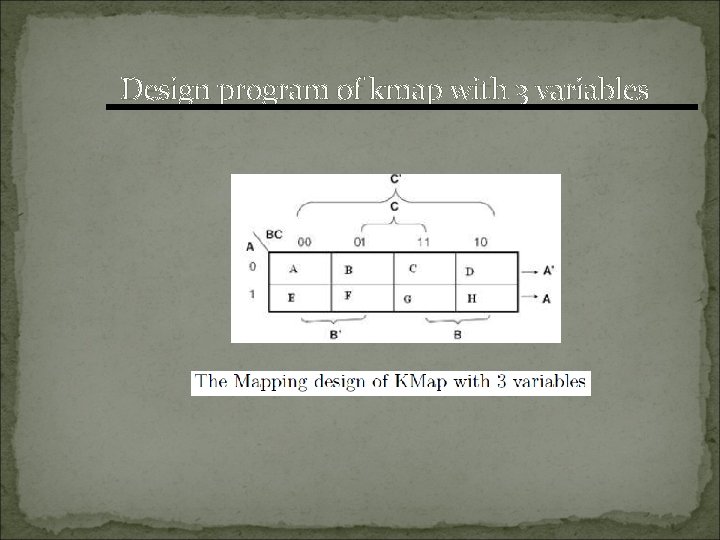

Design program of kmap with 3 variables

Design program of kmap with 4 variables

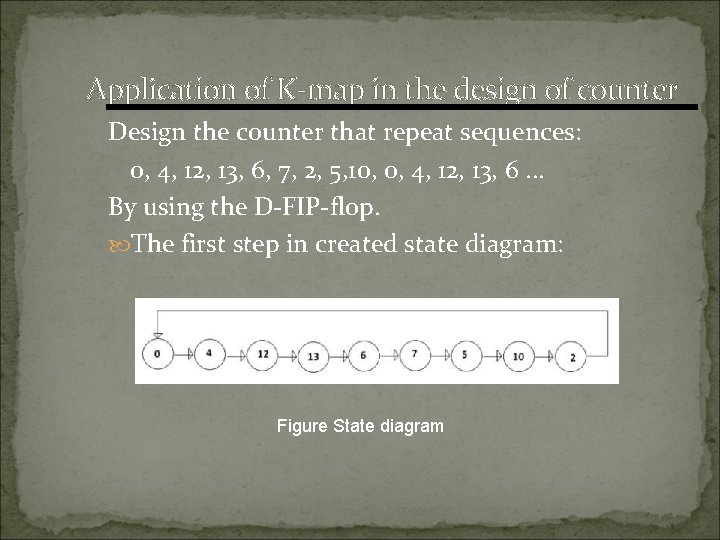

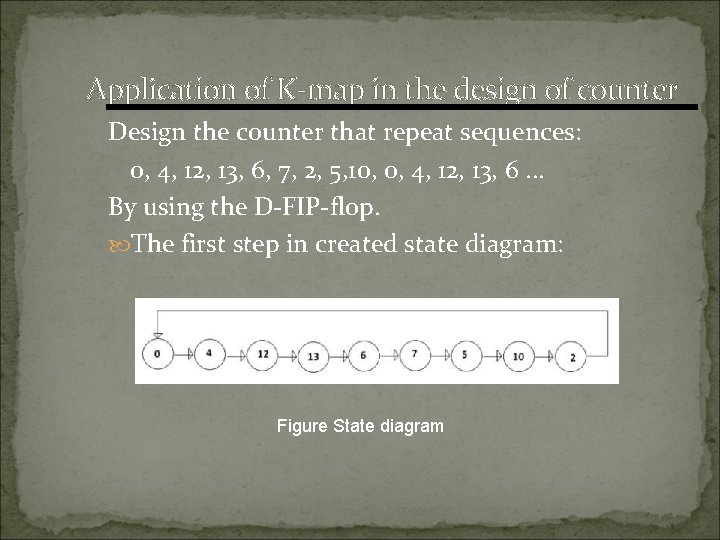

Application of K-map in the design of counter Design the counter that repeat sequences: 0, 4, 12, 13, 6, 7, 2, 5, 10, 0, 4, 12, 13, 6. . . By using the D-FIP-flop. The first step in created state diagram: Figure State diagram

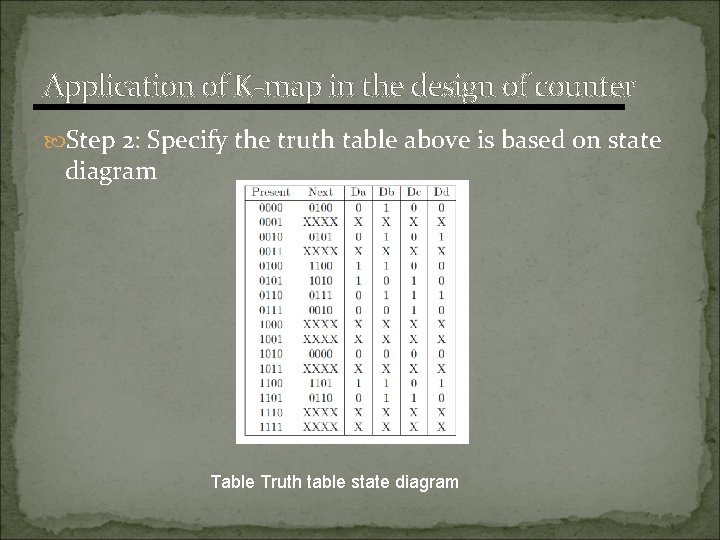

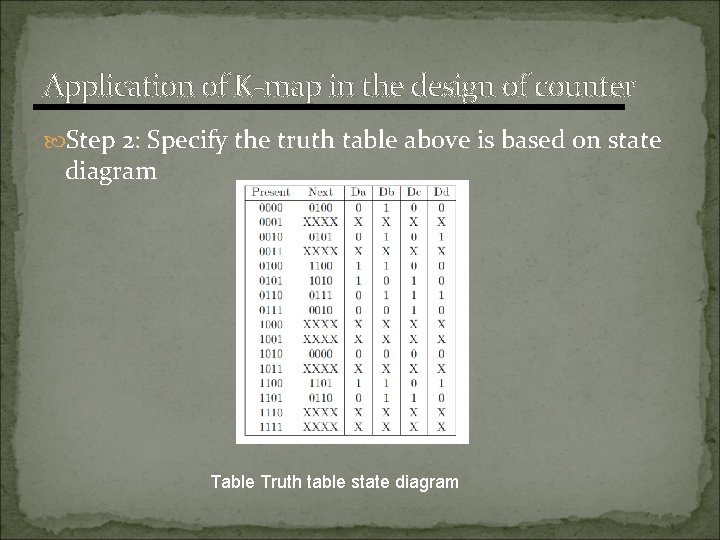

Application of K-map in the design of counter Step 2: Specify the truth table above is based on state diagram Table Truth table state diagram

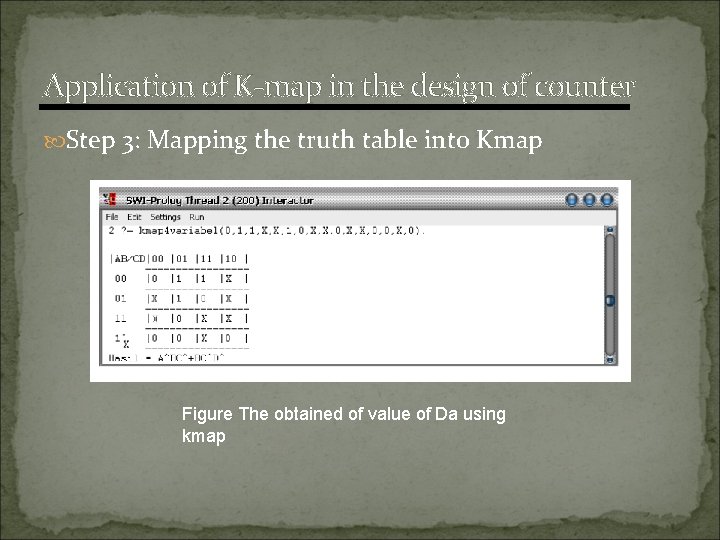

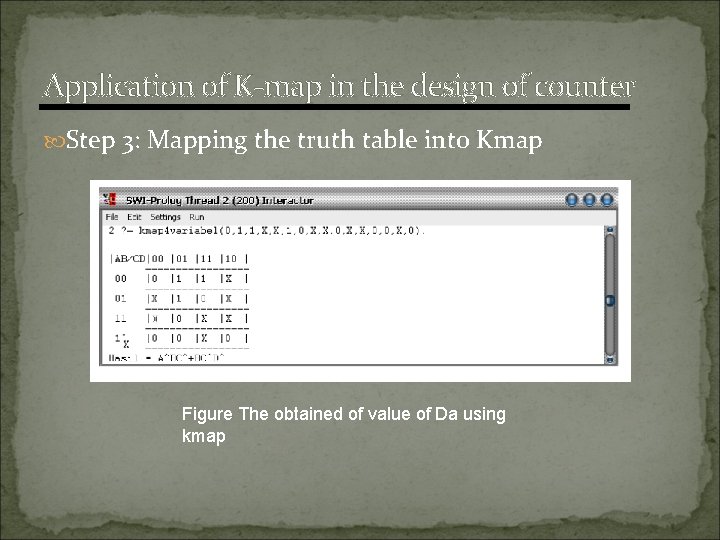

Application of K-map in the design of counter Step 3: Mapping the truth table into Kmap Figure The obtained of value of Da using kmap

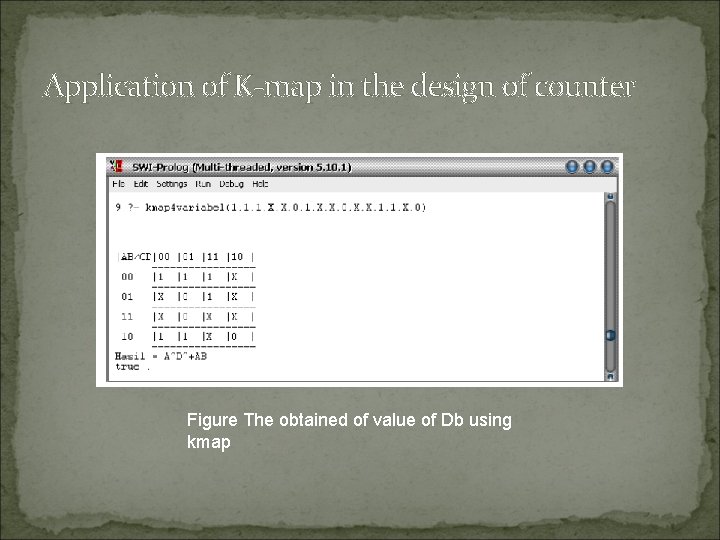

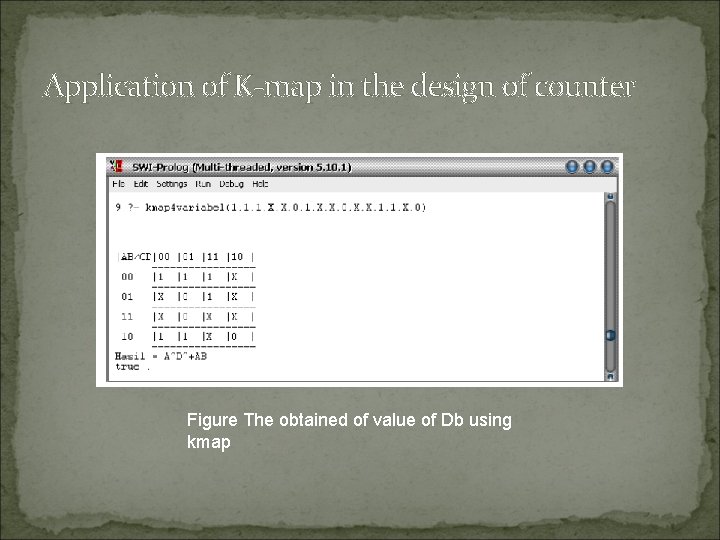

Application of K-map in the design of counter Figure The obtained of value of Db using kmap

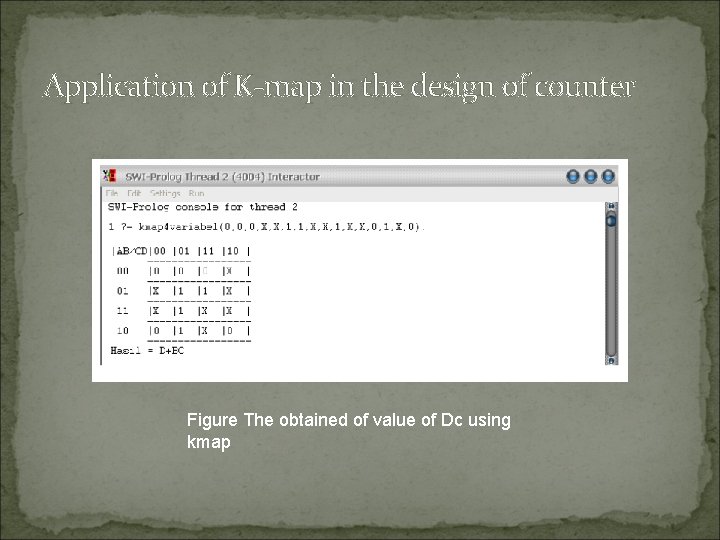

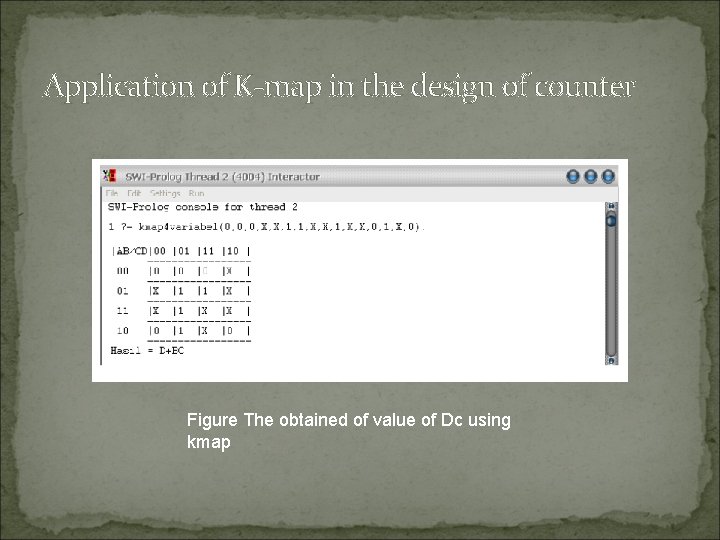

Application of K-map in the design of counter Figure The obtained of value of Dc using kmap

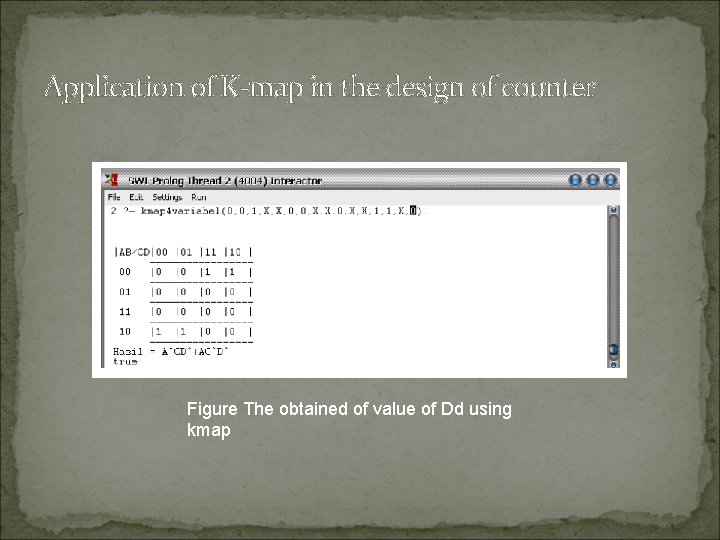

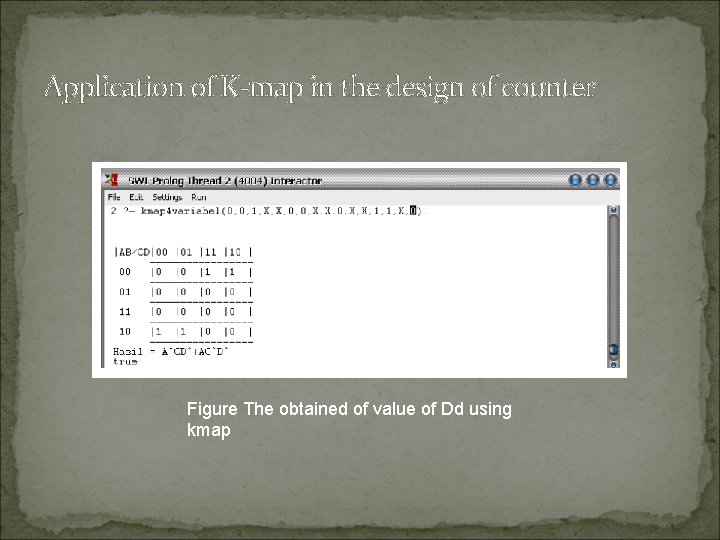

Application of K-map in the design of counter Figure The obtained of value of Dd using kmap

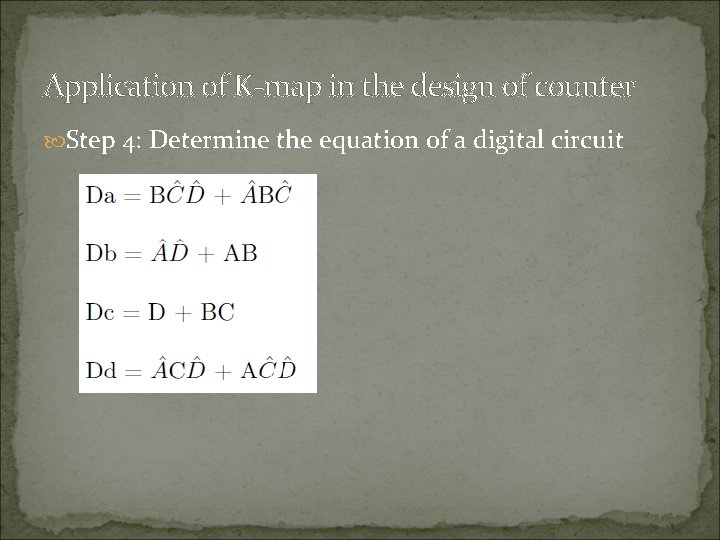

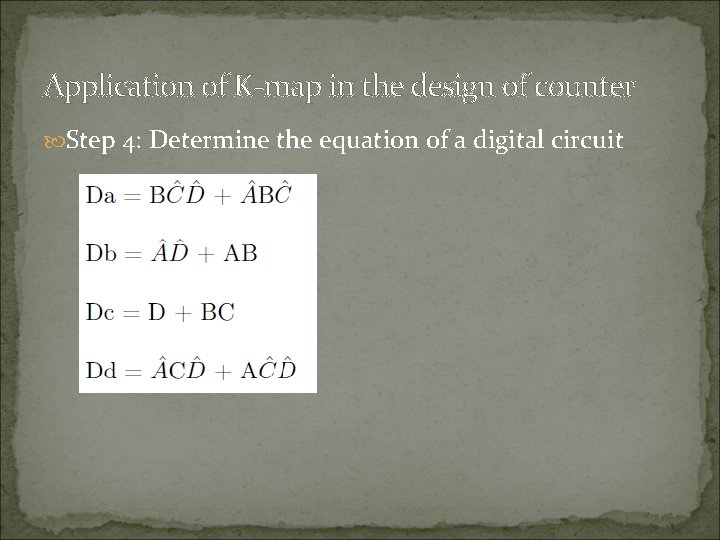

Application of K-map in the design of counter Step 4: Determine the equation of a digital circuit

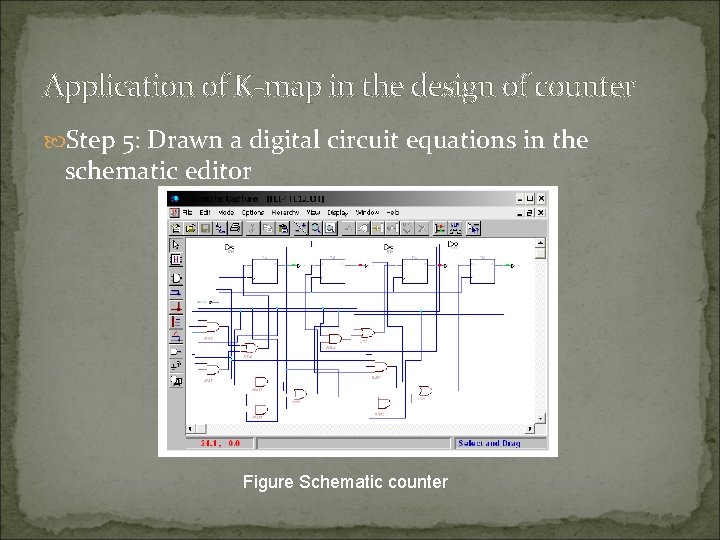

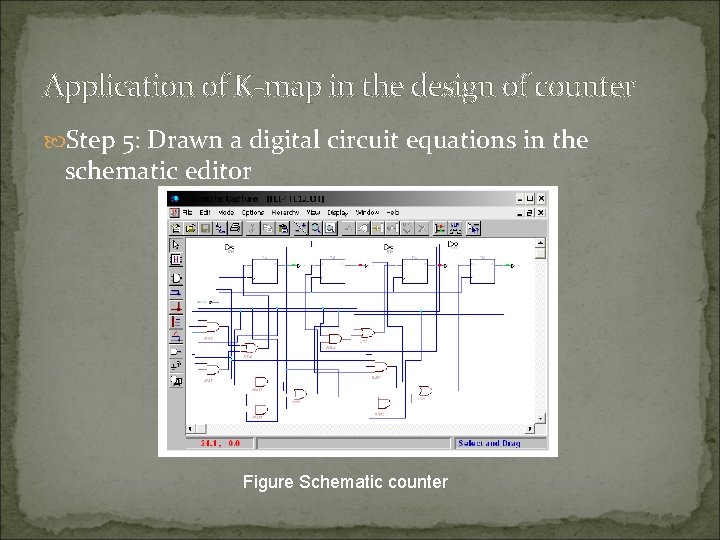

Application of K-map in the design of counter Step 5: Drawn a digital circuit equations in the schematic editor Figure Schematic counter

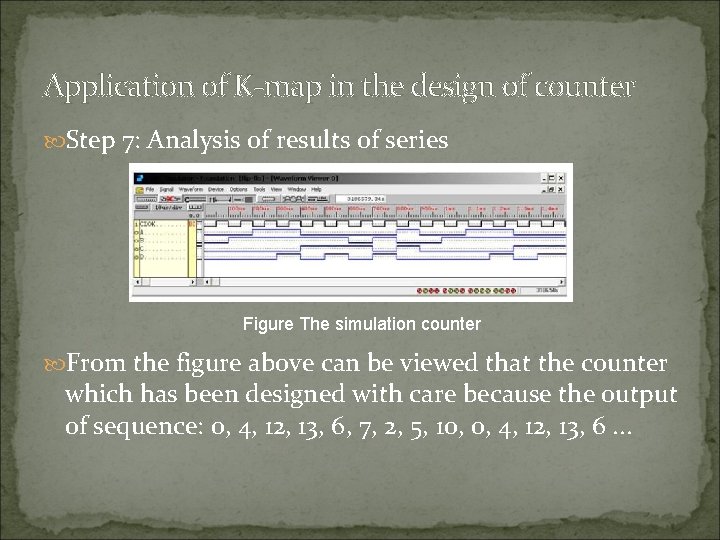

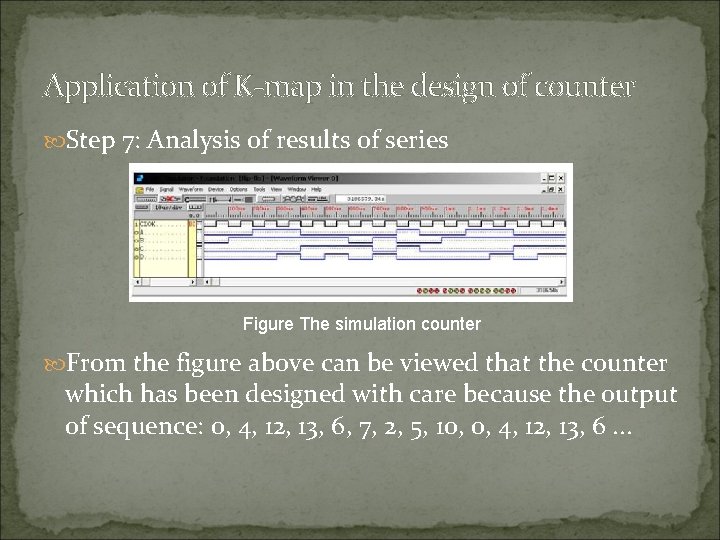

Application of K-map in the design of counter Step 7: Analysis of results of series Figure The simulation counter From the figure above can be viewed that the counter which has been designed with care because the output of sequence: 0, 4, 12, 13, 6, 7, 2, 5, 10, 0, 4, 12, 13, 6. . .

Conclusions Some processes kmap with 2, 3, and 4 variables can be done by automated logic minimizer by using logic programming. Results from experiments digital circuit before simplified and after simplified by automated logic programming has the same result. Cost the component of the digital circuits by using kmap can be minimized without affecting the output desired Time used to simplify the digital circuits much less. Prolog language as one of the programming language is quite effective to use in the process of logic programming

Future Works Simplification kmap digital circuits up to the n variables. Displaying interface to users can be made better. Directly displaying the simplified digital circuit.

THE END THANK YOU FOR YOUR ATTENTION