Atmel TimerCounter System Most microcontrollers include some type

- Slides: 15

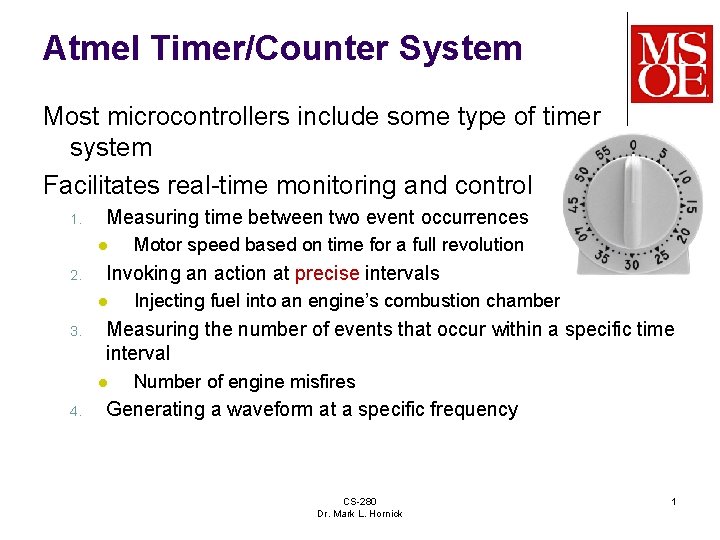

Atmel Timer/Counter System Most microcontrollers include some type of timer system Facilitates real-time monitoring and control 1. Measuring time between two event occurrences l 2. Invoking an action at precise intervals l 3. Injecting fuel into an engine’s combustion chamber Measuring the number of events that occur within a specific time interval l 4. Motor speed based on time for a full revolution Number of engine misfires Generating a waveform at a specific frequency CS-280 Dr. Mark L. Hornick 1

Atmega 32 Timer/Counter subsystem has 3 T/C units l Timer/Counter 0 l l Timer/Counter 1 l l 8 -bit timer Subsequent slides will focus on Timer/Counter 0 16 -bit timer Timer/Counter 2 l 8 -bit timer CS-280 Dr. Mark L. Hornick 2

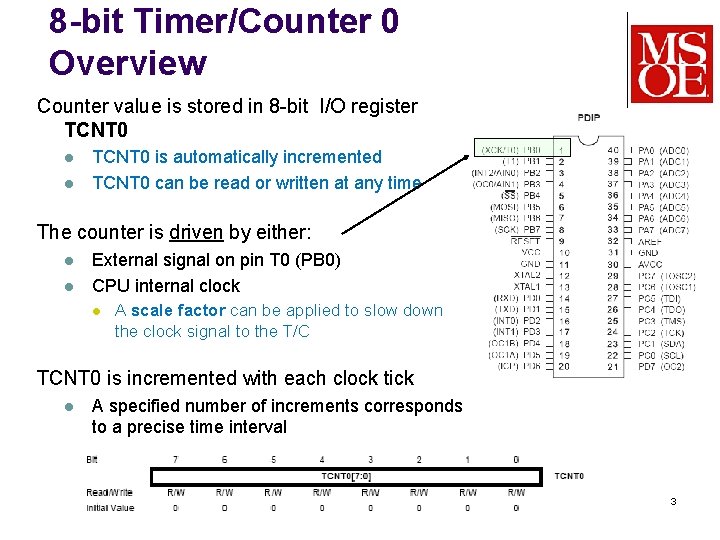

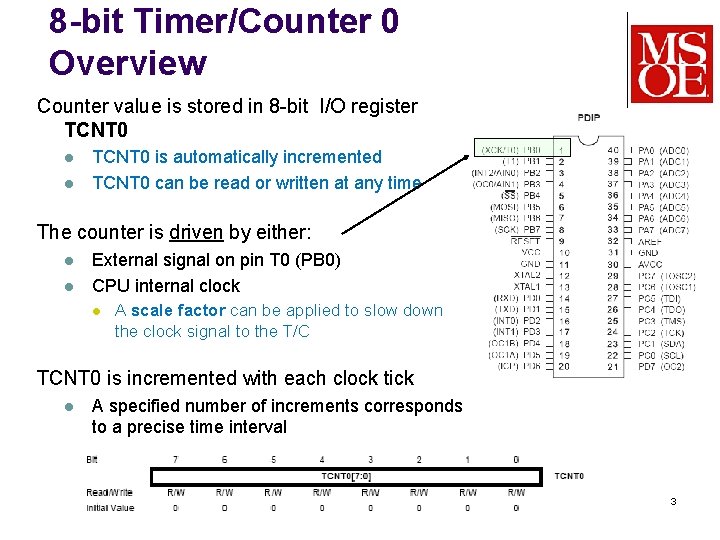

8 -bit Timer/Counter 0 Overview Counter value is stored in 8 -bit I/O register TCNT 0 l l TCNT 0 is automatically incremented TCNT 0 can be read or written at any time The counter is driven by either: l l External signal on pin T 0 (PB 0) CPU internal clock l A scale factor can be applied to slow down the clock signal to the T/C TCNT 0 is incremented with each clock tick l A specified number of increments corresponds to a precise time interval CS-280 Dr. Mark L. Hornick 3

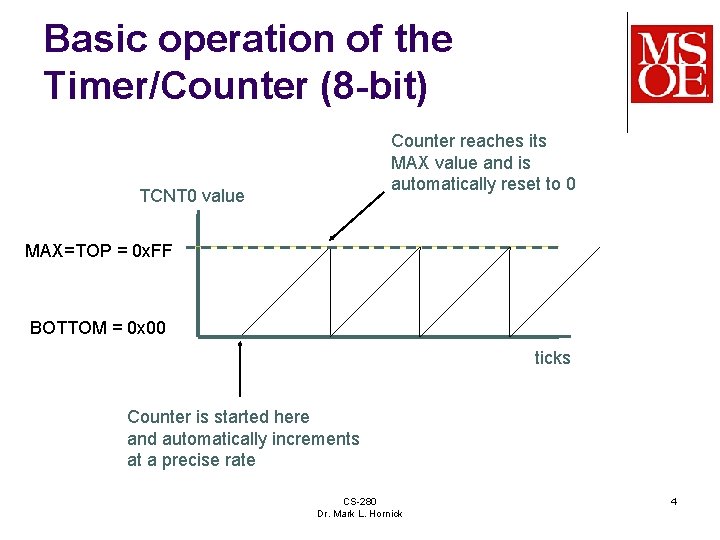

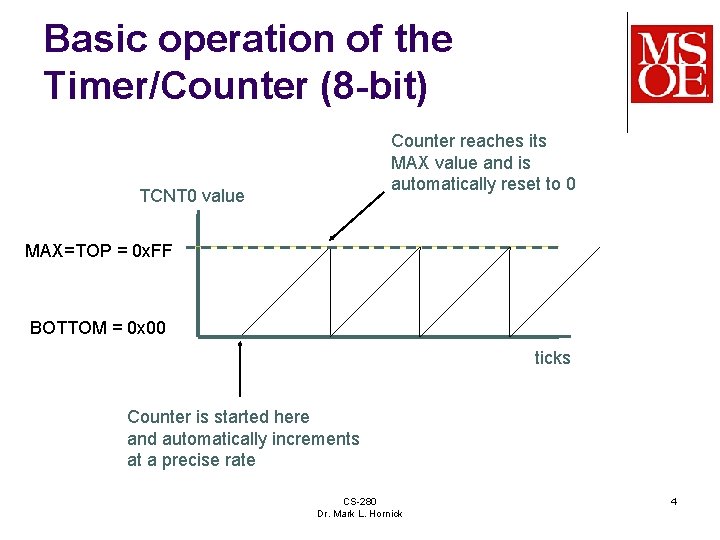

Basic operation of the Timer/Counter (8 -bit) Counter reaches its MAX value and is automatically reset to 0 TCNT 0 value MAX=TOP = 0 x. FF BOTTOM = 0 x 00 ticks Counter is started here and automatically increments at a precise rate CS-280 Dr. Mark L. Hornick 4

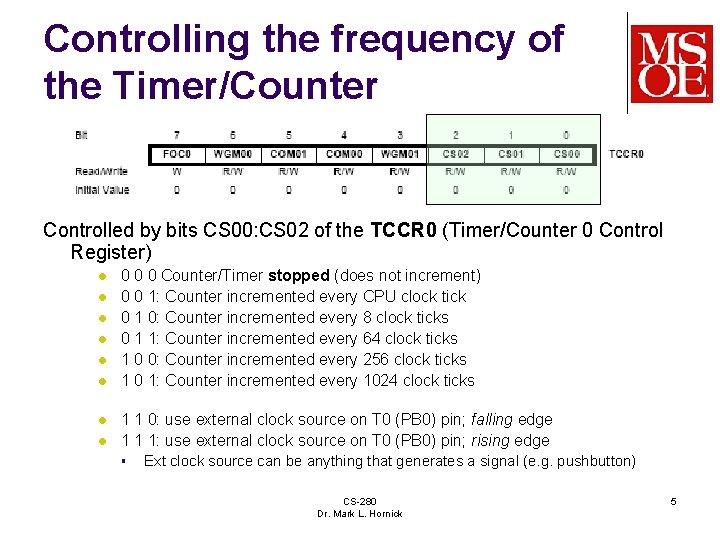

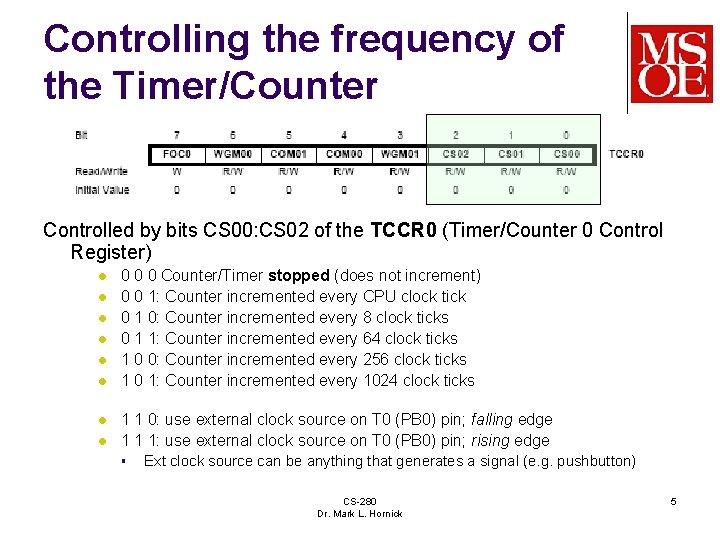

Controlling the frequency of the Timer/Counter Controlled by bits CS 00: CS 02 of the TCCR 0 (Timer/Counter 0 Control Register) l l l l 0 0 0 Counter/Timer stopped (does not increment) 0 0 1: Counter incremented every CPU clock tick 0 1 0: Counter incremented every 8 clock ticks 0 1 1: Counter incremented every 64 clock ticks 1 0 0: Counter incremented every 256 clock ticks 1 0 1: Counter incremented every 1024 clock ticks 1 1 0: use external clock source on T 0 (PB 0) pin; falling edge 1 1 1: use external clock source on T 0 (PB 0) pin; rising edge § Ext clock source can be anything that generates a signal (e. g. pushbutton) CS-280 Dr. Mark L. Hornick 5

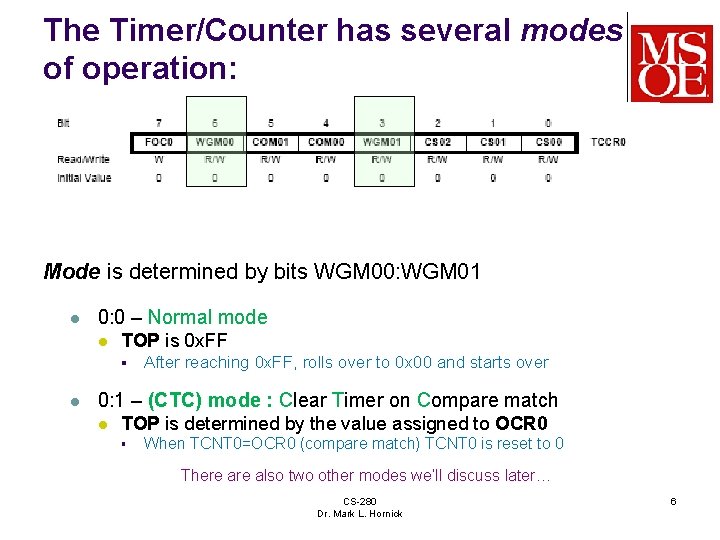

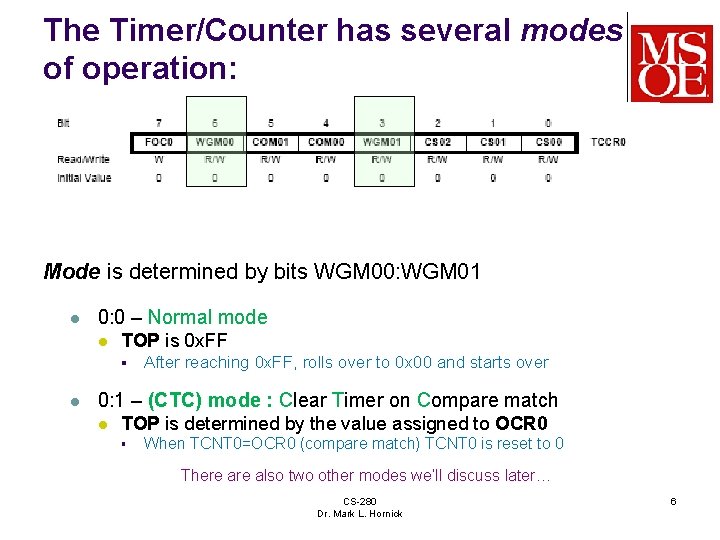

The Timer/Counter has several modes of operation: Mode is determined by bits WGM 00: WGM 01 l 0: 0 – Normal mode l TOP is 0 x. FF § l After reaching 0 x. FF, rolls over to 0 x 00 and starts over 0: 1 – (CTC) mode : Clear Timer on Compare match l TOP is determined by the value assigned to OCR 0 § When TCNT 0=OCR 0 (compare match) TCNT 0 is reset to 0 There also two other modes we’ll discuss later… CS-280 Dr. Mark L. Hornick 6

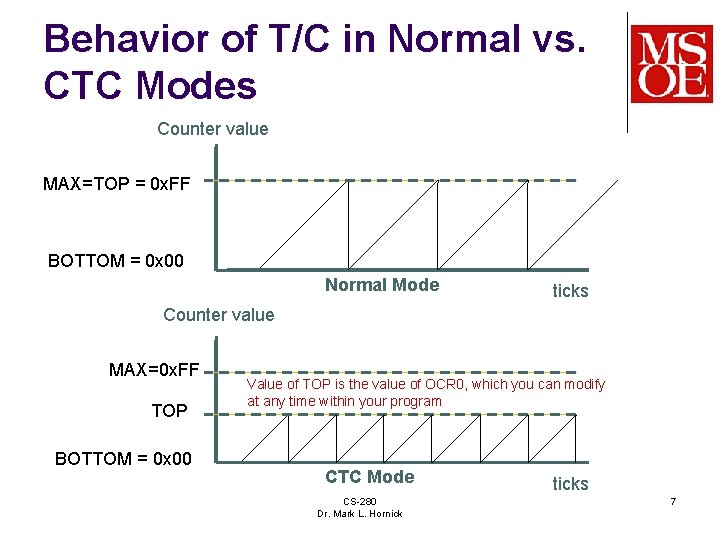

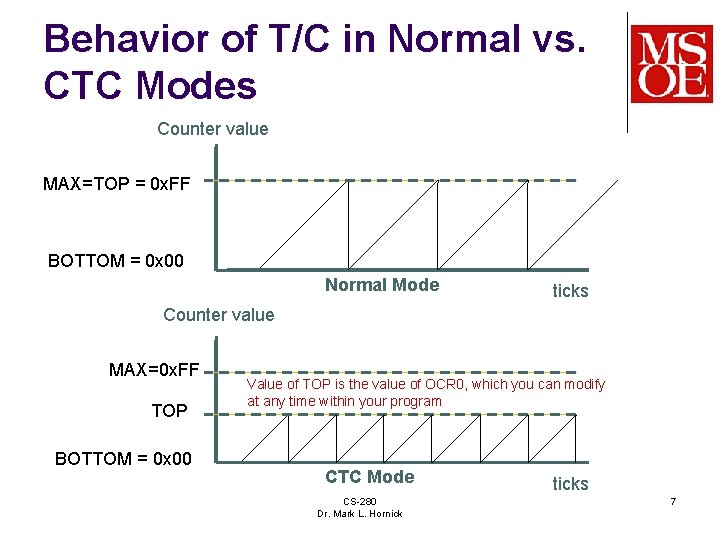

Behavior of T/C in Normal vs. CTC Modes Counter value MAX=TOP = 0 x. FF BOTTOM = 0 x 00 Normal Mode ticks Counter value MAX=0 x. FF TOP BOTTOM = 0 x 00 Value of TOP is the value of OCR 0, which you can modify at any time within your program CTC Mode CS-280 Dr. Mark L. Hornick ticks 7

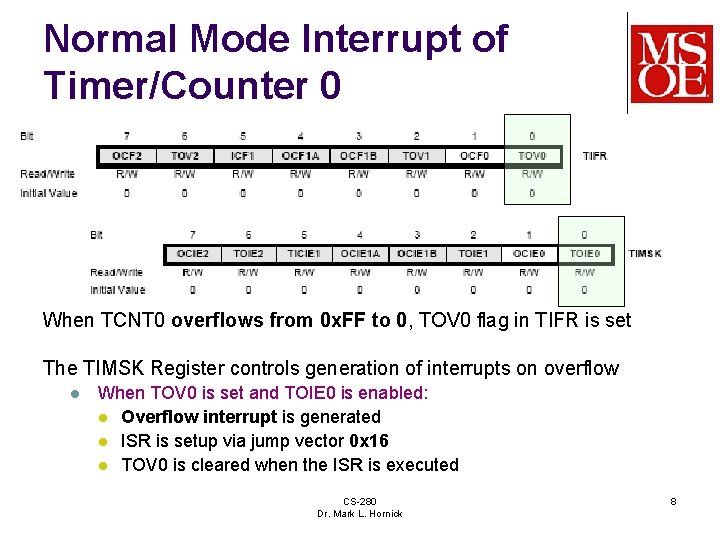

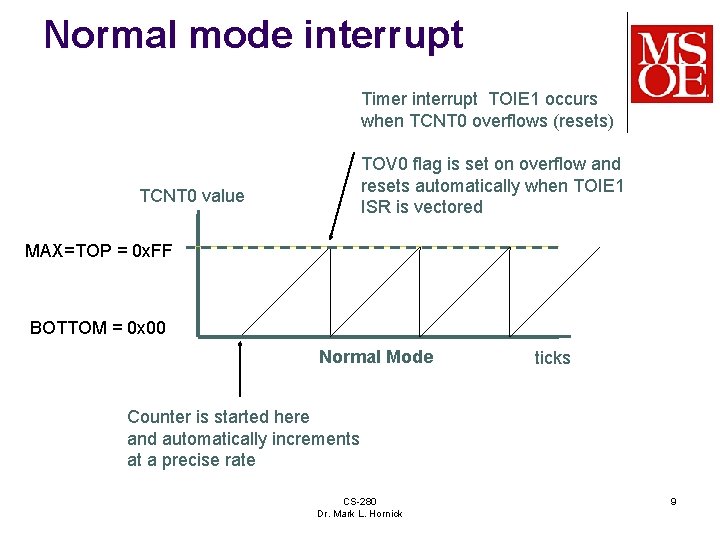

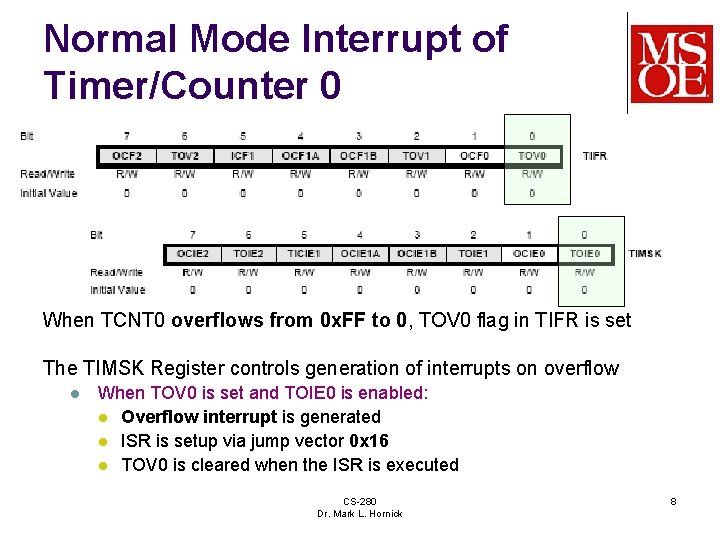

Normal Mode Interrupt of Timer/Counter 0 When TCNT 0 overflows from 0 x. FF to 0, TOV 0 flag in TIFR is set The TIMSK Register controls generation of interrupts on overflow l When TOV 0 is set and TOIE 0 is enabled: l Overflow interrupt is generated l ISR is setup via jump vector 0 x 16 l TOV 0 is cleared when the ISR is executed CS-280 Dr. Mark L. Hornick 8

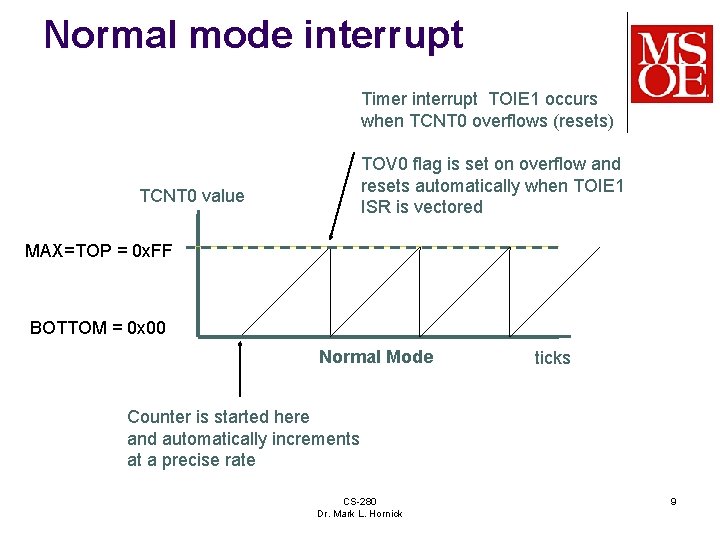

Normal mode interrupt Timer interrupt TOIE 1 occurs when TCNT 0 overflows (resets) TOV 0 flag is set on overflow and resets automatically when TOIE 1 ISR is vectored TCNT 0 value MAX=TOP = 0 x. FF BOTTOM = 0 x 00 Normal Mode ticks Counter is started here and automatically increments at a precise rate CS-280 Dr. Mark L. Hornick 9

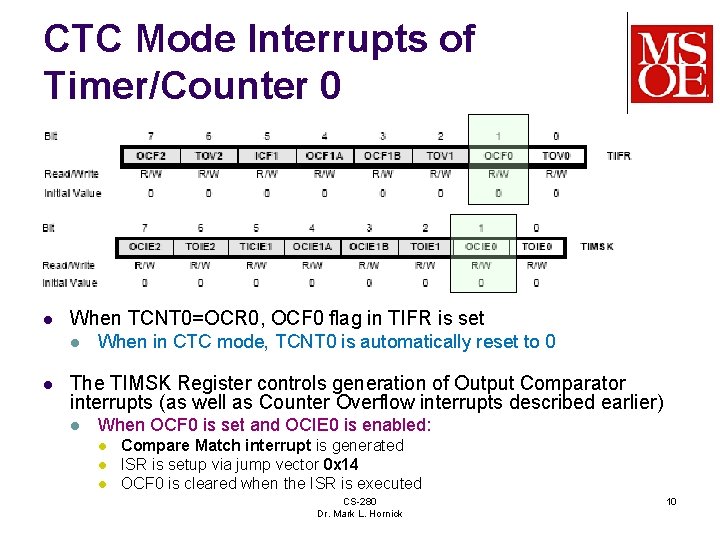

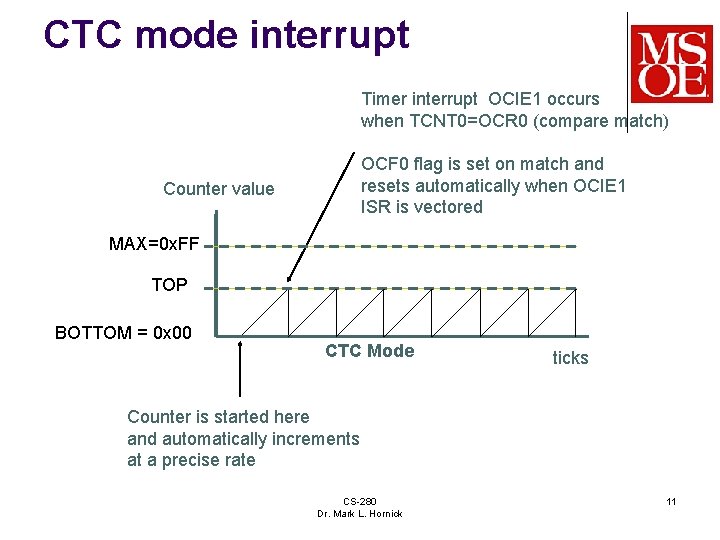

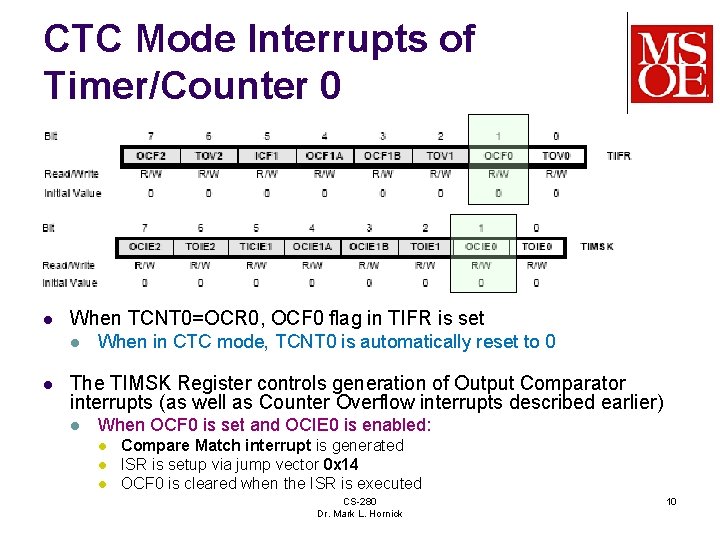

CTC Mode Interrupts of Timer/Counter 0 l When TCNT 0=OCR 0, OCF 0 flag in TIFR is set l l When in CTC mode, TCNT 0 is automatically reset to 0 The TIMSK Register controls generation of Output Comparator interrupts (as well as Counter Overflow interrupts described earlier) l When OCF 0 is set and OCIE 0 is enabled: l l l Compare Match interrupt is generated ISR is setup via jump vector 0 x 14 OCF 0 is cleared when the ISR is executed CS-280 Dr. Mark L. Hornick 10

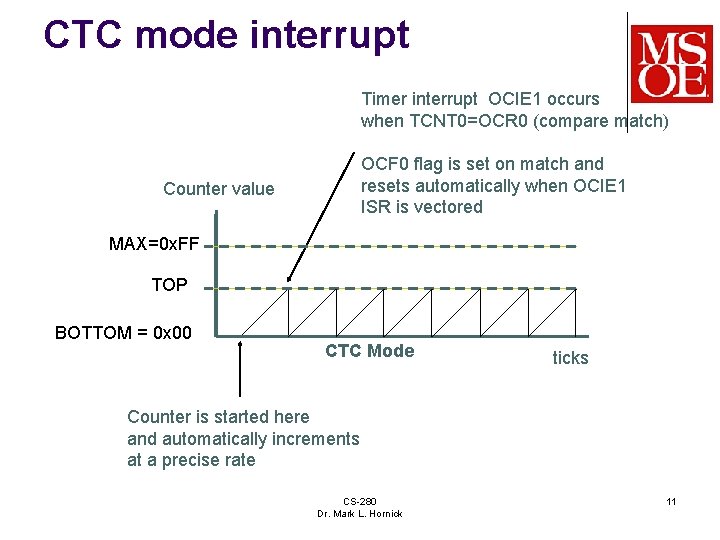

CTC mode interrupt Timer interrupt OCIE 1 occurs when TCNT 0=OCR 0 (compare match) OCF 0 flag is set on match and resets automatically when OCIE 1 ISR is vectored Counter value MAX=0 x. FF TOP BOTTOM = 0 x 00 CTC Mode ticks Counter is started here and automatically increments at a precise rate CS-280 Dr. Mark L. Hornick 11

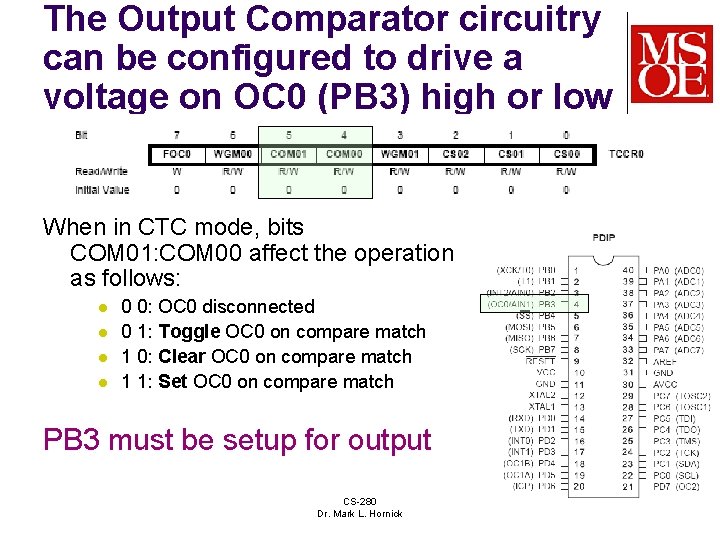

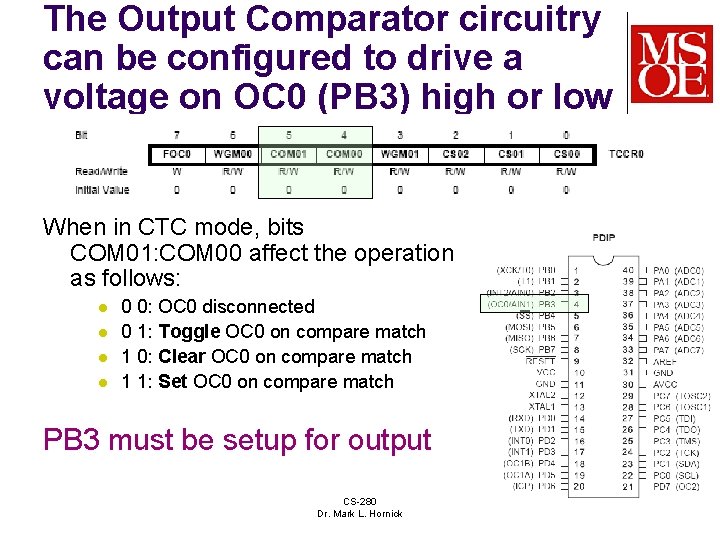

The Output Comparator circuitry can be configured to drive a voltage on OC 0 (PB 3) high or low When in CTC mode, bits COM 01: COM 00 affect the operation as follows: l l 0 0: OC 0 disconnected 0 1: Toggle OC 0 on compare match 1 0: Clear OC 0 on compare match 1 1: Set OC 0 on compare match PB 3 must be setup for output CS-280 Dr. Mark L. Hornick 12

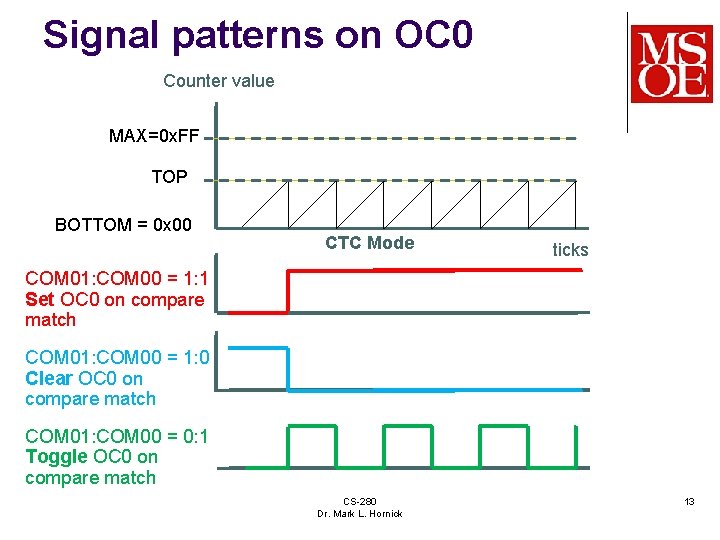

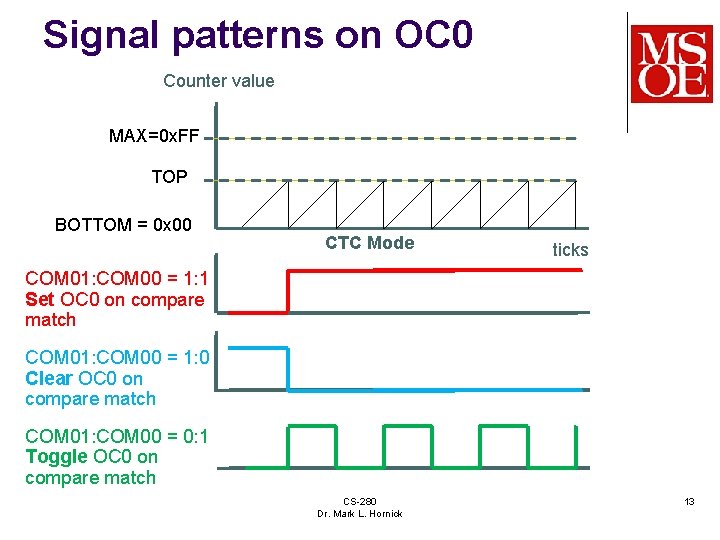

Signal patterns on OC 0 Counter value MAX=0 x. FF TOP BOTTOM = 0 x 00 CTC Mode ticks COM 01: COM 00 = 1: 1 Set OC 0 on compare match COM 01: COM 00 = 1: 0 Clear OC 0 on compare match COM 01: COM 00 = 0: 1 Toggle OC 0 on compare match CS-280 Dr. Mark L. Hornick 13

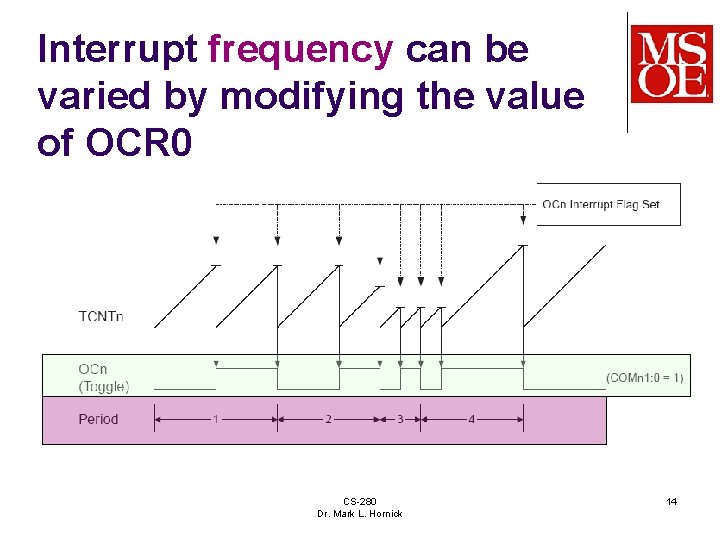

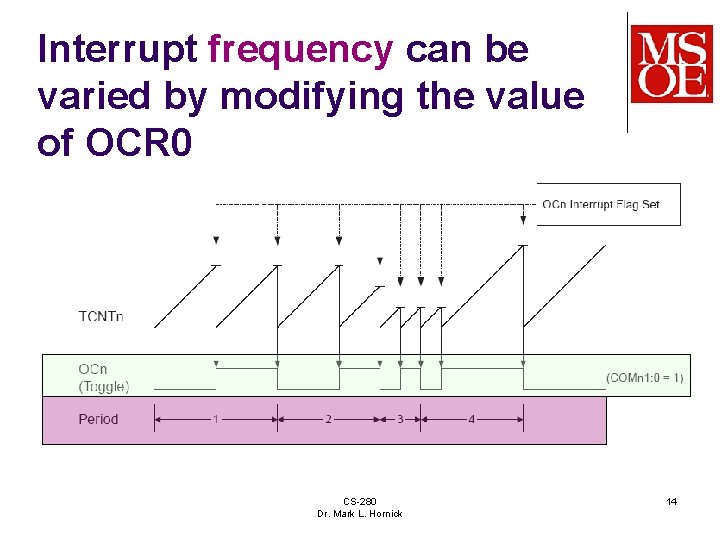

Interrupt frequency can be varied by modifying the value of OCR 0 CS-280 Dr. Mark L. Hornick 14

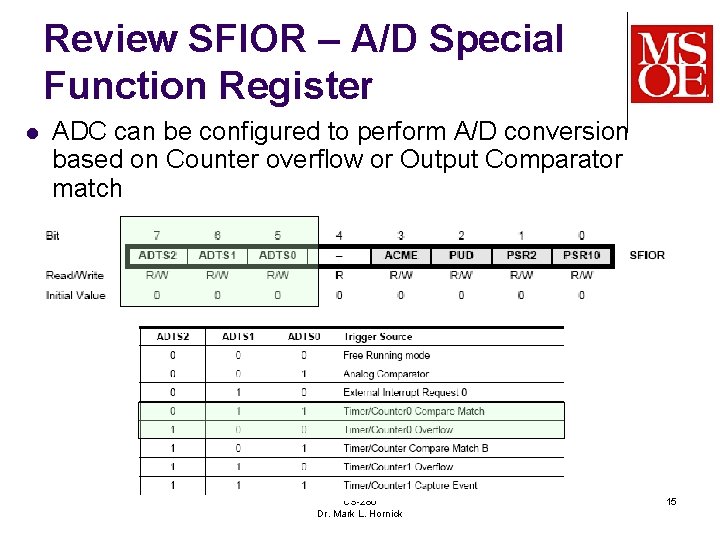

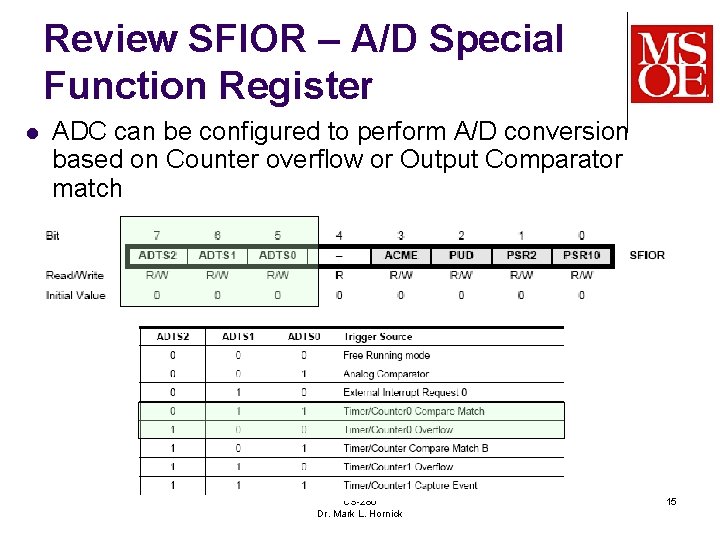

Review SFIOR – A/D Special Function Register l ADC can be configured to perform A/D conversion based on Counter overflow or Output Comparator match CS-280 Dr. Mark L. Hornick 15