ATLAS Upgrade for SLHC ESE Seminar 25 September

ATLAS Upgrade for SLHC ESE Seminar 25 September 2008 Philippe Farthouat, CERN

• Content: Ø Ø Ø Ph. Farthouat LHC upgrade plans Detector upgrade (except tracker) Electronics upgrade Tracker upgrade Upgrade organisation CERN participation ESE Seminar 25 September 2008 Slide 2

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade LHC Evolution – Phase 1 • LHC is complete apart from full collimation – – – Limited to 40 % of nominal for protection until collimators installed Collimators to be completed in 2010/11 shutdown, allowing rise to ~nominal luminosity of 1034 cm-2 s-1 Best current estimate is that one nominal year will deliver 60 fb-1 • Phase-1: 2013 -2016 – Linac-4 • Approved and work has started; higher brightness – Allows higher LHC current, to “Ultimate” which is 2. 3 times nominal • – Ready to run in 2013 New Inner Triplet focusing magnets Use spare super-conductor from LHC magnets • Larger aperture, allows � * of 0. 25 m instead of 0. 55 m • Install in 2012/13 shutdown • In principle also gives factor 2 on nominal • – Expectation is that these two improvements will allow a ramp-up to 3 x nominal; Conditions: 70 minimum bias events per BC; ~700 fb-1 before phase 2 Ph. Farthouat ESE Seminar 25 September 2008 Slide 3

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade LHC Evolution – Phase 2 • Several ideas being explored to see the best way to achieve 10 x nominal in 2017 • Injector improvements – higher current, higher reliability, shorter fill time • New machine elements and ideas: – – Magnets inside the experiments for “Early Separation” schemes Crab cavities Wire correctors Luminosity Leveling Ph. Farthouat ESE Seminar 25 September 2008 Slide 4

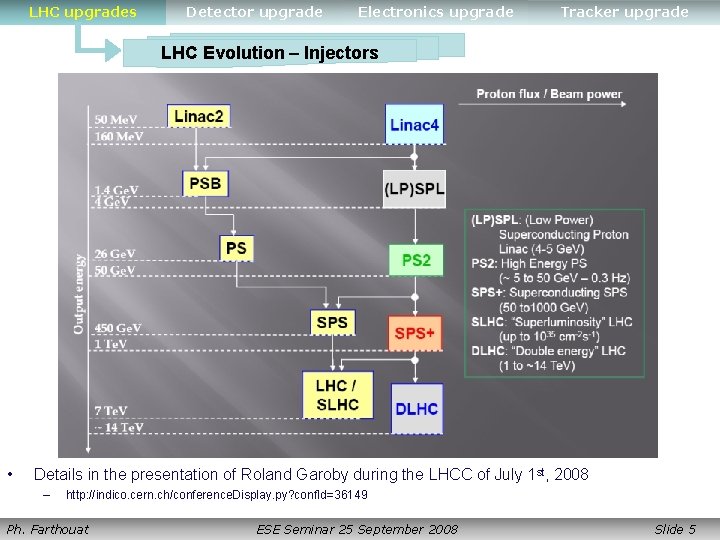

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade LHC Evolution – Injectors • Details in the presentation of Roland Garoby during the LHCC of July 1 st, 2008 – http: //indico. cern. ch/conference. Display. py? conf. Id=36149 Ph. Farthouat ESE Seminar 25 September 2008 Slide 5

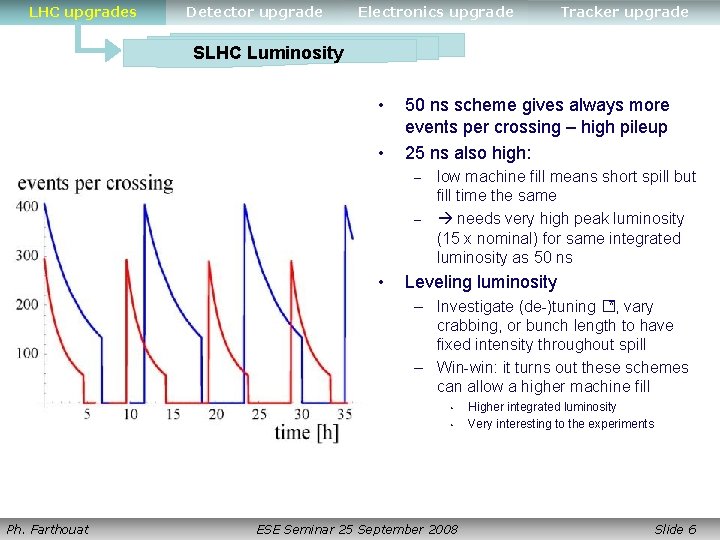

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade SLHC Luminosity • • 50 ns scheme gives always more events per crossing – high pileup 25 ns also high: – – • low machine fill means short spill but fill time the same needs very high peak luminosity (15 x nominal) for same integrated luminosity as 50 ns Leveling luminosity – Investigate (de-)tuning �*, vary crabbing, or bunch length to have fixed intensity throughout spill – Win-win: it turns out these schemes can allow a higher machine fill • • Ph. Farthouat ESE Seminar 25 September 2008 Higher integrated luminosity Very interesting to the experiments Slide 6

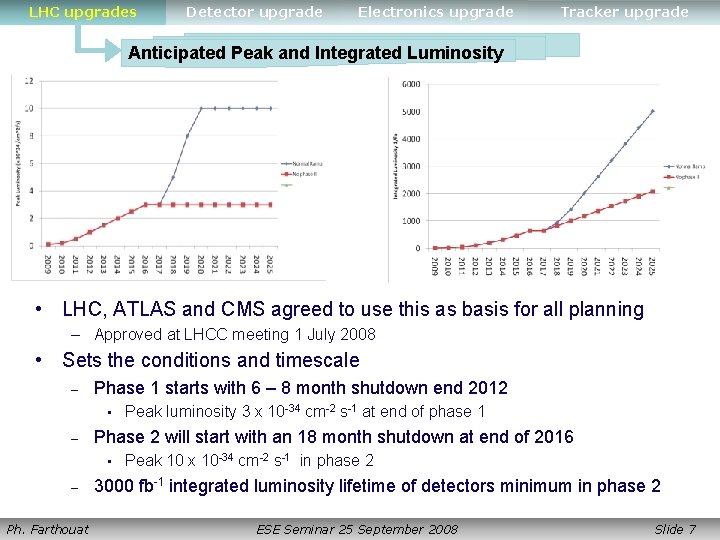

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Anticipated Peak and Integrated Luminosity • LHC, ATLAS and CMS agreed to use this as basis for all planning – Approved at LHCC meeting 1 July 2008 • Sets the conditions and timescale – Phase 1 starts with 6 – 8 month shutdown end 2012 • – Phase 2 will start with an 18 month shutdown at end of 2016 • – Ph. Farthouat Peak luminosity 3 x 10 -34 cm-2 s-1 at end of phase 1 Peak 10 x 10 -34 cm-2 s-1 in phase 2 3000 fb-1 integrated luminosity lifetime of detectors minimum in phase 2 ESE Seminar 25 September 2008 Slide 7

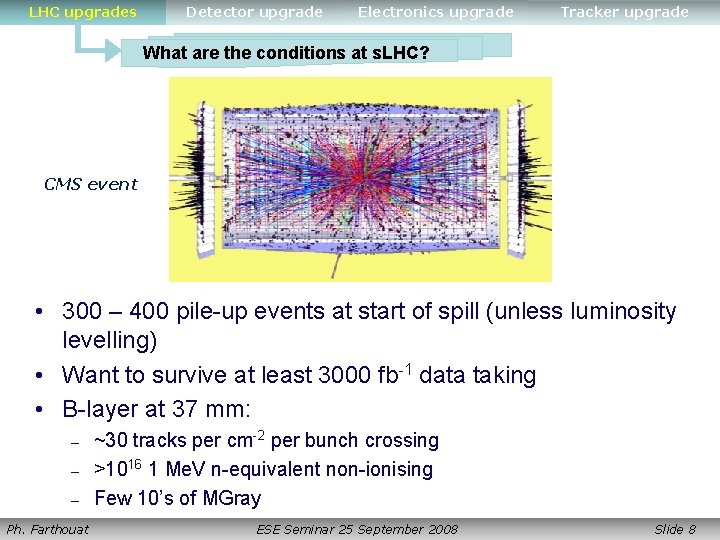

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade What are the conditions at s. LHC? CMS event • 300 – 400 pile-up events at start of spill (unless luminosity levelling) • Want to survive at least 3000 fb-1 data taking • B-layer at 37 mm: – – – Ph. Farthouat ~30 tracks per cm-2 per bunch crossing >1016 1 Me. V n-equivalent non-ionising Few 10’s of MGray ESE Seminar 25 September 2008 Slide 8

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Phase 1 • Limited time for installation – 6 to 8 months in 2012/13 shutdown • Small increase in peak rate above previous estimates (2 --> 3 x 1034) • Total integrated luminosity similar to previous expectations ~700 fb-1 – Limited changes needed • Pixel B-layer to be replaced – – In fact the replacement would take more than a year A new B-layer will be put inside the current detector, along with a new smaller diameter beam pipe • TDAQ – – TDAQ will be continuously upgraded to cope with rates and take advantage of new processing power Level-1 trigger might need some improvement such as the introduction of topological triggers • • Ph. Farthouat The Central Trigger Processor would be affected (CERN involvement) Fast track finding might be introduced to speed up Level-2 ESE Seminar 25 September 2008 Slide 9

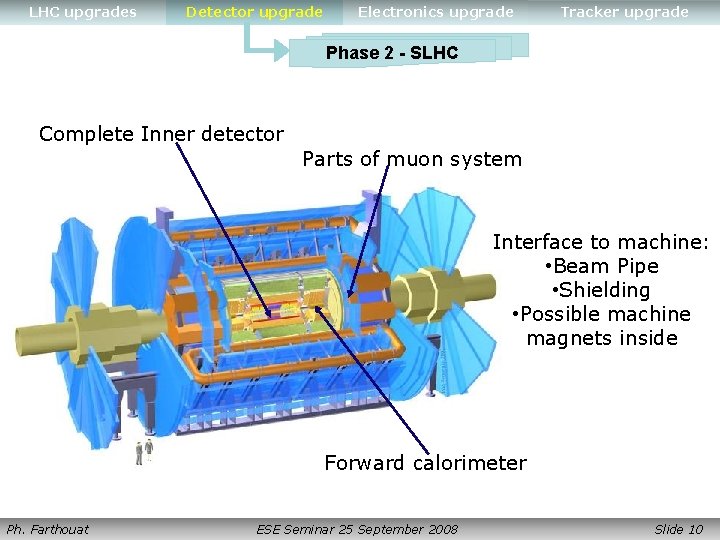

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Phase 2 - SLHC Complete Inner detector Parts of muon system Interface to machine: • Beam Pipe • Shielding • Possible machine magnets inside Forward calorimeter Ph. Farthouat ESE Seminar 25 September 2008 Slide 10

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Beam Pipe & Shielding • Currently central part of ATLAS beam pipe is Be, rest is Stainless Steel – SS gives large backgrounds, especially to muon system • SS gets activated Access problems for maintenance – – Change to Al in ~2009 Change to all Be for SLHC Be is expensive compared to SS, but cheap compared to muon chambers! It gives a big reduction in background in critical areas of muon system • A factor 2 or better • Shielding – Already highly optimised, only small improvements possible Ph. Farthouat ESE Seminar 25 September 2008 Slide 11

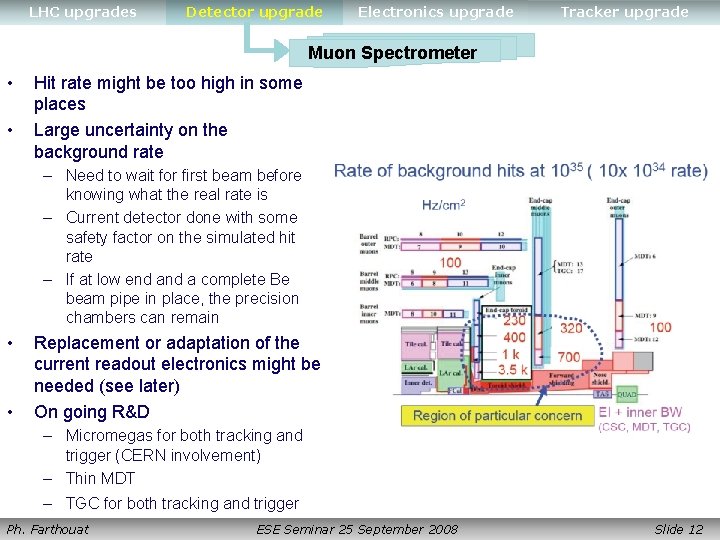

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Muon Spectrometer • • Hit rate might be too high in some places Large uncertainty on the background rate – Need to wait for first beam before knowing what the real rate is – Current detector done with some safety factor on the simulated hit rate – If at low end a complete Be beam pipe in place, the precision chambers can remain • • Replacement or adaptation of the current readout electronics might be needed (see later) On going R&D – Micromegas for both tracking and trigger (CERN involvement) – Thin MDT – TGC for both tracking and trigger Ph. Farthouat ESE Seminar 25 September 2008 Slide 12

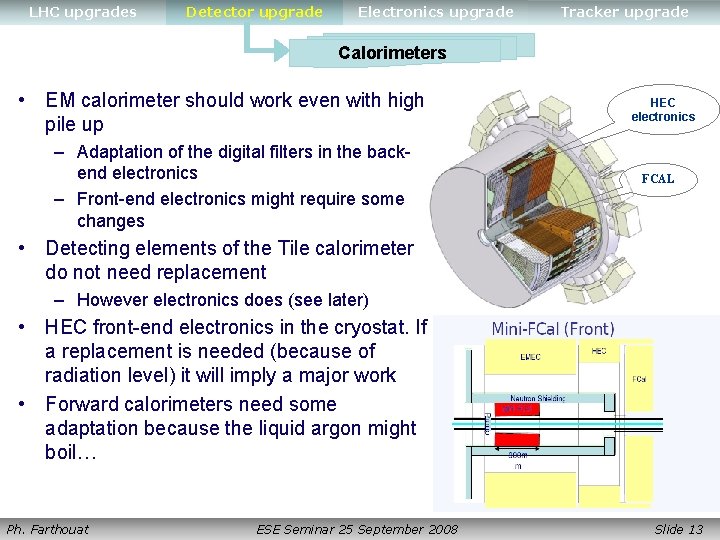

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Calorimeters • EM calorimeter should work even with high pile up – Adaptation of the digital filters in the backend electronics – Front-end electronics might require some changes HEC electronics FCAL • Detecting elements of the Tile calorimeter do not need replacement – However electronics does (see later) • HEC front-end electronics in the cryostat. If a replacement is needed (because of radiation level) it will imply a major work • Forward calorimeters need some adaptation because the liquid argon might boil… Ph. Farthouat ESE Seminar 25 September 2008 Slide 13

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Main topics • • • General concern for the electronics in the cavern Level-1 trigger Muon readout electronics Calorimeters readout electronics New readout electronics for the tracker Ph. Farthouat ESE Seminar 25 September 2008 Slide 14

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade General concerns • • The electronics installed in the cavern will be affected by the higher level of radiation ATLAS rules defined safety factors for the radiation tolerance of the electronics – Don’t know yet if we are on the safe side or not – Major upgrades could be required if not • Power supplies • FE electronics of the calorimeters and muon chambers • Control devices (ELMBs) – Wait for the beam for final assessment • A substantial fraction of the front-end electronics will be obsolete at the time of SLHC – Could need a replacement in case of high level of failure • R&D starting to be ready in case Ph. Farthouat ESE Seminar 25 September 2008 Slide 15

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Level-1 Trigger • More complexe algorithms needed – For instance, currently level-1 calorimeter only performs object counting – So far no need for tracking in level-1 although it might change • Can both the latency and the L 1 A rate be maintained at their current values (2. 5 µs and 75 -100 k. Hz)? • Latency very likely to increase • Very much linked to what will happen to readout systems of the calorimeters and muon chambers • Intermediate upgrade for Phase-1 Ph. Farthouat ESE Seminar 25 September 2008 Slide 16

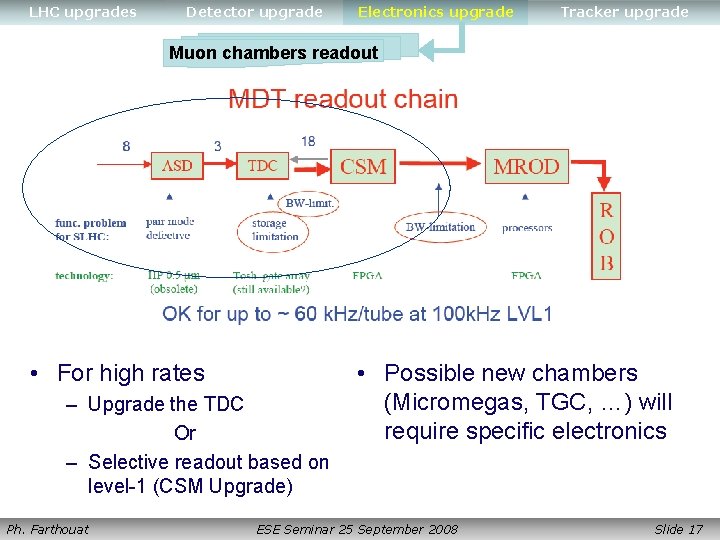

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Muon chambers readout • For high rates – Upgrade the TDC Or – Selective readout based on level-1 (CSM Upgrade) Ph. Farthouat • Possible new chambers (Micromegas, TGC, …) will require specific electronics ESE Seminar 25 September 2008 Slide 17

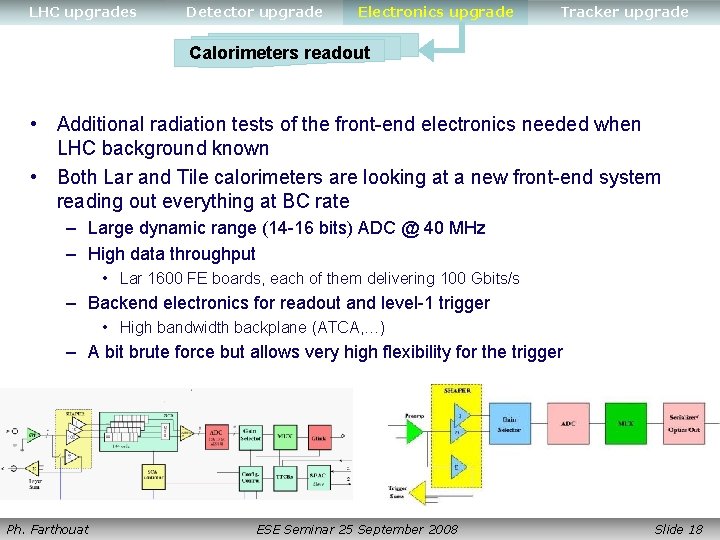

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Calorimeters readout • Additional radiation tests of the front-end electronics needed when LHC background known • Both Lar and Tile calorimeters are looking at a new front-end system reading out everything at BC rate – Large dynamic range (14 -16 bits) ADC @ 40 MHz – High data throughput • Lar 1600 FE boards, each of them delivering 100 Gbits/s – Backend electronics for readout and level-1 trigger • High bandwidth backplane (ATCA, …) – A bit brute force but allows very high flexibility for the trigger Ph. Farthouat ESE Seminar 25 September 2008 Slide 18

LHC upgrades Detector upgrade Electronics upgrade Tracker upgrade Content Ø Detector layout Ø Ø Ø Readout Detector Control Power Services Schedule On-going developments • On-going work in the collaboration, still far from being finalised • Mainly presentation of the strips detector • A lot of what is presented here is very likely to be inaccurate or even wrong Ph. Farthouat ESE Seminar 25 September 2008 Slide 19

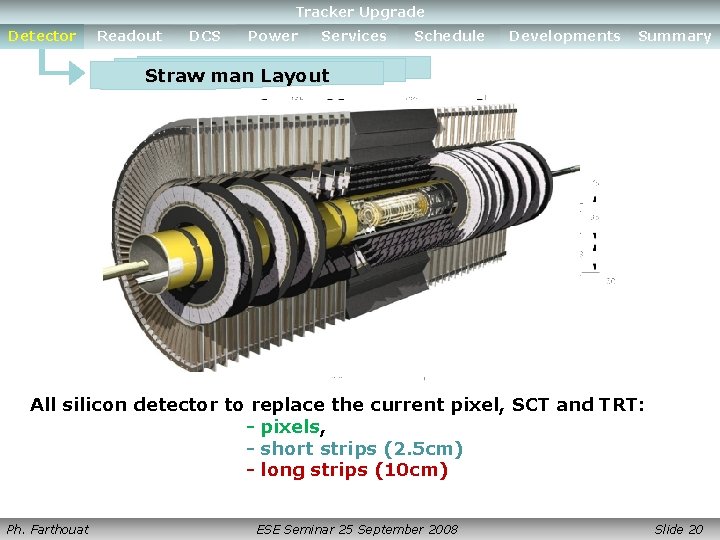

Detector Readout DCS Upgrade Power. Tracker Services Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Straw man Layout All silicon detector to replace the current pixel, SCT and TRT: - pixels, - short strips (2. 5 cm) - long strips (10 cm) Ph. Farthouat ESE Seminar 25 September 2008 Slide 20

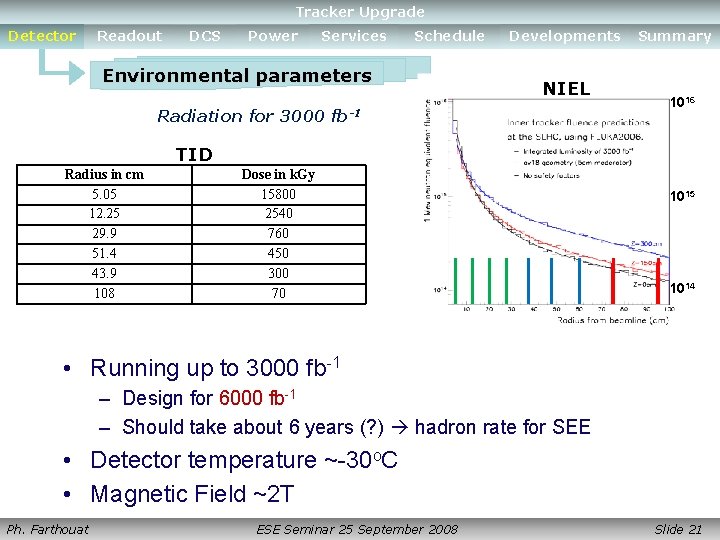

Detector Readout DCS Upgrade Power. Tracker Services Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Environmental parameters NIEL Radiation for 3000 fb-1 1016 TID Radius in cm 5. 05 12. 25 29. 9 51. 4 43. 9 108 Dose in k. Gy 15800 2540 760 450 300 70 1015 1014 • Running up to 3000 fb-1 – Design for 6000 fb-1 – Should take about 6 years (? ) hadron rate for SEE • Detector temperature ~-30 o. C • Magnetic Field ~2 T Ph. Farthouat ESE Seminar 25 September 2008 Slide 21

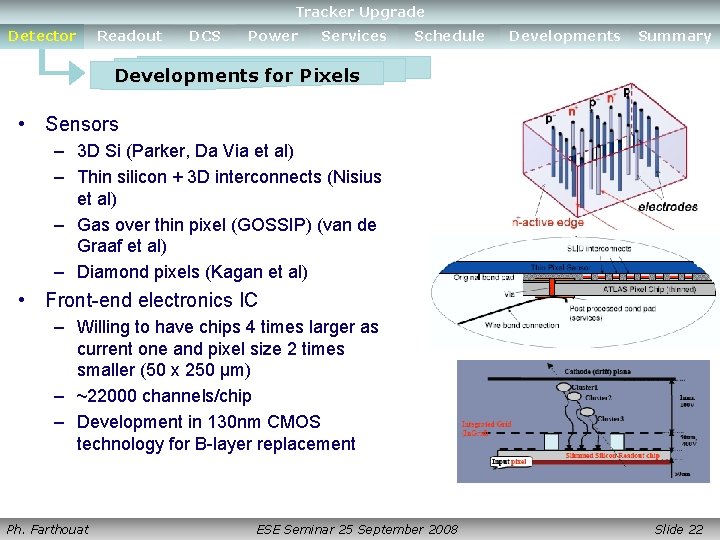

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Developments for Pixels • Sensors – 3 D Si (Parker, Da Via et al) – Thin silicon + 3 D interconnects (Nisius et al) – Gas over thin pixel (GOSSIP) (van de Graaf et al) – Diamond pixels (Kagan et al) • Front-end electronics IC – Willing to have chips 4 times larger as current one and pixel size 2 times smaller (50 x 250 µm) – ~22000 channels/chip – Development in 130 nm CMOS technology for B-layer replacement Ph. Farthouat ESE Seminar 25 September 2008 Slide 22

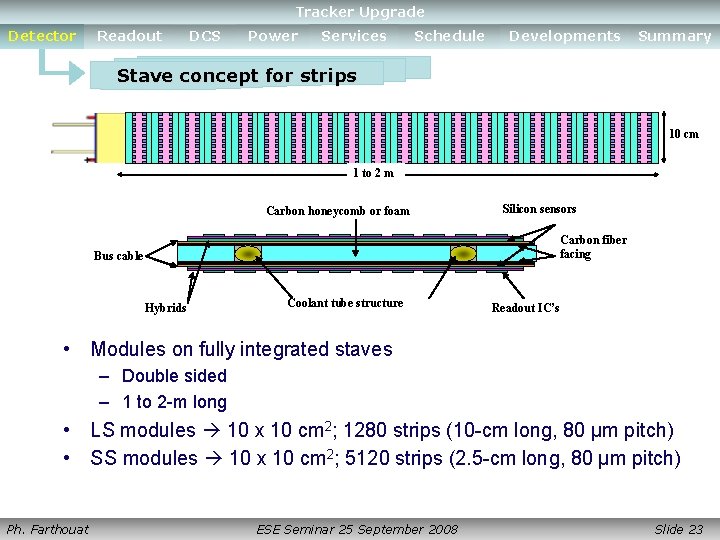

Detector Readout DCS Upgrade Power. Tracker Services Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Stave concept for strips 10 cm 1 to 2 m Carbon honeycomb or foam Silicon sensors Carbon fiber facing Bus cable Hybrids Coolant tube structure Readout IC’s • Modules on fully integrated staves – Double sided – 1 to 2 -m long • LS modules 10 x 10 cm 2; 1280 strips (10 -cm long, 80 µm pitch) • SS modules 10 x 10 cm 2; 5120 strips (2. 5 -cm long, 80 µm pitch) Ph. Farthouat ESE Seminar 25 September 2008 Slide 23

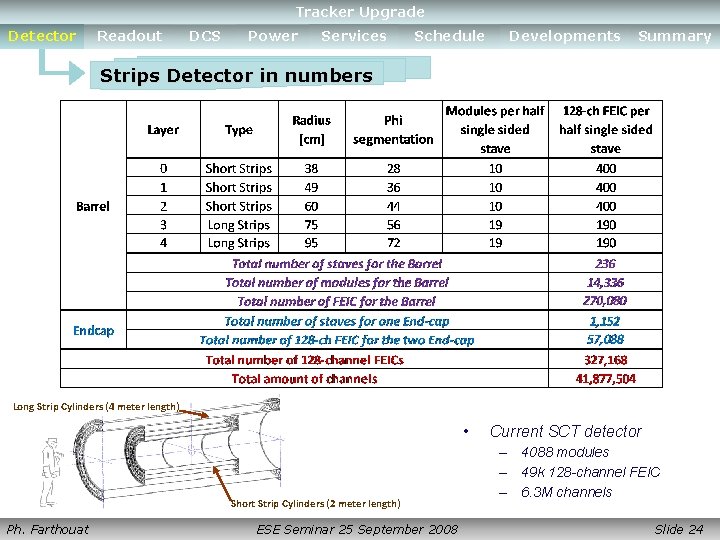

Detector Readout DCS Upgrade Power. Tracker Services Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Strips Detector in numbers Long Strip Cylinders (4 meter length) • Short Strip Cylinders (2 meter length) Ph. Farthouat ESE Seminar 25 September 2008 Current SCT detector – 4088 modules – 49 k 128 -channel FEIC – 6. 3 M channels Slide 24

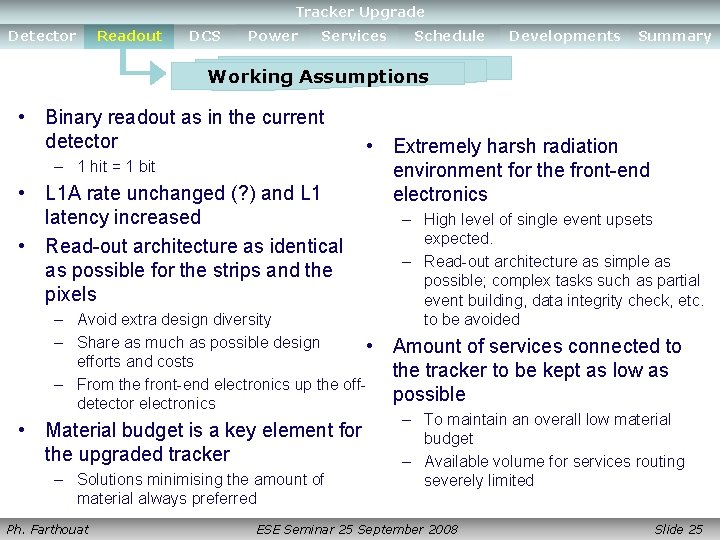

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Working Assumptions • Binary readout as in the current detector – 1 hit = 1 bit • L 1 A rate unchanged (? ) and L 1 latency increased • Read-out architecture as identical as possible for the strips and the pixels • Extremely harsh radiation environment for the front-end electronics – Avoid extra design diversity – Share as much as possible design • efforts and costs – From the front-end electronics up the offdetector electronics • Material budget is a key element for the upgraded tracker – Solutions minimising the amount of material always preferred Ph. Farthouat – High level of single event upsets expected. – Read-out architecture as simple as possible; complex tasks such as partial event building, data integrity check, etc. to be avoided Amount of services connected to the tracker to be kept as low as possible – To maintain an overall low material budget – Available volume for services routing severely limited ESE Seminar 25 September 2008 Slide 25

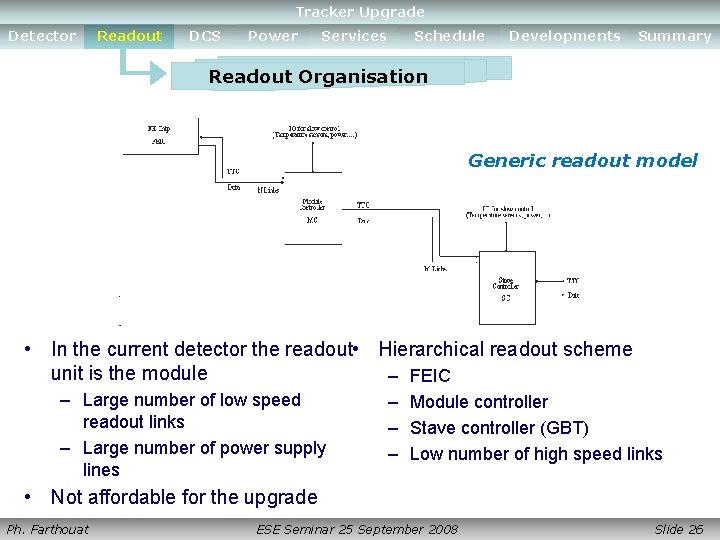

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Readout Organisation Generic readout model • In the current detector the readout • Hierarchical readout scheme unit is the module – FEIC – Large number of low speed readout links – Large number of power supply lines – Module controller – Stave controller (GBT) – Low number of high speed links • Not affordable for the upgrade Ph. Farthouat ESE Seminar 25 September 2008 Slide 26

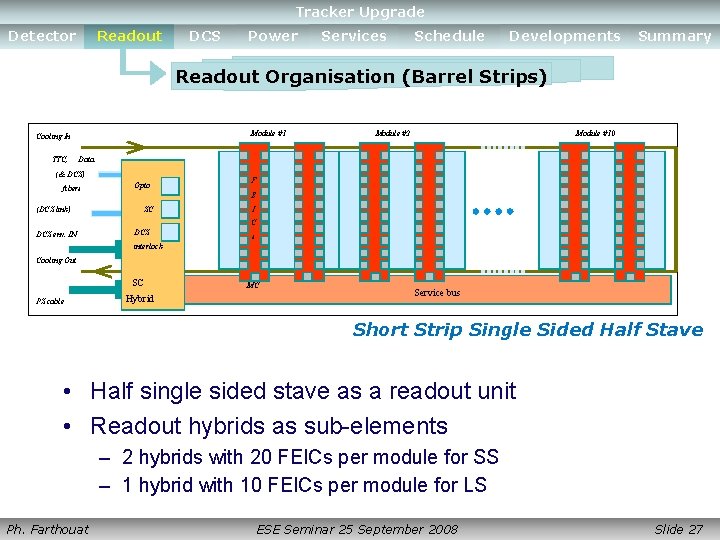

Detector Readout DCS Power. Tracker Services Upgrade Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Readout Organisation (Barrel Strips) Module #1 Cooling In TTC, Module #2 Module #10 Data ( & DCS) fibers (DCS link) Opto F E SC I C DCS env. IN DCS s interlock Cooling Out SC PS cable Hybrid MC Service bus Short Strip Single Sided Half Stave • Half single sided stave as a readout unit • Readout hybrids as sub-elements – 2 hybrids with 20 FEICs per module for SS – 1 hybrid with 10 FEICs per module for LS Ph. Farthouat ESE Seminar 25 September 2008 Slide 27

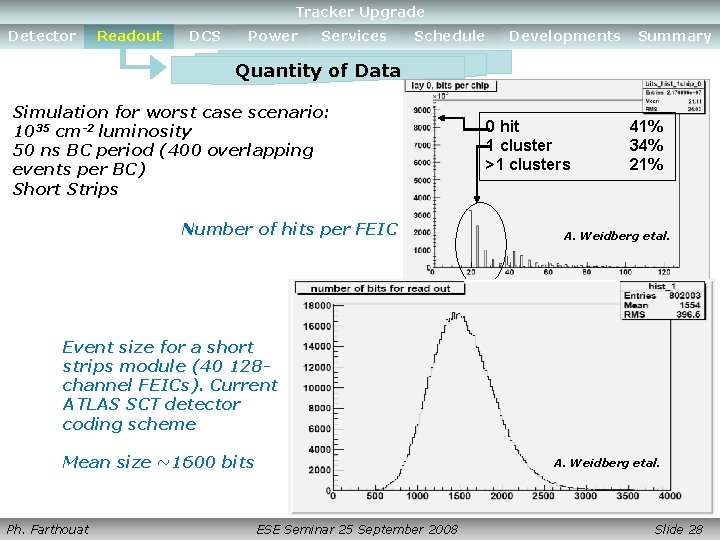

Detector Readout DCS Power. Tracker Services Upgrade Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Quantity of Data Simulation for worst case scenario: 1035 cm-2 luminosity 50 ns BC period (400 overlapping events per BC) Short Strips Number of hits per FEIC 0 hit 1 cluster >1 clusters 41% 34% 21% A. Weidberg etal. Event size for a short strips module (40 128 channel FEICs). Current ATLAS SCT detector coding scheme Mean size ~1600 bits Ph. Farthouat A. Weidberg etal. ESE Seminar 25 September 2008 Slide 28

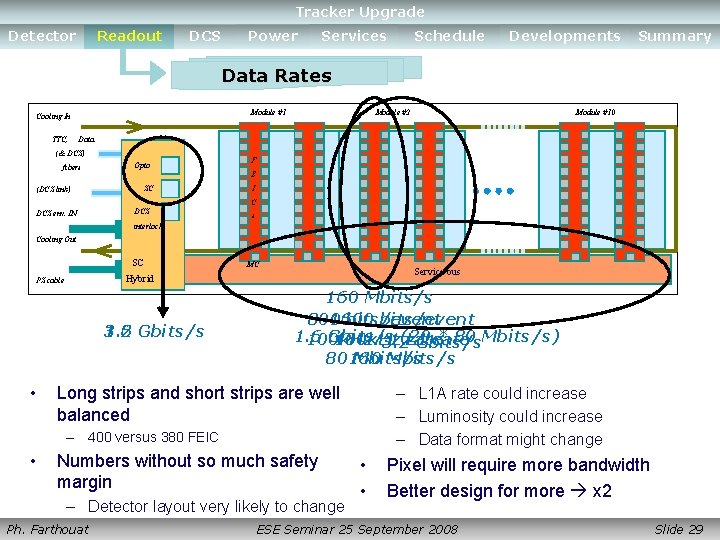

Detector Readout DCS Power. Tracker Services Upgrade Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Data Rates Module #1 Cooling In TTC, Module #2 Module #10 Data ( & DCS) fibers (DCS link) Opto F E SC I C DCS env. IN DCS s interlock Cooling Out SC Service bus Hybrid PS cable 3. 2 Gbits/s 1. 6 • MC 160 Mbits/s 800 1600 bits/event 1. 6 Gbits/s (20 * 80 Mbits/s) 100 k. Hz L 1 rate 3. 2 Gbits/s 80160 Mbits/s Long strips and short strips are well balanced – L 1 A rate could increase – Luminosity could increase – Data format might change – 400 versus 380 FEIC • Numbers without so much safety margin – Detector layout very likely to change Ph. Farthouat • • Pixel will require more bandwidth Better design for more x 2 ESE Seminar 25 September 2008 Slide 29

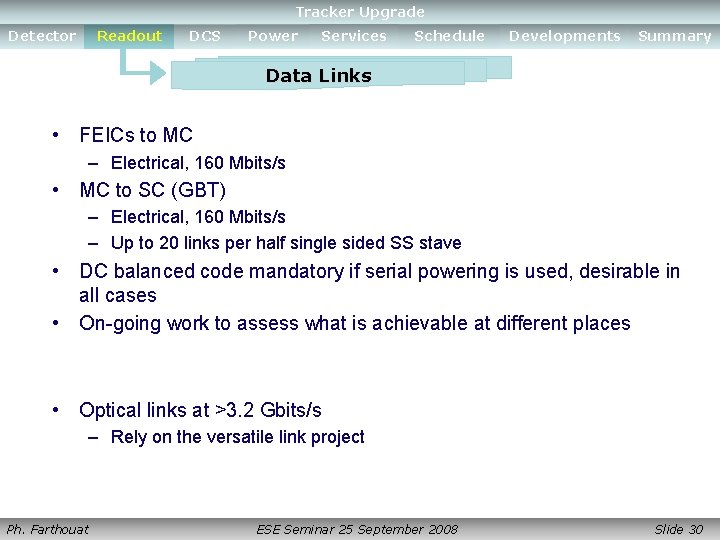

Detector Readout DCS Power. Tracker Services Upgrade Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Data Links • FEICs to MC – Electrical, 160 Mbits/s • MC to SC (GBT) – Electrical, 160 Mbits/s – Up to 20 links per half single sided SS stave • DC balanced code mandatory if serial powering is used, desirable in all cases • On-going work to assess what is achievable at different places • Optical links at >3. 2 Gbits/s – Rely on the versatile link project Ph. Farthouat ESE Seminar 25 September 2008 Slide 30

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary TTC Links • The TTC links are used to transmit to the front-end: – A clock synchronised with the beam (either the LHC clock or a multiple of it) – The L 1 A – Synchronous commands such as the bunch counter reset (BCR) or the event counter reset (ECR) – Control data to be stored in the FEICs, MCs and SMCs (e. g. threshold, masks, …) • Unidirectional links to minimise the number of lines – To read a register, command transmitted on TTC link, data transmitted on the read-out data link • TTC links bandwidth dictated by : – Clock frequency to be transmitted • Might be better to transmit a clock at higher frequency than the BC to be used directly by the readout logic (e. g. 160 Mhz if reading out at 160 Mbits/s. Avoid some PLL) – Necessity to transmit simultaneously the L 1 A and commands (e. g. Bunch Counter Reset) – Need forward error correction to fight SEUs – Need for DC balanced codes and self clock recovery protocols • Bandwidth greater than or equal to 80 Mbits/s Ph. Farthouat ESE Seminar 25 September 2008 Slide 31

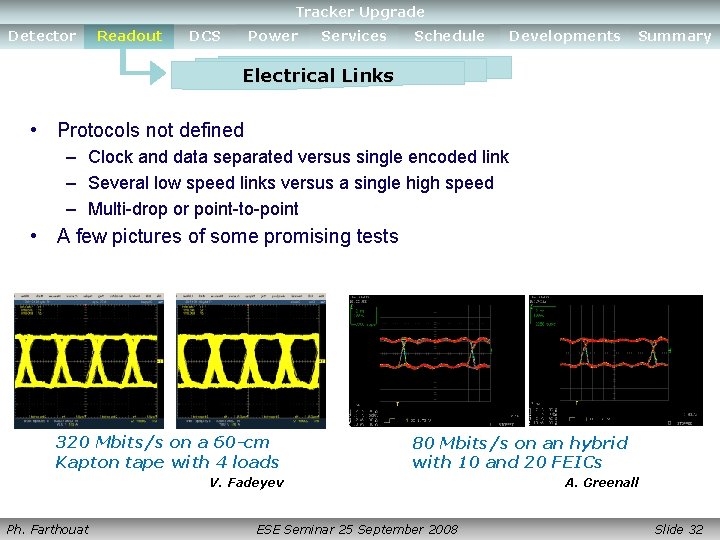

Detector Readout DCS Power. Tracker Services Upgrade Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Electrical Links • Protocols not defined – Clock and data separated versus single encoded link – Several low speed links versus a single high speed – Multi-drop or point-to-point • A few pictures of some promising tests 320 Mbits/s on a 60 -cm Kapton tape with 4 loads 80 Mbits/s on an hybrid with 10 and 20 FEICs V. Fadeyev Ph. Farthouat ESE Seminar 25 September 2008 A. Greenall Slide 32

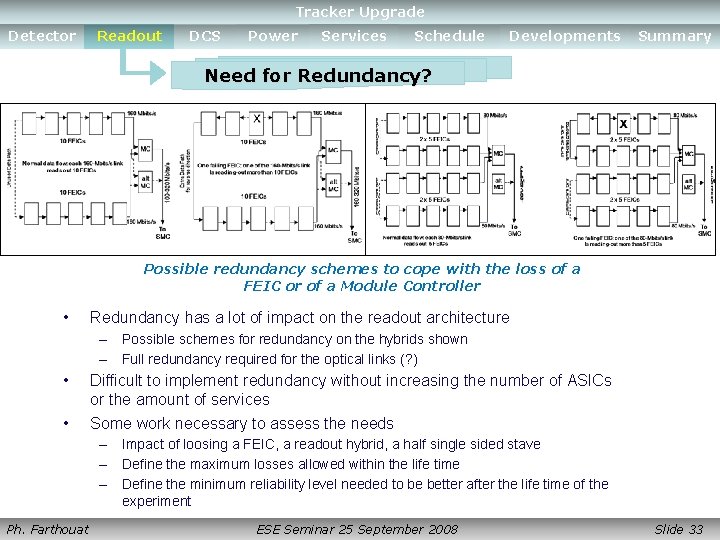

Detector Readout DCS Power. Tracker Services Upgrade Schedule Developments Summary Detector Readout DCS Power Developments Summary Services Schedule Need for Redundancy? Possible redundancy schemes to cope with the loss of a FEIC or of a Module Controller • Redundancy has a lot of impact on the readout architecture – Possible schemes for redundancy on the hybrids shown – Full redundancy required for the optical links (? ) • • Difficult to implement redundancy without increasing the number of ASICs or the amount of services Some work necessary to assess the needs – Impact of loosing a FEIC, a readout hybrid, a half single sided stave – Define the maximum losses allowed within the life time – Define the minimum reliability level needed to be better after the life time of the experiment Ph. Farthouat ESE Seminar 25 September 2008 Slide 33

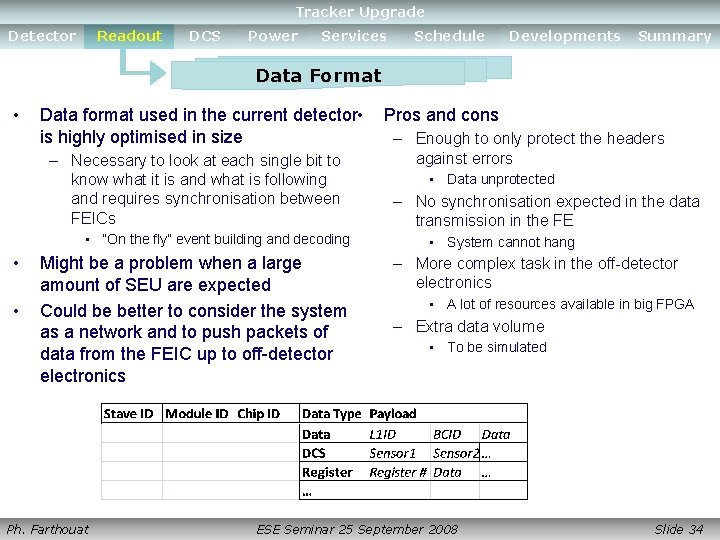

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Data Format • Data format used in the current detector • is highly optimised in size – Necessary to look at each single bit to know what it is and what is following and requires synchronisation between FEICs • “On the fly” event building and decoding • • Might be a problem when a large amount of SEU are expected Could be better to consider the system as a network and to push packets of data from the FEIC up to off-detector electronics Ph. Farthouat Pros and cons – Enough to only protect the headers against errors • Data unprotected – No synchronisation expected in the data transmission in the FE • System cannot hang – More complex task in the off-detector electronics • A lot of resources available in big FPGA – Extra data volume • To be simulated ESE Seminar 25 September 2008 Slide 34

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Integrated with the readout or separated? • In the current detector, a lot of direct connections of sensors – Not applicable for the upgrade • A lot of discussions concerning the need for a fully separated DCS system – Separately powered and separate communications – Separate ASICs – Additional services…. • Still possible to run safely the detector even with the DCS integrated in the readout Ph. Farthouat ESE Seminar 25 September 2008 Slide 35

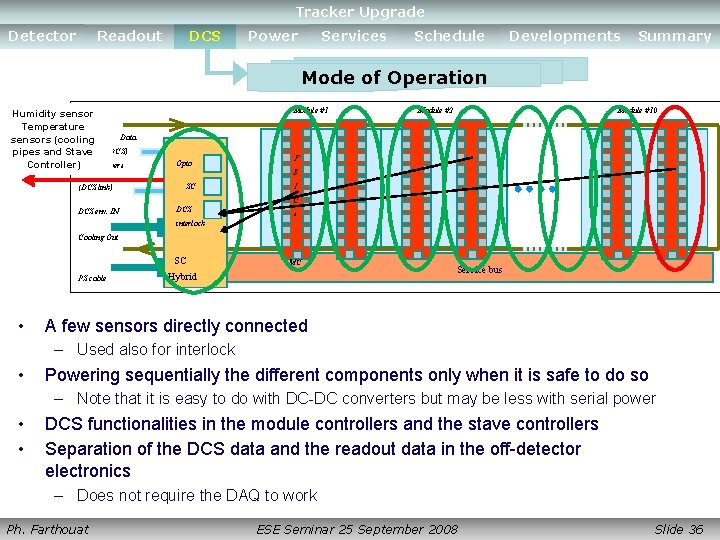

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Mode of Operation Cooling In Humidity sensor Temperature sensors (cooling. TTC, Data pipes and Stave ( & DCS) Controller) fibers (DCS link) Module #1 Opto Module #2 Module #10 F E SC I C DCS env. IN DCS s interlock Cooling Out SC PS cable • MC Hybrid Service bus A few sensors directly connected – Used also for interlock • Powering sequentially the different components only when it is safe to do so – Note that it is easy to do with DC-DC converters but may be less with serial power • • DCS functionalities in the module controllers and the stave controllers Separation of the DCS data and the readout data in the off-detector electronics – Does not require the DAQ to work Ph. Farthouat ESE Seminar 25 September 2008 Slide 36

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Total Power for the Strips • Assumptions: – Pessimistic 1. 5 m. W [1 m. W] per channel for the strip FEIC and 1. 3 V Vdd – 150 m. A [100 m. A] per 128 -channel FEIC. • Total current (for the barrel and both end-caps): 48. 5 k. A [33 k. A] • 80% efficiency of front-end power devices would lead to 78. 5 k. W [52 k. W] dissipated in the tracker volume – 70% efficiency would lead to 90 k. W [60 k. W] • Current SCT and TRT detectors are fed with about 12 k. A • Assuming the amount of services cannot be increased, the powering scheme to be used must limit the amount of current to be fed at that level – That’s about 1/6 th (1/5 th) of the current needed by the front-end electronics. Hence either a factor 5 to 6 (at least) DC-DC conversion or a serial powering scheme of at least 5 to 6 modules has to be used. Ph. Farthouat ESE Seminar 25 September 2008 Slide 37

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary DC-DC or Serial Power • Developments are on-going: serial powering and DC-DC conversion – Cf last ESE seminar (Federicco) and the presentations during TWEPP 08 • Reducing the current to be fed by a factor of 5 -to-10 minimum is reachable with both solutions • DC-DC converters offer some interesting flexibility – Can separate different supplies easily • Analog – digital saving in overall power • Stave controller, module controller and FEICs capability of controlling the operation – Radiation hardness not solved • Serial powering scheme has some system issues which are being tackled • Options to be kept opened for a while • Real estate is an important issue for both solutions Ph. Farthouat ESE Seminar 25 September 2008 Slide 38

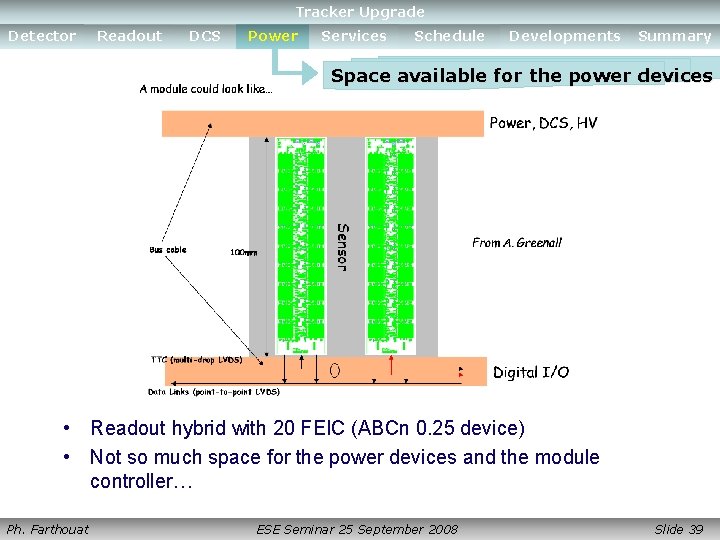

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Space available for the power devices • Readout hybrid with 20 FEIC (ABCn 0. 25 device) • Not so much space for the power devices and the module controller… Ph. Farthouat ESE Seminar 25 September 2008 Slide 39

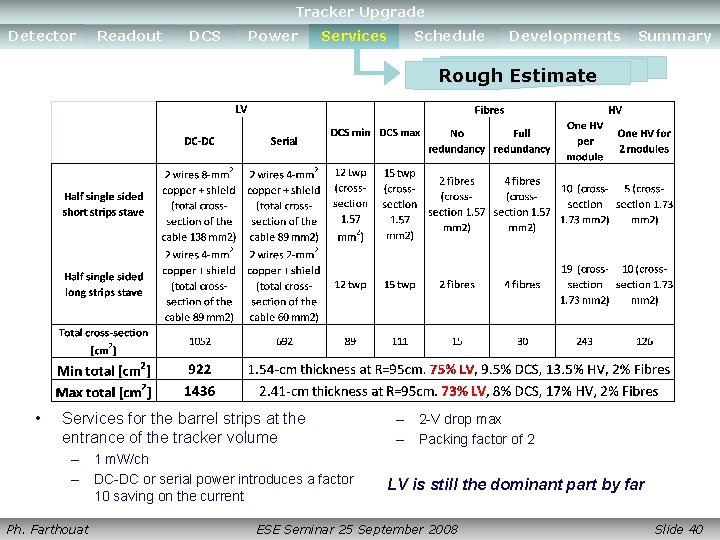

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Rough Estimate • Services for the barrel strips at the entrance of the tracker volume – 1 m. W/ch – DC-DC or serial power introduces a factor 10 saving on the current Ph. Farthouat – 2 -V drop max – Packing factor of 2 LV is still the dominant part by far ESE Seminar 25 September 2008 Slide 40

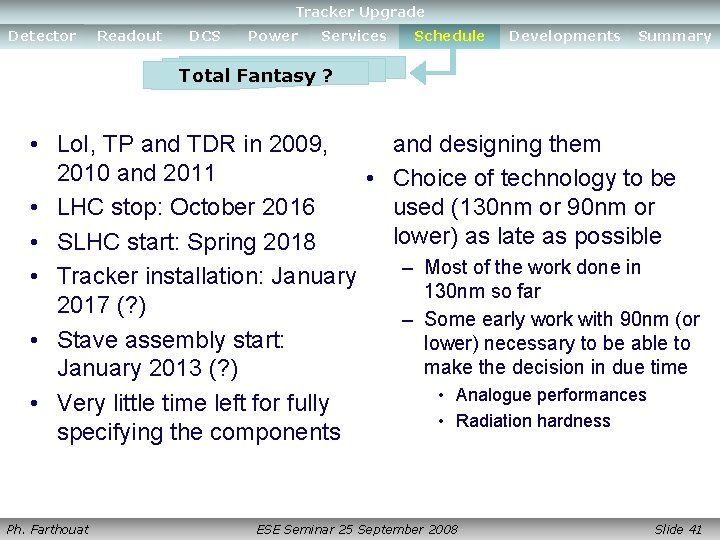

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Total Fantasy ? • Lo. I, TP and TDR in 2009, and designing them 2010 and 2011 • Choice of technology to be • LHC stop: October 2016 used (130 nm or 90 nm or lower) as late as possible • SLHC start: Spring 2018 – Most of the work done in • Tracker installation: January 130 nm so far 2017 (? ) – Some early work with 90 nm (or • Stave assembly start: lower) necessary to be able to make the decision in due time January 2013 (? ) • Analogue performances • Very little time left for fully • Radiation hardness specifying the components Ph. Farthouat ESE Seminar 25 September 2008 Slide 41

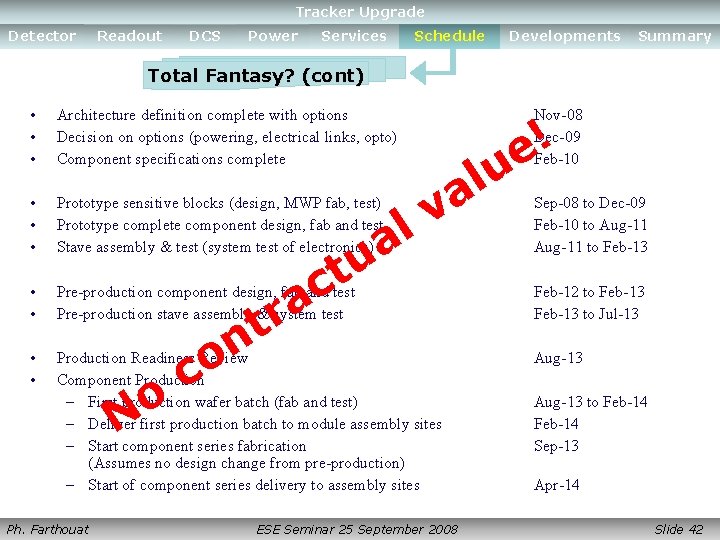

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Total Fantasy? (cont) • • • Architecture definition complete with options Decision on options (powering, electrical links, opto) Component specifications complete • • • Prototype sensitive blocks (design, MWP fab, test) Prototype complete component design, fab and test Stave assembly & test (system test of electronics) • • Pre-production component design, fab and test Pre-production stave assembly & system test • • Production Readiness Review Component Production – First production wafer batch (fab and test) – Deliver first production batch to module assembly sites – Start component series fabrication (Assumes no design change from pre-production) – Start of component series delivery to assembly sites t c Ph. Farthouat o N c n o a r t l a v l a u ESE Seminar 25 September 2008 Nov-08 Dec-09 Feb-10 ! e u Sep-08 to Dec-09 Feb-10 to Aug-11 to Feb-13 Feb-12 to Feb-13 to Jul-13 Aug-13 to Feb-14 Sep-13 Apr-14 Slide 42

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary ASICs developments and specifications • Working document on architecture available since about a year – Reviewed and presented to the collaboration • Two working groups in place to try and define more precisely the specifications of the different components. One for the pixels and one for the strips – Inputs to the “common projects” teams (e. g. GBT) – ~350 k FEIC but only ~20 k MC and ~5 k SC(GBT) • ABCn 0. 25 chip as test vehicule for sensor studies – Also contains some features for testing different power schemes and readout speeds • Preliminary study of the front-end part (preamplifier-shaperdiscriminator) in 0. 13 – Very good power performances: <200µW per channel – See J. Kaplon’s presentation during the TWEPP workshop • Evaluation of Si. Ge Ph. Farthouat ESE Seminar 25 September 2008 Slide 43

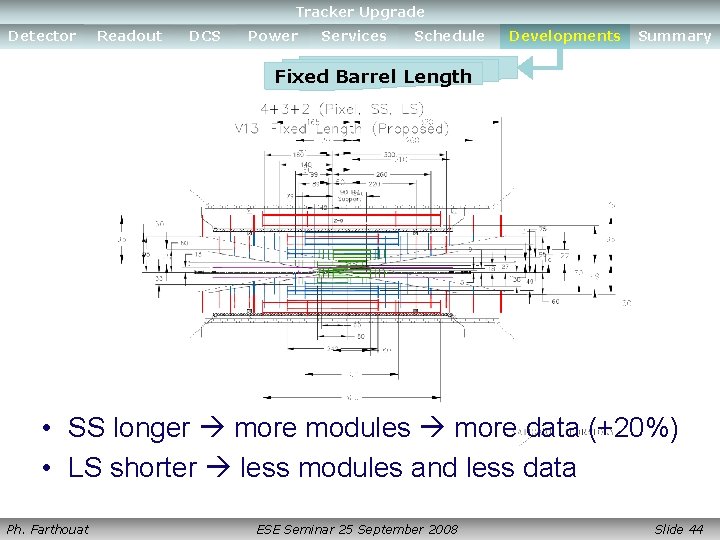

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary Fixed Barrel Length • SS longer more modules more data (+20%) • LS shorter less modules and less data Ph. Farthouat ESE Seminar 25 September 2008 Slide 44

Tracker Upgrade Detector Readout DCS Power Services Schedule Developments Summary • The readout architecture of the ATLAS upgraded tracker has to be different from the current one • Detector organised in staves. Hierarchical readout following this segmentation – Fewer but higher speed links • Some elements of the readout are not to be produced in very high quantity – Points towards common solutions with CMS and others • Power distribution requires special efforts to maintain reasonable services – Saving factor 5 - 10 on the current • Schedule looks uneasy – Not so much time for the electronics development – Decision on technology to be used for the FE electronics at the latest in 2012 Ph. Farthouat ESE Seminar 25 September 2008 Slide 45

Upgrade Organisation • Two major coordination bodies CERN Involvement • – Develop a realistic and coherent upgrade plan – Steer R&D activities – Cover engineering aspects from the beginning • Upgrade Steering Group (USG) – Representatives from systems, software, • physics and technical coordination Project Office – Part of the technical coordination – Project Office should technically guide the upgrade activities • Conceptual design and R&D • Prototyping • Pre-series and construction • Installation and commissioning Upgrade addressed during each ATLAS overview week and during dedicated workshops – Several devoted to the tracker Ref: https: //edms. cern. ch/file/690177/1/Upgrade_Org_PO. doc Indico pages: http: //indico. cern. ch/category. Display. py? categ. Id=350 Ph. Farthouat ESE Seminar 25 September 2008 Slide 46

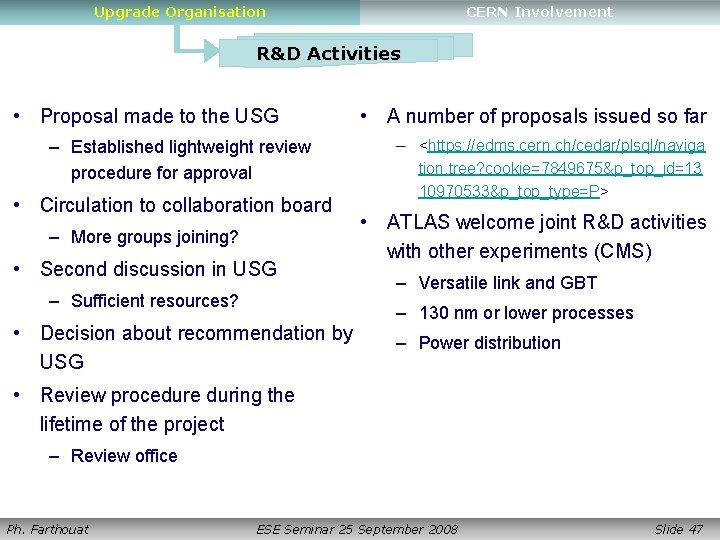

Upgrade Organisation CERN Involvement R&D Activities • Proposal made to the USG – Established lightweight review procedure for approval • Circulation to collaboration board – More groups joining? • Second discussion in USG – Sufficient resources? • Decision about recommendation by USG • A number of proposals issued so far – <https: //edms. cern. ch/cedar/plsql/naviga tion. tree? cookie=7849675&p_top_id=13 10970533&p_top_type=P> • ATLAS welcome joint R&D activities with other experiments (CMS) – Versatile link and GBT – 130 nm or lower processes – Power distribution • Review procedure during the lifetime of the project – Review office Ph. Farthouat ESE Seminar 25 September 2008 Slide 47

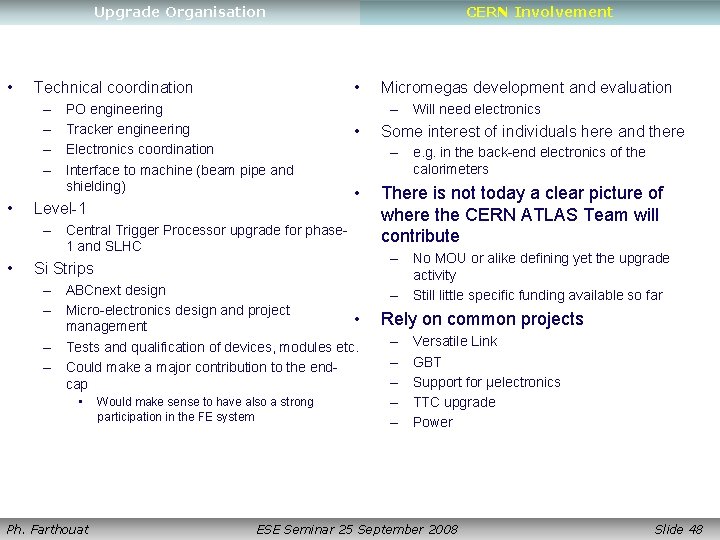

Upgrade Organisation • • • Technical coordination – – CERN Involvement PO engineering Tracker engineering Electronics coordination Interface to machine (beam pipe and shielding) Level-1 – Will need electronics • • Si Strips – ABCnext design – Micro-electronics design and project • management – Tests and qualification of devices, modules etc. – Could make a major contribution to the endcap • Ph. Farthouat Would make sense to have also a strong participation in the FE system Some interest of individuals here and there – e. g. in the back-end electronics of the calorimeters – Central Trigger Processor upgrade for phase 1 and SLHC • Micromegas development and evaluation There is not today a clear picture of where the CERN ATLAS Team will contribute – No MOU or alike defining yet the upgrade activity – Still little specific funding available so far Rely on common projects – – – Versatile Link GBT Support for µelectronics TTC upgrade Power ESE Seminar 25 September 2008 Slide 48

- Slides: 48