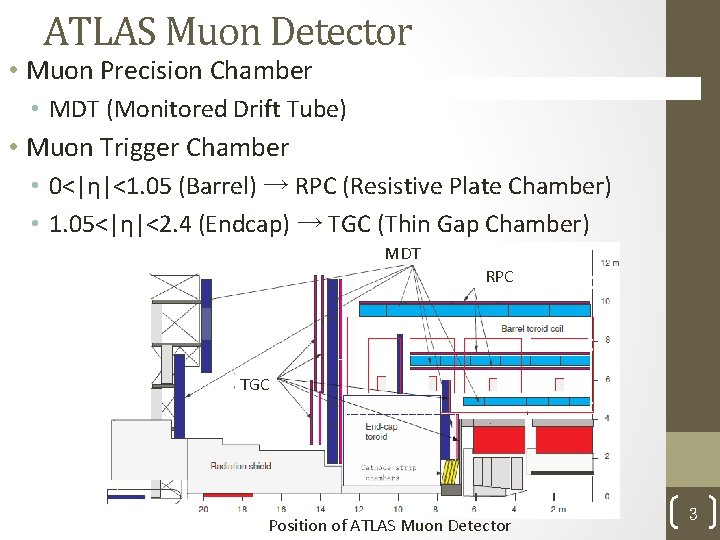

ATLAS Muon Detector Muon Precision Chamber MDT Monitored

ATLAS Muon Detector • Muon Precision Chamber • MDT (Monitored Drift Tube) • Muon Trigger Chamber • 0<|η|<1. 05 (Barrel) → RPC (Resistive Plate Chamber) • 1. 05<|η|<2. 4 (Endcap) → TGC (Thin Gap Chamber) MDT RPC TGC Position of ATLAS Muon Detector 3

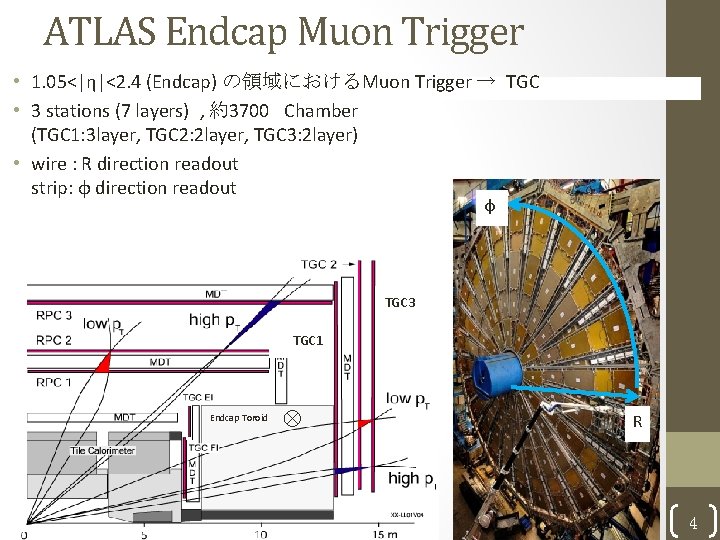

ATLAS Endcap Muon Trigger • 1. 05<|η|<2. 4 (Endcap) の領域におけるMuon Trigger → TGC • 3 stations (7 layers) , 約3700 Chamber (TGC 1: 3 layer, TGC 2: 2 layer, TGC 3: 2 layer) • wire : R direction readout strip: φ direction readout φ TGC 3 TGC 1 Endcap Toroid R 4

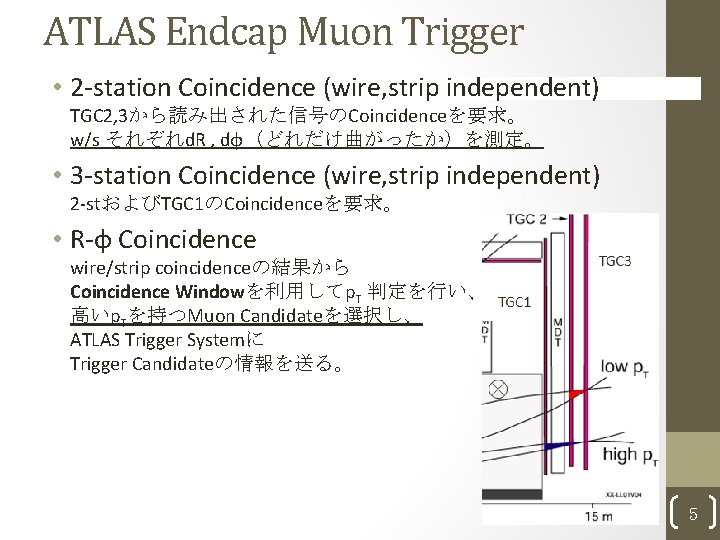

ATLAS Endcap Muon Trigger • 2 -station Coincidence (wire, strip independent) TGC 2, 3から読み出された信号のCoincidenceを要求。 w/s それぞれd. R , dφ(どれだけ曲がったか)を測定。 • 3 -station Coincidence (wire, strip independent) 2 -stおよびTGC 1のCoincidenceを要求。 • R-φ Coincidence wire/strip coincidenceの結果から Coincidence Windowを利用してp. T 判定を行い、 高いp. Tを持つMuon Candidateを選択し、 ATLAS Trigger Systemに Trigger Candidateの情報を送る。 5

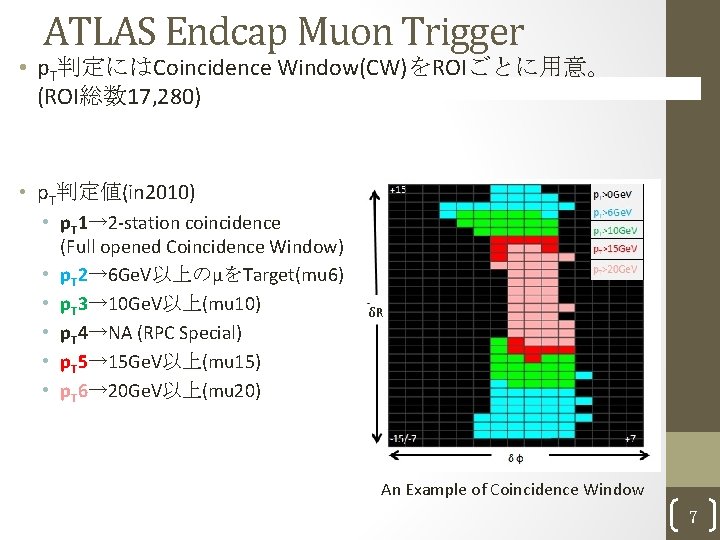

ATLAS Endcap Muon Trigger • p. T判定にはCoincidence Window(CW)をROIごとに用意。 (ROI総数 17, 280) • p. T判定値(in 2010) • p. T 1→ 2 -station coincidence (Full opened Coincidence Window) • p. T 2→ 6 Ge. V以上のμをTarget(mu 6) • p. T 3→ 10 Ge. V以上(mu 10) • p. T 4→NA (RPC Special) • p. T 5→ 15 Ge. V以上(mu 15) • p. T 6→ 20 Ge. V以上(mu 20) δR An Example of Coincidence Window 7

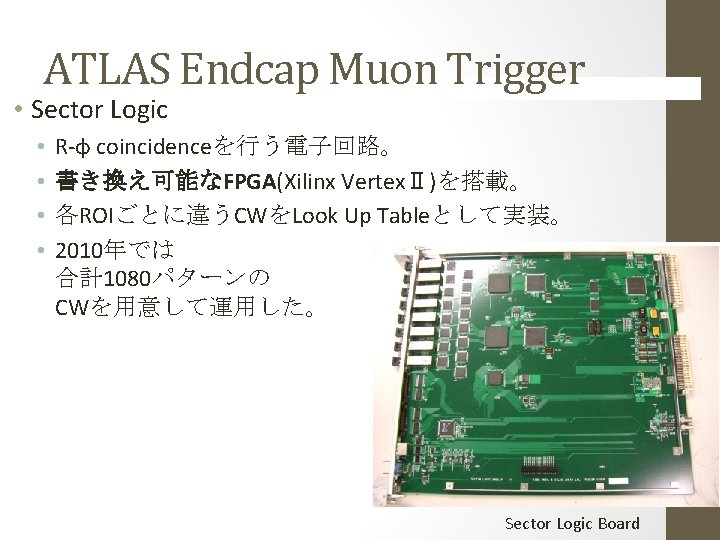

ATLAS Endcap Muon Trigger • Sector Logic • • R-φ coincidenceを行う電子回路。 書き換え可能なFPGA(Xilinx VertexⅡ)を搭載。 各ROIごとに違うCWをLook Up Tableとして実装。 2010年では 合計1080パターンの CWを用意して運用した。 8 Sector Logic Board

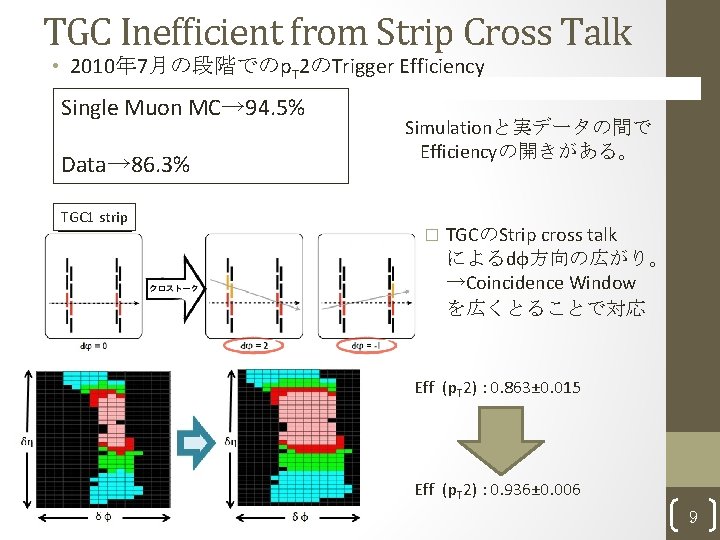

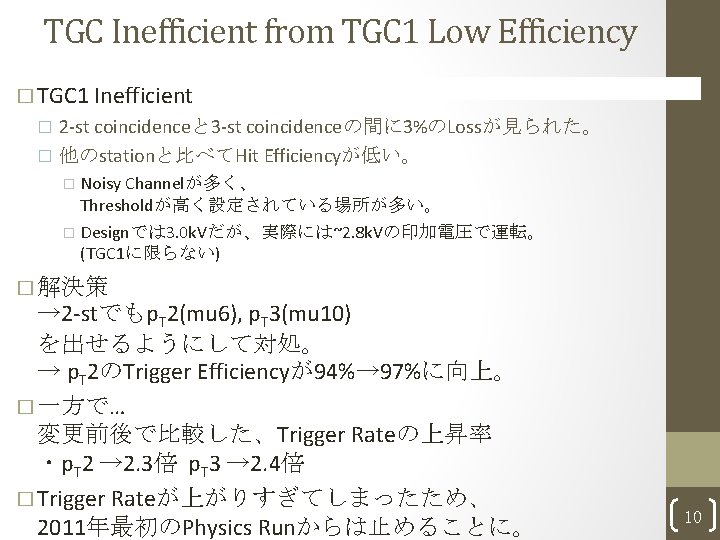

TGC Inefficient from Strip Cross Talk • 2010年 7月の段階でのp. T 2のTrigger Efficiency Single Muon MC→ 94. 5% Simulationと実データの間で Efficiencyの開きがある。 Data→ 86. 3% TGC 1 strip � TGCのStrip cross talk によるdφ方向の広がり。 →Coincidence Window を広くとることで対応 Eff (p. T 2) : 0. 863± 0. 015 Eff (p. T 2) : 0. 936± 0. 006 9

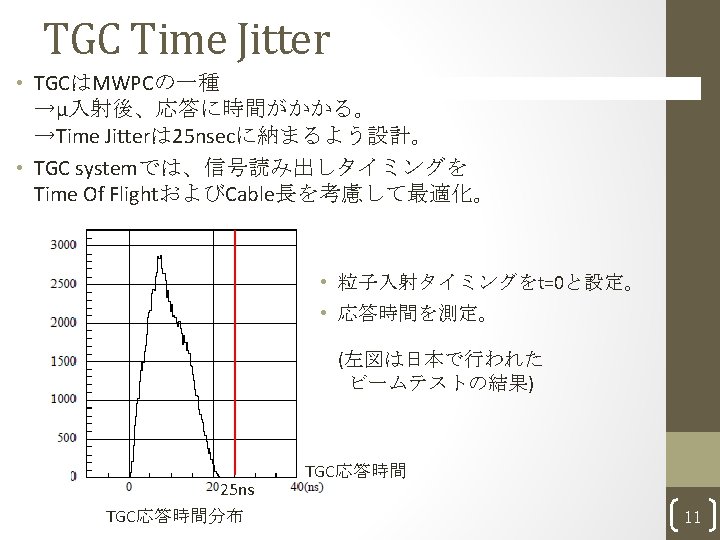

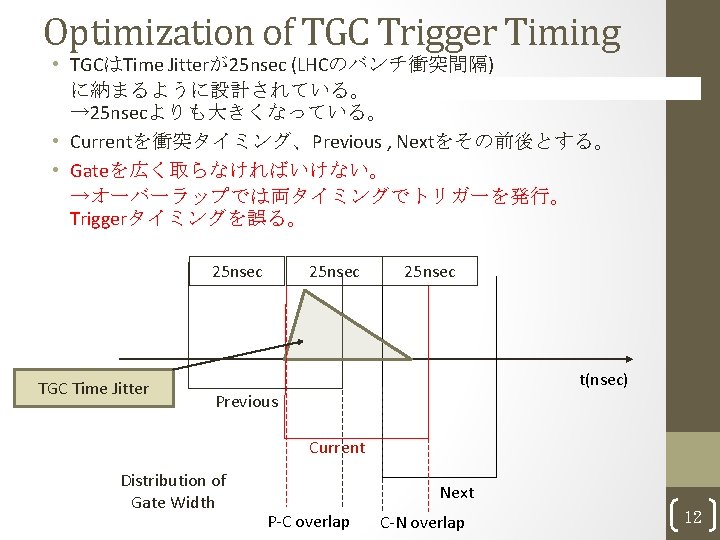

Optimization of TGC Trigger Timing • TGCはTime Jitterが25 nsec (LHCのバンチ衝突間隔) に納まるように設計されている。 → 25 nsecよりも大きくなっている。 • Currentを衝突タイミング、Previous , Nextをその前後とする。 • Gateを広く取らなければいけない。 →オーバーラップでは両タイミングでトリガーを発行。 Triggerタイミングを誤る。 25 nsec TGC Time Jitter 25 nsec t(nsec) Previous Current Distribution of Gate Width Next P-C overlap C-N overlap 12

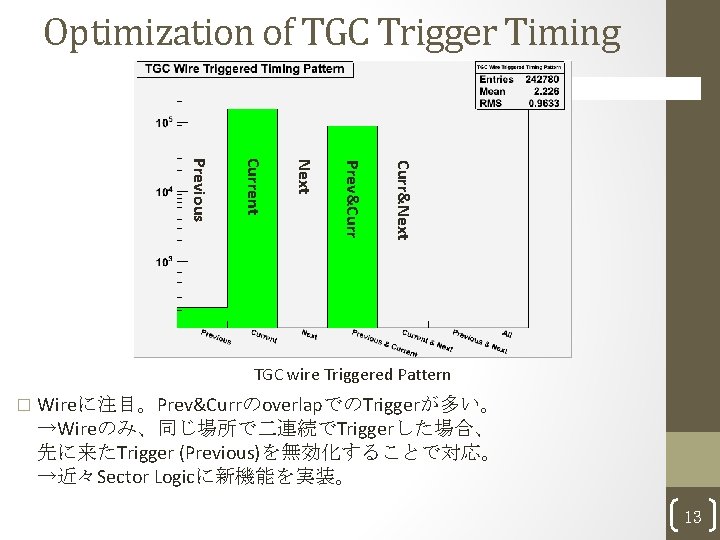

Optimization of TGC Trigger Timing Curr&Next Prev&Curr Next Current Previous TGC wire Triggered Pattern � Wireに注目。Prev&CurrのoverlapでのTriggerが多い。 →Wireのみ、同じ場所で二連続でTriggerした場合、 先に来たTrigger (Previous)を無効化することで対応。 →近々Sector Logicに新機能を実装。 13

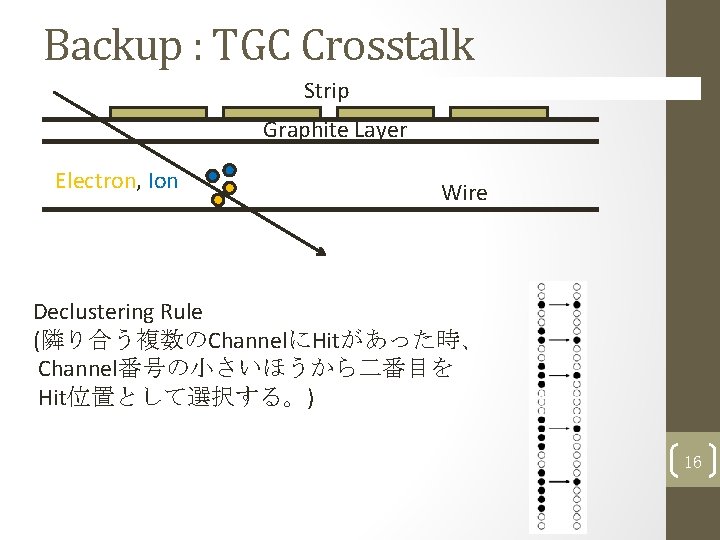

Backup : TGC Crosstalk Strip Graphite Layer Electron, Ion Wire Declustering Rule (隣り合う複数のChannelにHitがあった時、 Channel番号の小さいほうから二番目を Hit位置として選択する。) 16

- Slides: 16