ATLAS CMOS Pixel Program Marlon Barbero AMU CPPM

ATLAS CMOS Pixel Program Marlon Barbero – AMU / CPPM Aida-2020 workshop on HV/HR CMOS TCAD and Geant 4 simulations

Content • ITk phase II ATLAS program. – HL-LHC environment. – CMOS pixels in the ITk. • CMOS program. – Recent highlights (focus on demonstrator program). – Plans. • Conclusion. With material borrowed from AUW (19/04/2016), fully monolithic CMOS chip kickoff (09/05/2016), and more… ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 2

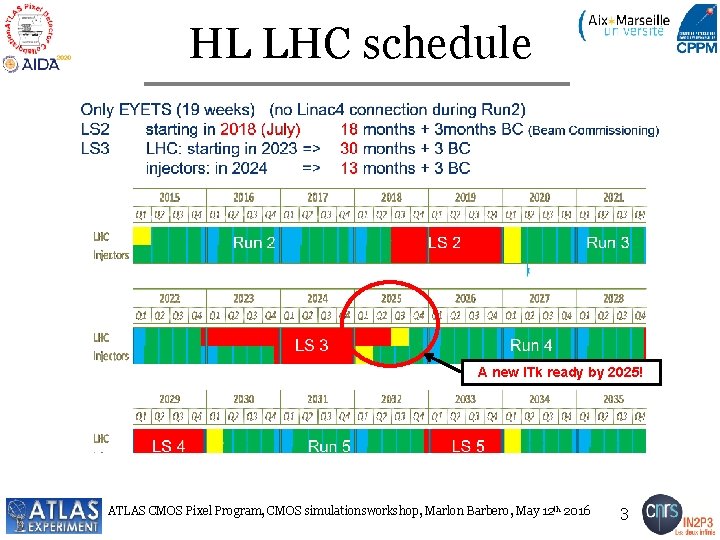

HL LHC schedule A new ITk ready by 2025! ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 3

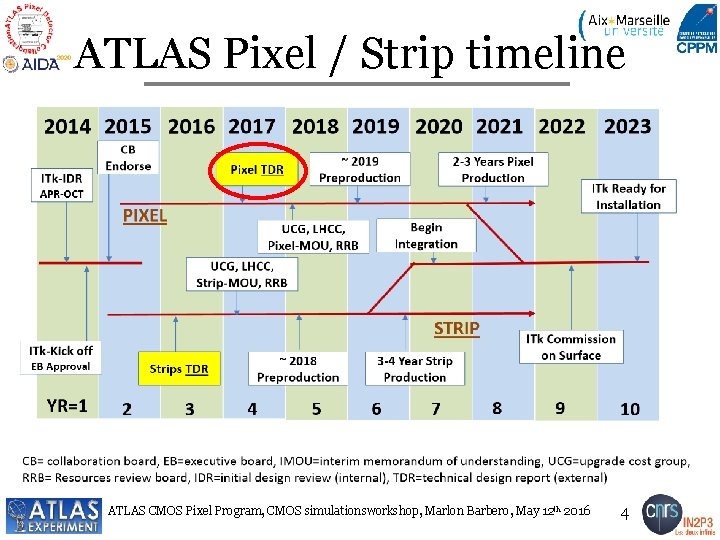

ATLAS Pixel / Strip timeline ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 4

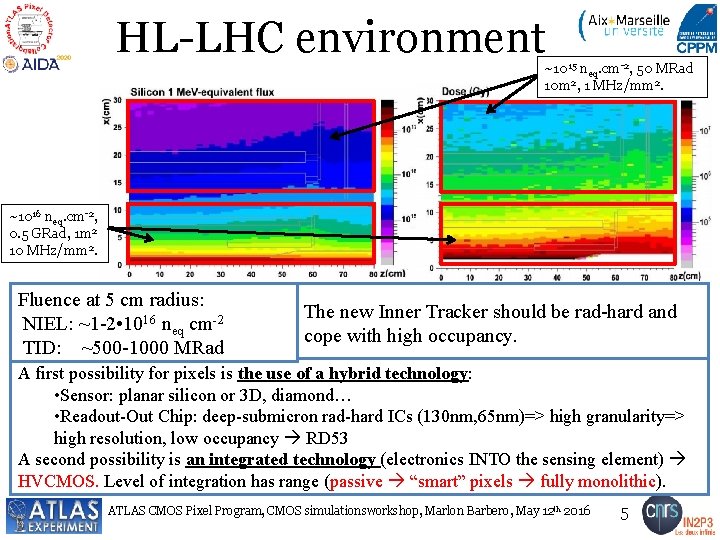

HL-LHC environment ~1015 neq. cm-2, 50 MRad 10 m 2, 1 MHz/mm 2. ~1016 neq. cm-2, 0. 5 GRad, 1 m 2 10 MHz/mm 2. Fluence at 5 cm radius: NIEL: ~1 -2 • 1016 neq cm-2 TID: ~500 -1000 MRad The new Inner Tracker should be rad-hard and cope with high occupancy. A first possibility for pixels is the use of a hybrid technology: • Sensor: planar silicon or 3 D, diamond… • Readout-Out Chip: deep-submicron rad-hard ICs (130 nm, 65 nm)=> high granularity=> high resolution, low occupancy RD 53 A second possibility is an integrated technology (electronics INTO the sensing element) HVCMOS. Level of integration has range (passive “smart” pixels fully monolithic). ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 5

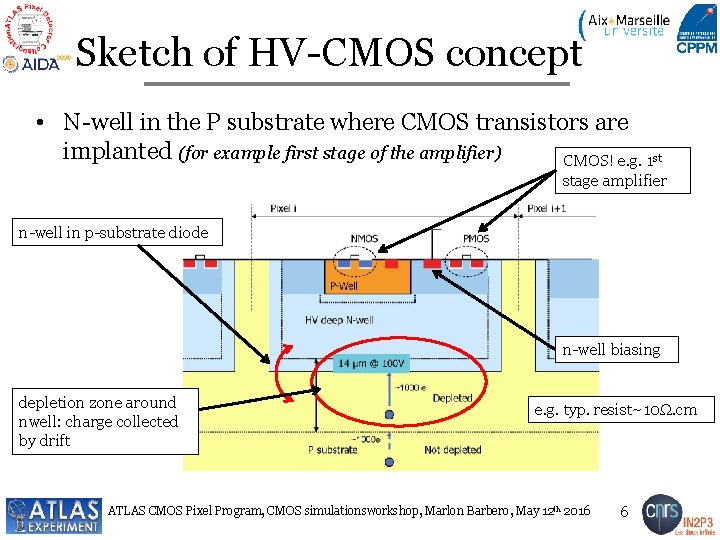

Sketch of HV-CMOS concept • N-well in the P substrate where CMOS transistors are implanted (for example first stage of the amplifier) CMOS! e. g. 1 st stage amplifier n-well in p-substrate diode n-well biasing depletion zone around nwell: charge collected by drift e. g. typ. resist~10Ω. cm ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 6

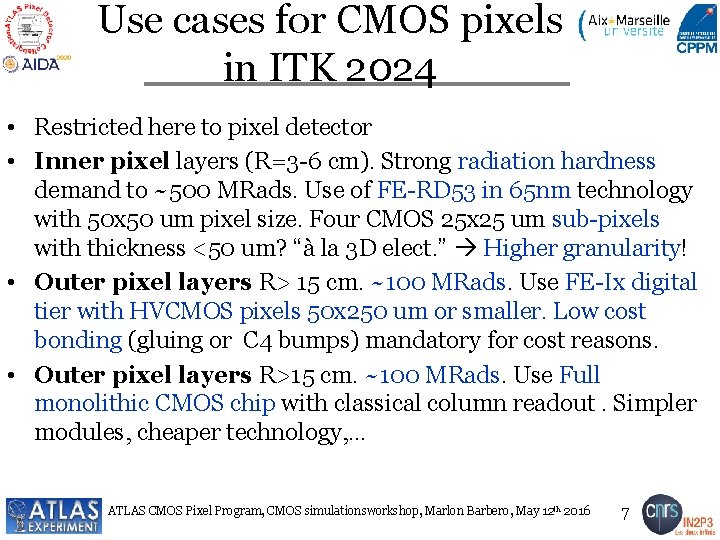

Use cases for CMOS pixels in ITK 2024 • Restricted here to pixel detector • Inner pixel layers (R=3 -6 cm). Strong radiation hardness demand to ~500 MRads. Use of FE-RD 53 in 65 nm technology with 50 x 50 um pixel size. Four CMOS 25 x 25 um sub-pixels with thickness <50 um? “à la 3 D elect. ” Higher granularity! • Outer pixel layers R> 15 cm. ~100 MRads. Use FE-Ix digital tier with HVCMOS pixels 50 x 250 um or smaller. Low cost bonding (gluing or C 4 bumps) mandatory for cost reasons. • Outer pixel layers R>15 cm. ~100 MRads. Use Full monolithic CMOS chip with classical column readout. Simpler modules, cheaper technology, … ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 7

Pixel and Strip CMOS RD • Weekly meeting organized from 08. 11. 2011. • Started as Bonn-Berkeley-CERN-CPPM-Geneva-Heidelberg collaboration. • CPIX Chairs S. Rozanov / N. Wermes. • Number of institutes currently involved: ~15 -20 + strips, Karlsruhe-Berkeley-Bonn-CERN-Geneva-Marseille-Gottingen -Prague-IRFU-Glasgow-Oxford-Liverpool-INFN-Genova. Milan-SLAC-UCSC-……. (sorry if I forget some here) (gaining momentum : Monday 9 th “Fully Monolithic CMOS Chip” kickoff meeting very well attended). • In this context: “CMOS demonstrator task force” end 2014 large size demonstrators. ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 8

Goals for pixels: 2015/6 • Large area demonstrator for 2015/6: HVHR-CMOS capacitively coupled to FE-I 4 B. Need to demonstrate: – – – – Operate 1× 1 or full size 2× 2 cm 2 demonstrator. Low noise (<1% pixels masked). MIP >99 % detection efficiency. Limited radiation hardness (~100 Mrad, ~10. 15 neq. cm-2). Glue coupling (but bump-bonding explored in //). Module: Wire-bonds. Granularity: conservative 50× 250 μm 2 or more aggressive 33× 125 μm 2. – Depleted zone of order 100 μm or less. ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 9

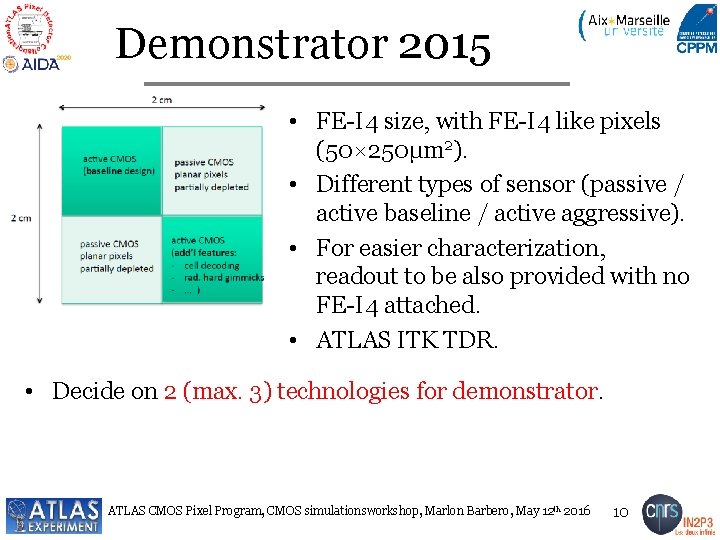

Demonstrator 2015 • FE-I 4 size, with FE-I 4 like pixels (50× 250μm 2). • Different types of sensor (passive / active baseline / active aggressive). • For easier characterization, readout to be also provided with no FE-I 4 attached. • ATLAS ITK TDR. • Decide on 2 (max. 3) technologies for demonstrator. ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 10

Demonstrator needed • Based on first prototypes. • Survey of available processes + TCAD simulations of CMOS sensors. • Signal and efficiency: High interest in HR processes. • Coupling: AC or DC. Investigate TSV (lower priority). • Irradiation: Electronics rad-hardness, charge collection efficiency Xrays / neutrons / protons. • Test system development. ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 11

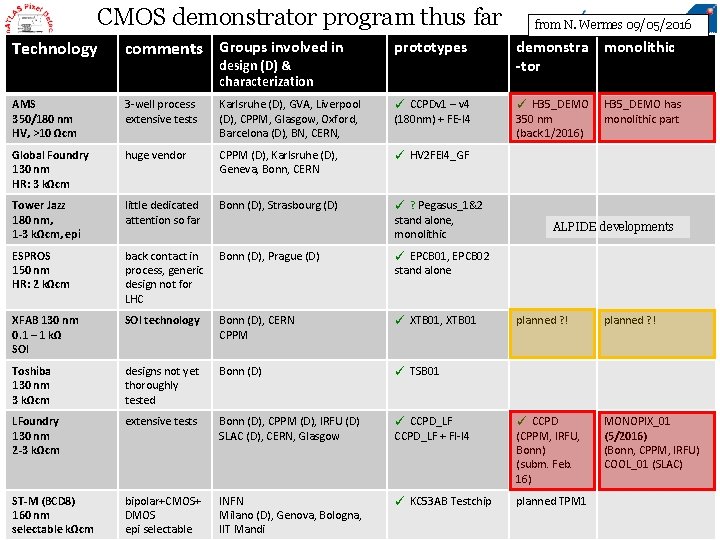

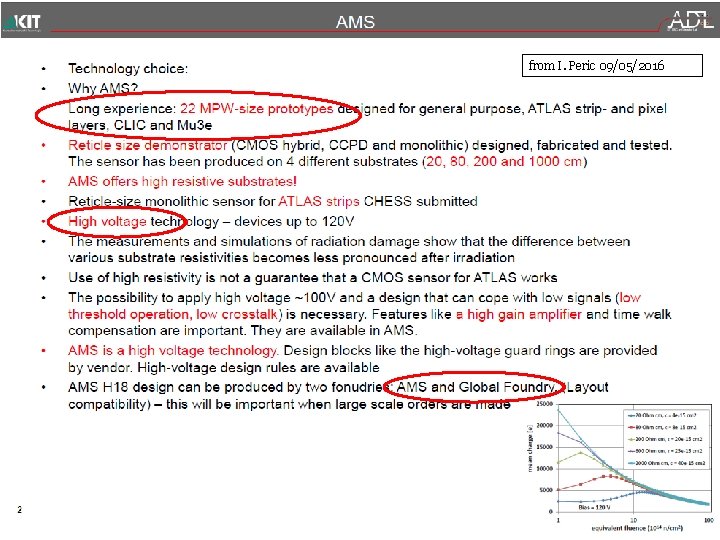

CMOS demonstrator program thus far from N. Wermes 09/05/2016 Technology comments Groups involved in prototypes demonstra monolithic -tor AMS 350/180 nm HV, >10 Ωcm 3 -well process extensive tests Karlsruhe (D), GVA, Liverpool (D), CPPM, Glasgow, Oxford, Barcelona (D), BN, CERN, ✓ CCPDv 1 – v 4 (180 nm) + FE-I 4 ✓ H 35_DEMO 350 nm (back 1/2016) Global Foundry 130 nm HR: 3 kΩcm huge vendor CPPM (D), Karlsruhe (D), Geneva, Bonn, CERN ✓ HV 2 FEI 4_GF Tower Jazz 180 nm, 1 -3 kΩcm, epi little dedicated attention so far Bonn (D), Strasbourg (D) ✓ ? Pegasus_1&2 stand alone, monolithic ESPROS 150 nm HR: 2 kΩcm back contact in process, generic design not for LHC Bonn (D), Prague (D) ✓ EPCB 01, EPCB 02 stand alone XFAB 130 nm 0. 1 – 1 kΩ SOI technology Bonn (D), CERN CPPM ✓ XTB 01, XTB 01 Toshiba 130 nm 3 kΩcm designs not yet thoroughly tested Bonn (D) ✓ TSB 01 LFoundry 130 nm 2 -3 kΩcm extensive tests Bonn (D), CPPM (D), IRFU (D) SLAC (D), CERN, Glasgow ST-M (BCD 8) 160 nm selectable kΩcm bipolar+CMOS+ DMOS epi selectable INFN Milano (D), Genova, Bologna, IIT Mandi design (D) & characterization H 35_DEMO has monolithic part ALPIDE developments planned ? ! ✓ CCPD_LF + FI-I 4 ✓ CCPD (CPPM, IRFU, Bonn) (subm. Feb. 16) MONOPIX_01 (5/2016) (Bonn, CPPM, IRFU) COOL_01 (SLAC) ✓ KC 53 AB Testchip planned TPM 1

AMS Demo ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 13

from I. Peric 09/05/2016

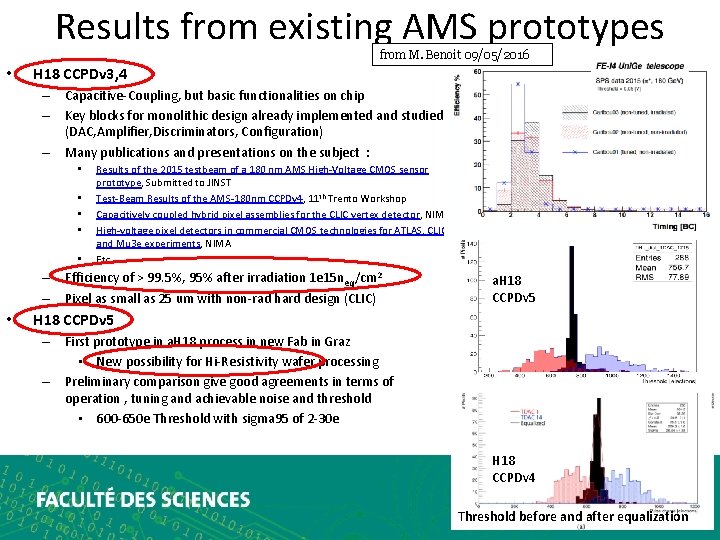

Results from existing AMS prototypes from M. Benoit 09/05/2016 • H 18 CCPDv 3, 4 – Capacitive-Coupling, but basic functionalities on chip – Key blocks for monolithic design already implemented and studied (DAC, Amplifier, Discriminators, Configuration) – Many publications and presentations on the subject : • • • Results of the 2015 testbeam of a 180 nm AMS High-Voltage CMOS sensor prototype, Submitted to JINST Test-Beam Results of the AMS-180 nm CCPDv 4, 11 th Trento Workshop Capacitively coupled hybrid pixel assemblies for the CLIC vertex detector, NIMA High-voltage pixel detectors in commercial CMOS technologies for ATLAS, CLIC and Mu 3 e experiments, NIMA Etc. – Efficiency of > 99. 5%, 95% after irradiation 1 e 15 neq/cm 2 – Pixel as small as 25 um with non-rad hard design (CLIC) • a. H 18 CCPDv 5 – First prototype in a. H 18 process in new Fab in Graz • New possibility for Hi-Resistivity wafer processing – Preliminary comparison give good agreements in terms of operation , tuning and achievable noise and threshold • 600 -650 e Threshold with sigma 95 of 2 -30 e H 18 CCPDv 4 Threshold before and after equalization

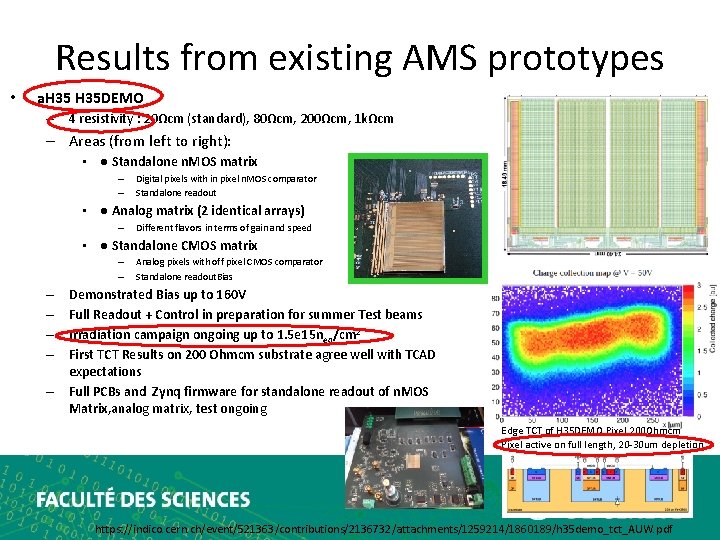

Results from existing AMS prototypes • a. H 35 DEMO – 4 resistivity : 20Ωcm (standard), 80Ωcm, 200Ωcm, 1 kΩcm – Areas (from left to right): • ● Standalone n. MOS matrix – – Digital pixels with in pixel n. MOS comparator Standalone readout • ● Analog matrix (2 identical arrays) – Different flavors in terms of gain and speed • ● Standalone CMOS matrix – – – – Analog pixels with off pixel CMOS comparator Standalone readout. Bias Demonstrated Bias up to 160 V Full Readout + Control in preparation for summer Test beams Irradiation campaign ongoing up to 1. 5 e 15 neq/cm 2 First TCT Results on 200 Ohmcm substrate agree well with TCAD expectations Full PCBs and Zynq firmware for standalone readout of n. MOS Matrix, analog matrix, test ongoing Edge TCT of H 35 DEMO Pixel 200 Ohmcm Pixel active on full length, 20 -30 um depletion https: //indico. cern. ch/event/521363/contributions/2136732/attachments/1259214/1860189/h 35 demo_tct_AUW. pdf

LF Demo ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 18

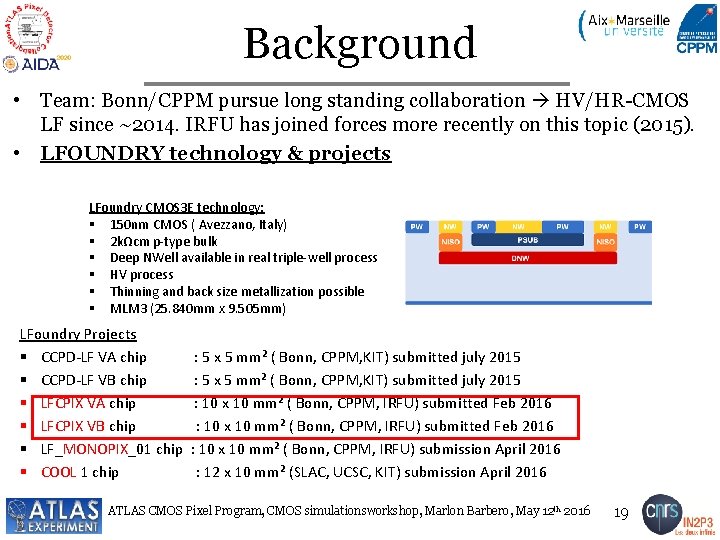

Background • Team: Bonn/CPPM pursue long standing collaboration HV/HR-CMOS LF since ~2014. IRFU has joined forces more recently on this topic (2015). • LFOUNDRY technology & projects LFoundry CMOS 3 E technology: § 150 nm CMOS ( Avezzano, Italy) § 2 kΩcm p-type bulk § Deep NWell available in real triple-well process § HV process § Thinning and back size metallization possible § MLM 3 (25. 840 mm x 9. 505 mm) LFoundry Projects § CCPD-LF VA chip § CCPD-LF VB chip § LFCPIX VA chip § LFCPIX VB chip § LF_MONOPIX_01 chip § COOL 1 chip : 5 x 5 mm² ( Bonn, CPPM, KIT) submitted july 2015 : 10 x 10 mm² ( Bonn, CPPM, IRFU) submitted Feb 2016 : 10 x 10 mm² ( Bonn, CPPM, IRFU) submission April 2016 : 12 x 10 mm² (SLAC, UCSC, KIT) submission April 2016 ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 19

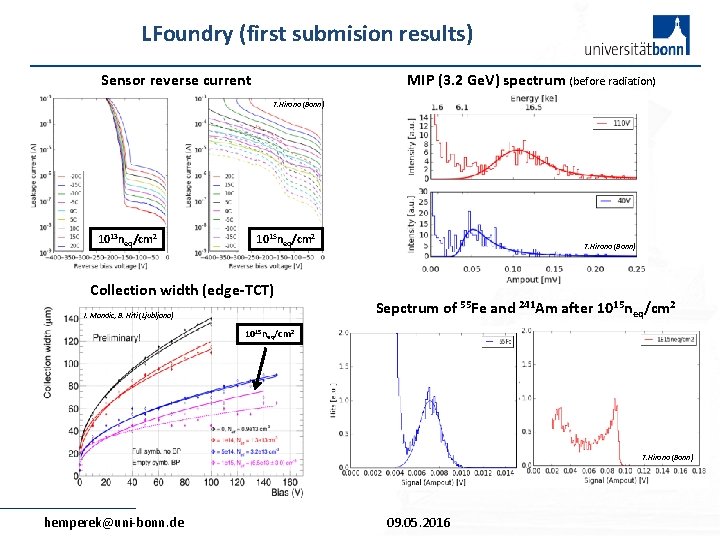

LFoundry (first submision results) Sensor reverse current MIP (3. 2 Ge. V) spectrum (before radiation) T. Hirono (Bonn) 1013 neq/cm 2 1015 neq/cm 2 Collection width (edge-TCT) I. Mandic, B. Hiti (Ljubljana) T. Hirono (Bonn) Sepctrum of 55 Fe and 241 Am after 1015 neq/cm 2 T. Hirono (Bonn) hemperek@uni-bonn. de 09. 05. 2016

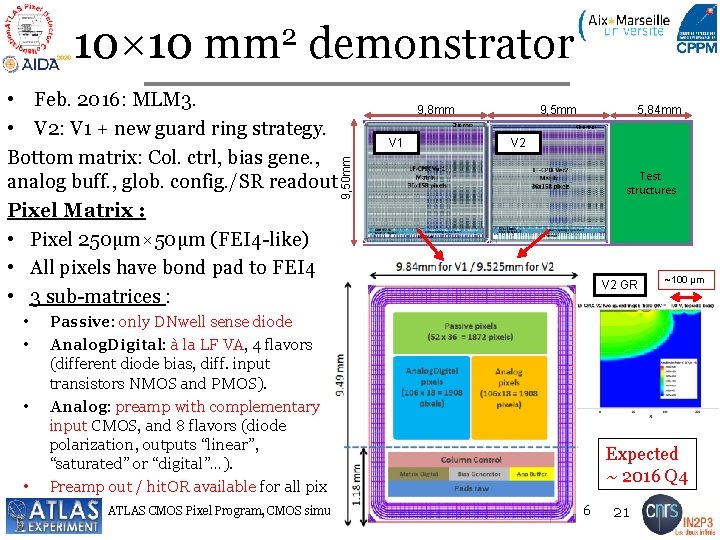

10× 10 mm 2 demonstrator • • 9, 8 mm V 1 9, 50 mm • Feb. 2016: MLM 3. • V 2: V 1 + new guard ring strategy. Bottom matrix: Col. ctrl, bias gene. , analog buff. , glob. config. /SR readout Pixel Matrix : • Pixel 250µm× 50µm (FEI 4 -like) • All pixels have bond pad to FEI 4 • 3 sub-matrices : SEAT 1 9, 5 mm 5, 84 mm V 2 SEAT 2 Passive: only DNwell sense diode Analog. Digital: à la LF VA, 4 flavors (different diode bias, diff. input transistors NMOS and PMOS). Analog: preamp with complementary input CMOS, and 8 flavors (diode polarization, outputs “linear”, “saturated” or “digital”…). Preamp out / hit. OR available for all pix! ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 Test structures V 2 GR ~100 μm Expected ~ 2016 Q 4 21

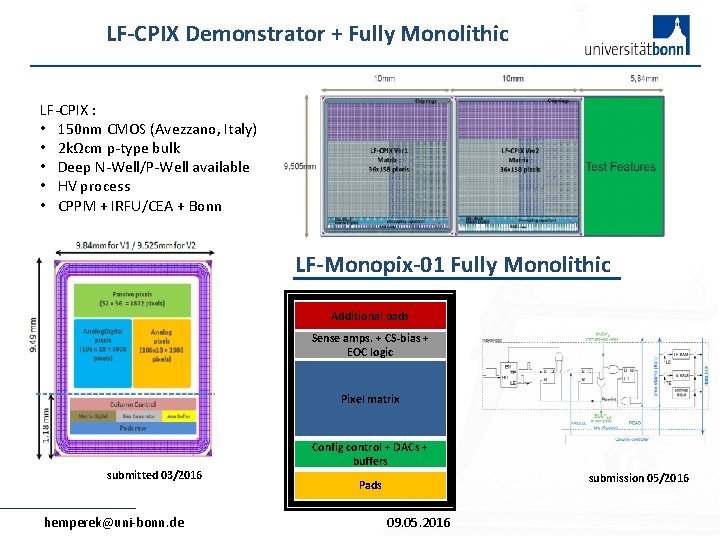

LF-CPIX Demonstrator + Fully Monolithic LF-CPIX : • 150 nm CMOS (Avezzano, Italy) • 2 kΩcm p-type bulk • Deep N-Well/P-Well available • HV process • CPPM + IRFU/CEA + Bonn LF-Monopix-01 Fully Monolithic Additional pads Sense amps. + CS-bias + EOC logic Pixel matrix submitted 03/2016 hemperek@uni-bonn. de Config control + DACs + buffers submission 05/2016 Pads 09. 05. 2016

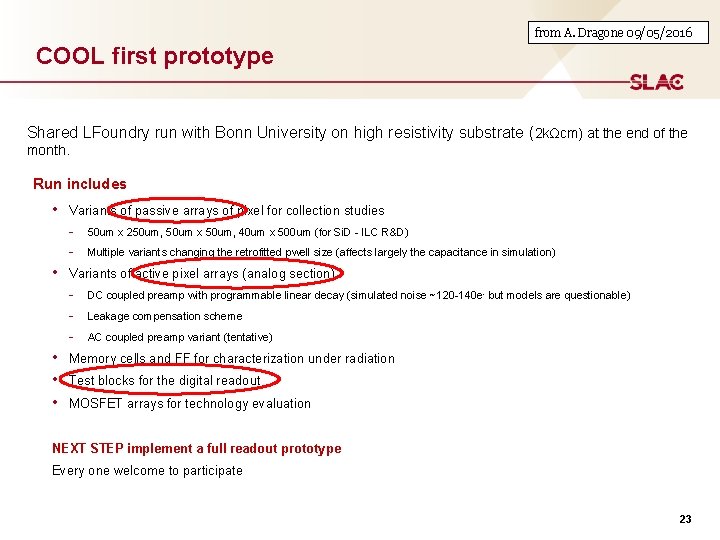

from A. Dragone 09/05/2016 COOL first prototype Shared LFoundry run with Bonn University on high resistivity substrate (2 kΩcm) at the end of the month. Run includes • Variants of passive arrays of pixel for collection studies - 50 um x 250 um, 50 um x 50 um, 40 um x 500 um (for Si. D - ILC R&D) - Multiple variants changing the retrofitted pwell size (affects largely the capacitance in simulation) • Variants of active pixel arrays (analog section) - DC coupled preamp with programmable linear decay (simulated noise ~120 -140 e- but models are questionable) - Leakage compensation scheme - AC coupled preamp variant (tentative) • Memory cells and FF for characterization under radiation • Test blocks for the digital readout • MOSFET arrays for technology evaluation NEXT STEP implement a full readout prototype Every one welcome to participate 23

This workshop • 2 important goals: – TCAD and tools for conception. • Optimize sensor layout wrt technology chosen. – Geant 4 and pixel performances with HV-CMOS. • (note there might be technological case -simpler modules, less material, better yields, …- , cost case…) But what is the physics case for the technology? – Monolithic at high radius? Track trigger (see Schoening 09/05/2016) , improvement on momentum resolution in η range ~1. 2 -1. 8 (see Garcia-Sciveres 09/05/2016), others? – Smart CMOS pixel + digital IC at inner radius (and/or subpixel encoding? ) smaller granularity (<50× 50μm 2!) improves b-tagging & tracking performances!? ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 24

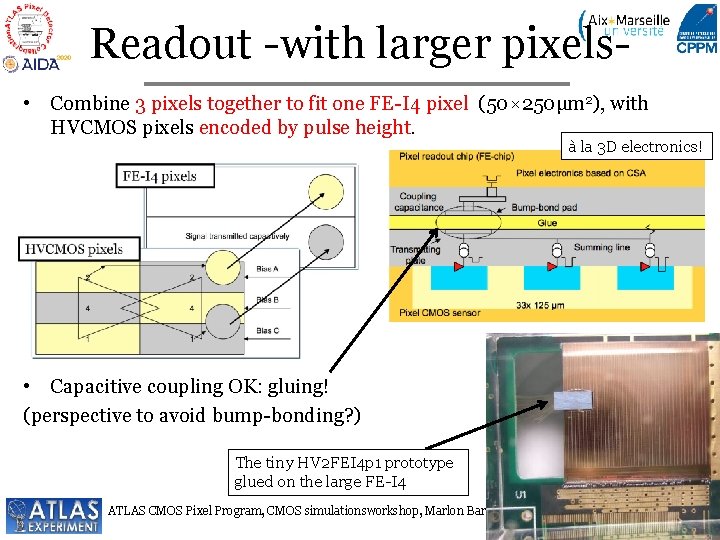

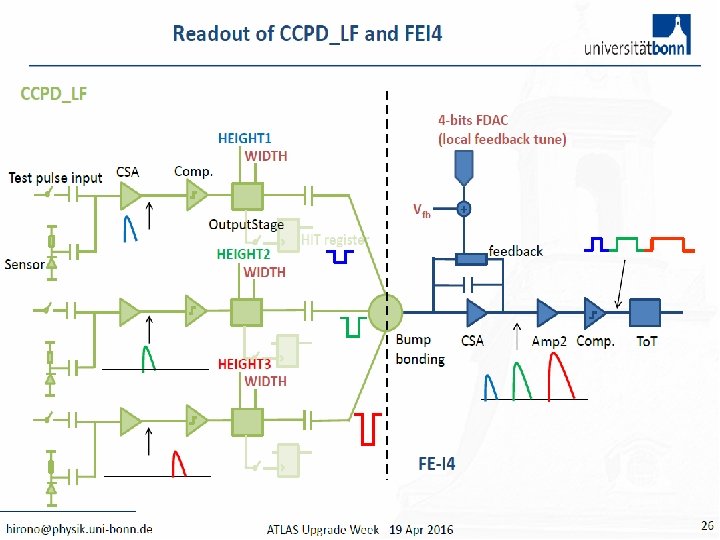

Readout -with larger pixels • Combine 3 pixels together to fit one FE-I 4 pixel (50× 250μm 2), with HVCMOS pixels encoded by pulse height. à la 3 D electronics! • Capacitive coupling OK: gluing! (perspective to avoid bump-bonding? ) The tiny HV 2 FEI 4 p 1 prototype glued on the large FE-I 4 ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 25

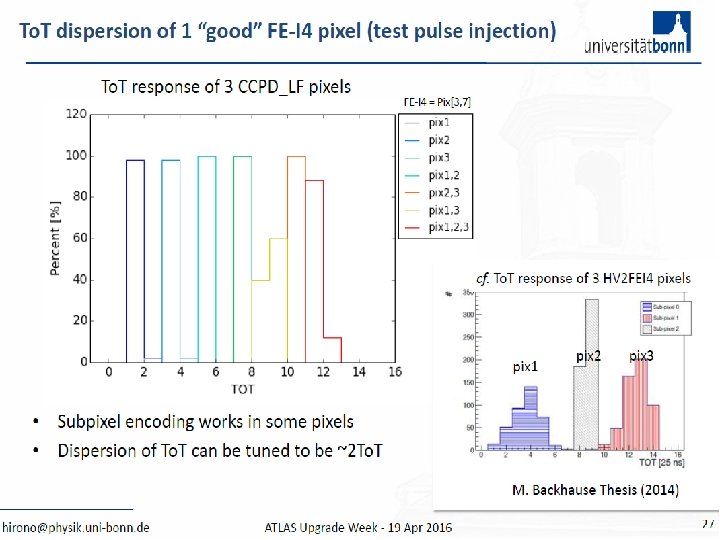

ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 26

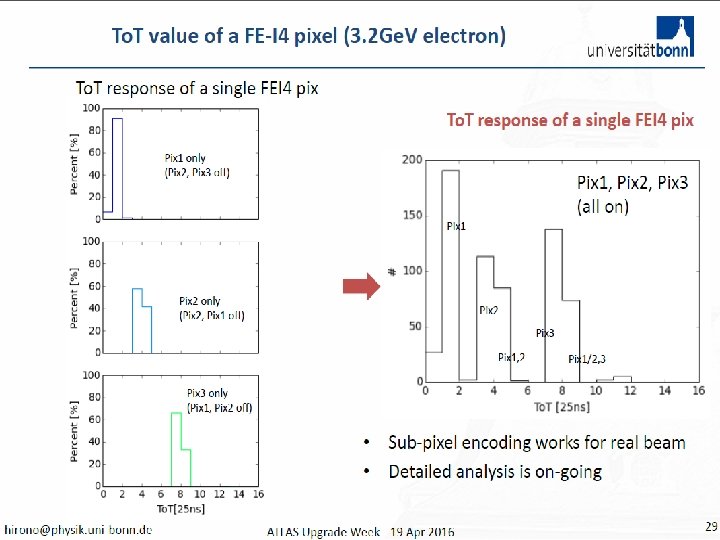

ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 27

ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 28

2016+ • Module concept (coupling, TSV, etc…), study mechanics (power, cooling, etc…) • Increased radiation hardness. • Study efficiency at various test-beams (DESY, SLAC, CERN…). • Now: – TCAD simulations sensor designs – Simulations Geant 4 -based. Parameters: granularity, sensor thickness , detector arrangement. • Two different goals: 1 - Low cost, large scale, high yield. outer layers 2 - Ultimate performance small granularity! ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 29

Conclusion • CPIX meetings organized prototyping and communication on this technology. • CMOS Demonstrator Task Force Large scale demonstrator available (AMS) or submitted (LF). • Fully Monolithic CMOS meeting kick-off new momentum. • Now is the moment to contribute with sensor design (TCAD) as well as contribute to making the case for the technology (performances) This workshop! ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 30

Backup ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 31

Goals for pixels >2016 • Targets outer layers: – HVHR-CMOS capacitively coupled to FE-I 4. Need to demonstrate: • • Operate full size 2× 2 cm 2. Low noise (<1% pixels masked). MIP >99 % detection efficiency. Increased radiation hardness (~300 Mrad, >10. 15 neq. cm-2). Glue coupling for low cost. Module: Wire-bonds. Granularity: 33× 125 μm 2. Depleted zone of order 100 μm or less. – Or fully monolithic option. ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 32

Ultimate goal (targets ~2018/9? ) • Solution for inner layers? HVHR-CMOS capacitively coupled to FE 65 -like chip. Need to demonstrate: – – – – Operate full size 2× 2 cm 2. Low noise (<1% pixels masked). MIP >99 % detection efficiency. Increased radiation hardness (~500 MRad, 1016 neq. cm-2). Glue coupling or bump-bonding. Module: TSV, low cost wafer bonding? ? ? Granularity: minimal requirement 25× 100 μm 2 or 50× 50 μm 2 , better would be sub-FE 65 pixel size e. g. 25× 25 μm 2. – Depleted zone below <50 μm. ATLAS CMOS Pixel Program, CMOS simulationsworkshop, Marlon Barbero, May 12 th 2016 33

- Slides: 33