ATCA LLP CARRIER BLOCK DIAGRAMS LAST UPDATE 09052007

ATCA LLP CARRIER BLOCK DIAGRAMS LAST UPDATE 09/05/2007

Master / Slave Structure SLOT A (n) MASTER/SLAVE CARD_PRESENT TCLK_PRESENT DATAPATH TRIGGER CLOCK SYNCs And DATA MANAGERS CLOCK AND SYNCS SWITCHES SLOT B (n+1) MASTER/SLAVE CARD_PRESENT TCLK_PRESENT DATAPATH TRIGGER CLOCK SYNCs And DATA MANAGERS CLOCK AND SYNCS TCLK

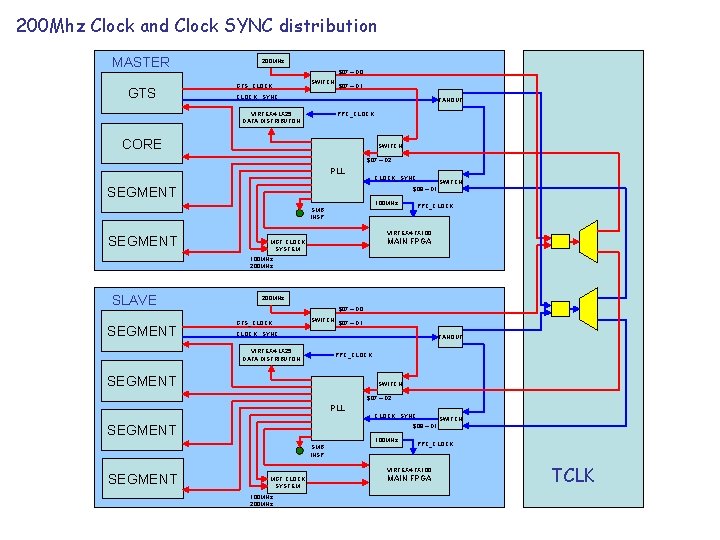

200 Mhz Clock and Clock SYNC distribution MASTER GTS 200 MHz $07 – D 0 GTS_CLOCK SWITCH $07 – D 1 CLOCK_ SYNC FANOUT VIRTEX 4 LX 25 DATA DISTRIBUTON PPC_CLOCK CORE SWITCH $07 – D 2 PLL CLOCK_ SYNC SEGMENT 100 MHz PPC_CLOCK SMB INSP SEGMENT SWITCH $08 – D 1 VIRTEX 4 FX 100 MAIN FPGA MGT CLOCK SYSTEM 100 MHz 200 MHz SLAVE SEGMENT 200 MHz $07 – D 0 GTS_CLOCK SWITCH $07 – D 1 CLOCK_ SYNC FANOUT VIRTEX 4 LX 25 DATA DISTRIBUTON PPC_CLOCK SEGMENT SWITCH $07 – D 2 PLL SEGMENT SWITCH $08 – D 1 100 MHz SMB INSP SEGMENT CLOCK_ SYNC PPC_CLOCK VIRTEX 4 FX 100 MGT CLOCK SYSTEM 100 MHz 200 MHz MAIN FPGA TCLK

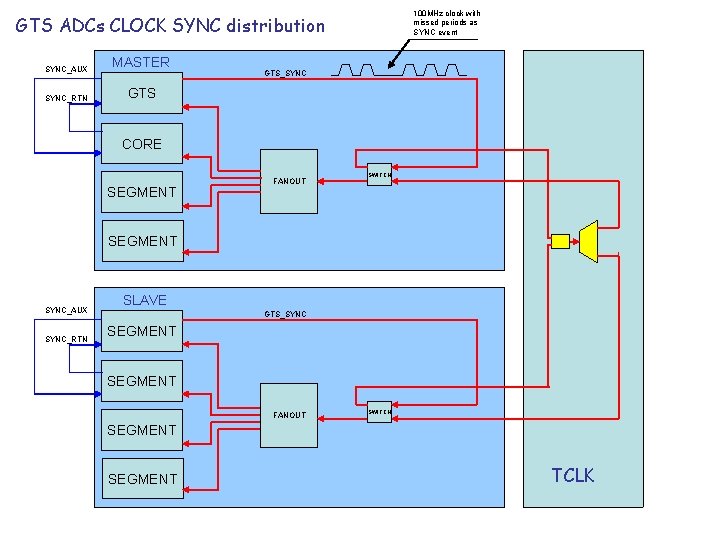

100 MHz clock with missed periods as SYNC event GTS ADCs CLOCK SYNC distribution SYNC_AUX MASTER SYNC_RTN GTS_SYNC CORE SEGMENT FANOUT SWITCH SEGMENT SYNC_AUX SYNC_RTN SLAVE GTS_SYNC SEGMENT FANOUT SWITCH SEGMENT TCLK

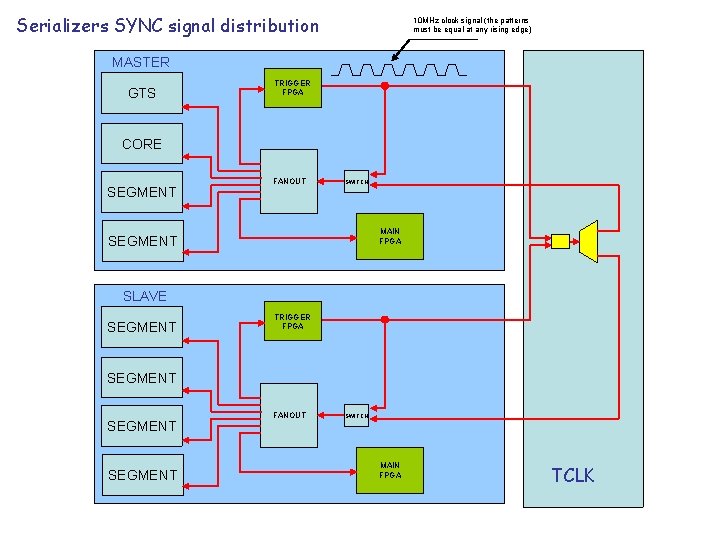

Serializers SYNC signal distribution 10 MHz clock signal (the patterns must be equal at any rising edge) MASTER GTS TRIGGER FPGA CORE SEGMENT FANOUT SWITCH MAIN FPGA SEGMENT SLAVE SEGMENT TRIGGER FPGA SEGMENT FANOUT SWITCH MAIN FPGA TCLK

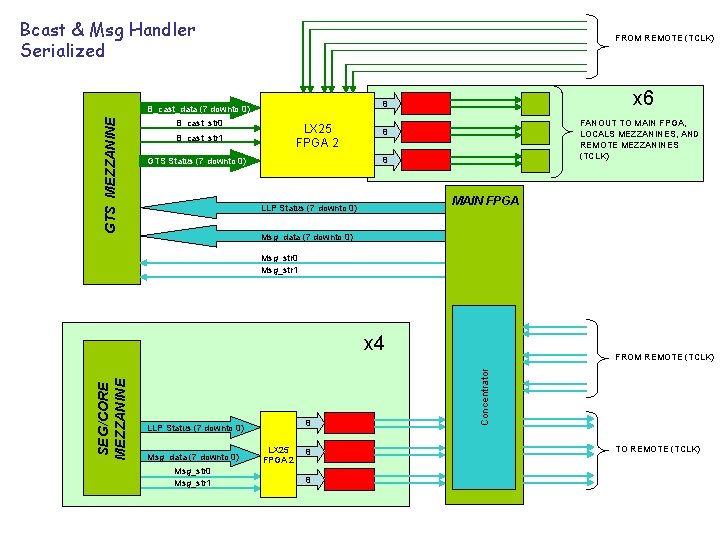

Bcast & Msg Handler Serialized B_cast_str 0 B_cast_str 1 GTS Status (7 downto 0) SERIALIZERS 8 1 GTS MEZZANINE B_cast_data (7 downto 0) FROM REMOTE (TCLK) x 6 8 LX 25 FPGA 2 FANOUT TO MAIN FPGA, LOCALS MEZZANINES, AND REMOTE MEZZANINES (TCLK) 8 8 MAIN FPGA LLP Status (7 downto 0) Msg_data (7 downto 0) Msg_str 0 Msg_str 1 8 LLP Status (7 downto 0) Msg_data (7 downto 0) Msg_str 0 Msg_str 1 LX 25 FPGA 2 8 8 FROM REMOTE (TCLK) Concentrator SEG/CORE MEZZANINE x 4 TO REMOTE (TCLK)

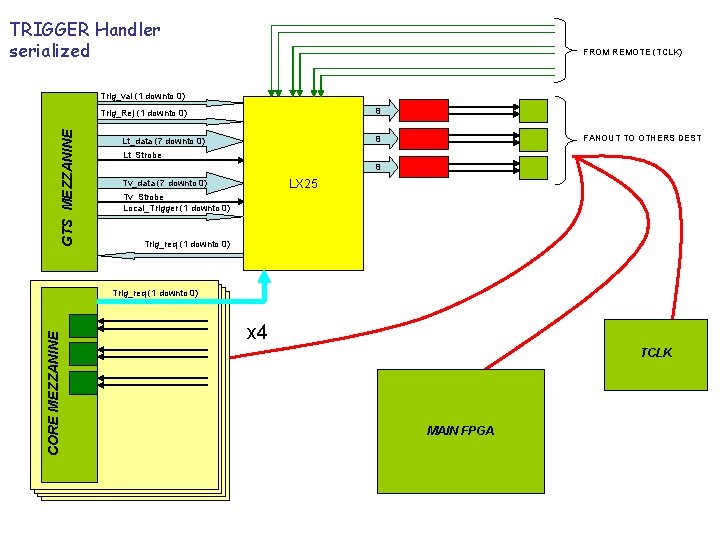

TRIGGER Handler serialized FROM REMOTE (TCLK) Trig_val (1 downto 0) 8 GTS MEZZANINE Trig_Rej (1 downto 0) FANOUT TO OTHERS DEST 8 Lt_data (7 downto 0) Lt_Strobe 8 LX 25 Tv_data (7 downto 0) Tv_Strobe Local_Trigger (1 downto 0) Trig_req (1 downto 0) CORE MEZZANINE Trig_req (1 downto 0) x 4 TCLK MAIN FPGA

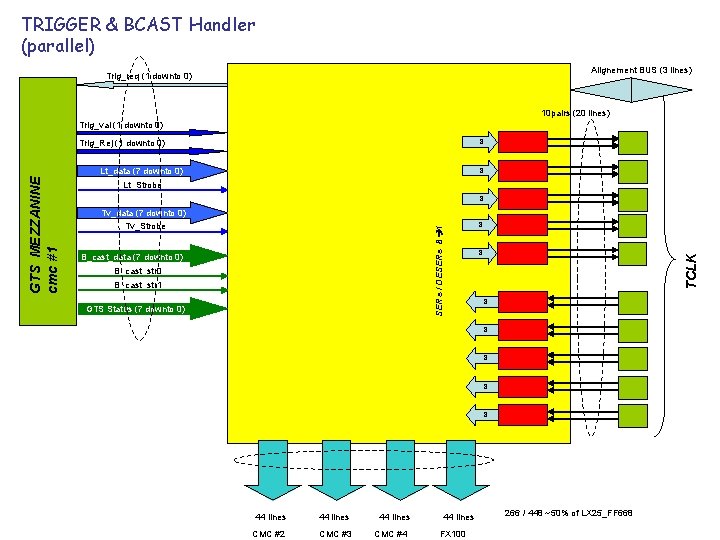

TRIGGER & BCAST Handler (parallel) Alignement BUS (3 lines) Trig_req (1 downto 0) 10 pairs (20 lines) Trig_val (1 downto 0) Trig_Rej (1 downto 0) 8 8 Lt_Strobe 8 B_cast_data (7 downto 0) B_cast_str 0 B_cast_str 1 GTS Status (7 downto 0) 8 8 TCLK Tv_data (7 downto 0) Tv_Strobe SERs / DESERs 8 1 GTS MEZZANINE cmc #1 Lt_data (7 downto 0) 8 8 8 44 lines CMC #2 CMC #3 44 lines CMC #4 44 lines FX 100 266 / 448 ~50% of LX 25_FF 668

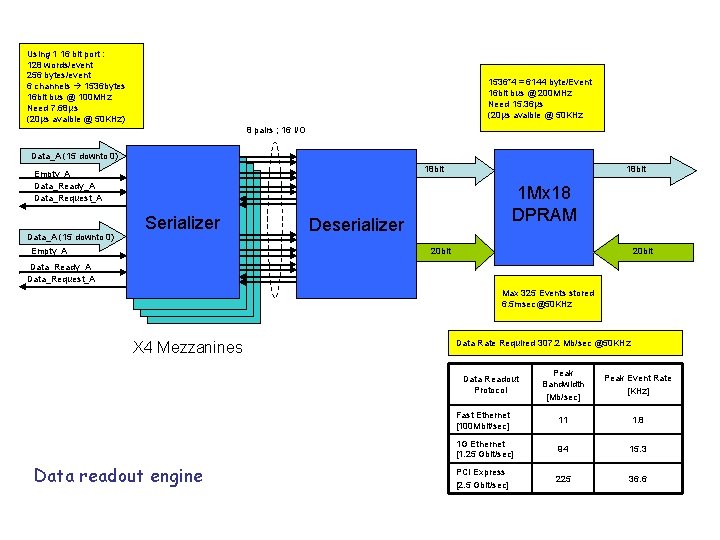

Using 1 16 bit port : 128 words/event 256 bytes/event 6 channels 1536 bytes 16 bit bus @ 100 MHz Need 7. 68µs (20µs avaible @ 50 KHz) 1536*4 = 6144 byte/Event 16 bit bus @ 200 MHz Need 15. 36µs (20µs avaible @ 50 KHz 8 pairs ; 16 I/O Data_A (15 downto 0) 18 bit Empty_A Data_Ready_A Data_Request_A Data_A (15 downto 0) Empty_A Serializer 18 bit 1 Mx 18 DPRAM Deserializer 20 bit Data_Ready_A Data_Request_A Max 325 Events stored 6. 5 msec@50 KHz X 4 Mezzanines Data Rate Required 307. 2 Mb/sec @50 KHz Peak Bandwidth [Mb/sec] Peak Event Rate [KHz] Fast Ethernet [100 Mbit/sec] 11 1. 8 1 G Ethernet [1. 25 Gbit/sec] 94 15. 3 PCI Express [2. 5 Gbit/sec] 225 36. 6 Data Readout Protocol Data readout engine

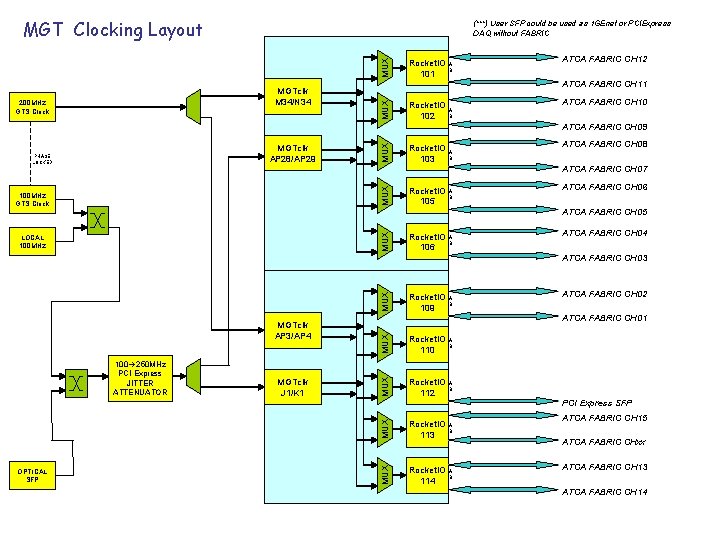

MGT Clocking Layout MUX (***) User SFP could be used as 1 GEnet or PCIExpress DAQ without FABRIC 200 MHz GTS Clock ATCA FABRIC CH 12 ATCA FABRIC CH 11 MUX MGTclk M 34/N 34 Rocket. IO A B 101 Rocket. IO A B 102 ATCA FABRIC CH 10 MGTclk AP 28/AP 29 PHASE LOCKED MUX ATCA FABRIC CH 09 Rocket. IO A B 103 ATCA FABRIC CH 08 MUX ATCA FABRIC CH 07 100 MHz GTS Clock Rocket. IO A B 105 ATCA FABRIC CH 06 MUX ATCA FABRIC CH 05 LOCAL 100 MHz Rocket. IO A B 106 ATCA FABRIC CH 04 MUX ATCA FABRIC CH 03 MGTclk J 1/K 1 MUX 100 250 MHz PCI Express JITTER ATTENUATOR ATCA FABRIC CH 02 ATCA FABRIC CH 01 Rocket. IO A B 110 MUX MGTclk AP 3/AP 4 Rocket. IO A B 109 Rocket. IO A B 112 MUX OPTICAL SFP Rocket. IO A B 113 MUX PCI Express SFP Rocket. IO A B 114 ATCA FABRIC CH 15 ATCA FABRIC CHxx ATCA FABRIC CH 13 ATCA FABRIC CH 14

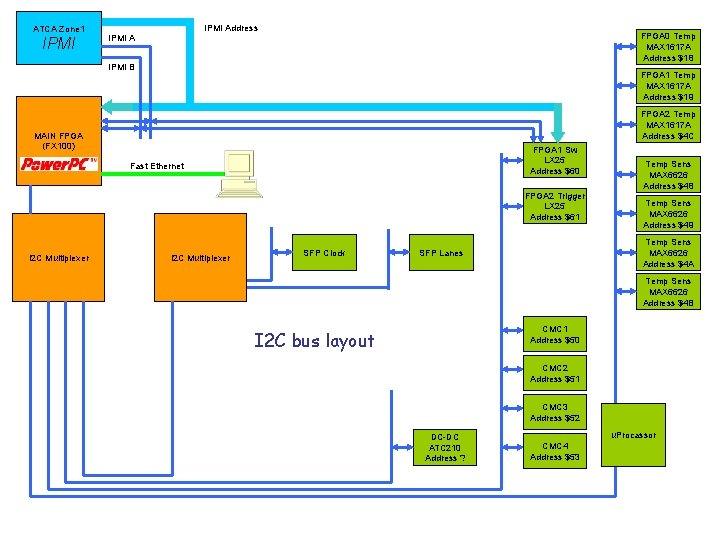

ATCA Zone 1 IPMI Address FPGA 0 Temp MAX 1617 A Address $18 IPMI A IPMI B FPGA 1 Temp MAX 1617 A Address $19 FPGA 2 Temp MAX 1617 A Address $4 C MAIN FPGA (FX 100) FPGA 1 Sw LX 25 Address $60 Fast Ethernet FPGA 2 Trigger LX 25 Address $61 I 2 C Multiplexer SFP Clock Temp Sens MAX 6626 Address $48 Temp Sens MAX 6626 Address $49 Temp Sens MAX 6626 Address $4 A SFP Lanes Temp Sens MAX 6626 Address $4 B CMC 1 Address $50 I 2 C bus layout CMC 2 Address $51 CMC 3 Address $52 DC-DC ATC 210 Address ? u. Procassor CMC 4 Address $53

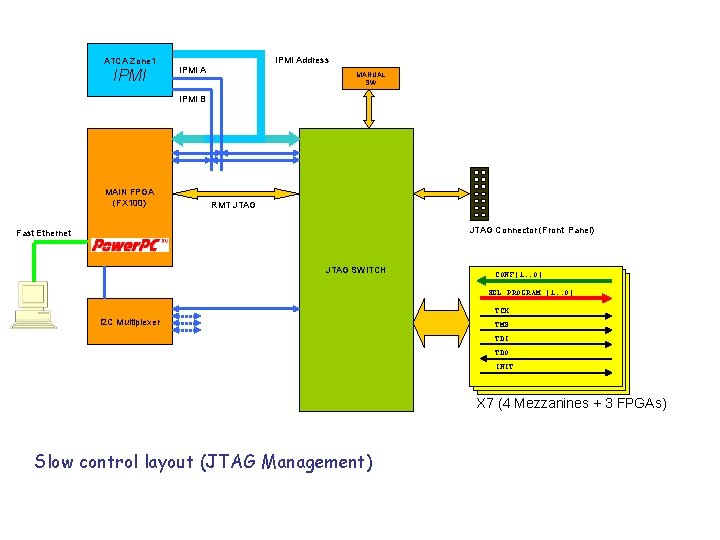

ATCA Zone 1 IPMI Address IPMI A MANUAL SW IPMI B MAIN FPGA (FX 100) RMT JTAG Connector (Front Panel) Fast Ethernet JTAG SWITCH CONF[1. . 0] SEL PROGRAM [1. . 0] TCK I 2 C Multiplexer TMS TDI TDO INIT X 7 (4 Mezzanines + 3 FPGAs) Slow control layout (JTAG Management)

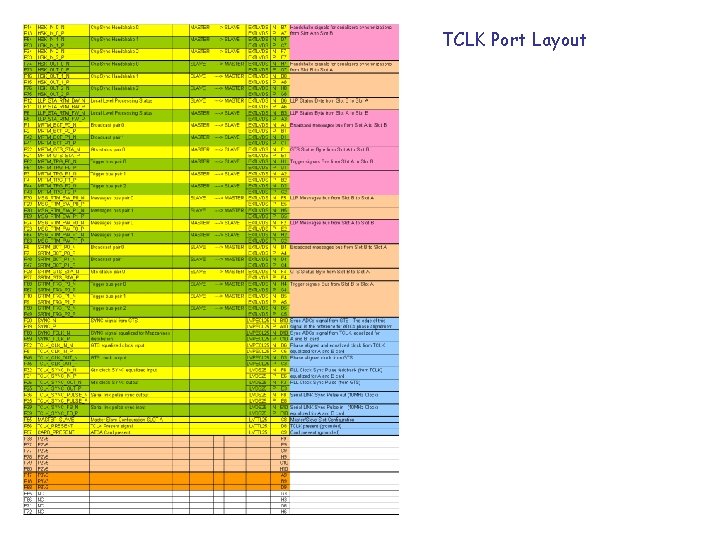

TCLK Port Layout

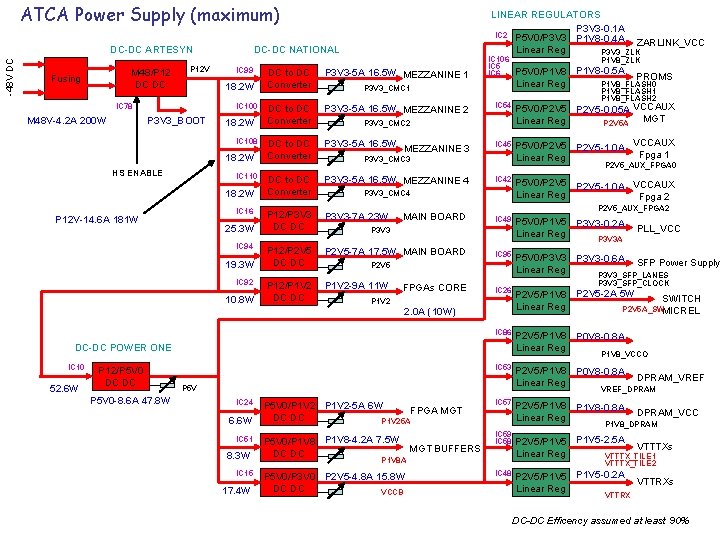

ATCA Power Supply (maximum) -48 V DC DC-DC ARTESYN M 48/P 12 DC DC Fusing P 12 V DC-DC NATIONAL IC 99 18. 2 W IC 100 IC 78 M 48 V-4. 2 A 200 W P 3 V 3_BOOT 18. 2 W IC 108 18. 2 W HS ENABLE IC 110 18. 2 W IC 16 P 12 V-14. 6 A 181 W LINEAR REGULATORS P 3 V 3 -0. 1 A IC 2 P 5 V 0/P 3 V 3 P 1 V 8 -0. 4 A ZARLINK_VCC Linear Reg P 3 V 3_ZLK 25. 3 W IC 94 19. 3 W IC 92 10. 8 W DC to DC Converter P 3 V 3 -5 A 16. 5 W MEZZANINE 1 IC 106 IC 5 IC 6 P 3 V 3_CMC 1 DC to DC Converter P 3 V 3 -5 A 16. 5 W MEZZANINE 2 DC to DC Converter P 3 V 3 -5 A 16. 5 W MEZZANINE 4 P 12/P 3 V 3 DC DC P 3 V 3 -7 A 23 W P 5 V 0/P 2 V 5 -0. 05 A VCCAUX MGT Linear Reg P 2 V 5 A IC 45 P 5 V 0/P 2 V 5 -1. 0 A VCCAUX Fpga 1 Linear Reg P 3 V 3_CMC 3 P 2 V 5_AUX_FPGA 0 IC 42 P 3 V 3_CMC 4 MAIN BOARD P 3 V 3 52. 6 W P 5 V 0 -8. 6 A 47. 8 W P 5 V 0/P 1 V 5 P 3 V 3 -0. 2 A Linear Reg PLL_VCC P 5 V 0/P 3 V 3 -0. 6 A Linear Reg SFP Power Supply P 3 V 3 A P 12/P 2 V 5 DC DC P 12/P 1 V 2 DC DC P 2 V 5 -7 A 17. 5 W MAIN BOARD IC 95 P 2 V 5 P 1 V 2 -9 A 11 W FPGAs CORE P 3 V 3_SFP_LANES P 3 V 3_SFP_CLOCK IC 26 P 2 V 5/P 1 V 8 P 2 V 5 -2 A 5 W SWITCH Linear Reg P 2 V 5 A_SWMICREL IC 86 P 2 V 5/P 1 V 8 P 0 V 8 -0. 8 A Linear Reg P 1 V 2 DC-DC POWER ONE P 12/P 5 V 0 DC DC P 5 V 0/P 2 V 5 -1. 0 A VCCAUX Linear Reg Fpga 2 P 2 V 5_AUX_FPGA 2 IC 49 2. 0 A (10 W) IC 10 P 1 V 8_FLASH 1 P 1 V 8_FLASH 2 IC 54 P 3 V 3_CMC 2 MEZZANINE 3 P 1 V 8_ZLK P 5 V 0/P 1 V 8 -0. 5 A PROMS Linear Reg P 1 V 8_FLASH 0 P 1 V 8_VCCO IC 53 P 5 V P 2 V 5/P 1 V 8 P 0 V 8 -0. 8 A Linear Reg DPRAM_VREF P 2 V 5/P 1 V 8 -0. 8 A Linear Reg DPRAM_VCC VREF_DPRAM IC 24 6. 6 W IC 51 8. 3 W IC 15 17. 4 W P 5 V 0/P 1 V 2 -5 A 6 W FPGA MGT DC DC P 1 V 25 A IC 57 P 5 V 0/P 1 V 8 -4. 2 A 7. 5 W MGT BUFFERS DC DC IC 59 IC 58 P 2 V 5/P 1 V 5 -2. 5 A VTTTXs Linear Reg VTTTX_TILE 1 P 5 V 0/P 3 V 0 P 2 V 5 -4. 8 A 15. 8 W DC DC VCCB IC 48 P 2 V 5/P 1 V 5 -0. 2 A Linear Reg P 1 V 8_DPRAM P 1 V 8 A VTTTX_TILE 2 VTTRXs VTTRX DC-DC Efficency assumed at least 90%

Case 1 : PCIExpress 1 Mx 36 DPRAM PCIExpress 1 Mx 36 DPRAM TCLK Bus PCIExpress 1 Mx 36 DPRAM ADCs PCIExpress PRE PROCESSING PCIExpress 1 Mx 36 DPRAM 1 Mx 36 DPRAM PCIExpress 1 Mx 36 DPRAM PCIExpress

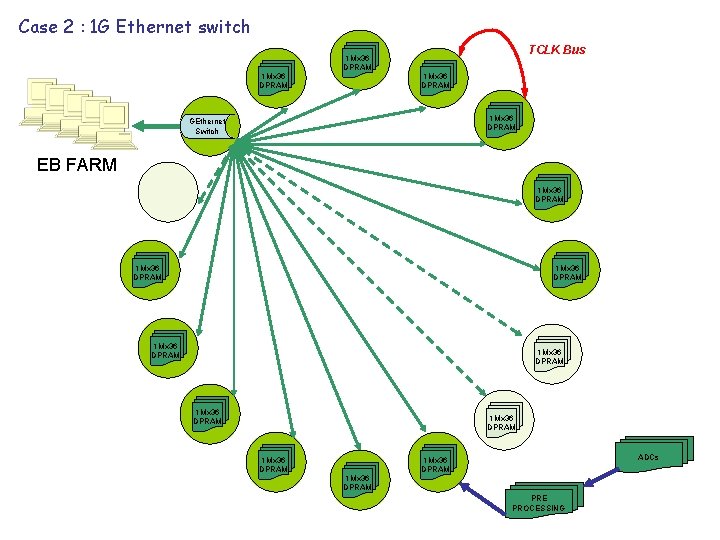

Case 2 : 1 G Ethernet switch 1 Mx 36 DPRAM TCLK Bus 1 Mx 36 DPRAM GEthernet Switch EB FARM 1 Mx 36 DPRAM 1 Mx 36 DPRAM 1 Mx 36 DPRAM ADCs 1 Mx 36 DPRAM PRE PROCESSING

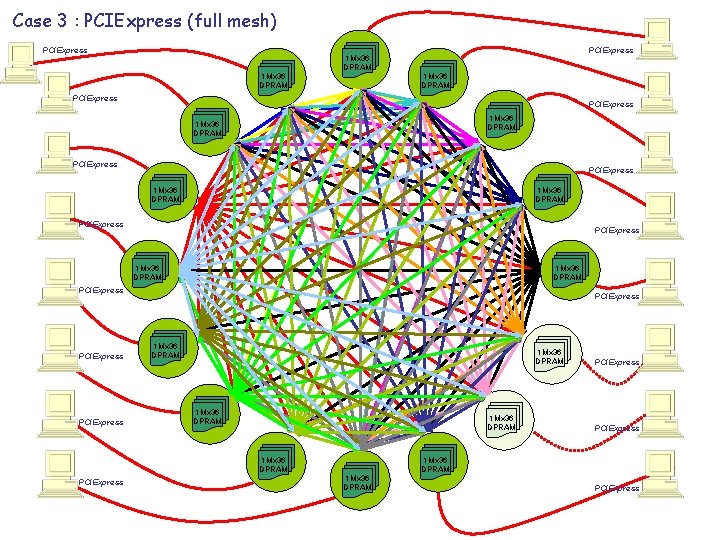

Case 3 : PCIExpress (full mesh) PCIExpress 1 Mx 36 DPRAM PCIExpress 1 Mx 36 DPRAM PCIExpress 1 Mx 36 DPRAM PCIExpress 1 Mx 36 DPRAM 1 Mx 36 DPRAM PCIExpress 1 Mx 36 DPRAM PCIExpress

- Slides: 17