AT 40 K Family w Free RAM TM

- Slides: 23

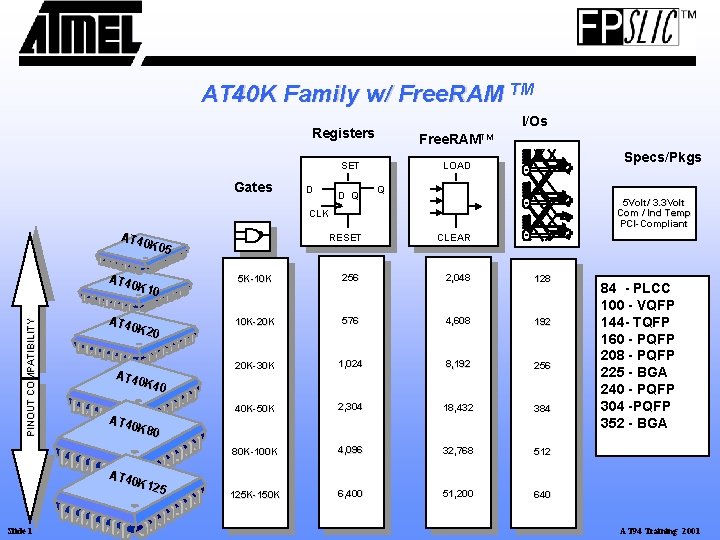

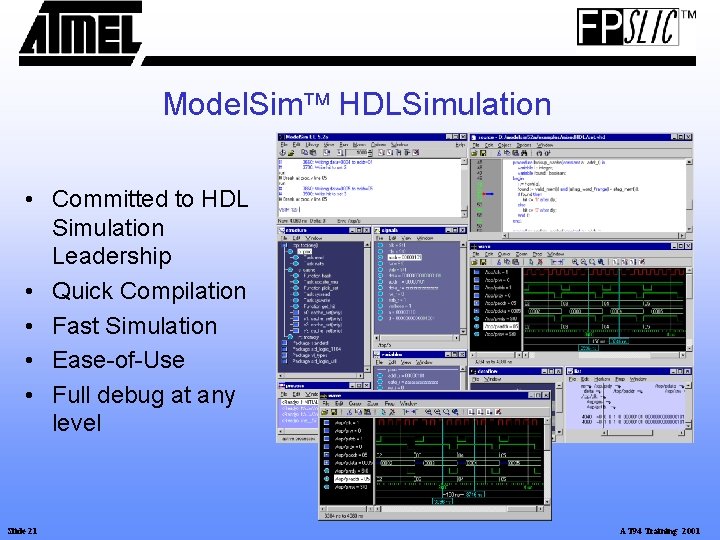

AT 40 K Family w/ Free. RAM TM I/Os Registers Free. RAMTM SET Gates D D Q Specs/Pkgs LOAD Q 5 Volt/ 3. 3 Volt Com / Ind Temp PCI-Compliant CLK PINOUT COMPATIBILITY AT 4 0 K 0 5 CLEAR AT 4 0 K 1 0 5 K-10 K 256 2, 048 128 AT 4 0 K 2 0 10 K-20 K 576 4, 608 192 20 K-30 K 1, 024 8, 192 256 40 K-50 K 2, 304 18, 432 384 80 K-100 K 4, 096 32, 768 512 125 K-150 K 6, 400 51, 200 640 AT 4 0 K 4 0 AT 4 0 K 8 0 AT 4 0 K 1 25 Slide 1 RESET 84 - PLCC 100 - VQFP 144 - TQFP 160 - PQFP 208 - PQFP 225 - BGA 240 - PQFP 304 -PQFP 352 - BGA AT 94 Training 2001

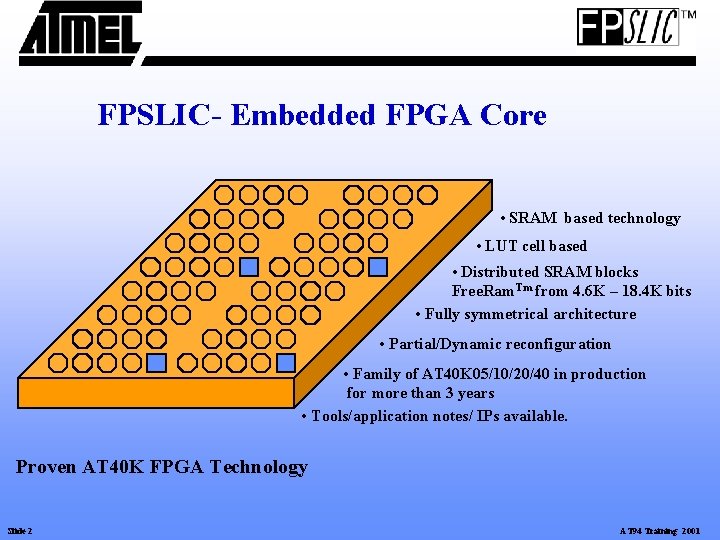

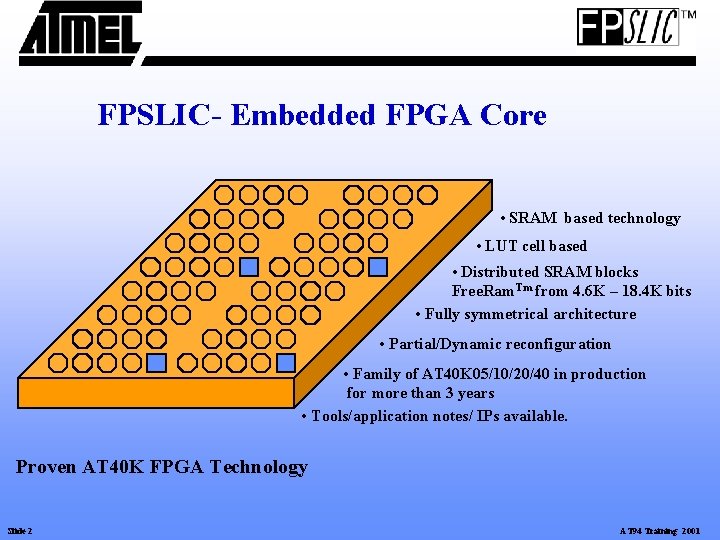

FPSLIC- Embedded FPGA Core • SRAM based technology • LUT cell based • Distributed SRAM blocks Free. Ram. Tm from 4. 6 K – 18. 4 K bits • Fully symmetrical architecture • Partial/Dynamic reconfiguration • Family of AT 40 K 05/10/20/40 in production for more than 3 years • Tools/application notes/ IPs available. Proven AT 40 K FPGA Technology Slide 2 AT 94 Training 2001

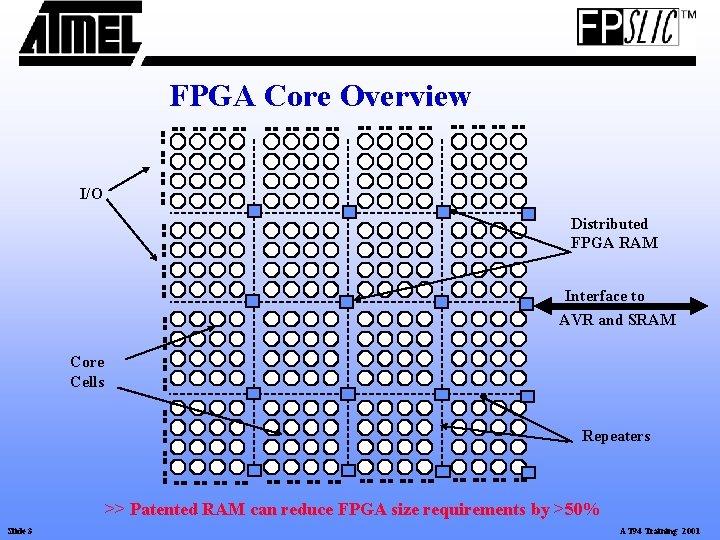

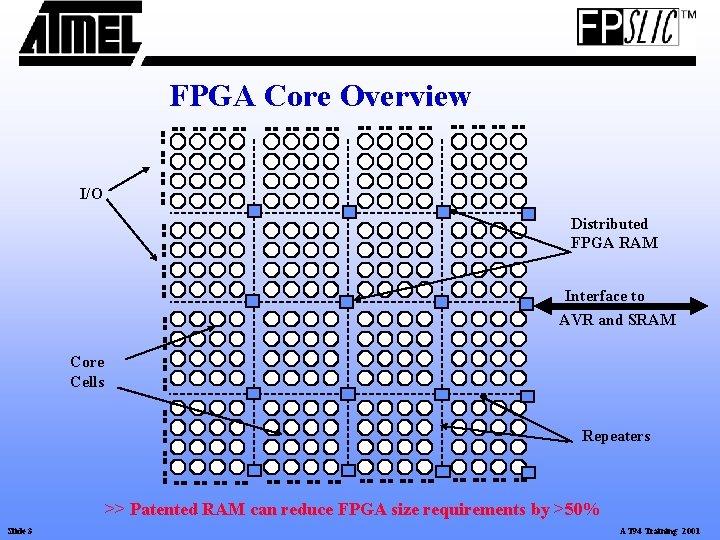

FPGA Core Overview I/O Distributed FPGA RAM Interface to AVR and SRAM Core Cells Repeaters >> Patented RAM can reduce FPGA size requirements by >50% Slide 3 AT 94 Training 2001

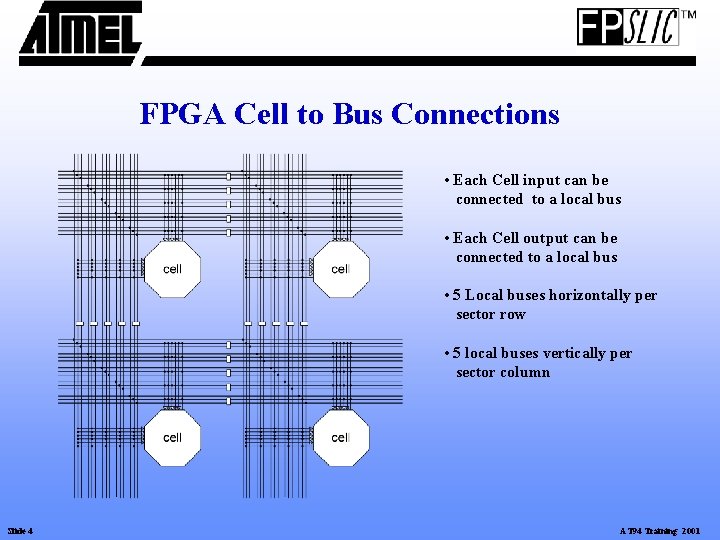

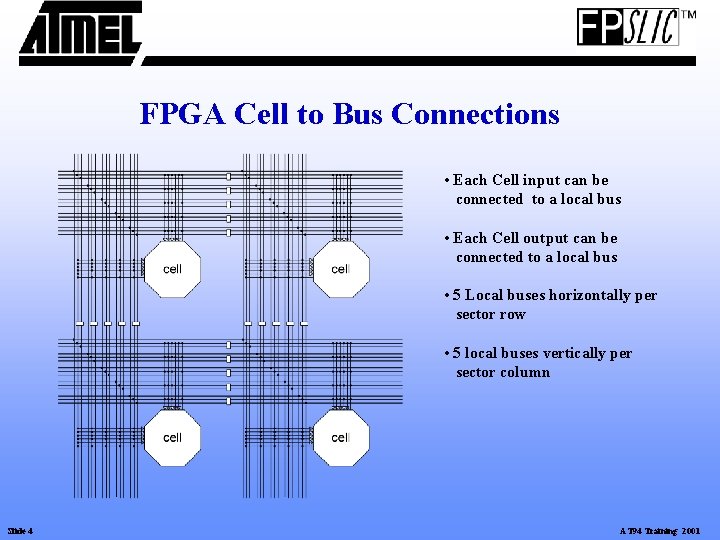

FPGA Cell to Bus Connections • Each Cell input can be connected to a local bus • Each Cell output can be connected to a local bus • 5 Local buses horizontally per sector row • 5 local buses vertically per sector column Slide 4 AT 94 Training 2001

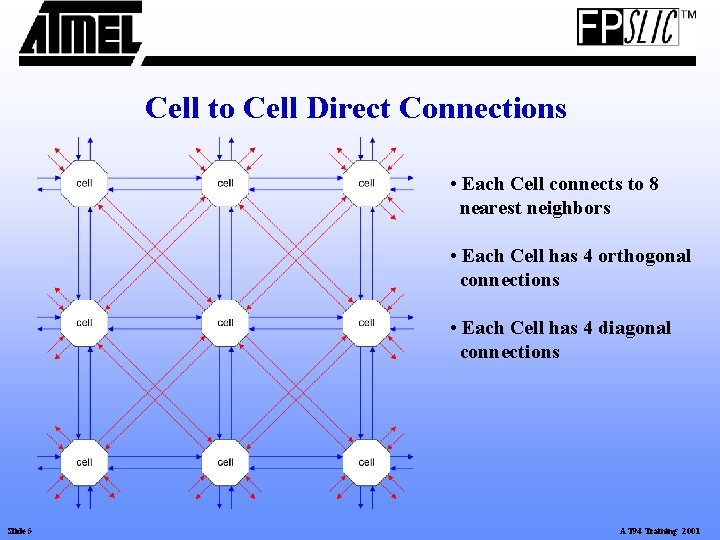

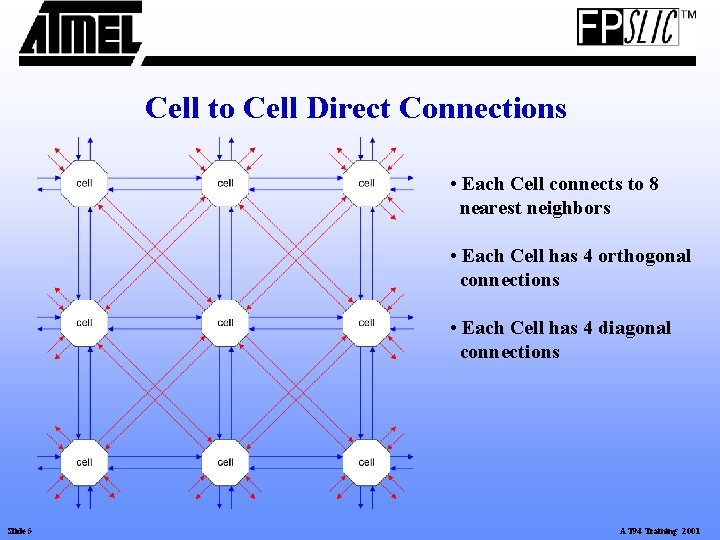

Cell to Cell Direct Connections • Each Cell connects to 8 nearest neighbors • Each Cell has 4 orthogonal connections • Each Cell has 4 diagonal connections Slide 5 AT 94 Training 2001

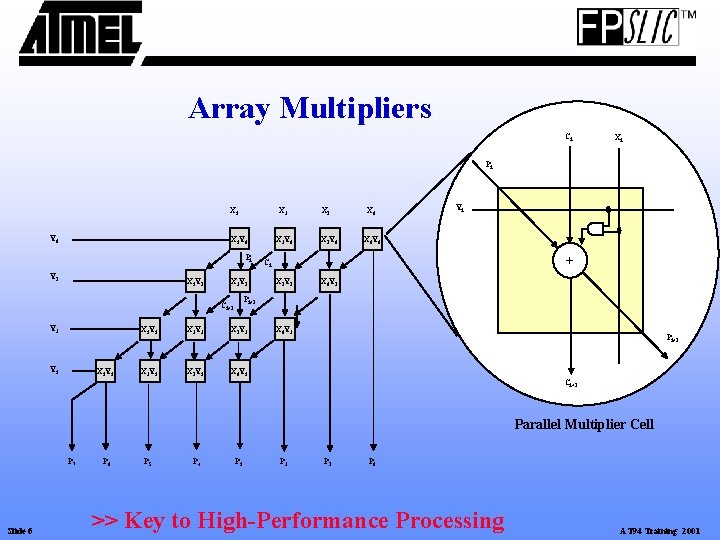

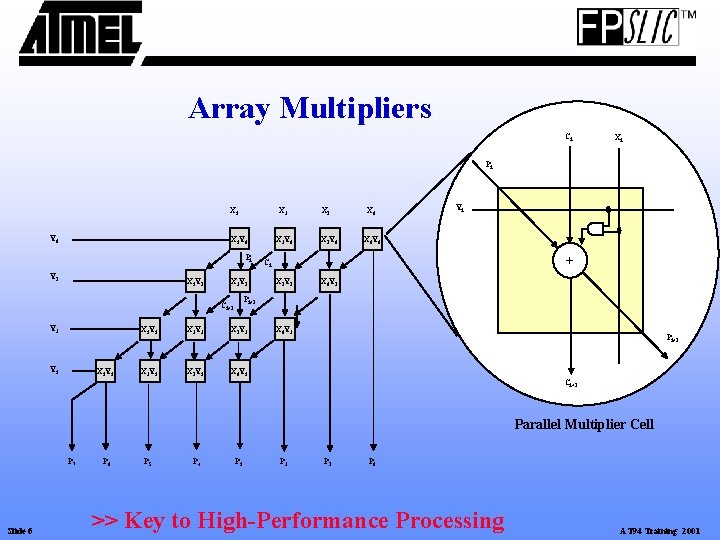

Array Multipliers Ci Xi Pi X 3 Y 0 X 2 X 3 Y 0 Pi Y 1 X 3 Y 1 X 2 Y 1 Y 3 X 3 Y 3 X 1 Y 0 X 0 Yi X 0 Y 0 + Ci X 1 Y 1 X 0 Y 1 Pi+1 Ci+1 Y 2 X 2 Y 0 X 1 X 3 Y 3 X 2 Y 2 X 1 Y 2 X 2 Y 3 X 1 Y 3 X 0 Y 2 Pi+1 Ci+1 Parallel Multiplier Cell P 7 Slide 6 P 5 P 4 P 3 P 2 P 1 P 0 >> Key to High-Performance Processing AT 94 Training 2001

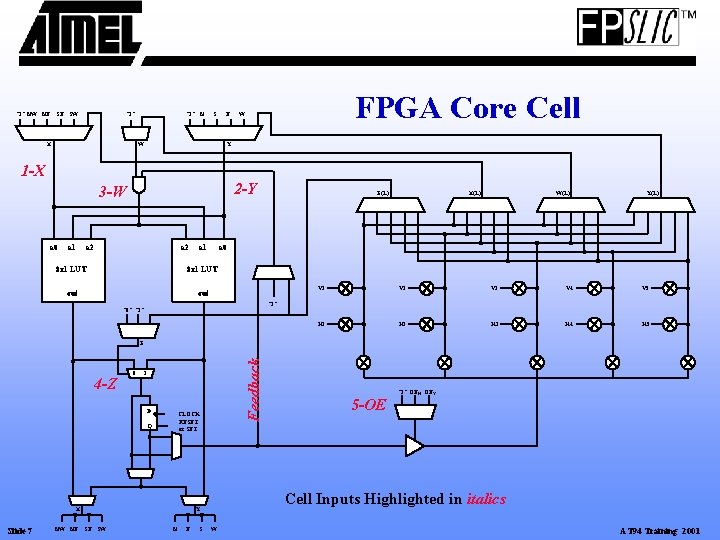

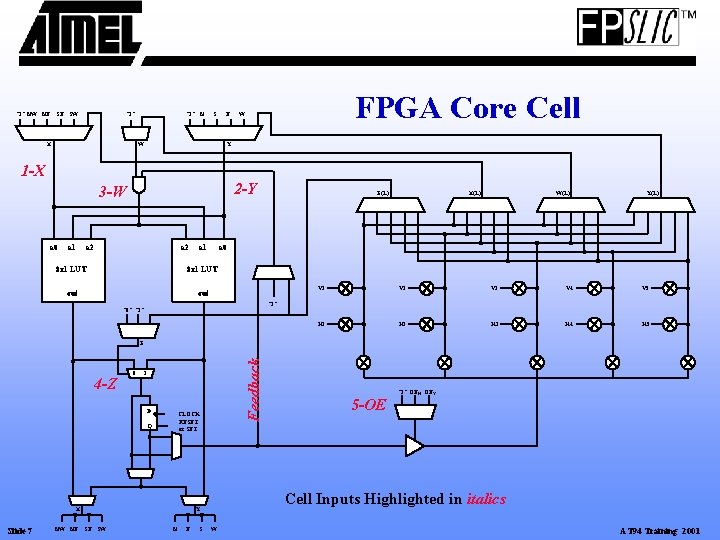

"1" NW NE SE SW "1" X "1" N S E W FPGA Core Cell W Y 1 -X 2 -Y 3 -W a 0 a 1 a 2 a 1 Z(L) X(L) W(L) Y(L) a 0 8 x 1 LUT out V 1 V 2 V 3 V 4 V 5 H 1 H 2 H 3 H 4 H 5 "1" "0" "1" 4 -Z 0 1 D CLOCK RESET or SET Q X Slide 7 NW NE Feedback Z Cell Inputs Highlighted in italics Y SE SW N E S 5 -OE "1" OEH OEV W AT 94 Training 2001

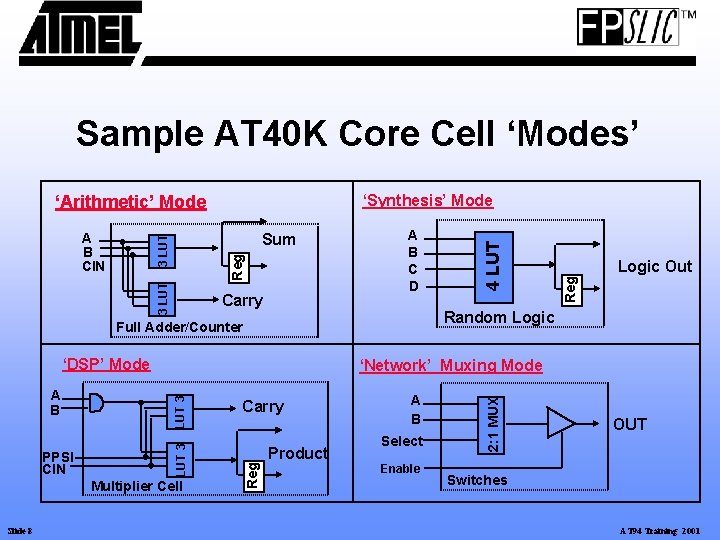

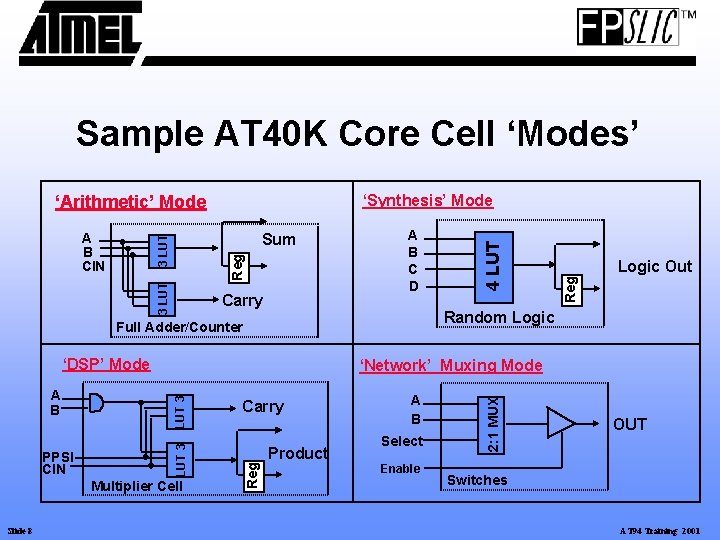

Sample AT 40 K Core Cell ‘Modes’ ‘Arithmetic’ Mode Random Logic Full Adder/Counter ‘DSP’ Mode Slide 8 Product A B Select Enable 2: 1 MUX LUT 3 Multiplier Cell Carry Reg PPSI CIN ‘Network’ Muxing Mode LUT 3 A B Logic Out Reg 3 LUT Carry A B C D 4 LUT Sum 3 LUT A B CIN ‘Synthesis’ Mode OUT Switches AT 94 Training 2001

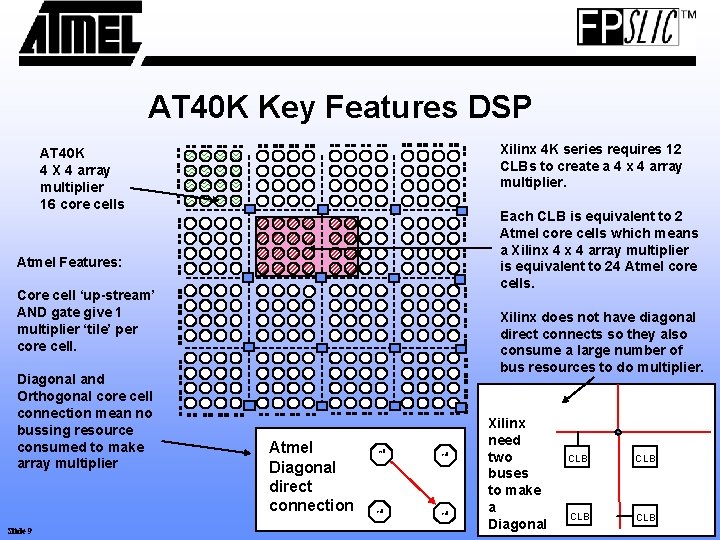

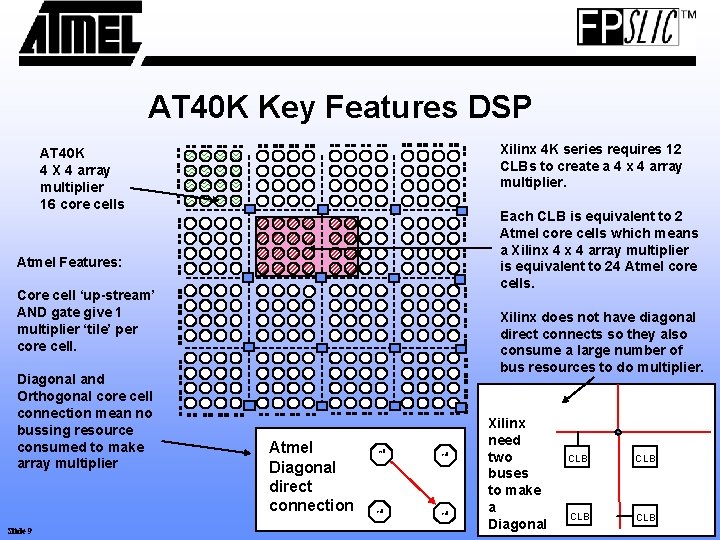

AT 40 K Key Features DSP Xilinx 4 K series requires 12 CLBs to create a 4 x 4 array multiplier. AT 40 K 4 X 4 array multiplier 16 core cells Each CLB is equivalent to 2 Atmel core cells which means a Xilinx 4 array multiplier is equivalent to 24 Atmel core cells. Atmel Features: Core cell ‘up-stream’ AND gate give 1 multiplier ‘tile’ per core cell. Diagonal and Orthogonal core cell connection mean no bussing resource consumed to make array multiplier Slide 9 Xilinx does not have diagonal direct connects so they also consume a large number of bus resources to do multiplier. Atmel Diagonal direct connection cell Xilinx need two buses to make a Diagonal CLB CLB AT 94 Training 2001

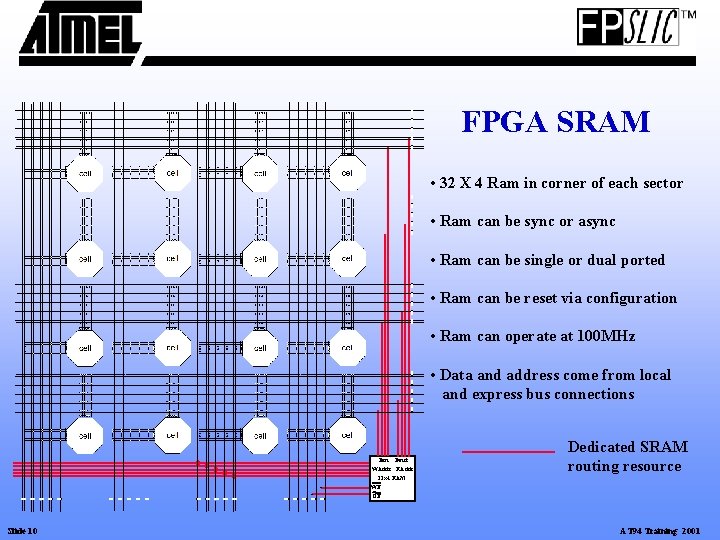

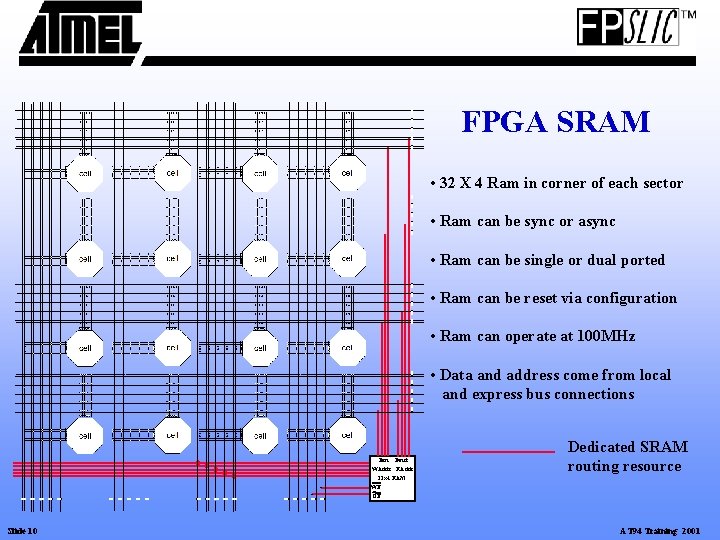

FPGA SRAM • 32 X 4 Ram in corner of each sector • Ram can be sync or async • Ram can be single or dual ported • Ram can be reset via configuration • Ram can operate at 100 MHz • Data and address come from local and express bus connections Din Dout WAddr RAddr Dedicated SRAM routing resource 32 x 4 RAM WE OE Slide 10 AT 94 Training 2001

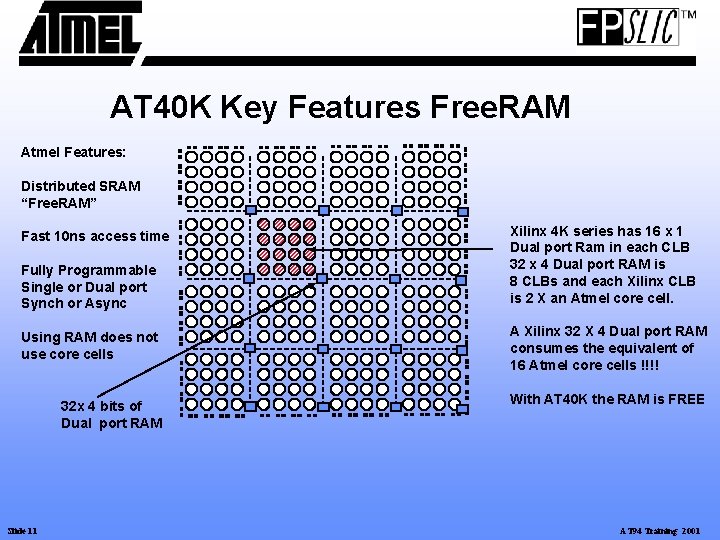

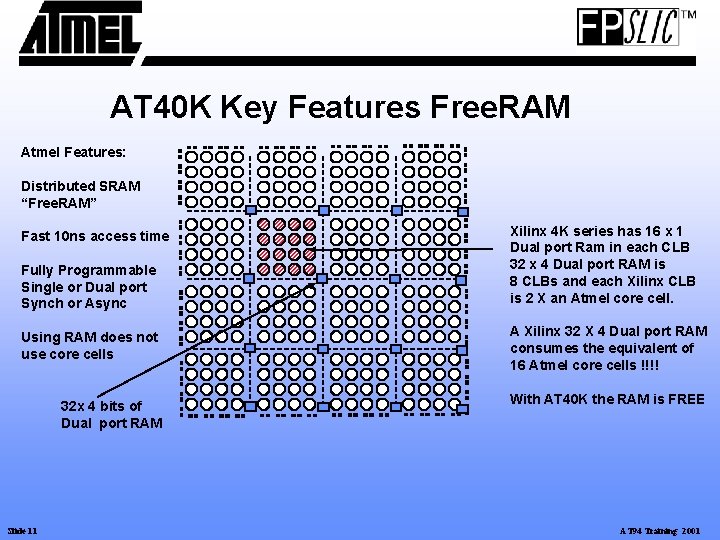

AT 40 K Key Features Free. RAM Atmel Features: Distributed SRAM “Free. RAM” Fast 10 ns access time Fully Programmable Single or Dual port Synch or Async Using RAM does not use core cells 32 x 4 bits of Dual port RAM Slide 11 Xilinx 4 K series has 16 x 1 Dual port Ram in each CLB 32 x 4 Dual port RAM is 8 CLBs and each Xilinx CLB is 2 X an Atmel core cell. A Xilinx 32 X 4 Dual port RAM consumes the equivalent of 16 Atmel core cells !!!! With AT 40 K the RAM is FREE AT 94 Training 2001

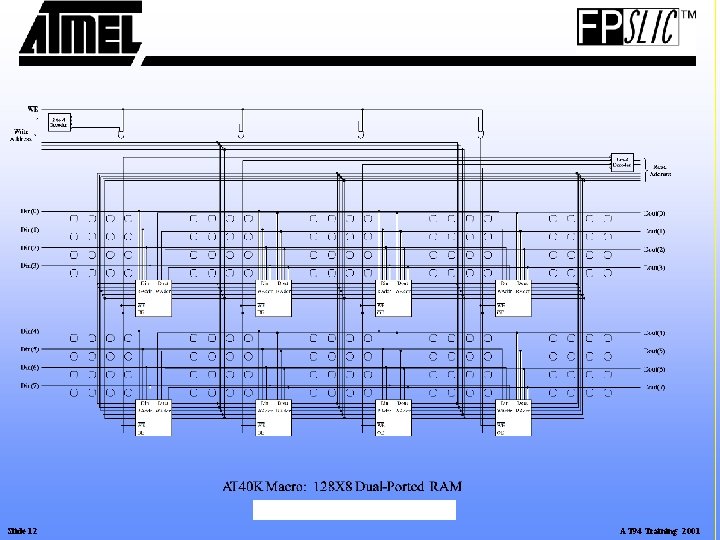

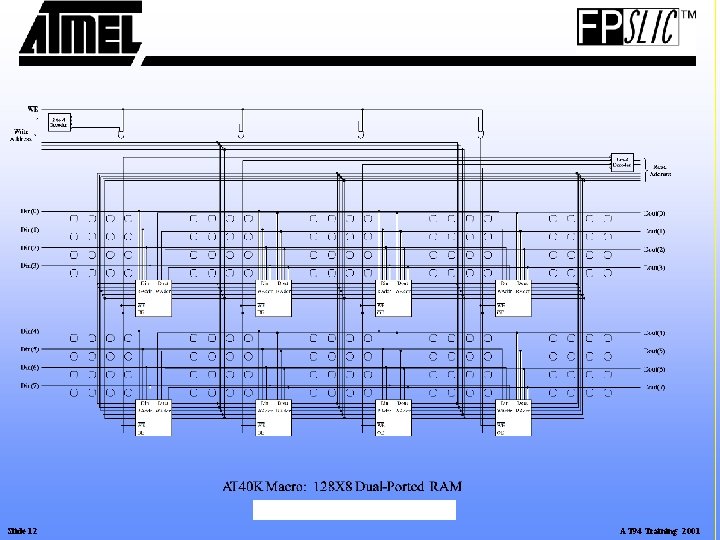

Slide 12 AT 94 Training 2001

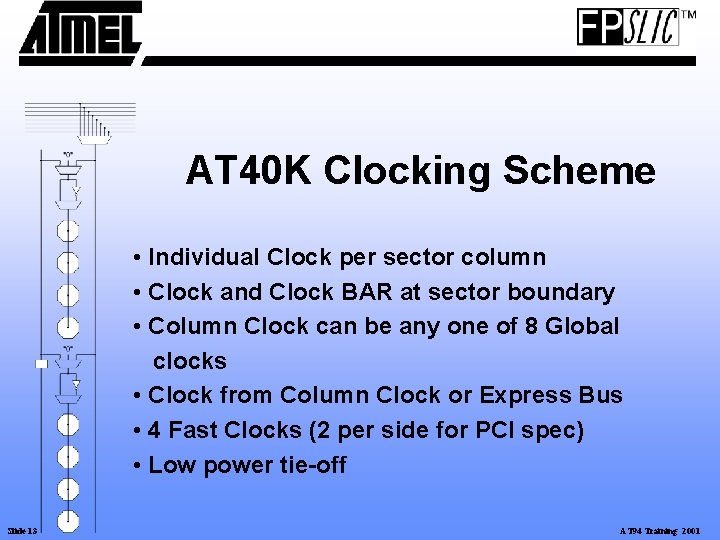

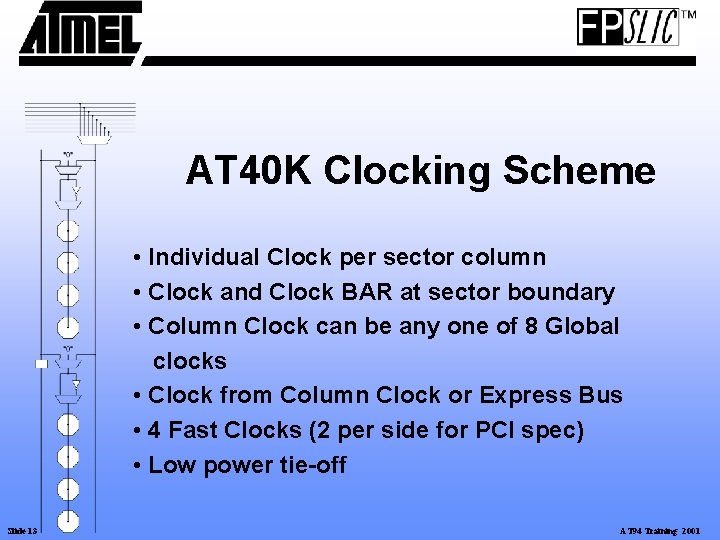

AT 40 K Clocking Scheme • Individual Clock per sector column • Clock and Clock BAR at sector boundary • Column Clock can be any one of 8 Global clocks • Clock from Column Clock or Express Bus • 4 Fast Clocks (2 per side for PCI spec) • Low power tie-off Slide 13 AT 94 Training 2001

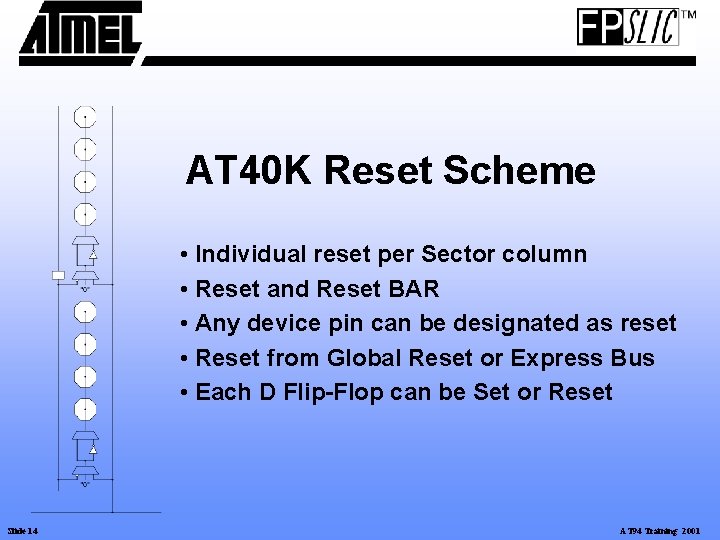

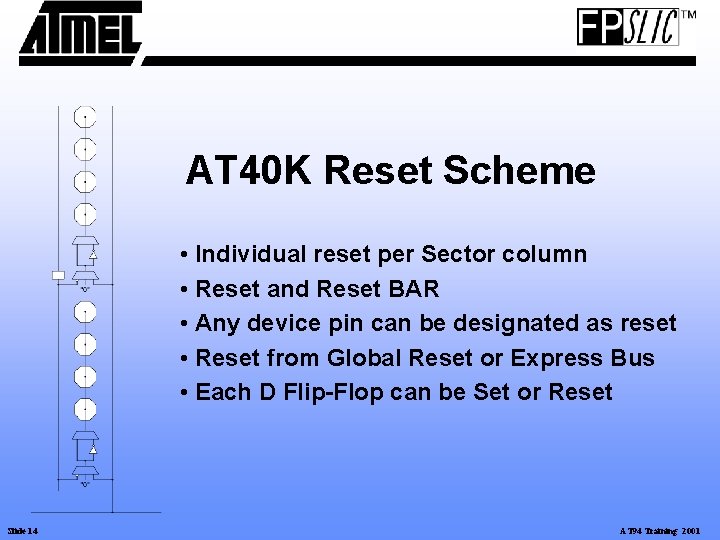

AT 40 K Reset Scheme • Individual reset per Sector column • Reset and Reset BAR • Any device pin can be designated as reset • Reset from Global Reset or Express Bus • Each D Flip-Flop can be Set or Reset Slide 14 AT 94 Training 2001

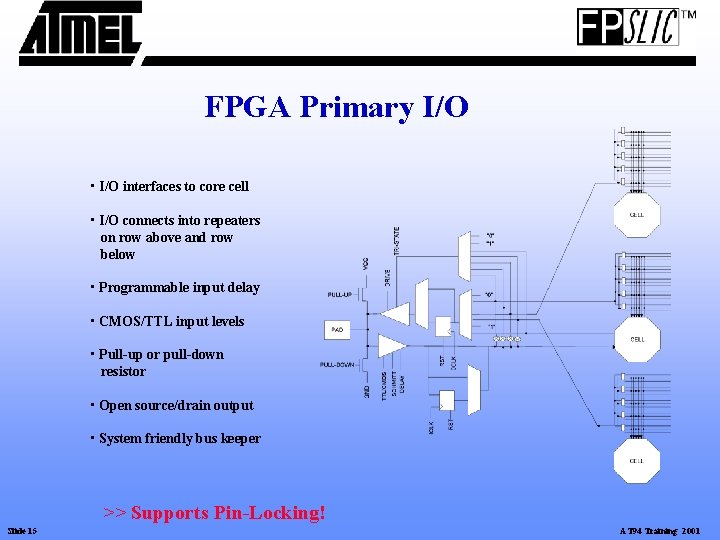

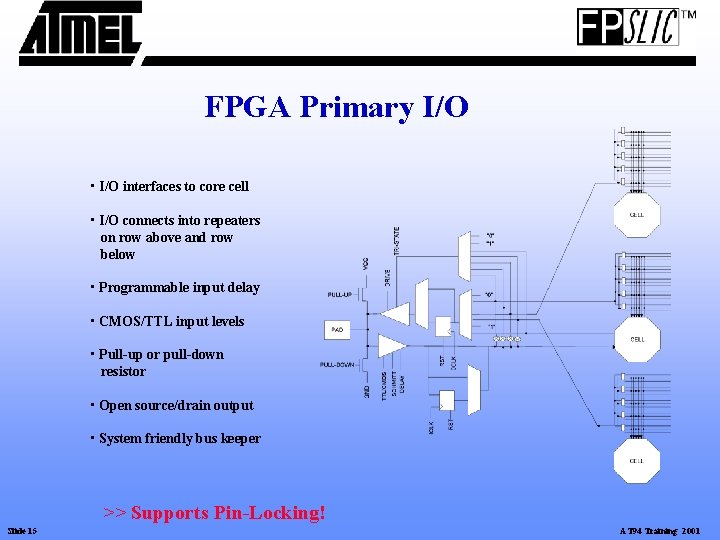

FPGA Primary I/O • I/O interfaces to core cell • I/O connects into repeaters on row above and row below • Programmable input delay • CMOS/TTL input levels • Pull-up or pull-down resistor • Open source/drain output • System friendly bus keeper >> Supports Pin-Locking! Slide 15 AT 94 Training 2001

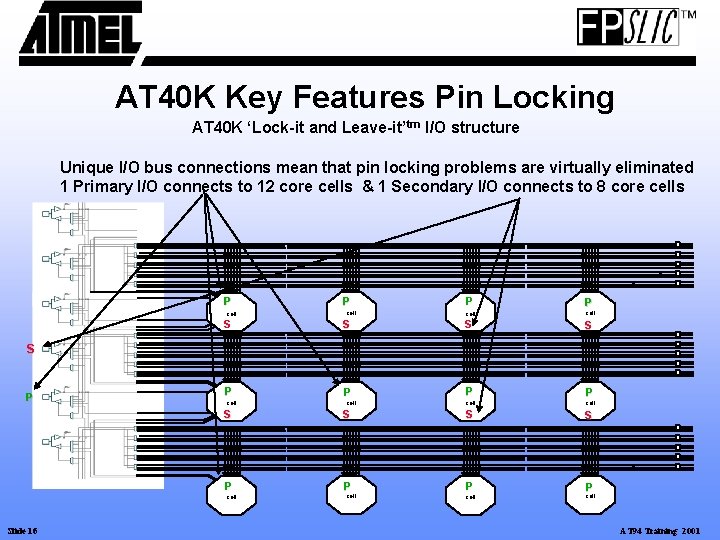

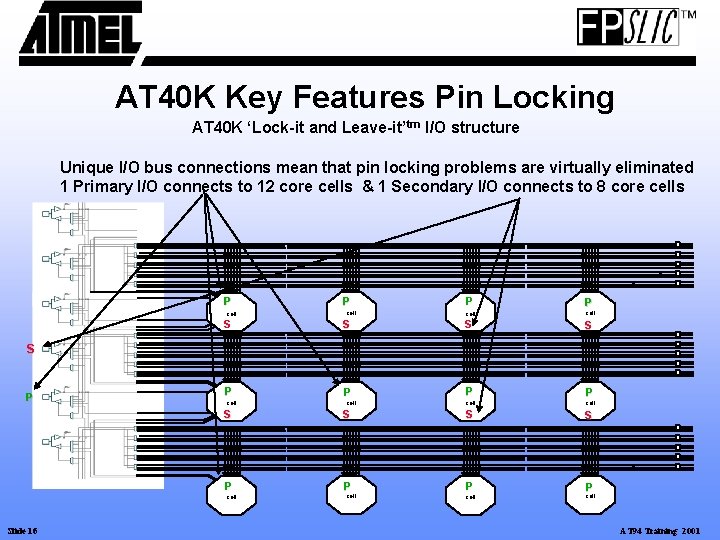

AT 40 K Key Features Pin Locking AT 40 K ‘Lock-it and Leave-it’tm I/O structure Unique I/O bus connections mean that pin locking problems are virtually eliminated 1 Primary I/O connects to 12 core cells & 1 Secondary I/O connects to 8 core cells P cell S S P P cell S S S P cell S S P P cell Slide 16 cell P P cell S S P cell AT 94 Training 2001

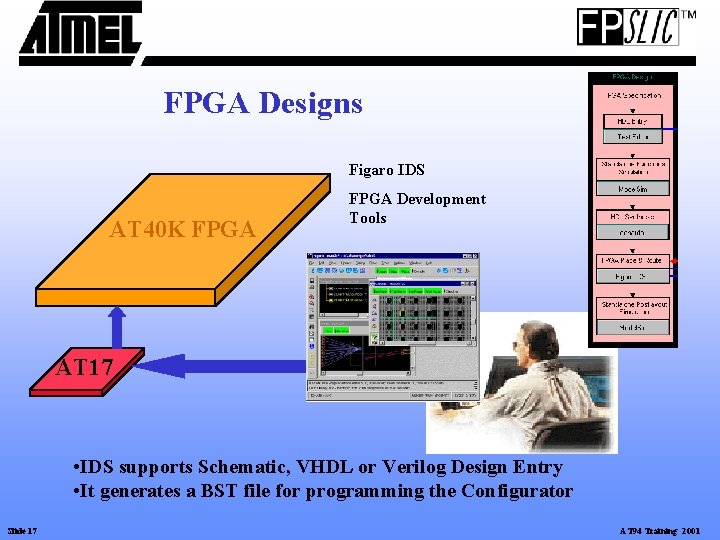

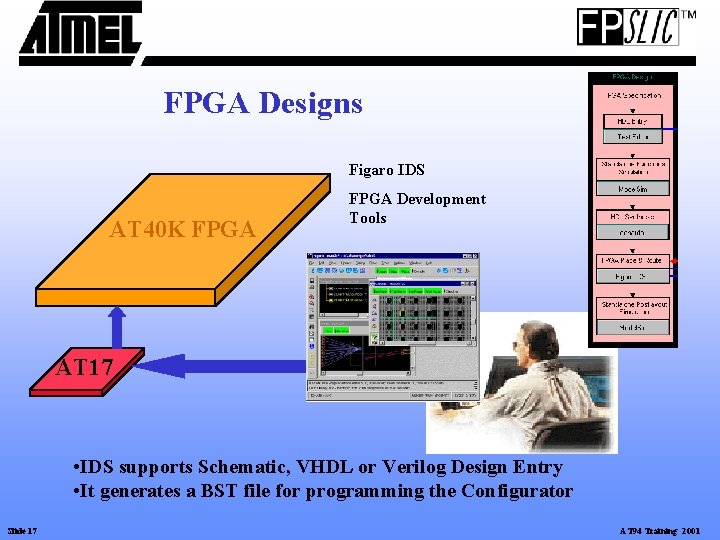

FPGA Designs Figaro IDS AT 40 K FPGA Development Tools AT 17 • IDS supports Schematic, VHDL or Verilog Design Entry • It generates a BST file for programming the Configurator Slide 17 AT 94 Training 2001

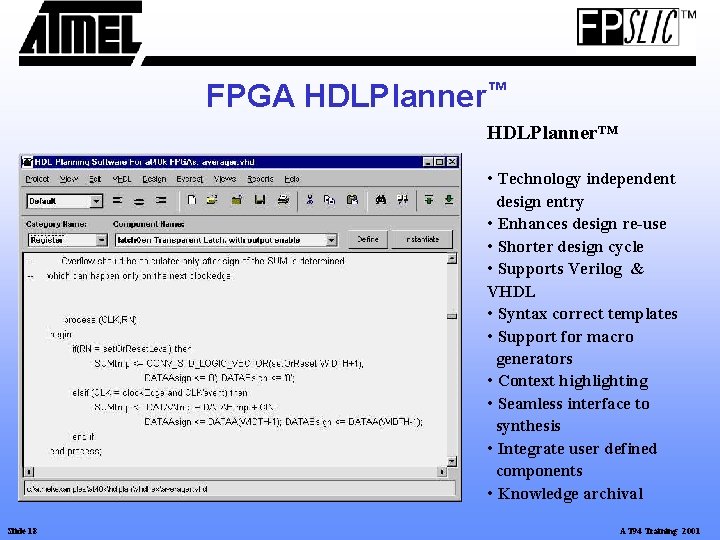

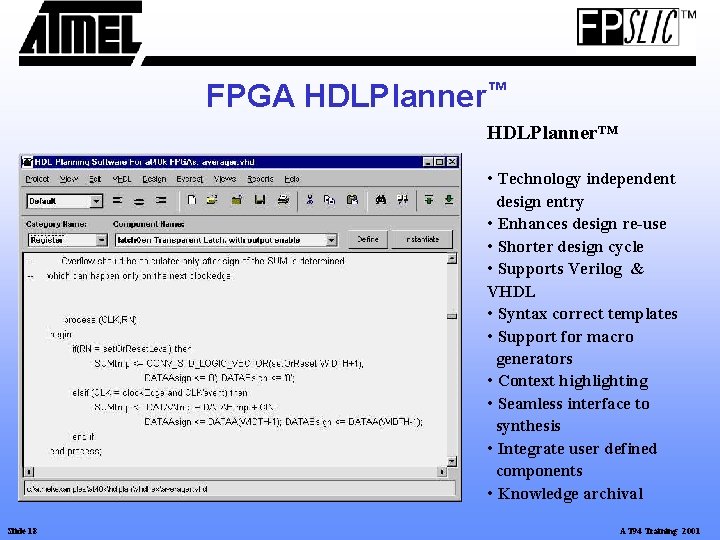

FPGA HDLPlanner™ • Technology independent design entry • Enhances design re-use • Shorter design cycle • Supports Verilog & VHDL • Syntax correct templates • Support for macro generators • Context highlighting • Seamless interface to synthesis • Integrate user defined components • Knowledge archival Slide 18 AT 94 Training 2001

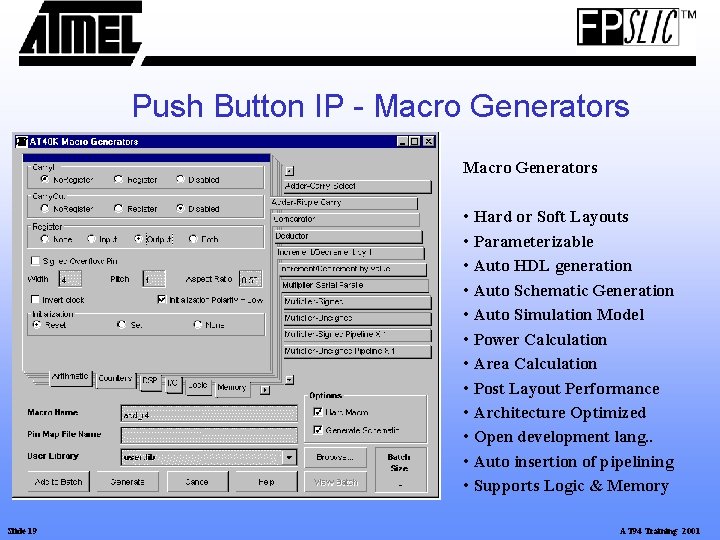

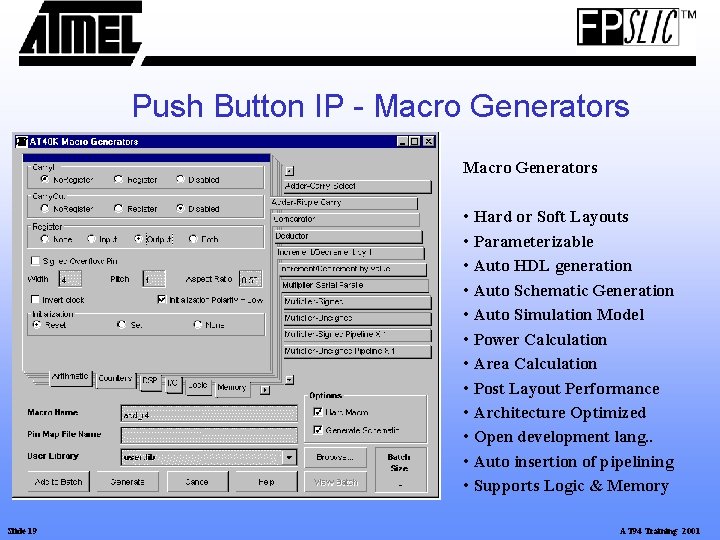

Push Button IP - Macro Generators • Hard or Soft Layouts • Parameterizable • Auto HDL generation • Auto Schematic Generation • Auto Simulation Model • Power Calculation • Area Calculation • Post Layout Performance • Architecture Optimized • Open development lang. . • Auto insertion of pipelining • Supports Logic & Memory Slide 19 AT 94 Training 2001

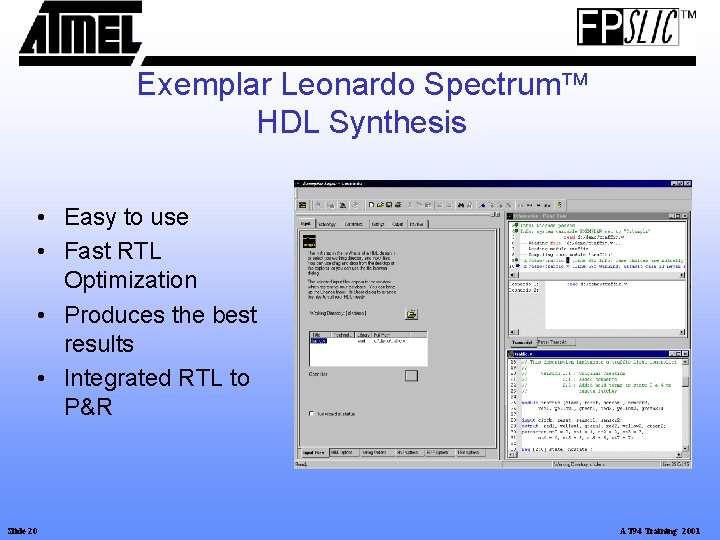

Exemplar Leonardo Spectrum HDL Synthesis • Easy to use • Fast RTL Optimization • Produces the best results • Integrated RTL to P&R Slide 20 AT 94 Training 2001

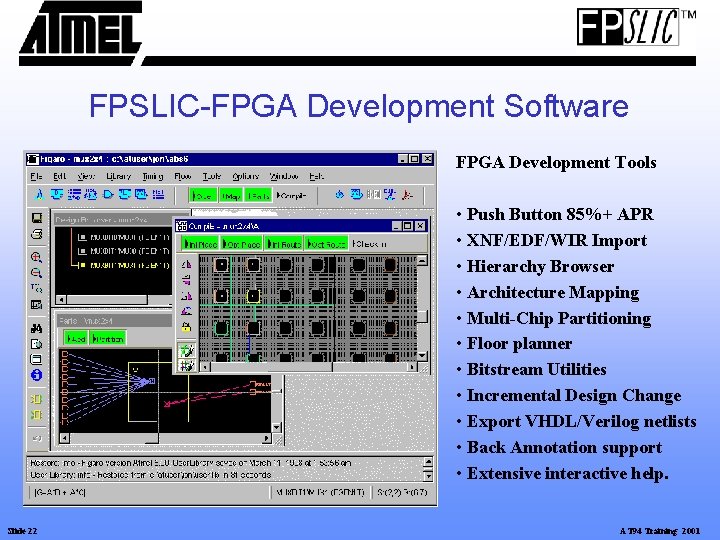

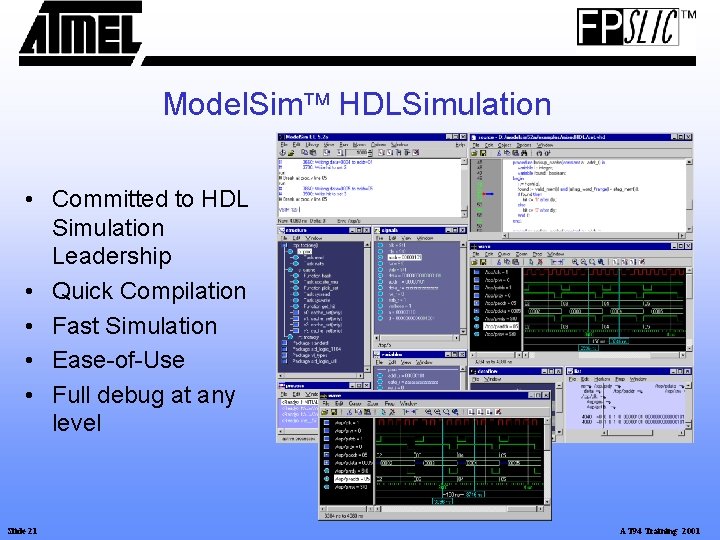

Model. Sim HDLSimulation • Committed to HDL Simulation Leadership • Quick Compilation • Fast Simulation • Ease-of-Use • Full debug at any level Slide 21 AT 94 Training 2001

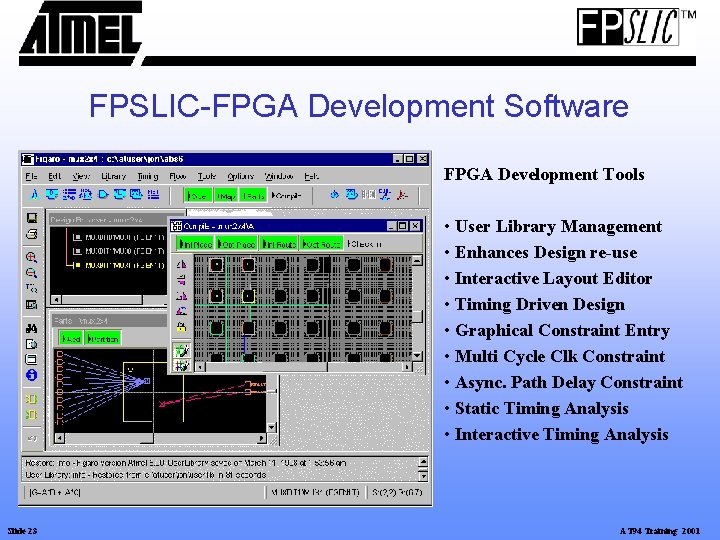

FPSLIC-FPGA Development Software FPGA Development Tools • Push Button 85%+ APR • XNF/EDF/WIR Import • Hierarchy Browser • Architecture Mapping • Multi-Chip Partitioning • Floor planner • Bitstream Utilities • Incremental Design Change • Export VHDL/Verilog netlists • Back Annotation support • Extensive interactive help. Slide 22 AT 94 Training 2001

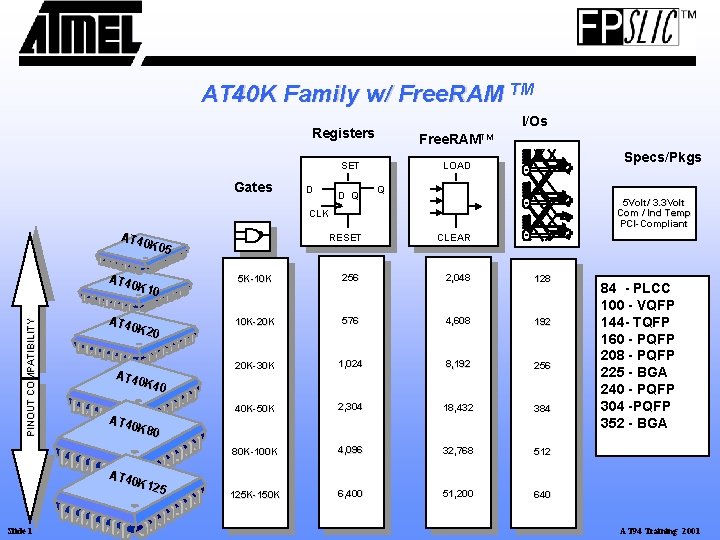

FPSLIC-FPGA Development Software FPGA Development Tools • User Library Management • Enhances Design re-use • Interactive Layout Editor • Timing Driven Design • Graphical Constraint Entry • Multi Cycle Clk Constraint • Async. Path Delay Constraint • Static Timing Analysis • Interactive Timing Analysis Slide 23 AT 94 Training 2001