AT 17 Series EEPROM Configuration Memories Atmel Corporation

- Slides: 44

AT 17 Series EEPROM Configuration Memories Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 Hotline (408) 436 -4119 fpga@atmel. com OR configurator@atmel. com Slide 1 AT 94 Training 2001

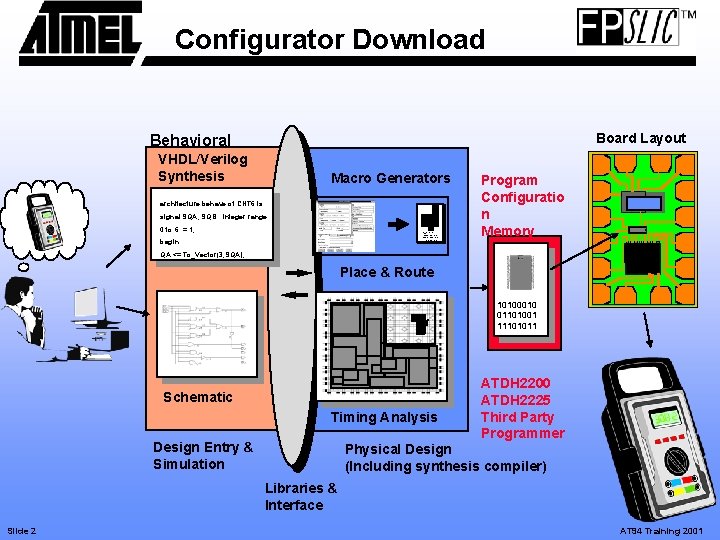

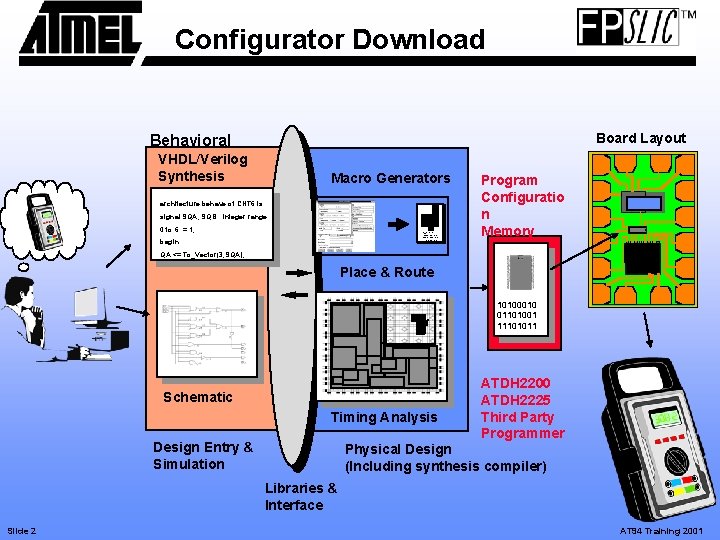

Configurator Download Board Layout Behavioral VHDL/Verilog Synthesis Macro Generators architecture behave of CNT 6 is signal SQA, SQB : integer range 0 to 6 : = 1; Tpd = 10 ns Fmax = 100 MHz Size = 12 x 8 Cells Icc =. 2 m. A/MHz begin Program Configuratio n Memory QA <= To_Vector(3, SQA); Place & Route 10100010 01101001 11101011 Schematic Timing Analysis Design Entry & Simulation ATDH 2200 ATDH 2225 Third Party Programmer Physical Design (Including synthesis compiler) Libraries & Interface Slide 2 AT 94 Training 2001

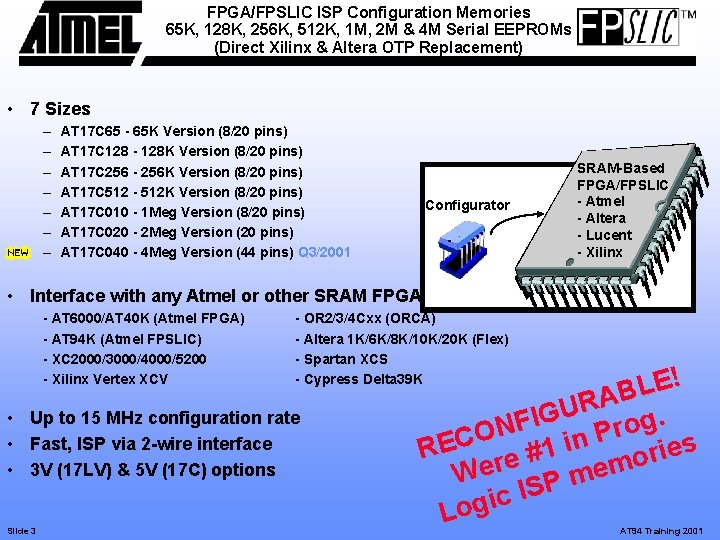

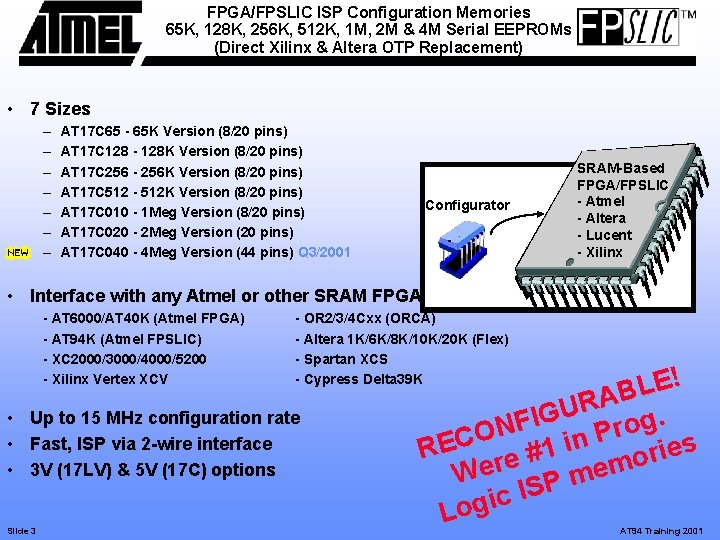

FPGA/FPSLIC ISP Configuration Memories 65 K, 128 K, 256 K, 512 K, 1 M, 2 M & 4 M Serial EEPROMs (Direct Xilinx & Altera OTP Replacement) • 7 Sizes – – – – AT 17 C 65 - 65 K Version (8/20 pins) AT 17 C 128 - 128 K Version (8/20 pins) AT 17 C 256 - 256 K Version (8/20 pins) AT 17 C 512 - 512 K Version (8/20 pins) AT 17 C 010 - 1 Meg Version (8/20 pins) AT 17 C 020 - 2 Meg Version (20 pins) AT 17 C 040 - 4 Meg Version (44 pins) Q 3/2001 Configurator SRAM-Based FPGA/FPSLIC - Atmel - Altera - Lucent - Xilinx • Interface with any Atmel or other SRAM FPGA & FPSLIC - AT 6000/AT 40 K (Atmel FPGA) - AT 94 K (Atmel FPSLIC) - XC 2000/3000/4000/5200 - Xilinx Vertex XCV - OR 2/3/4 Cxx (ORCA) - Altera 1 K/6 K/8 K/10 K/20 K (Flex) - Spartan XCS - Cypress Delta 39 K • Up to 15 MHz configuration rate • Fast, ISP via 2 -wire interface • 3 V (17 LV) & 5 V (17 C) options Slide 3 ! E L B A R U G. I g F o N r O P C n i s E e 1 R i r # o e r e em W m P S I c i Log AT 94 Training 2001

Key Features and Benefits • ISP 5 V or 3. 3 V • Fast programming up to 15 MHz • Cascade – Multiple devices can be cascaded. • Reconfigurable FPGA Memory – EEPROM is priced competitively with OTP products • Two Parts in One – AT 17 Cxxx can also emulate 24 Cxxx parts • In System (Re)Programmable Easy system hook-up for ISP operation – Can be soldered to PCB - no socket required Slide 4 AT 94 Training 2001

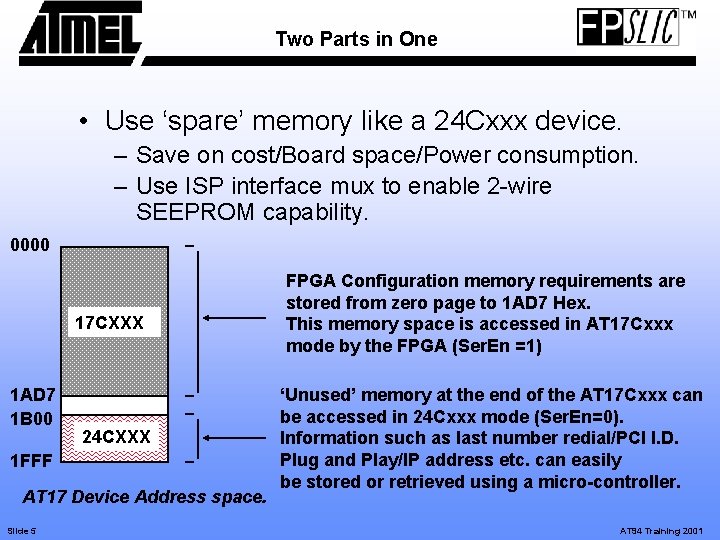

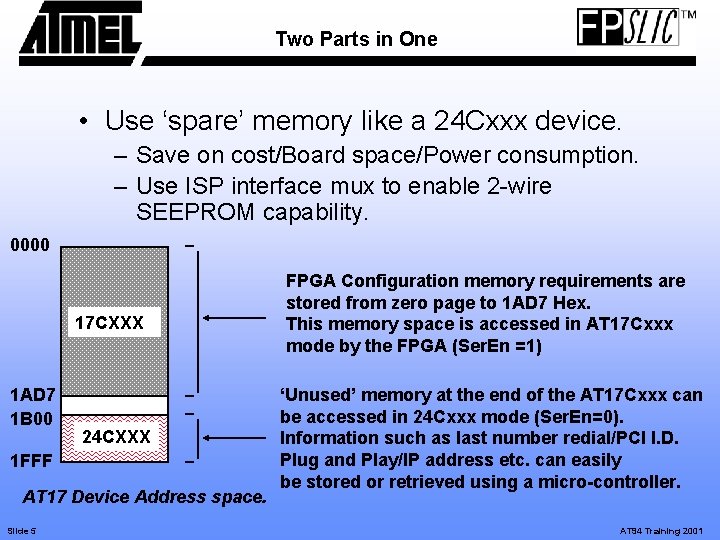

Two Parts in One • Use ‘spare’ memory like a 24 Cxxx device. – Save on cost/Board space/Power consumption. – Use ISP interface mux to enable 2 -wire SEEPROM capability. 0000 17 CXXX 1 AD 7 1 B 00 24 CXXX 1 FFF AT 17 Device Address space. Slide 5 FPGA Configuration memory requirements are stored from zero page to 1 AD 7 Hex. This memory space is accessed in AT 17 Cxxx mode by the FPGA (Ser. En =1) ‘Unused’ memory at the end of the AT 17 Cxxx can be accessed in 24 Cxxx mode (Ser. En=0). Information such as last number redial/PCI I. D. Plug and Play/IP address etc. can easily be stored or retrieved using a micro-controller. AT 94 Training 2001

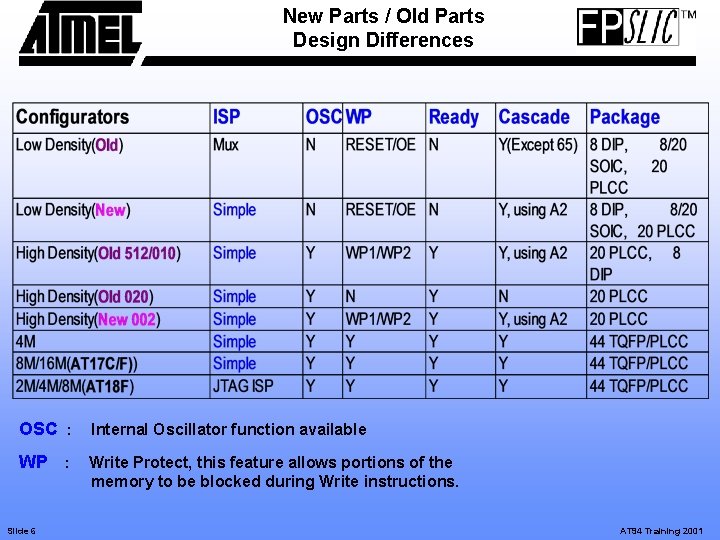

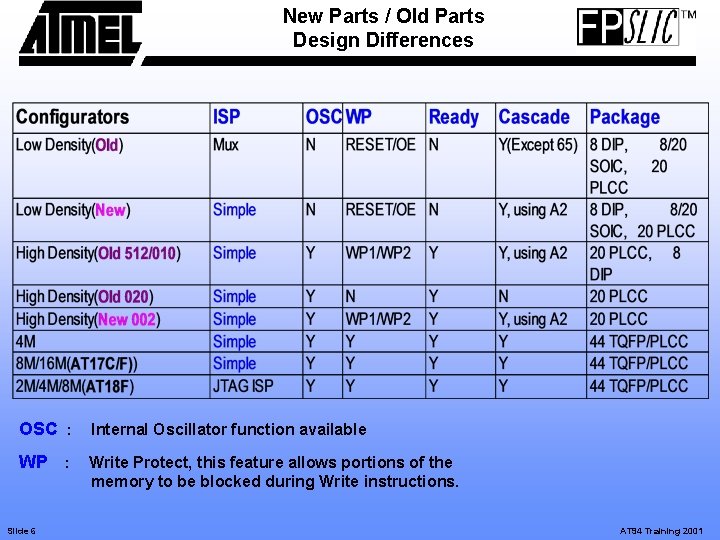

New Parts / Old Parts Design Differences OSC : Internal Oscillator function available WP : Write Protect, this feature allows portions of the memory to be blocked during Write instructions. Slide 6 AT 94 Training 2001

Configurator Availability Atmel & Xilinx Versions Slide 7 • AT 17 C/F series = 2 -wire serial ISP • AT 18 F series = JTAG ISP AT 94 Training 2001

Configurator Availability Altera Versions Slide 8 • AT 17 C/F series = 2 -wire serial ISP • AT 18 F series = JTAG ISP AT 94 Training 2001

ISP Programming Use Mux for ISP circuit Figure 1: In-System Programming of AT 17 C/LV 65/128/256 (old) EEPROM in AT 40 K FPGA Application Slide 9 Simple ISP circuit Figure 2: In-System Programming of AT 17 C/LV 65/128/256 (new) EEPROM in AT 40 K FPGA Application AT 94 Training 2001

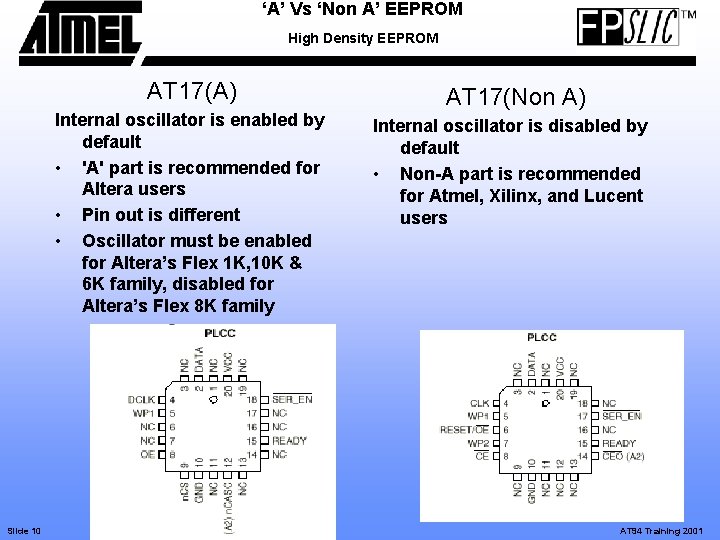

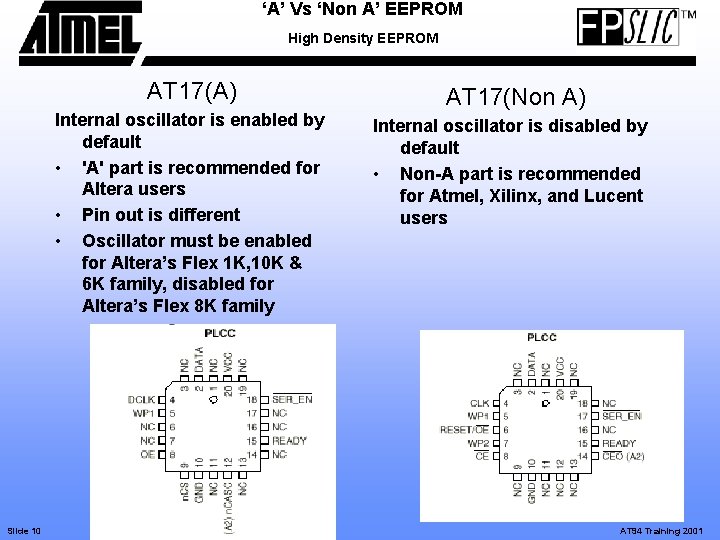

‘A’ Vs ‘Non A’ EEPROM High Density EEPROM AT 17(A) Internal oscillator is enabled by default • 'A' part is recommended for Altera users • Pin out is different • Oscillator must be enabled for Altera’s Flex 1 K, 10 K & 6 K family, disabled for Altera’s Flex 8 K family Slide 10 AT 17(Non A) Internal oscillator is disabled by default • Non-A part is recommended for Atmel, Xilinx, and Lucent users AT 94 Training 2001

Programming Options • ATDH 2200 board for ISP and stand-alone device programming • ATDH 2225 for ISP - Recommended for Atmel custom board layout - Allows cascading controlled by software • Broad third party programmer support – Faster to program than OTP parts • Source Code is available - For development of Microcontrolled programming Slide 11 AT 94 Training 2001

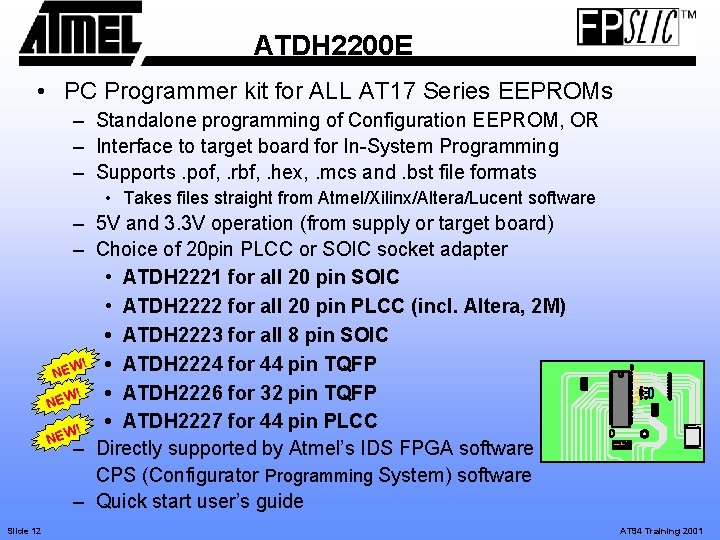

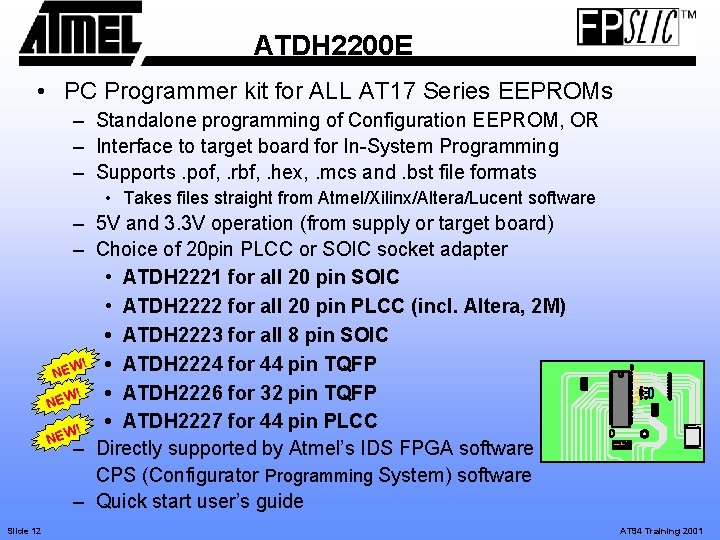

ATDH 2200 E • PC Programmer kit for ALL AT 17 Series EEPROMs – Standalone programming of Configuration EEPROM, OR – Interface to target board for In-System Programming – Supports. pof, . rbf, . hex, . mcs and. bst file formats • Takes files straight from Atmel/Xilinx/Altera/Lucent software – 5 V and 3. 3 V operation (from supply or target board) – Choice of 20 pin PLCC or SOIC socket adapter • ATDH 2221 for all 20 pin SOIC • ATDH 2222 for all 20 pin PLCC (incl. Altera, 2 M) • ATDH 2223 for all 8 pin SOIC ! • ATDH 2224 for 44 pin TQFP NEW ! • ATDH 2226 for 32 pin TQFP NEW • ATDH 2227 for 44 pin PLCC ! W E N – Directly supported by Atmel’s IDS FPGA software CPS (Configurator Programming System) software – Quick start user’s guide Slide 12 AT 94 Training 2001

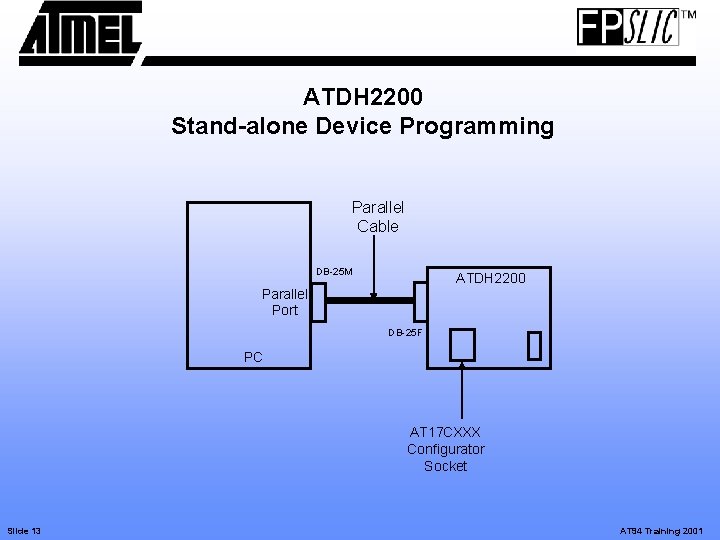

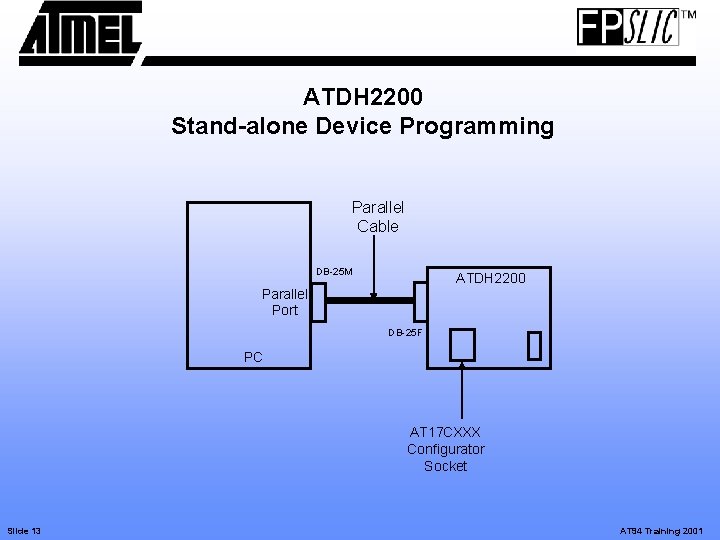

ATDH 2200 Stand-alone Device Programming Parallel Cable DB-25 M ATDH 2200 Parallel Port DB-25 F PC AT 17 CXXX Configurator Socket Slide 13 AT 94 Training 2001

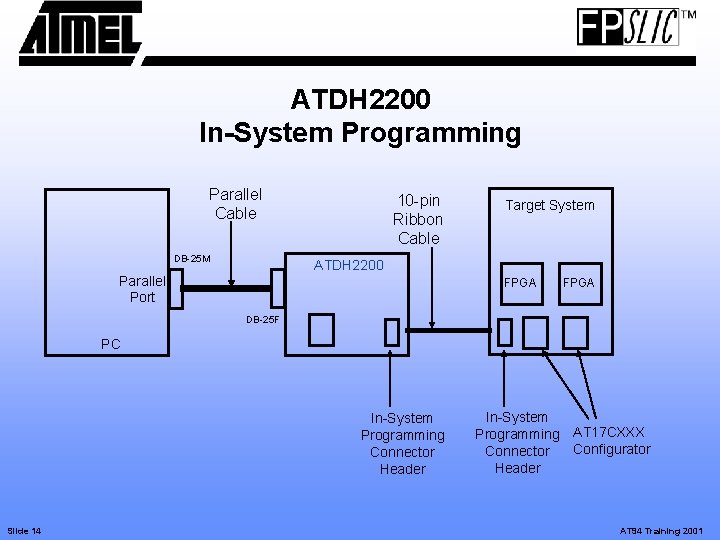

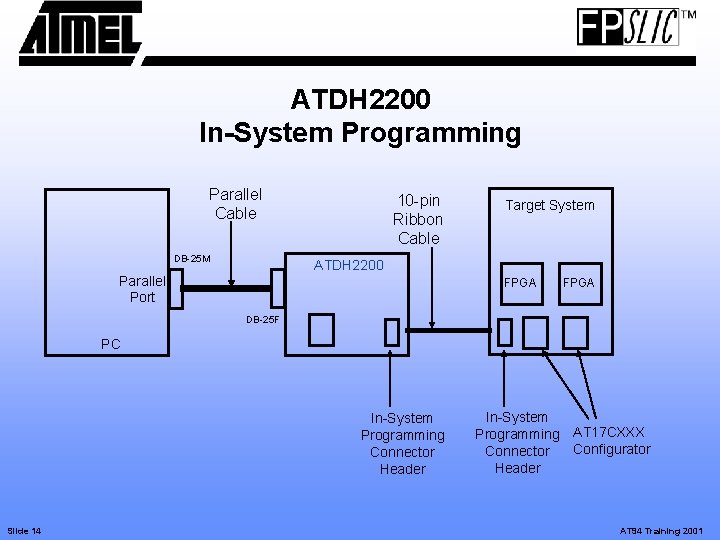

ATDH 2200 In-System Programming Parallel Cable DB-25 M 10 -pin Ribbon Cable Target System ATDH 2200 Parallel Port FPGA DB-25 F PC In-System Programming Connector Header Slide 14 In-System Programming AT 17 CXXX Configurator Connector Header AT 94 Training 2001

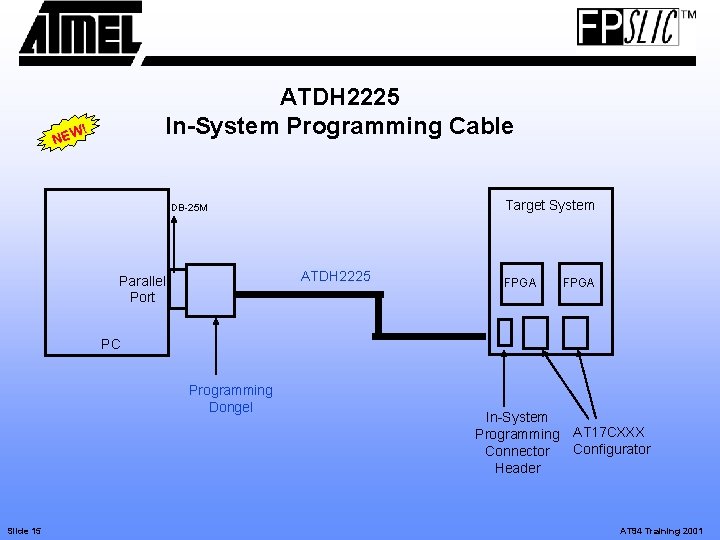

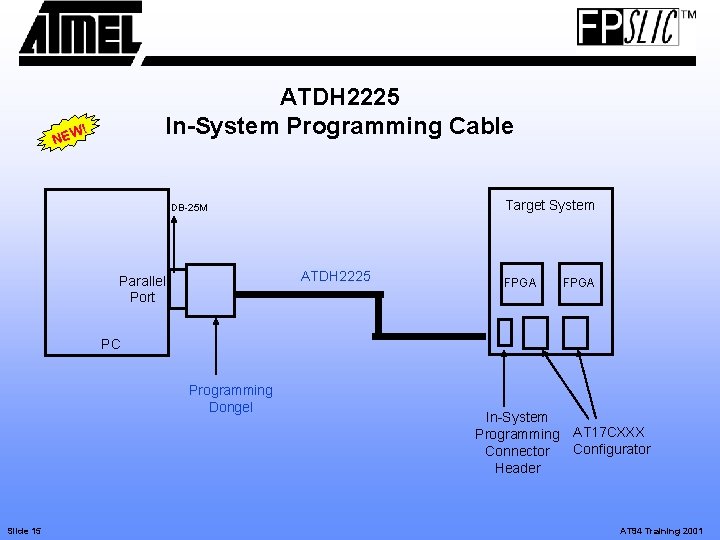

ATDH 2225 In-System Programming Cable ! NEW Target System DB-25 M ATDH 2225 Parallel Port FPGA PC Programming Dongel Slide 15 In-System Programming AT 17 CXXX Configurator Connector Header AT 94 Training 2001

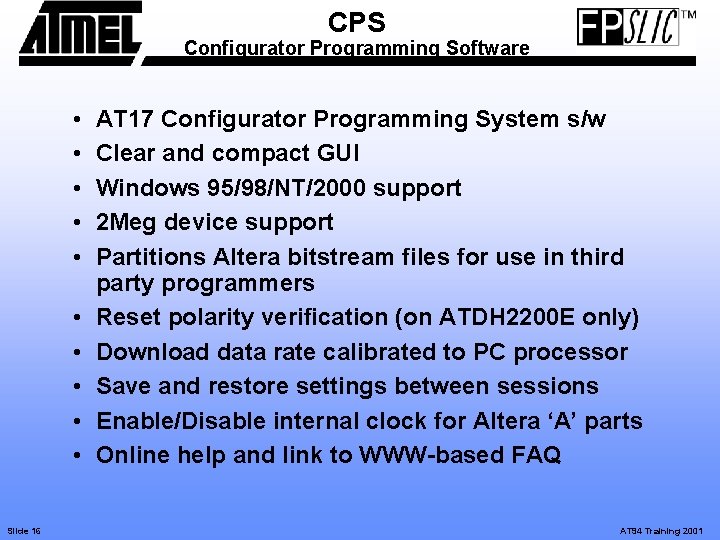

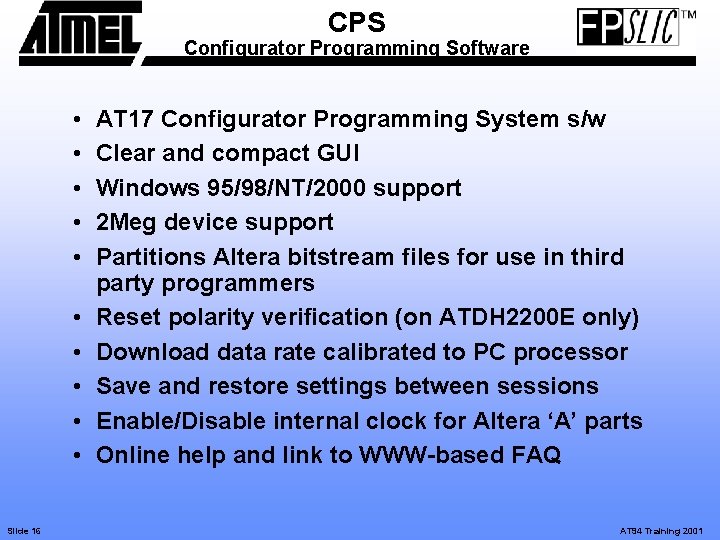

CPS Configurator Programming Software • • • Slide 16 AT 17 Configurator Programming System s/w Clear and compact GUI Windows 95/98/NT/2000 support 2 Meg device support Partitions Altera bitstream files for use in third party programmers Reset polarity verification (on ATDH 2200 E only) Download data rate calibrated to PC processor Save and restore settings between sessions Enable/Disable internal clock for Altera ‘A’ parts Online help and link to WWW-based FAQ AT 94 Training 2001

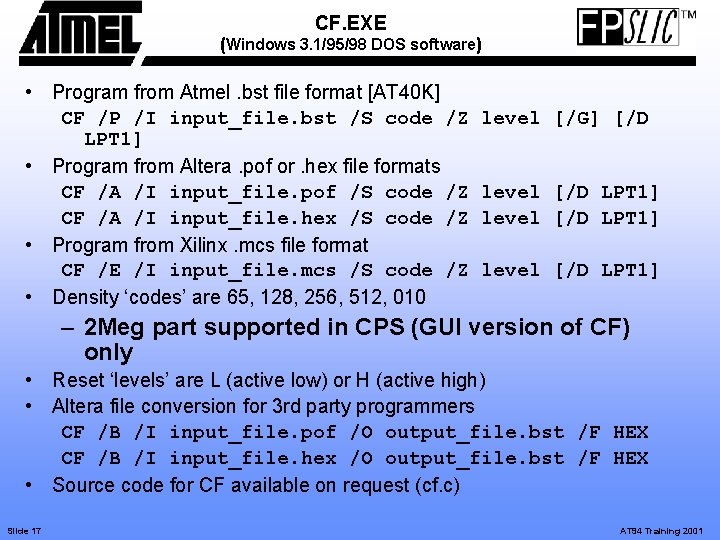

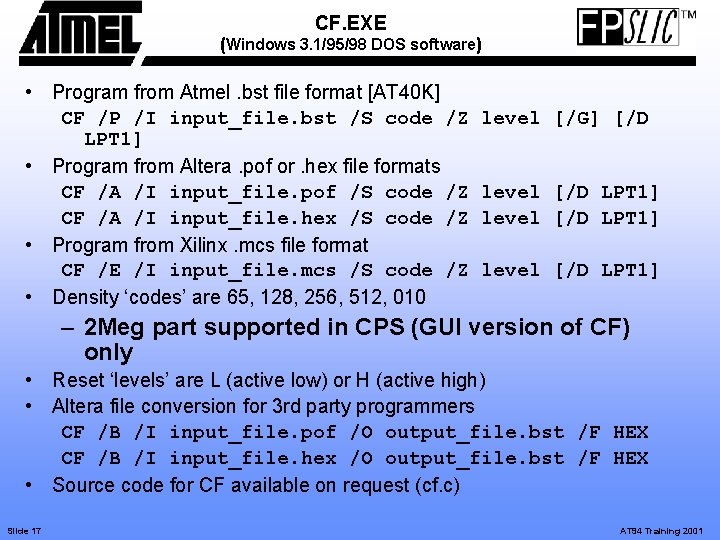

CF. EXE (Windows 3. 1/95/98 DOS software) • Program from Atmel. bst file format [AT 40 K] CF /P /I input_file. bst /S code /Z LPT 1] • Program from Altera. pof or. hex file formats CF /A /I input_file. pof /S code /Z CF /A /I input_file. hex /S code /Z • Program from Xilinx. mcs file format CF /E /I input_file. mcs /S code /Z • Density ‘codes’ are 65, 128, 256, 512, 010 level [/G] [/D level [/D LPT 1] – 2 Meg part supported in CPS (GUI version of CF) only • Reset ‘levels’ are L (active low) or H (active high) • Altera file conversion for 3 rd party programmers CF /B /I input_file. pof /O output_file. bst /F HEX CF /B /I input_file. hex /O output_file. bst /F HEX • Source code for CF available on request (cf. c) Slide 17 AT 94 Training 2001

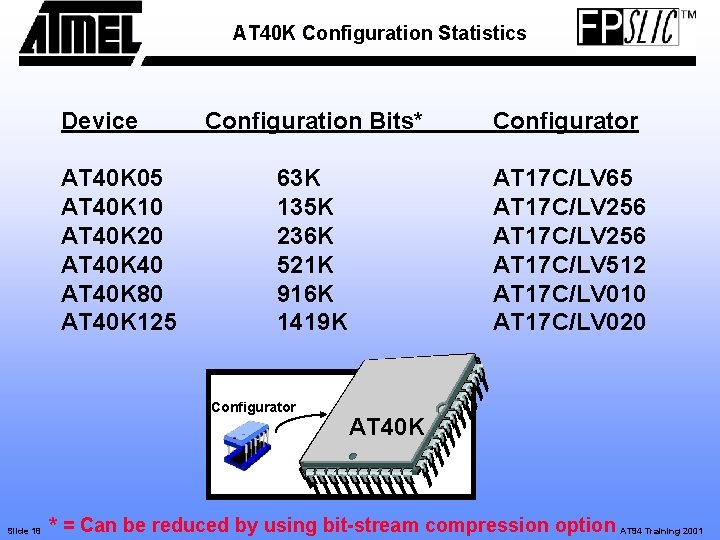

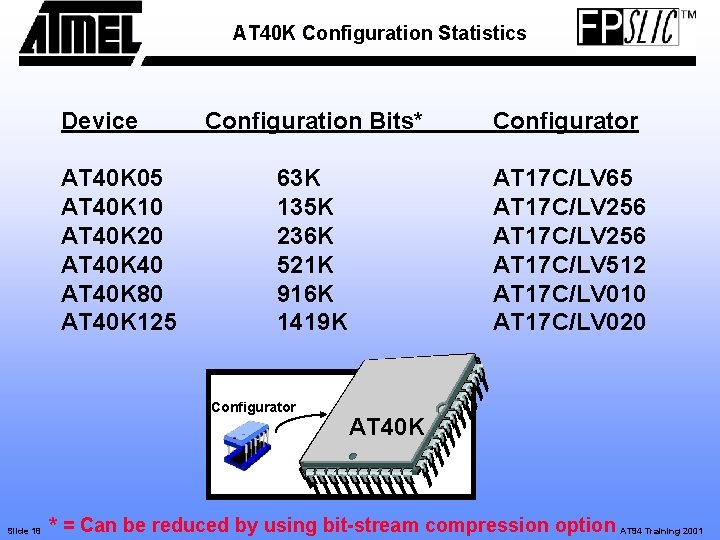

AT 40 K Configuration Statistics Device AT 40 K 05 AT 40 K 10 AT 40 K 20 AT 40 K 40 AT 40 K 80 AT 40 K 125 Configuration Bits* Configurator 63 K 135 K 236 K 521 K 916 K 1419 K AT 17 C/LV 65 AT 17 C/LV 256 AT 17 C/LV 512 AT 17 C/LV 010 AT 17 C/LV 020 Configurator Slide 18 AT 40 K * = Can be reduced by using bit-stream compression option AT 94 Training 2001

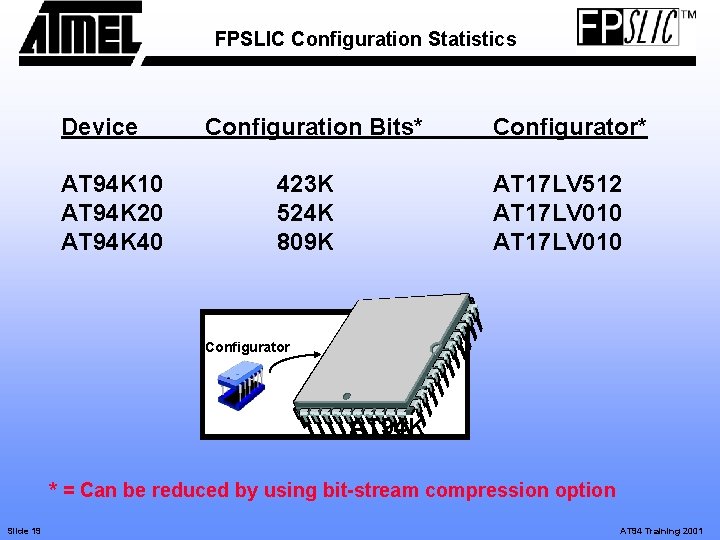

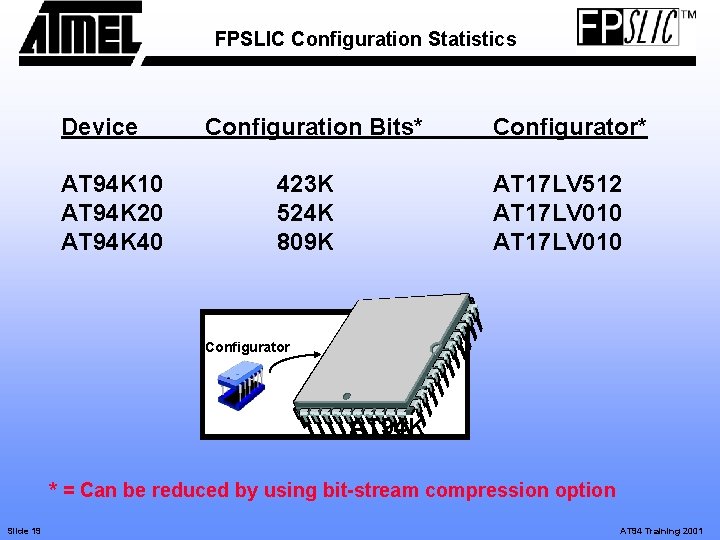

FPSLIC Configuration Statistics Device AT 94 K 10 AT 94 K 20 AT 94 K 40 Configuration Bits* 423 K 524 K 809 K Configurator* AT 17 LV 512 AT 17 LV 010 Configurator AT 94 K * = Can be reduced by using bit-stream compression option Slide 19 AT 94 Training 2001

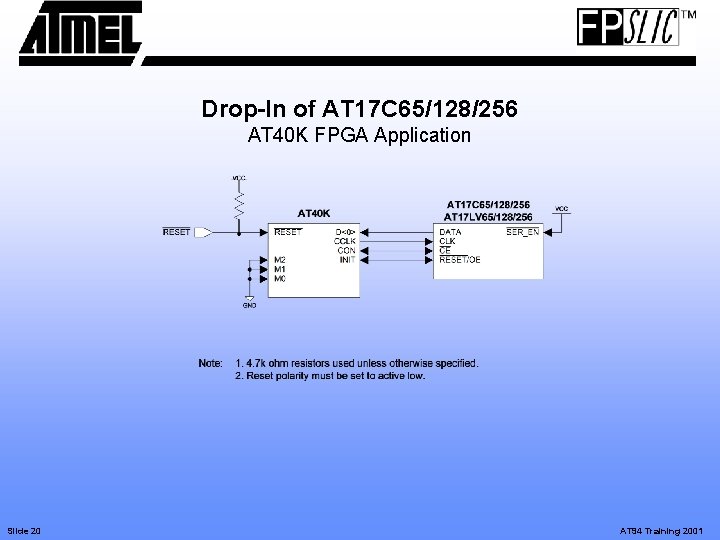

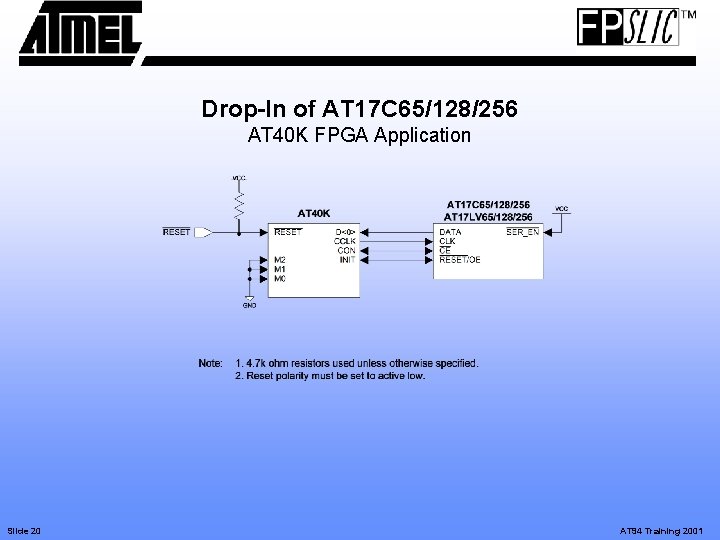

Drop-In of AT 17 C 65/128/256 AT 40 K FPGA Application Slide 20 AT 94 Training 2001

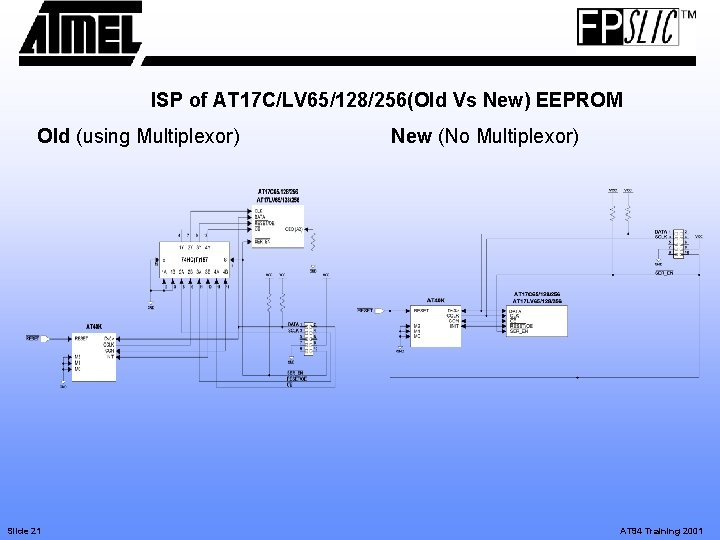

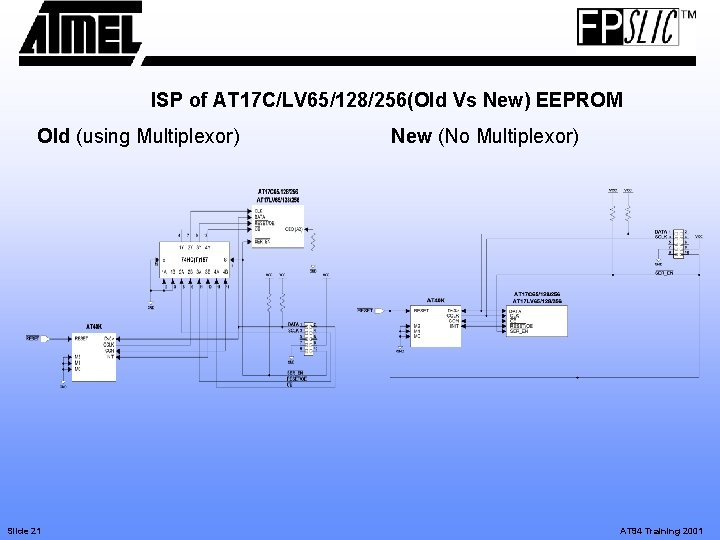

ISP of AT 17 C/LV 65/128/256(Old Vs New) EEPROM Old (using Multiplexor) Slide 21 New (No Multiplexor) AT 94 Training 2001

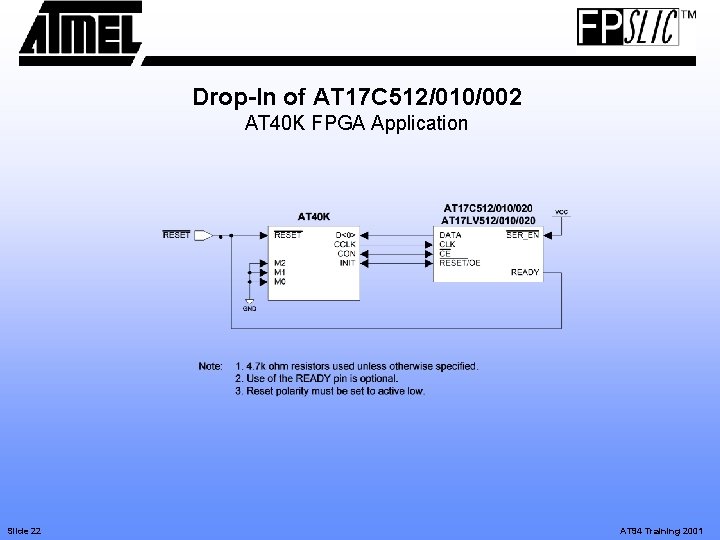

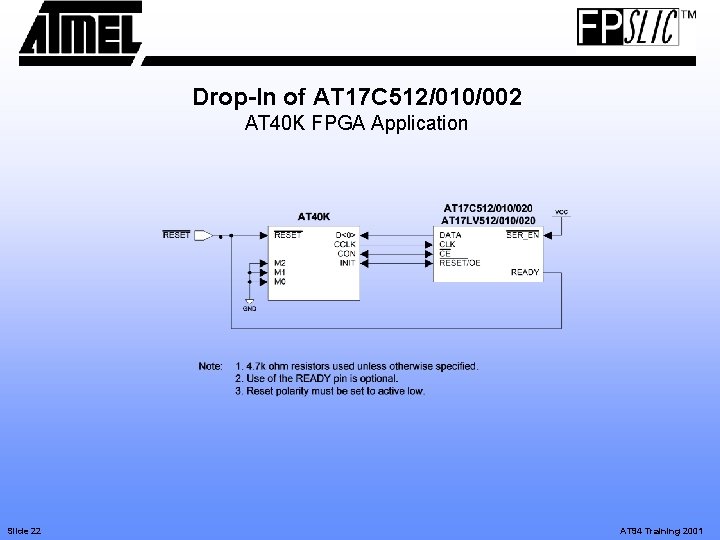

Drop-In of AT 17 C 512/010/002 AT 40 K FPGA Application Slide 22 AT 94 Training 2001

In-System Programming of the AT 17 C/LV 512/010/002 AT 40 K FPGA Application Slide 23 AT 94 Training 2001

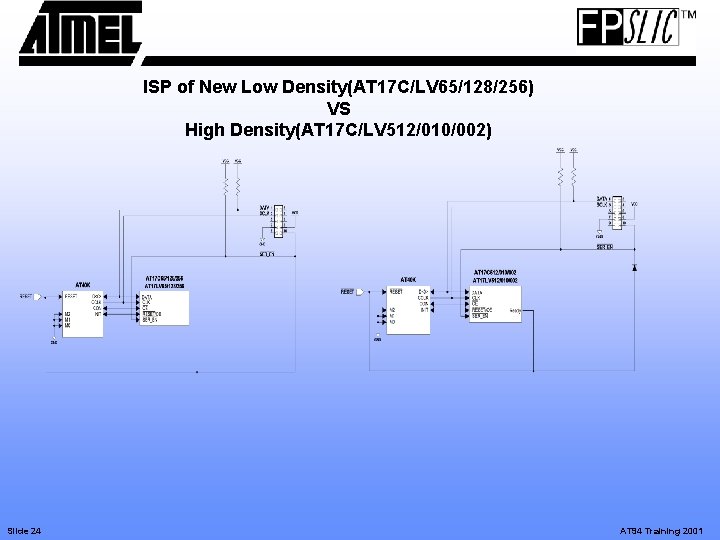

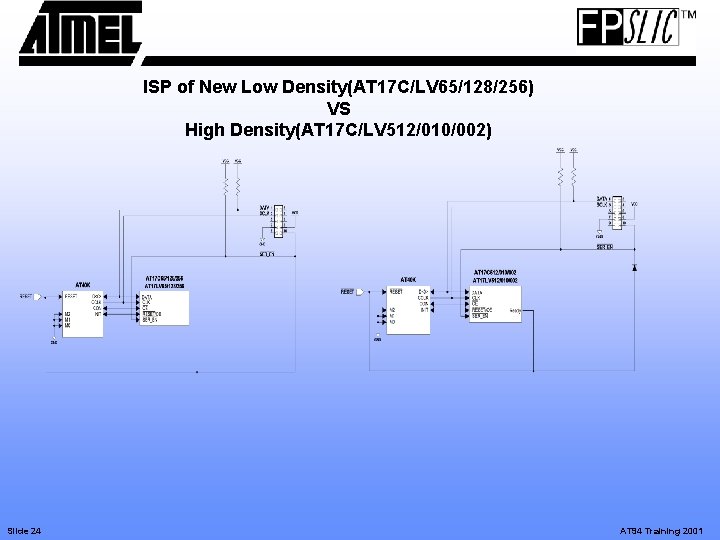

ISP of New Low Density(AT 17 C/LV 65/128/256) VS High Density(AT 17 C/LV 512/010/002) Slide 24 AT 94 Training 2001

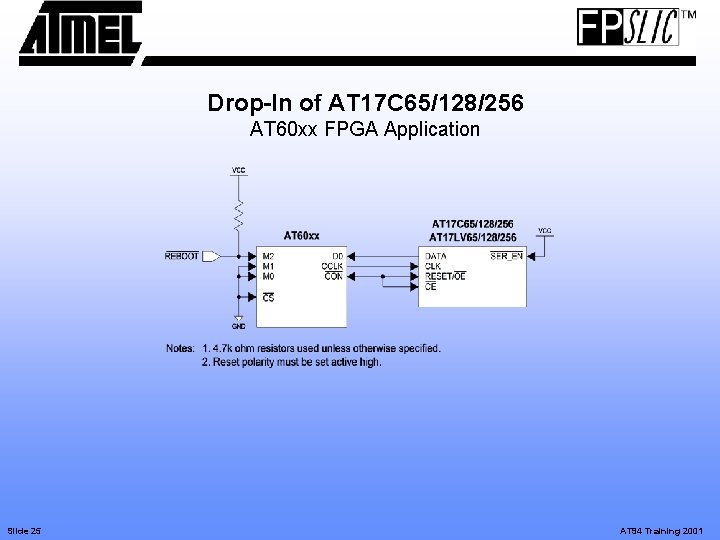

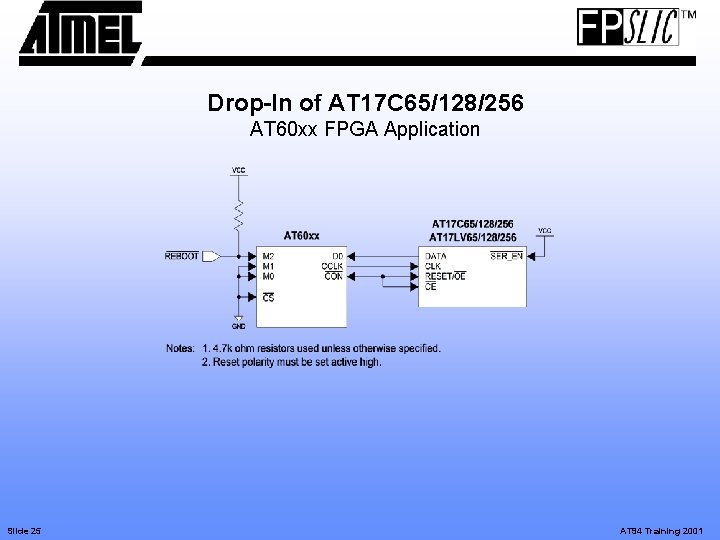

Drop-In of AT 17 C 65/128/256 AT 60 xx FPGA Application Slide 25 AT 94 Training 2001

In-System Programming of the AT 17 C 65/128/256 (Old) RESET/OE Programming Arrangement AT 60 xx FPGA Application Old Version Slide 26 AT 94 Training 2001

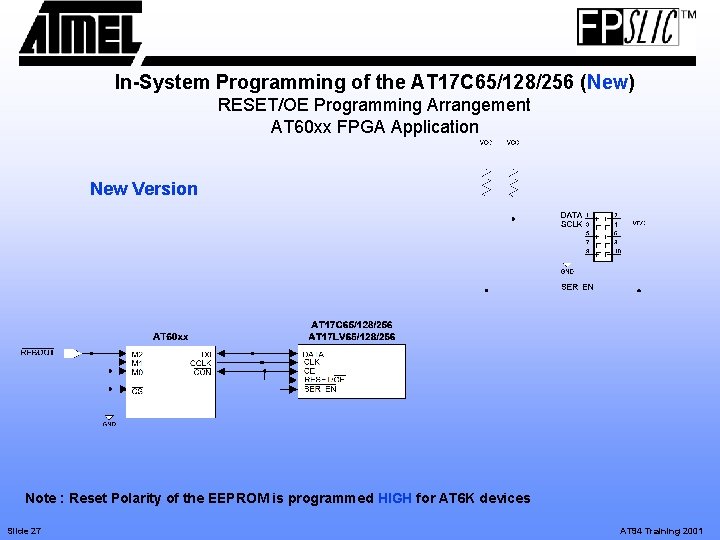

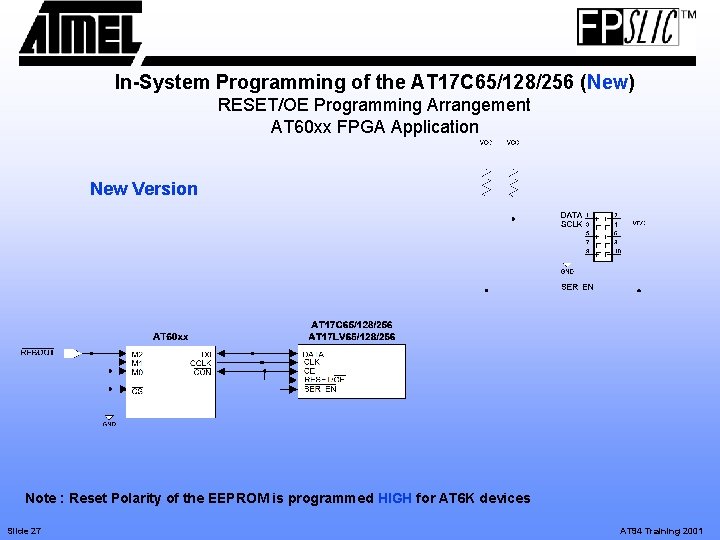

In-System Programming of the AT 17 C 65/128/256 (New) RESET/OE Programming Arrangement AT 60 xx FPGA Application New Version Note : Reset Polarity of the EEPROM is programmed HIGH for AT 6 K devices Slide 27 AT 94 Training 2001

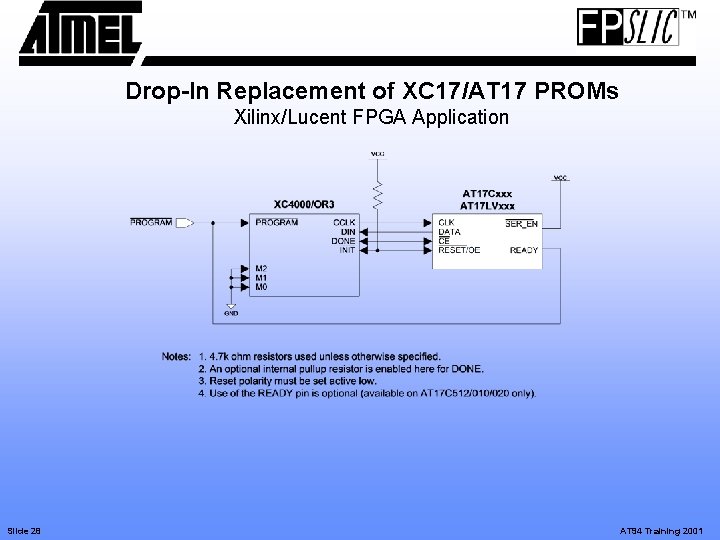

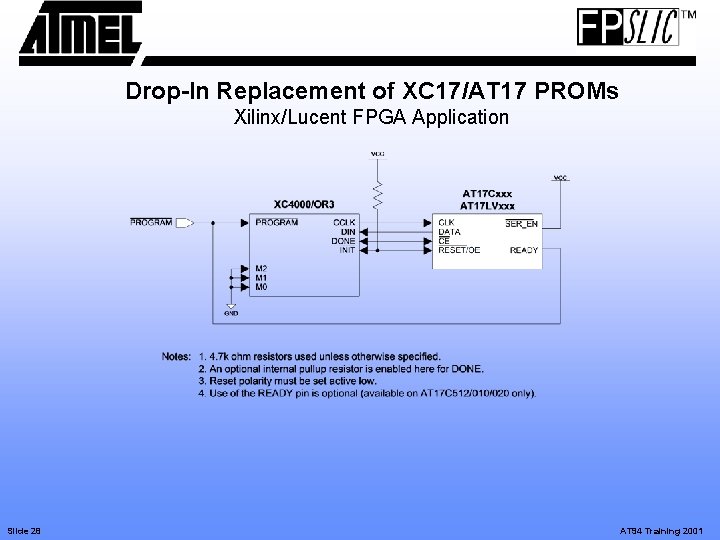

Drop-In Replacement of XC 17/AT 17 PROMs Xilinx/Lucent FPGA Application Slide 28 AT 94 Training 2001

In-System Programming of the AT 17 C 65/128/256 RESET/OE Programming Arrangement Xilinx/Lucent FPGA Application Slide 29 AT 94 Training 2001

In-System Programming of the AT 17 C 512/010/002 Xilinx/Lucent FPGA Application Slide 30 AT 94 Training 2001

In-System Programming of the AT 17 C 512/010/002 Cascaded Arrangement Xilinx/Lucent FPGA Application Slide 31 AT 94 Training 2001

In-System Programming of the AT 17 C/LV 020 Xilinx/Lucent FPGA Application Slide 32 AT 94 Training 2001

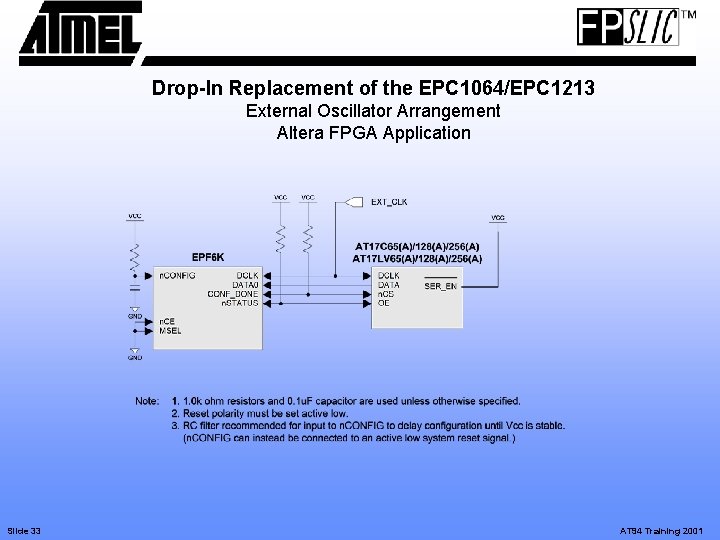

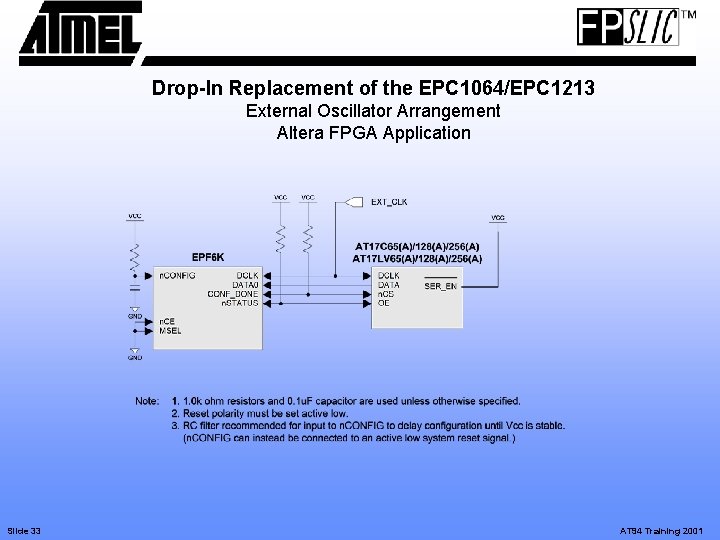

Drop-In Replacement of the EPC 1064/EPC 1213 External Oscillator Arrangement Altera FPGA Application Slide 33 AT 94 Training 2001

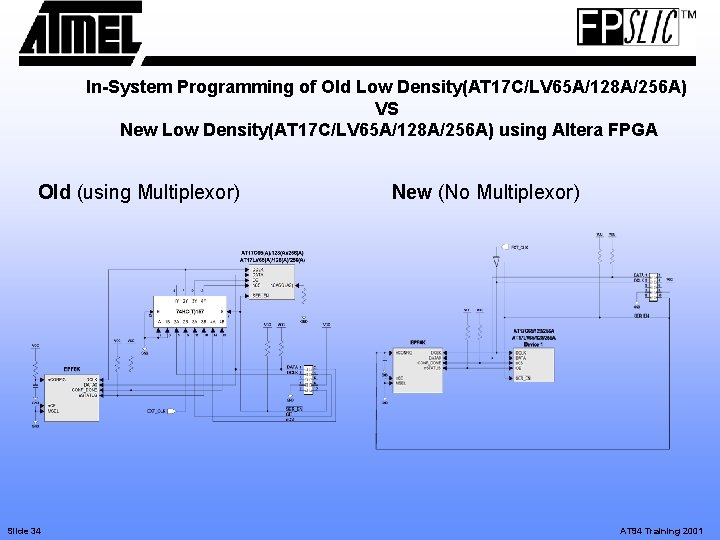

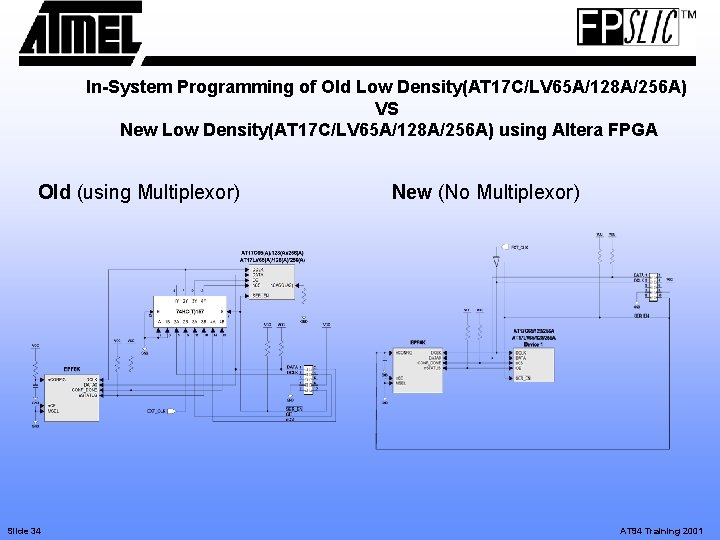

In-System Programming of Old Low Density(AT 17 C/LV 65 A/128 A/256 A) VS New Low Density(AT 17 C/LV 65 A/128 A/256 A) using Altera FPGA Old (using Multiplexor) Slide 34 New (No Multiplexor) AT 94 Training 2001

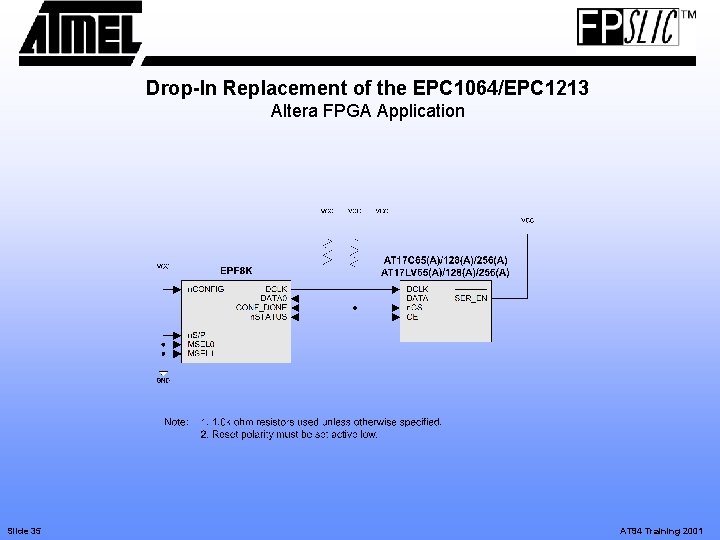

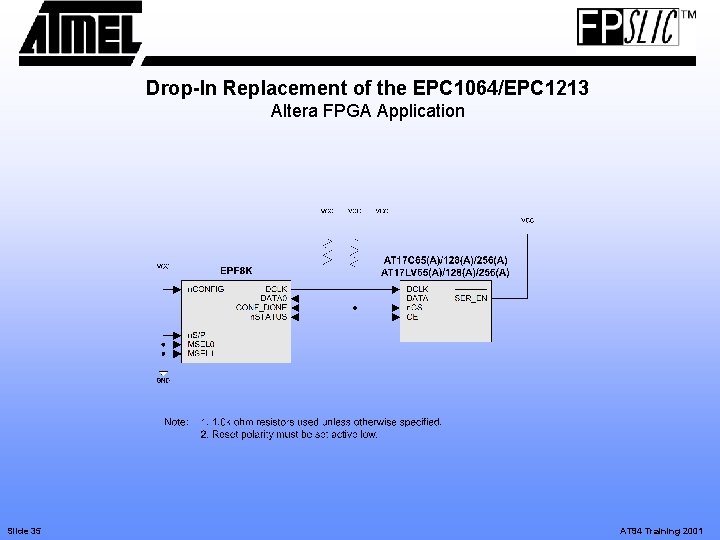

Drop-In Replacement of the EPC 1064/EPC 1213 Altera FPGA Application Slide 35 AT 94 Training 2001

Drop-In Replacement of the EPC 1441/EPC 2 Internal Oscillator Arrangement Altera FPGA Application Slide 36 AT 94 Training 2001

Drop-In Replacement of the EPC 1441/EPC 2 Internal Oscillator and Cascaded Arrangemen Altera FPGA Application Slide 37 AT 94 Training 2001

In-System Programming of the AT 17 C 65(A)/128(A)/256(A) RESET/OE Programming Arrangement Altera FPGA Application Slide 38 AT 94 Training 2001

In-System Programming of the AT 17 C 65 A/128 A/256 A(older version) RESET/OE Programming with External Oscillator Arrangement Altera FPGA Application Slide 39 AT 94 Training 2001

In-System Programming of the AT 17 C 512 A/010 A/002 A Altera FPGA Application Slide 40 AT 94 Training 2001

In-System Programming of the AT 17 C 512 A/010/002 A Internal Oscillator Arrangement Altera FPGA Application Slide 41 AT 94 Training 2001

In-System Programming of the AT 17 C 512 A/010 A/002 A Internal Oscillator and Cascaded Arrangement Altera FPGA Application Slide 42 AT 94 Training 2001

In-System Programming of the AT 17 C 512 A/010 A/002 A External Oscillator Arrangement Altera FPGA Application Slide 43 AT 94 Training 2001

In-System Programming of the AT 17 C/LV 020 A Internal Oscillator Arrangement Altera FPGA Application Slide 44 AT 94 Training 2001