Asynchronous communication Interface Modes of transfer Data transfer

- Slides: 19

Asynchronous communication Interface

Modes of transfer • Data transfer between peripherals and computer may be handled in one of 3 possible ways – Programmed I/O – Interrupt initiated I/O – Direct Memory Access(DMA)

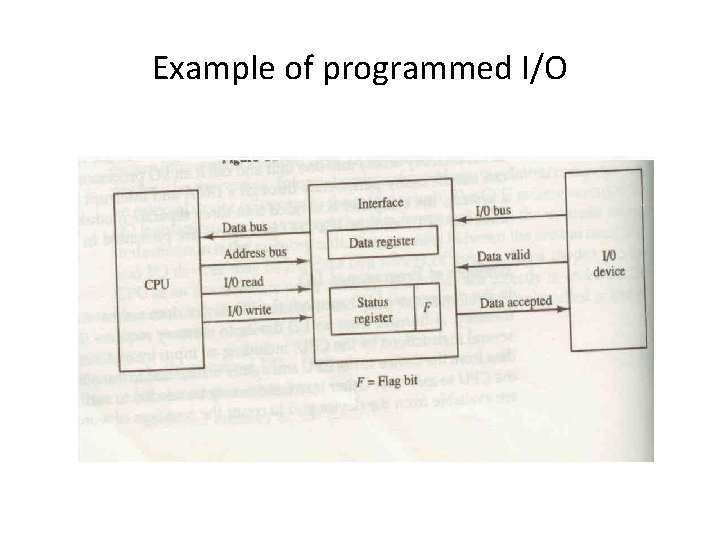

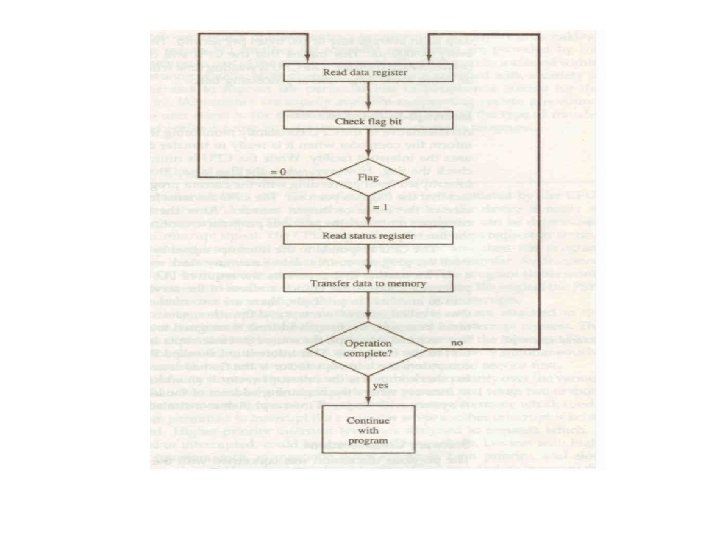

Programmed I/O • CPU has direct control over I/O – Sensing status – Read/write commands – Transferring data • CPU waits for I/O module to complete operation • Wastes CPU time

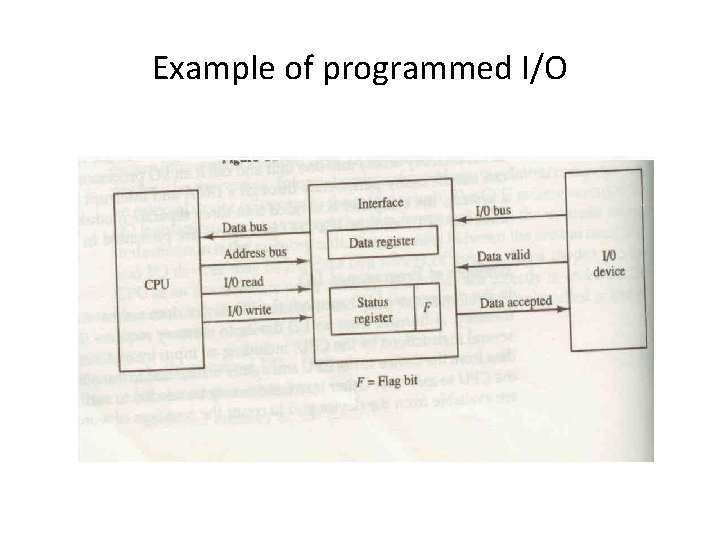

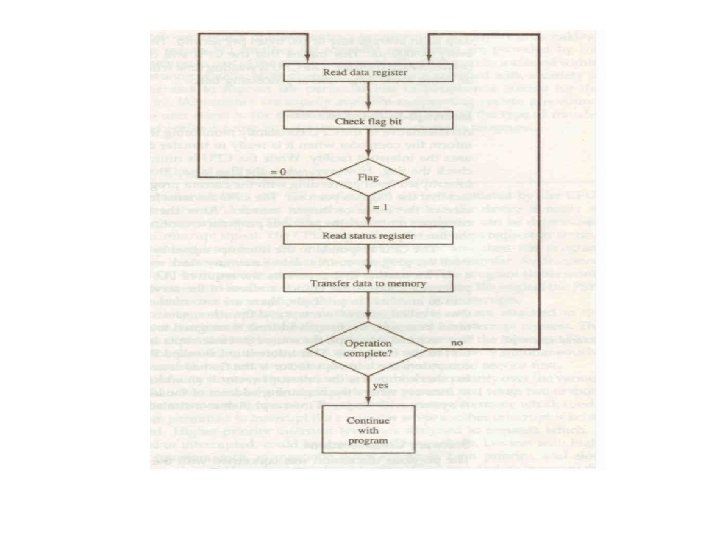

Example of programmed I/O

Interrupt Initiated I/O • Overcomes CPU waiting • No repeated CPU checking of device • I/O i/f interrupts when ready

• Vectored interrupt and nonvectored interrupt • I/O routines

Interrupt Initiated I/O Basic Operation • I/O module gets data from peripheral while CPU does other work • I/O module interrupts CPU • CPU requests data • I/O module transfers data

Priority Interrupt • It is a system that establishes a priority of simultaneous or multiple interrupts – Each interrupt line has a priority – Higher priority lines can interrupt lower priority lines • • Can be done by software or hardware S/W -- polling

Polling: • One common branch address for all interrupts • The program at the branch address polls all the interrupt sources in sequence • The order in which they are polled determines the priority • The highest priority source is tested first and if its interrupt signal is on, control branches to a service routine for that source otherwise the next lower priority source is tested and so on.

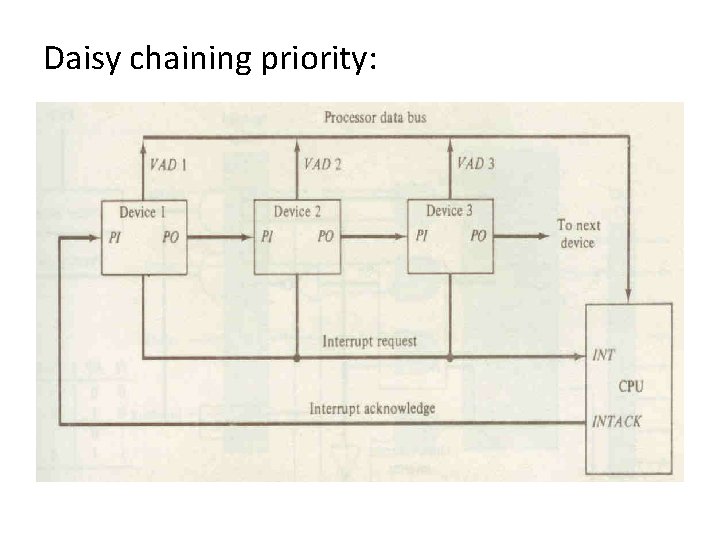

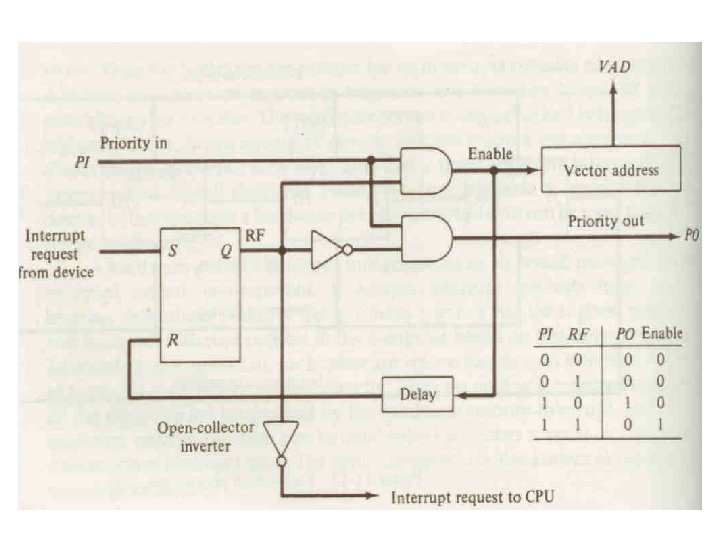

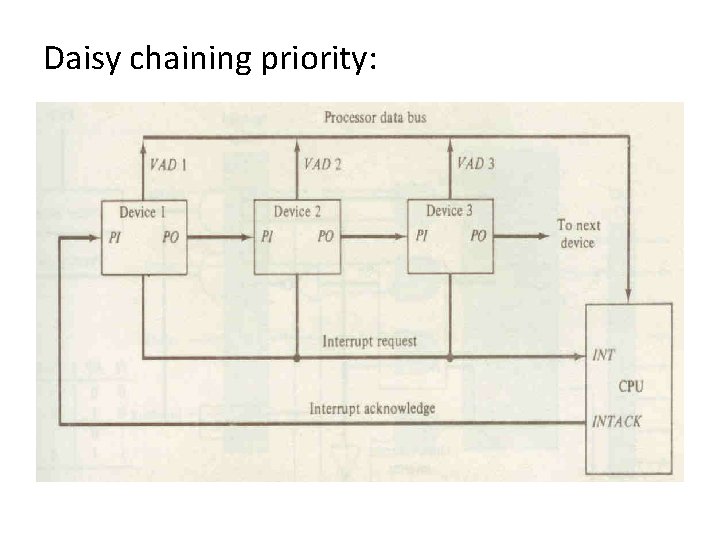

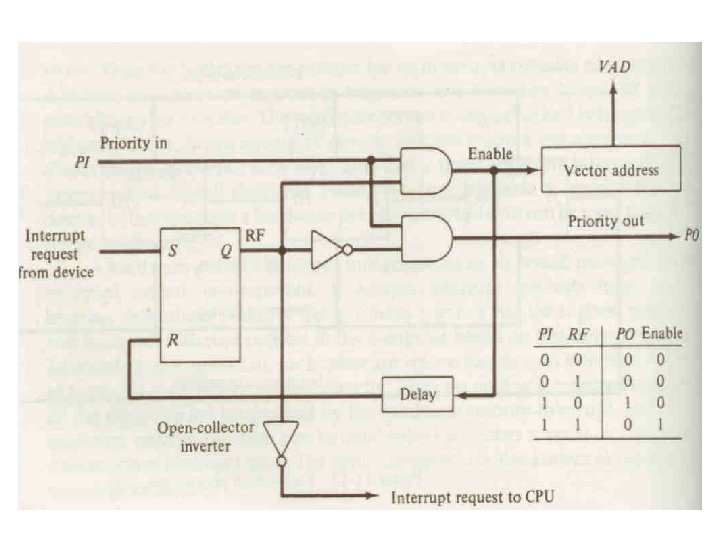

Disadvantages: • If there are many interrupts the time required to poll them can exceed the time available to service the I/O device H/W priority interrupt: • This unit accepts interrupts from many sources, determines which of the incoming requests has the highest priority , and issues an interrupt request to the computer • The h/w priority function can be established by a serial or parallel connection of interrupt lines. • The serial connection is known as daisy chaining method.

Daisy chaining priority:

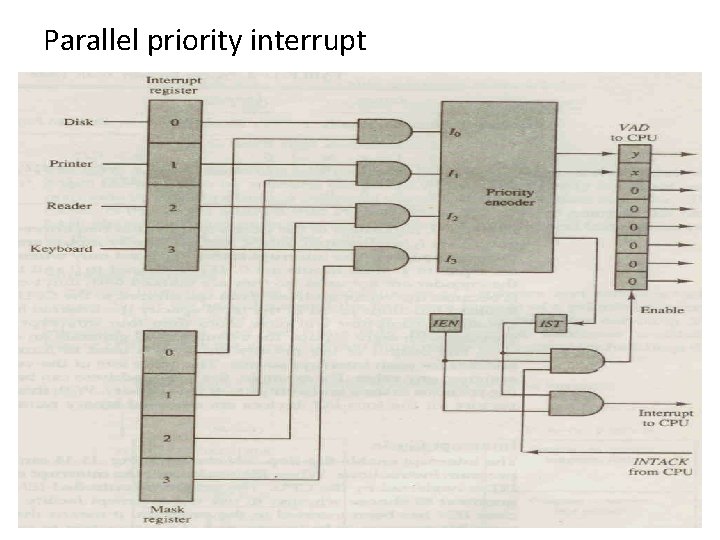

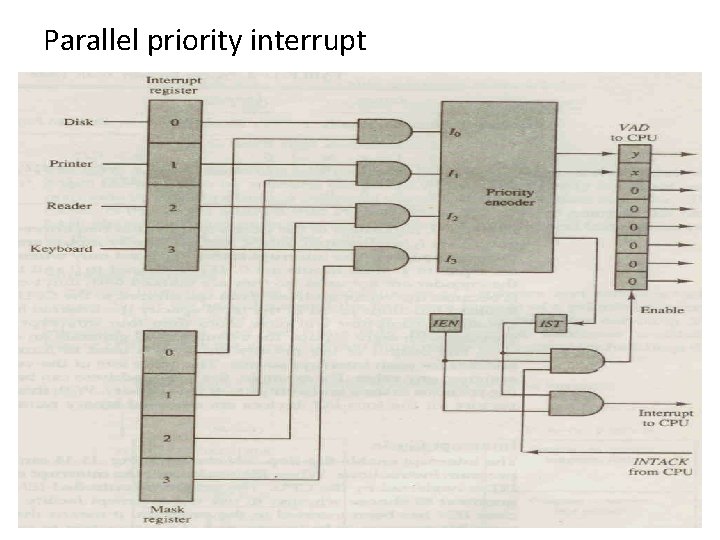

Parallel priority interrupt

• Uses a register whose bits are set separately by the interrupt signal • Priority is according to the position of bits in the register • Mask register is used to control the status of each interrupt request • It can be programmed to disable lower priority interrupts while a higher priority device is being serviced or a high priority device can interrupt the CPU while a low priority device is being serviced

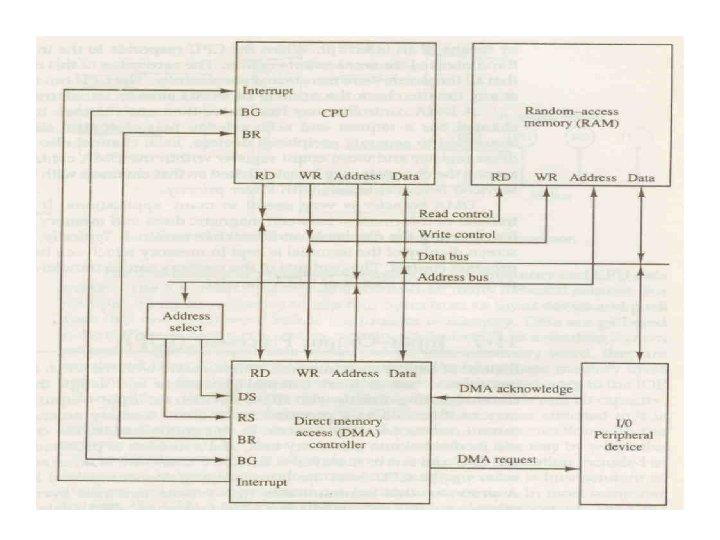

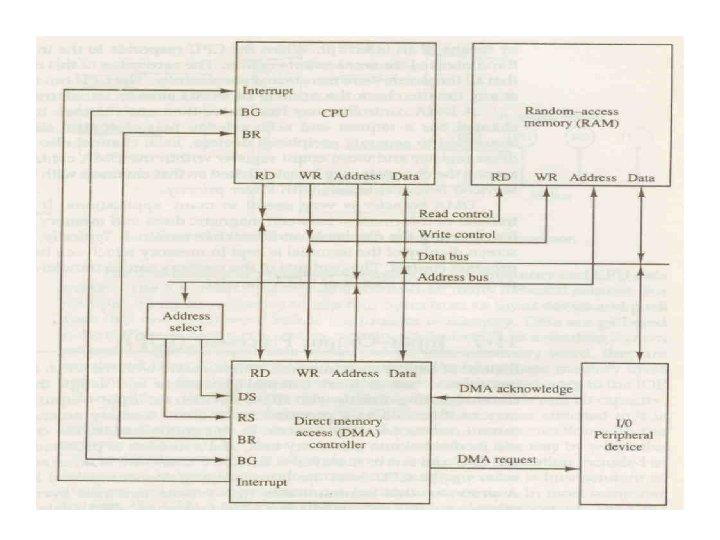

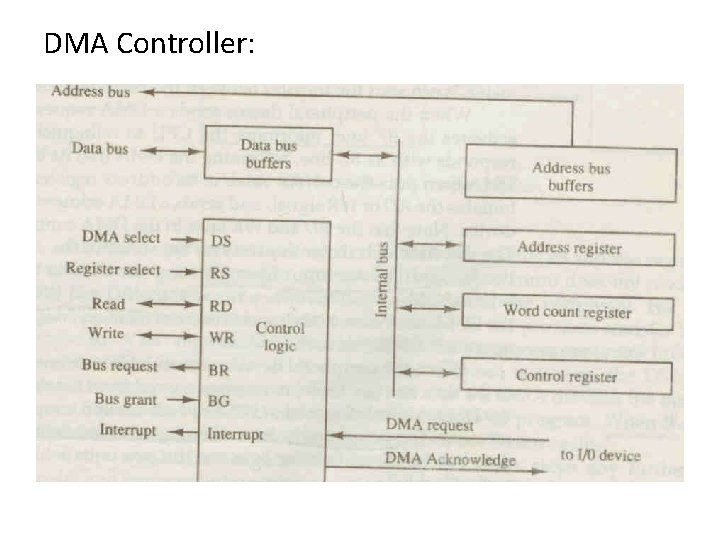

Direct Memory Access: • Removing CPU from the path and letting the peripheral device manage the memory buses directly • DMA controller is used. • Bus request • Bus grant • Burst transfer • Cycle stealing

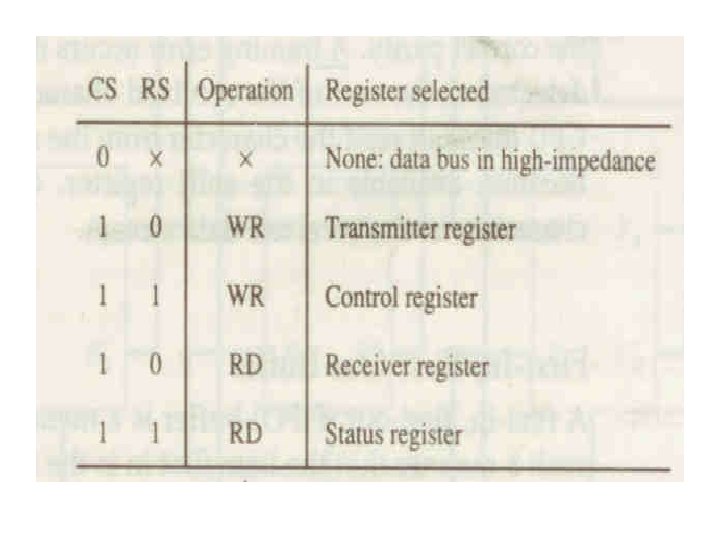

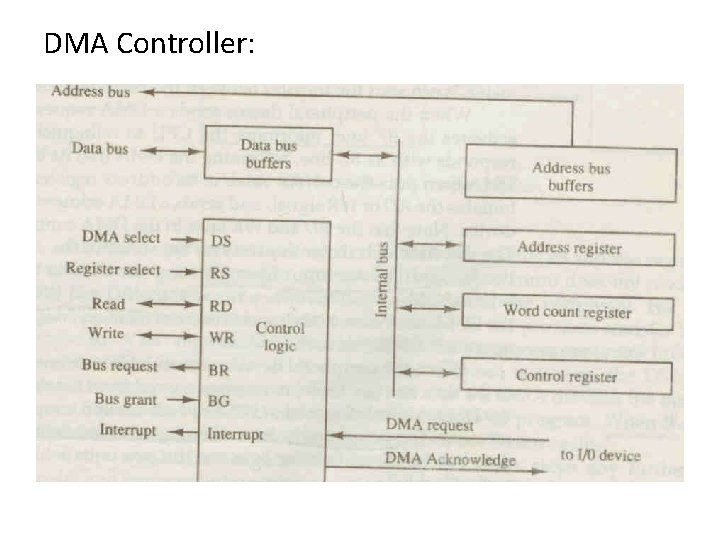

DMA Controller: