Assembly Languages I Prof Stephen A Edwards Copyright

Assembly Languages I Prof. Stephen A. Edwards Copyright © 2001 Stephen A. Edwards All rights reserved

Last Time § Languages § Syntax: what’s in the language § Semantics: what the language means § Model: what the language manipulates § Specification asks for something § Modeling asks what something will do § Concurrency § Nondeterminism Copyright © 2001 Stephen A. Edwards All rights reserved

Assembly Languages § One step up from machine language § Originally a more user-friendly way to program ENIAC, 1946 17 k tubes, 5 k. Hz § Now mostly a compiler target § Model of computation: stored program computer Copyright © 2001 Stephen A. Edwards All rights reserved

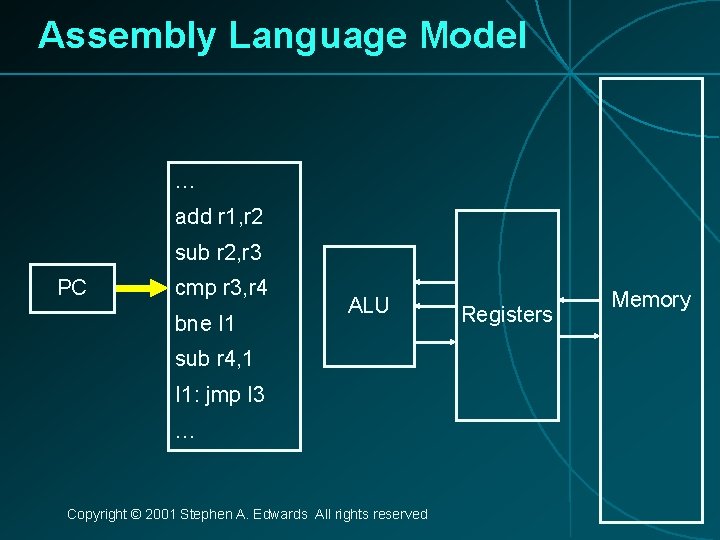

Assembly Language Model … add r 1, r 2 sub r 2, r 3 PC cmp r 3, r 4 bne I 1 ALU sub r 4, 1 I 1: jmp I 3 … Copyright © 2001 Stephen A. Edwards All rights reserved Registers Memory

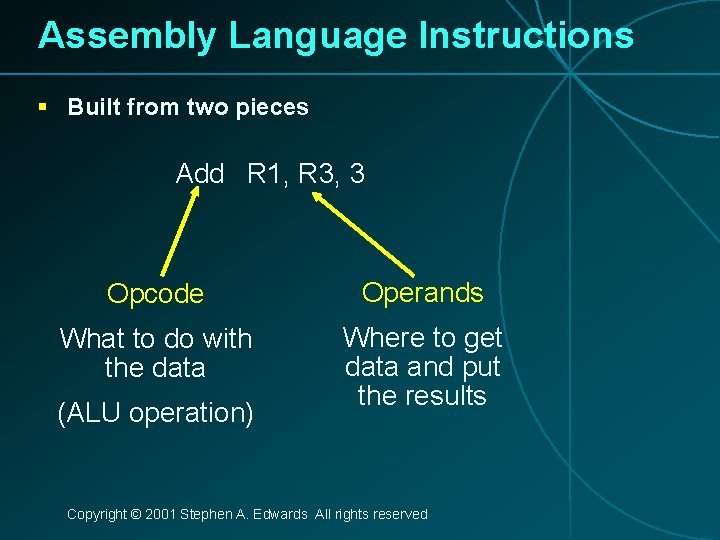

Assembly Language Instructions § Built from two pieces Add R 1, R 3, 3 Opcode Operands What to do with the data Where to get data and put the results (ALU operation) Copyright © 2001 Stephen A. Edwards All rights reserved

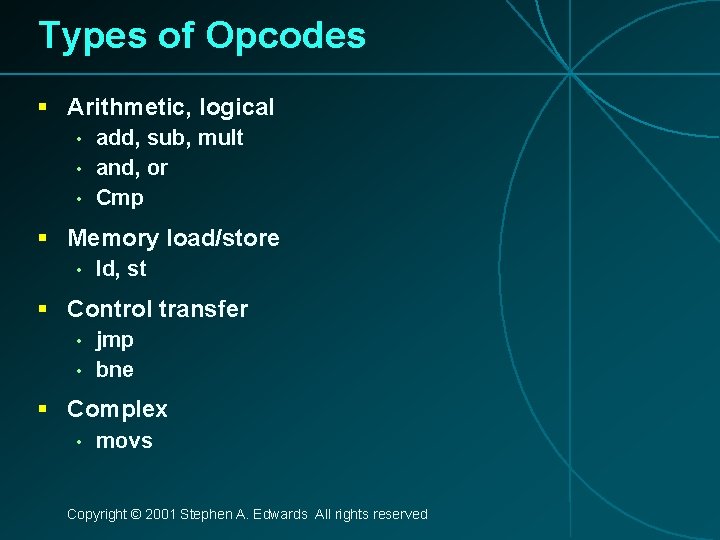

Types of Opcodes § Arithmetic, logical • • • add, sub, mult and, or Cmp § Memory load/store • ld, st § Control transfer • • jmp bne § Complex • movs Copyright © 2001 Stephen A. Edwards All rights reserved

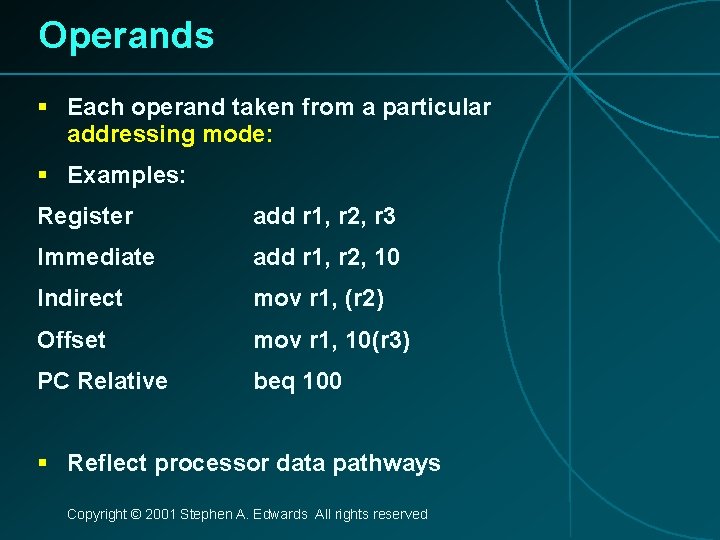

Operands § Each operand taken from a particular addressing mode: § Examples: Register add r 1, r 2, r 3 Immediate add r 1, r 2, 10 Indirect mov r 1, (r 2) Offset mov r 1, 10(r 3) PC Relative beq 100 § Reflect processor data pathways Copyright © 2001 Stephen A. Edwards All rights reserved

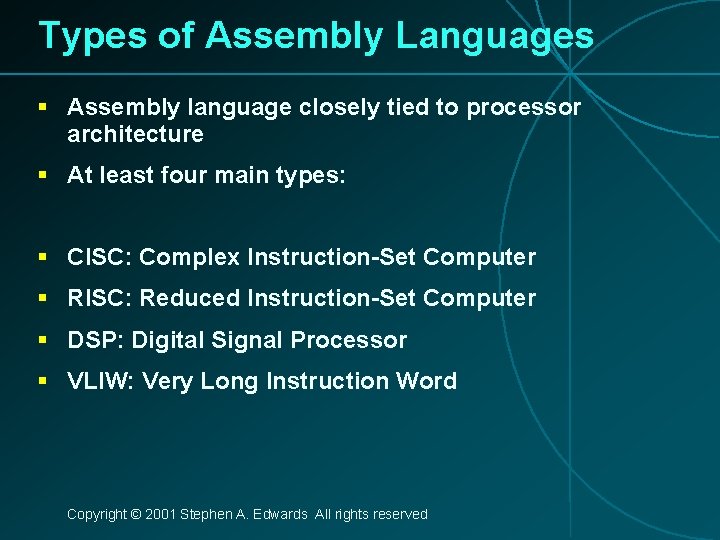

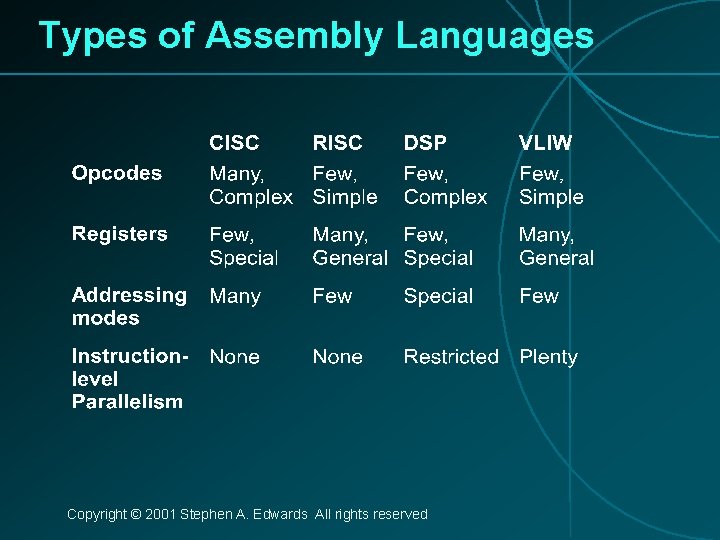

Types of Assembly Languages § Assembly language closely tied to processor architecture § At least four main types: § CISC: Complex Instruction-Set Computer § RISC: Reduced Instruction-Set Computer § DSP: Digital Signal Processor § VLIW: Very Long Instruction Word Copyright © 2001 Stephen A. Edwards All rights reserved

CISC Assembly Language § Developed when people wrote assembly language § Complicated, often specialized instructions with many effects § Examples from x 86 architecture • • String move Procedure enter, leave § Many, complicated addressing modes § So complicated, often executed by a little program (microcode) Copyright © 2001 Stephen A. Edwards All rights reserved

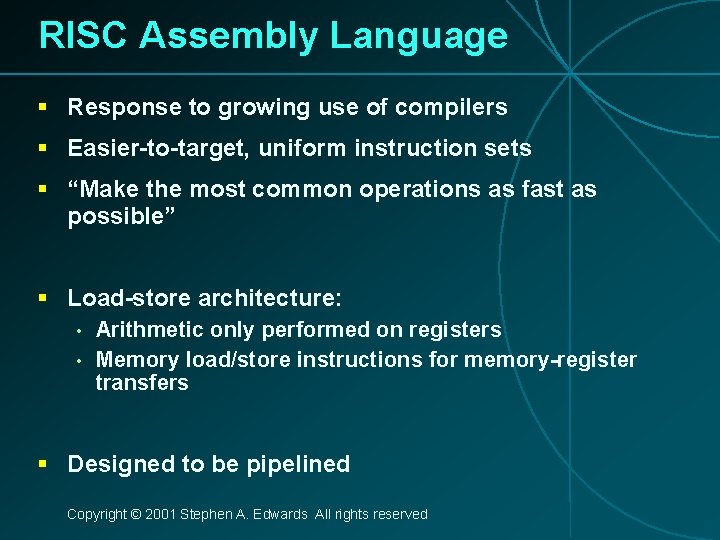

RISC Assembly Language § Response to growing use of compilers § Easier-to-target, uniform instruction sets § “Make the most common operations as fast as possible” § Load-store architecture: • • Arithmetic only performed on registers Memory load/store instructions for memory-register transfers § Designed to be pipelined Copyright © 2001 Stephen A. Edwards All rights reserved

DSP Assembly Language § Digital signal processors designed specifically for signal processing algorithms § Lots of regular arithmetic on vectors § Often written by hand § Irregular architectures to save power, area § Substantial instruction-level parallelism Copyright © 2001 Stephen A. Edwards All rights reserved

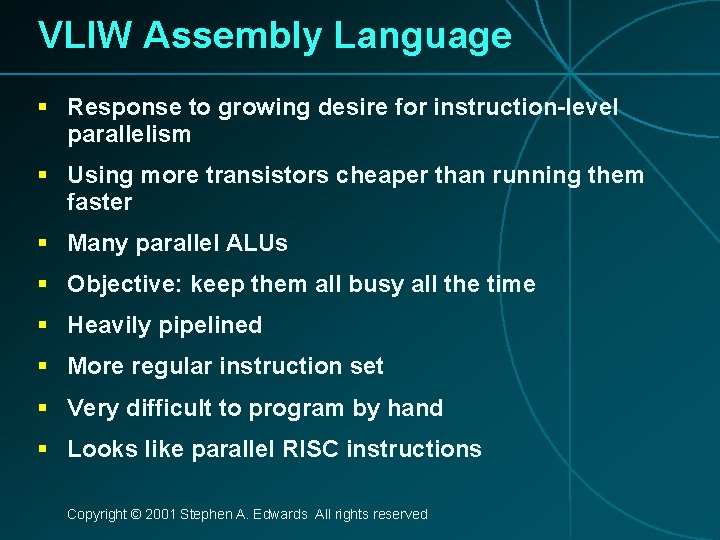

VLIW Assembly Language § Response to growing desire for instruction-level parallelism § Using more transistors cheaper than running them faster § Many parallel ALUs § Objective: keep them all busy all the time § Heavily pipelined § More regular instruction set § Very difficult to program by hand § Looks like parallel RISC instructions Copyright © 2001 Stephen A. Edwards All rights reserved

Types of Assembly Languages Copyright © 2001 Stephen A. Edwards All rights reserved

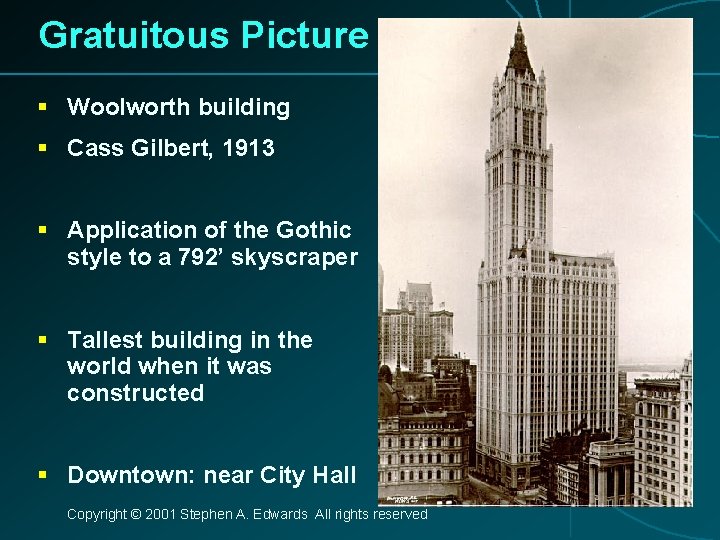

Gratuitous Picture § Woolworth building § Cass Gilbert, 1913 § Application of the Gothic style to a 792’ skyscraper § Tallest building in the world when it was constructed § Downtown: near City Hall Copyright © 2001 Stephen A. Edwards All rights reserved

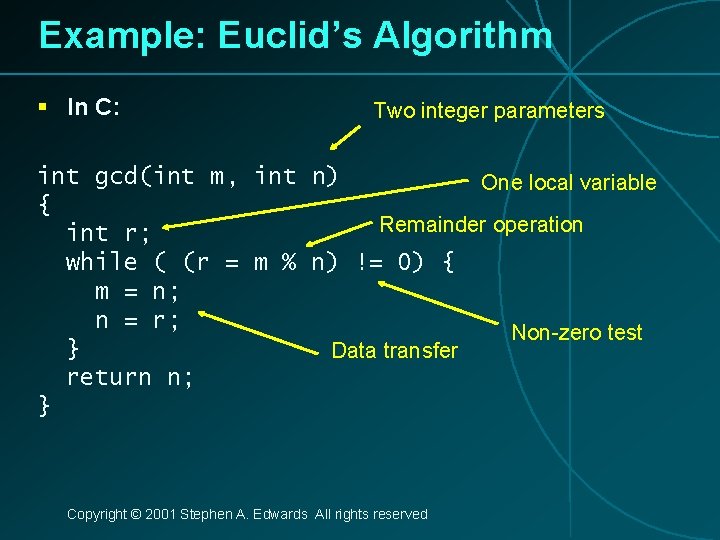

Example: Euclid’s Algorithm § In C: Two integer parameters int gcd(int m, int n) One local variable { Remainder operation int r; while ( (r = m % n) != 0) { m = n; n = r; Non-zero test } Data transfer return n; } Copyright © 2001 Stephen A. Edwards All rights reserved

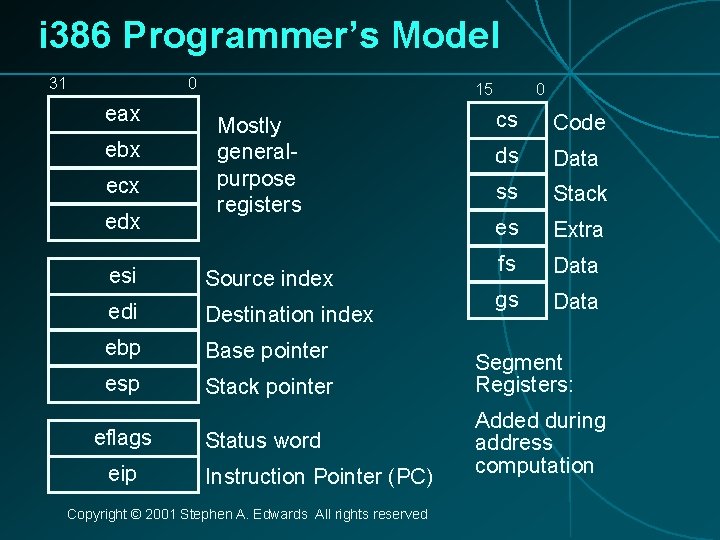

i 386 Programmer’s Model 31 0 eax ebx ecx edx 15 Mostly generalpurpose registers esi Source index edi Destination index ebp Base pointer esp Stack pointer eflags eip Status word Instruction Pointer (PC) Copyright © 2001 Stephen A. Edwards All rights reserved 0 cs Code ds Data ss Stack es Extra fs Data gs Data Segment Registers: Added during address computation

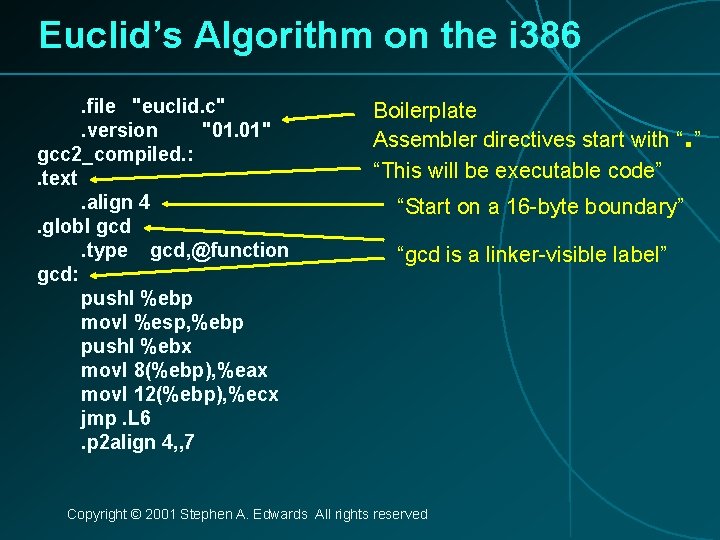

Euclid’s Algorithm on the i 386. file "euclid. c". version "01. 01" gcc 2_compiled. : . text. align 4. globl gcd. type gcd, @function gcd: pushl %ebp movl %esp, %ebp pushl %ebx movl 8(%ebp), %eax movl 12(%ebp), %ecx jmp. L 6. p 2 align 4, , 7 Boilerplate Assembler directives start with “ ” “This will be executable code” . “Start on a 16 -byte boundary” “gcd is a linker-visible label” Copyright © 2001 Stephen A. Edwards All rights reserved

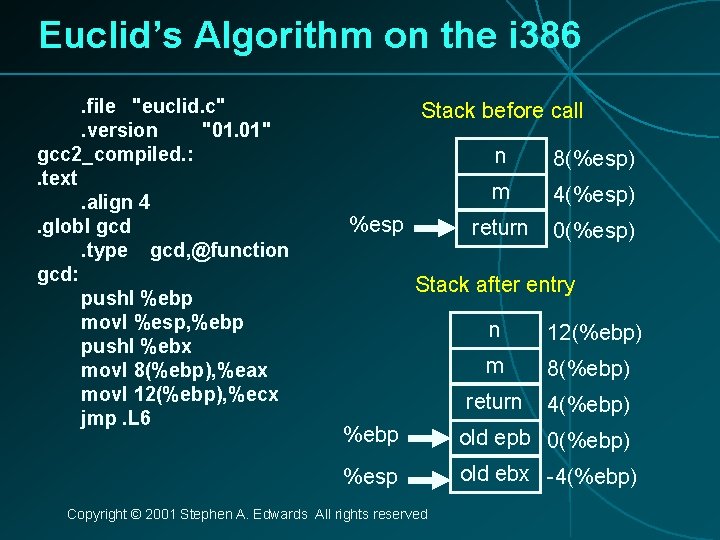

Euclid’s Algorithm on the i 386. file "euclid. c". version "01. 01" gcc 2_compiled. : . text. align 4. globl gcd. type gcd, @function gcd: pushl %ebp movl %esp, %ebp pushl %ebx movl 8(%ebp), %eax movl 12(%ebp), %ecx jmp. L 6 Stack before call %esp n 8(%esp) m 4(%esp) return 0(%esp) Stack after entry %ebp %esp Copyright © 2001 Stephen A. Edwards All rights reserved n 12(%ebp) m 8(%ebp) return 4(%ebp) old epb 0(%ebp) old ebx -4(%ebp)

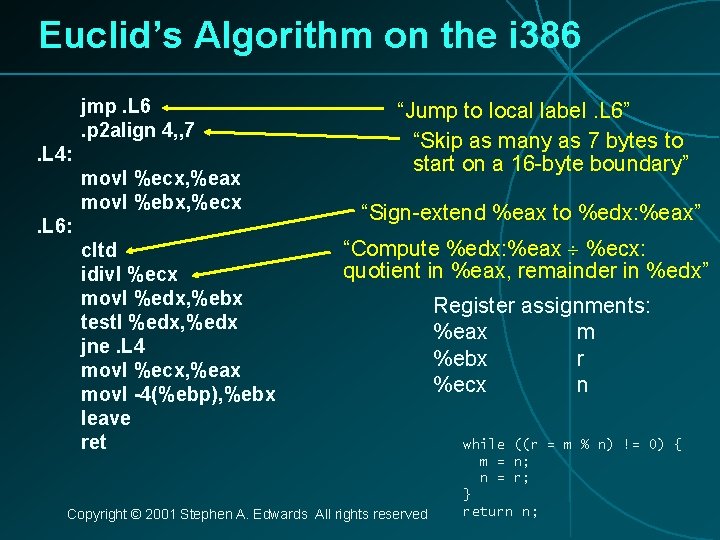

Euclid’s Algorithm on the i 386 jmp. L 6. p 2 align 4, , 7. L 4: movl %ecx, %eax movl %ebx, %ecx. L 6: cltd idivl %ecx movl %edx, %ebx testl %edx, %edx jne. L 4 movl %ecx, %eax movl -4(%ebp), %ebx leave ret “Jump to local label. L 6” “Skip as many as 7 bytes to start on a 16 -byte boundary” “Sign-extend %eax to %edx: %eax” “Compute %edx: %eax %ecx: quotient in %eax, remainder in %edx” Copyright © 2001 Stephen A. Edwards All rights reserved Register assignments: %eax m %ebx r %ecx n while ((r = m % n) != 0) { m = n; n = r; } return n;

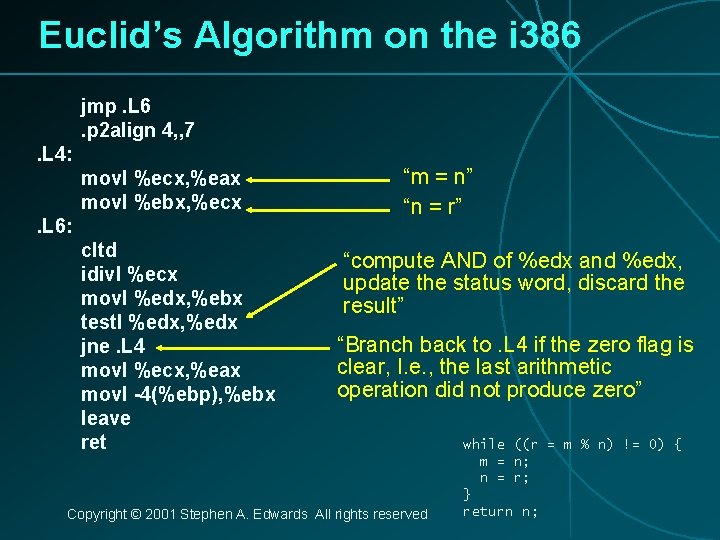

Euclid’s Algorithm on the i 386 jmp. L 6. p 2 align 4, , 7. L 4: movl %ecx, %eax movl %ebx, %ecx. L 6: cltd idivl %ecx movl %edx, %ebx testl %edx, %edx jne. L 4 movl %ecx, %eax movl -4(%ebp), %ebx leave ret “m = n” “n = r” “compute AND of %edx and %edx, update the status word, discard the result” “Branch back to. L 4 if the zero flag is clear, I. e. , the last arithmetic operation did not produce zero” Copyright © 2001 Stephen A. Edwards All rights reserved while ((r = m % n) != 0) { m = n; n = r; } return n;

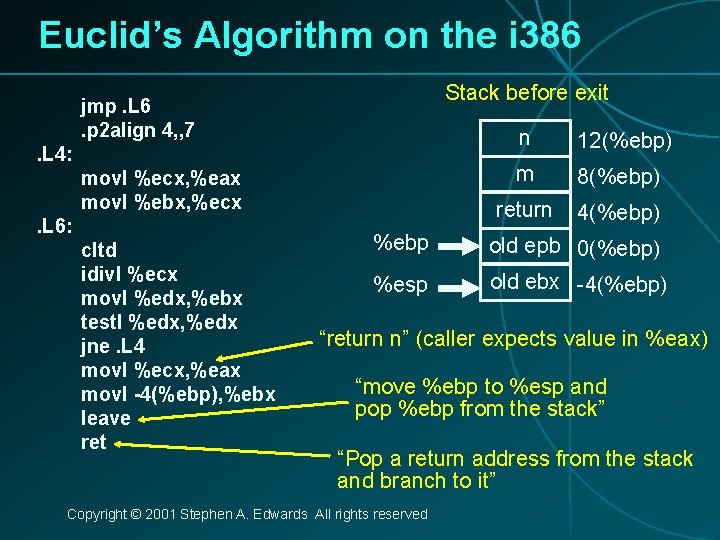

Euclid’s Algorithm on the i 386 Stack before exit jmp. L 6. p 2 align 4, , 7. L 4: movl %ecx, %eax movl %ebx, %ecx. L 6: cltd idivl %ecx movl %edx, %ebx testl %edx, %edx jne. L 4 movl %ecx, %eax movl -4(%ebp), %ebx leave ret %ebp %esp n 12(%ebp) m 8(%ebp) return 4(%ebp) old epb 0(%ebp) old ebx -4(%ebp) “return n” (caller expects value in %eax) “move %ebp to %esp and pop %ebp from the stack” “Pop a return address from the stack and branch to it” Copyright © 2001 Stephen A. Edwards All rights reserved

Another Gratuitous Picture § Types of Bridges Truss (Forth Bridge, Scotland) Suspension (Golden Gate Bridge, California) Copyright © 2001 Stephen A. Edwards All rights reserved Cable-stayed (Higashi Kobe, Japan)

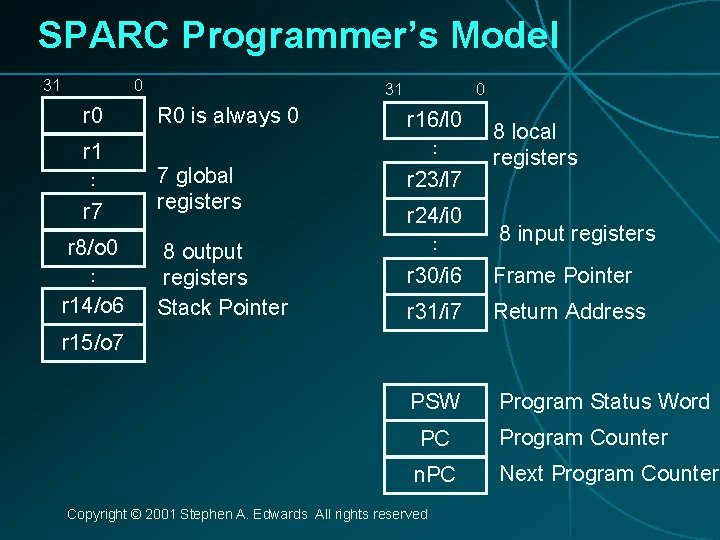

SPARC Programmer’s Model 31 0 r 0 … r 7 … r 14/o 6 R 0 is always 0 r 16/l 0 7 global registers r 23/l 7 8 output registers Stack Pointer r 24/i 0 … r 8/o 0 0 … r 1 31 8 local registers 8 input registers r 30/i 6 Frame Pointer r 31/i 7 Return Address PSW Program Status Word r 15/o 7 PC Program Counter n. PC Next Program Counter Copyright © 2001 Stephen A. Edwards All rights reserved

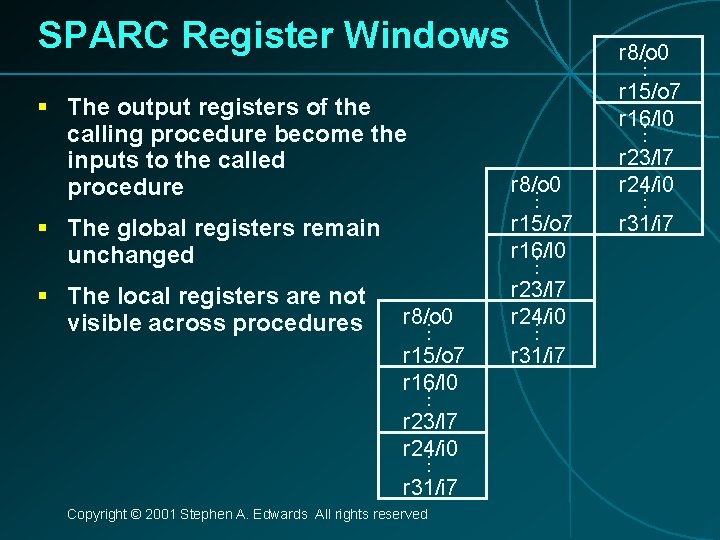

SPARC Register Windows … r 8/o 0 r 15/o 7 r 16/l 0 r 8/o 0 § The global registers remain unchanged r 15/o 7 r 16/l 0 § The local registers are not visible across procedures r 23/l 7 r 24/i 0 … § The output registers of the calling procedure become the inputs to the called procedure … … r 23/l 7 r 24/i 0 r 31/i 7 Copyright © 2001 Stephen A. Edwards All rights reserved … … r 15/o 7 r 16/l 0 r 31/i 7 … … … r 8/o 0 r 23/l 7 r 24/i 0 r 31/i 7

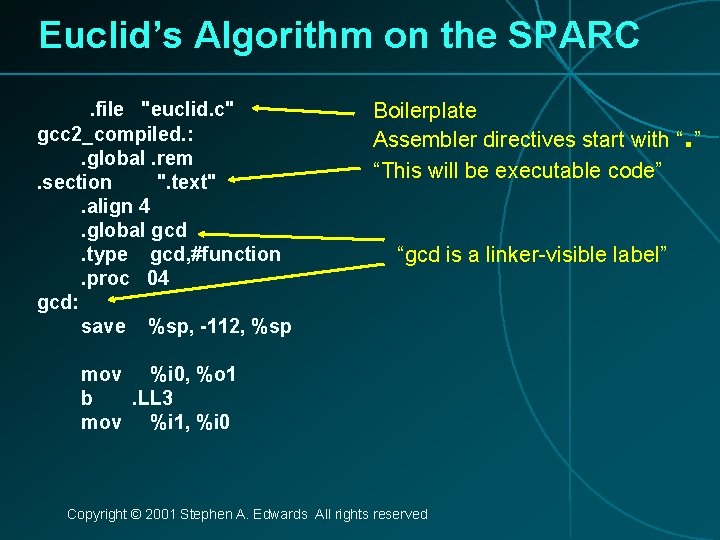

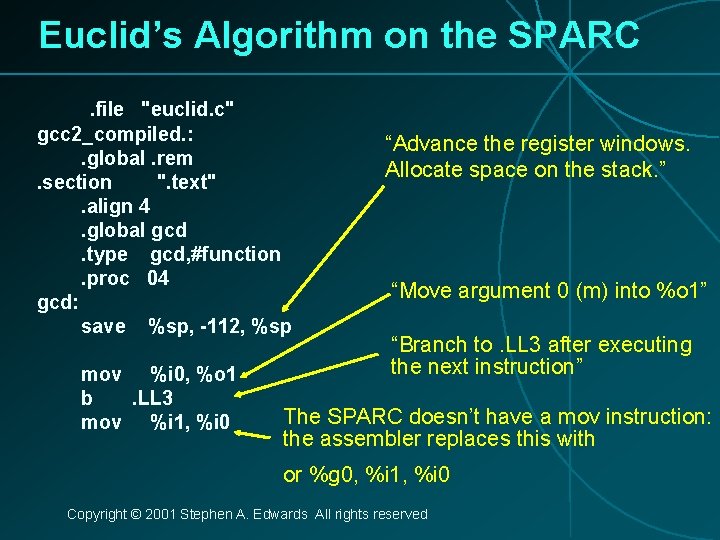

Euclid’s Algorithm on the SPARC. file "euclid. c" gcc 2_compiled. : . global. rem. section ". text". align 4. global gcd. type gcd, #function. proc 04 gcd: save %sp, -112, %sp Boilerplate Assembler directives start with “ ” “This will be executable code” . “gcd is a linker-visible label” mov %i 0, %o 1 b. LL 3 mov %i 1, %i 0 Copyright © 2001 Stephen A. Edwards All rights reserved

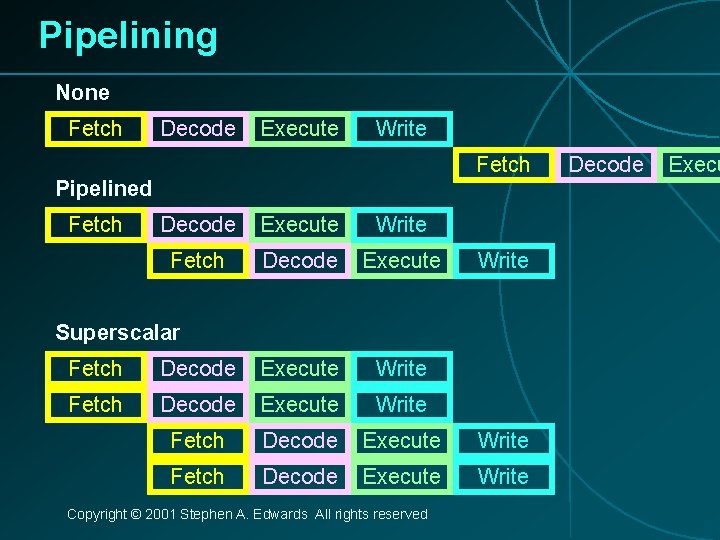

Pipelining None Fetch Decode Execute Write Fetch Pipelined Fetch Decode Execute Write Superscalar Fetch Decode Execute Write Copyright © 2001 Stephen A. Edwards All rights reserved Decode Execu

Euclid’s Algorithm on the SPARC. file "euclid. c" gcc 2_compiled. : . global. rem. section ". text". align 4. global gcd. type gcd, #function. proc 04 gcd: save %sp, -112, %sp mov %i 0, %o 1 b. LL 3 mov %i 1, %i 0 “Advance the register windows. Allocate space on the stack. ” “Move argument 0 (m) into %o 1” “Branch to. LL 3 after executing the next instruction” The SPARC doesn’t have a mov instruction: the assembler replaces this with or %g 0, %i 1, %i 0 Copyright © 2001 Stephen A. Edwards All rights reserved

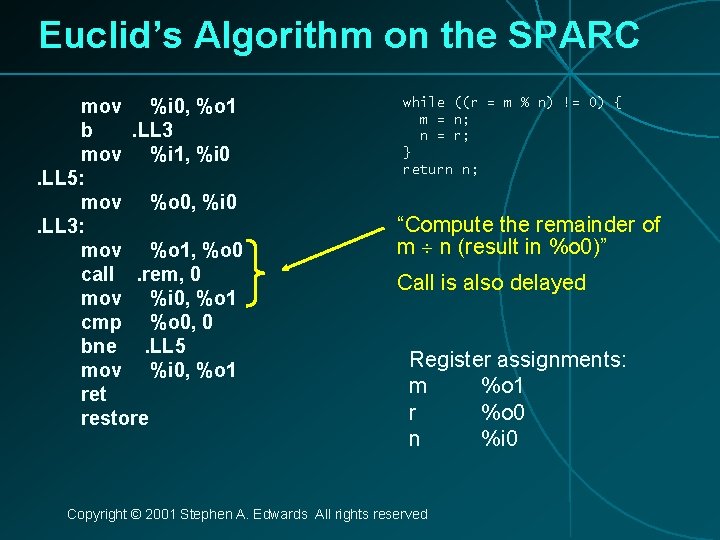

Euclid’s Algorithm on the SPARC mov %i 0, %o 1 b. LL 3 mov %i 1, %i 0. LL 5: mov %o 0, %i 0. LL 3: mov %o 1, %o 0 call. rem, 0 mov %i 0, %o 1 cmp %o 0, 0 bne. LL 5 mov %i 0, %o 1 ret restore while ((r = m % n) != 0) { m = n; n = r; } return n; “Compute the remainder of m n (result in %o 0)” Call is also delayed Register assignments: m %o 1 r %o 0 n %i 0 Copyright © 2001 Stephen A. Edwards All rights reserved

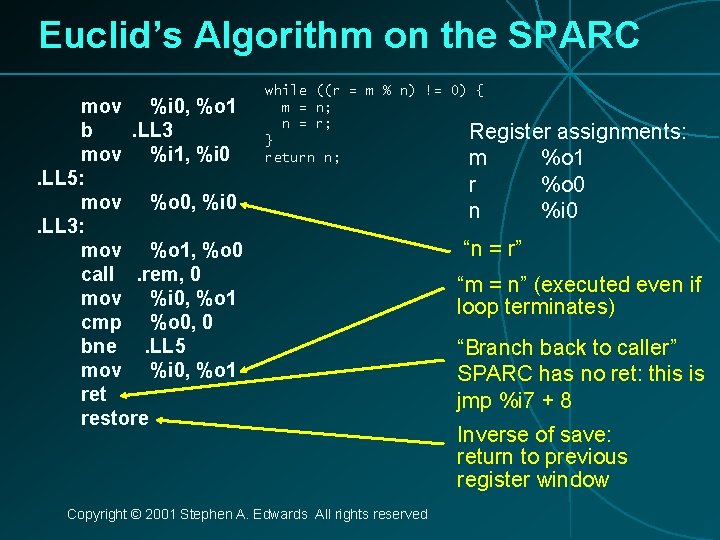

Euclid’s Algorithm on the SPARC mov %i 0, %o 1 b. LL 3 mov %i 1, %i 0. LL 5: mov %o 0, %i 0. LL 3: mov %o 1, %o 0 call. rem, 0 mov %i 0, %o 1 cmp %o 0, 0 bne. LL 5 mov %i 0, %o 1 ret restore while ((r = m % n) != 0) { m = n; n = r; Register assignments: } return n; m %o 1 Copyright © 2001 Stephen A. Edwards All rights reserved r n %o 0 %i 0 “n = r” “m = n” (executed even if loop terminates) “Branch back to caller” SPARC has no ret: this is jmp %i 7 + 8 Inverse of save: return to previous register window

- Slides: 29