ASSEMBLY LANGUAGE An Introduction to the ARM CORTEX

ASSEMBLY LANGUAGE An Introduction to the ARM CORTEX M 0+ Instructions Prepared by M. V. Iordache for EEGR 3233 Introduction to Microcontrollers, Fall 2018, Le. Tourneau University

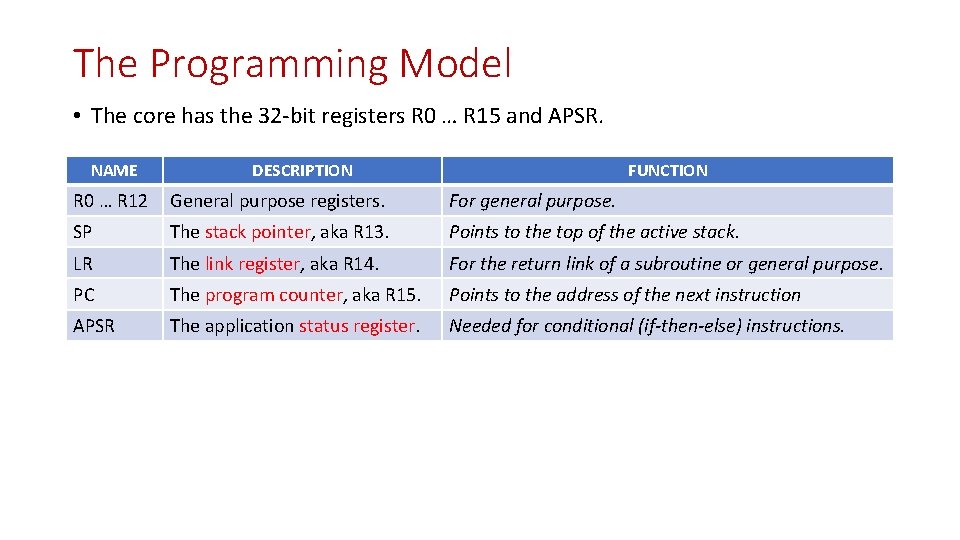

The Programming Model • The core has the 32 -bit registers R 0 … R 15 and APSR. NAME DESCRIPTION FUNCTION R 0 … R 12 General purpose registers. For general purpose. SP The stack pointer, aka R 13. Points to the top of the active stack. LR The link register, aka R 14. For the return link of a subroutine or general purpose. PC The program counter, aka R 15. Points to the address of the next instruction APSR The application status register. Needed for conditional (if-then-else) instructions.

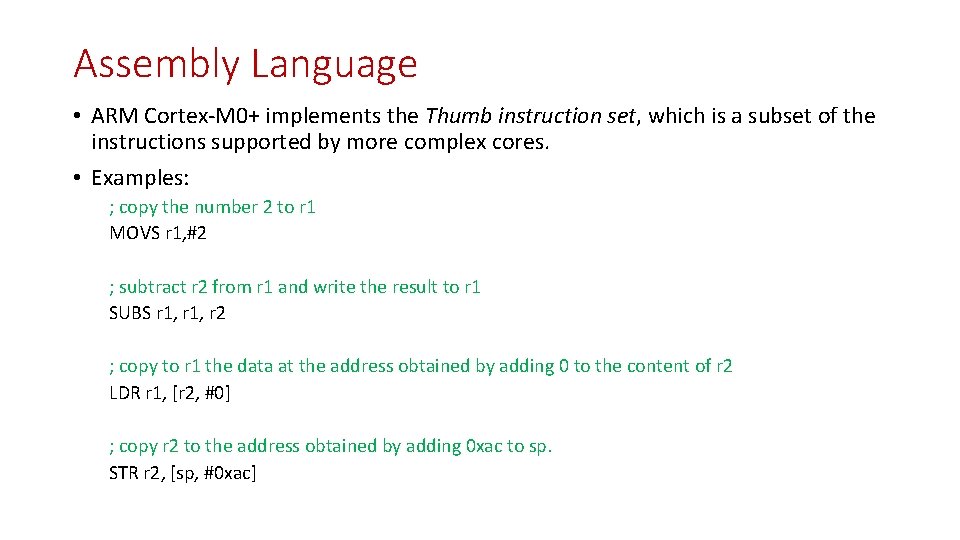

Assembly Language • ARM Cortex-M 0+ implements the Thumb instruction set, which is a subset of the instructions supported by more complex cores. • Examples: ; copy the number 2 to r 1 MOVS r 1, #2 ; subtract r 2 from r 1 and write the result to r 1 SUBS r 1, r 2 ; copy to r 1 the data at the address obtained by adding 0 to the content of r 2 LDR r 1, [r 2, #0] ; copy r 2 to the address obtained by adding 0 xac to sp. STR r 2, [sp, #0 xac]

Addressing Modes •

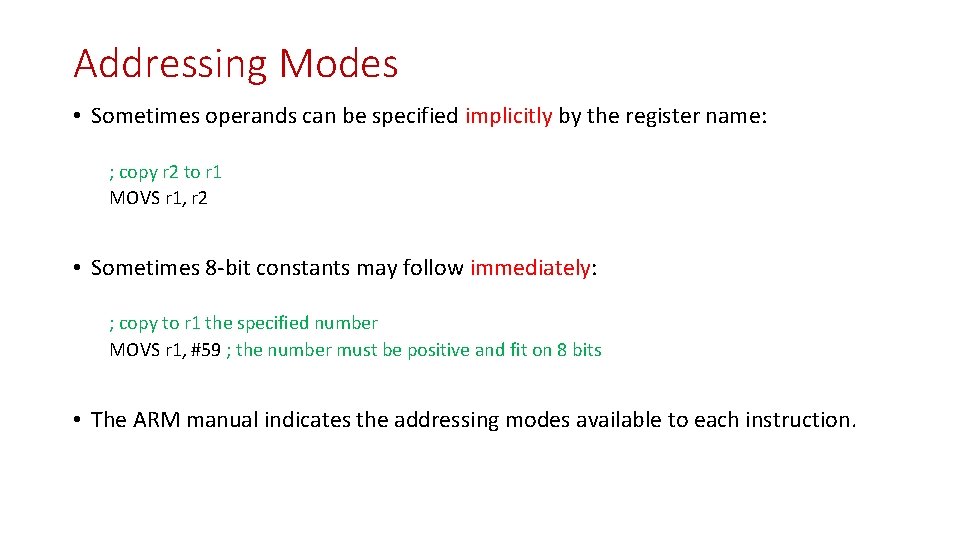

Addressing Modes • Sometimes operands can be specified implicitly by the register name: ; copy r 2 to r 1 MOVS r 1, r 2 • Sometimes 8 -bit constants may follow immediately: ; copy to r 1 the specified number MOVS r 1, #59 ; the number must be positive and fit on 8 bits • The ARM manual indicates the addressing modes available to each instruction.

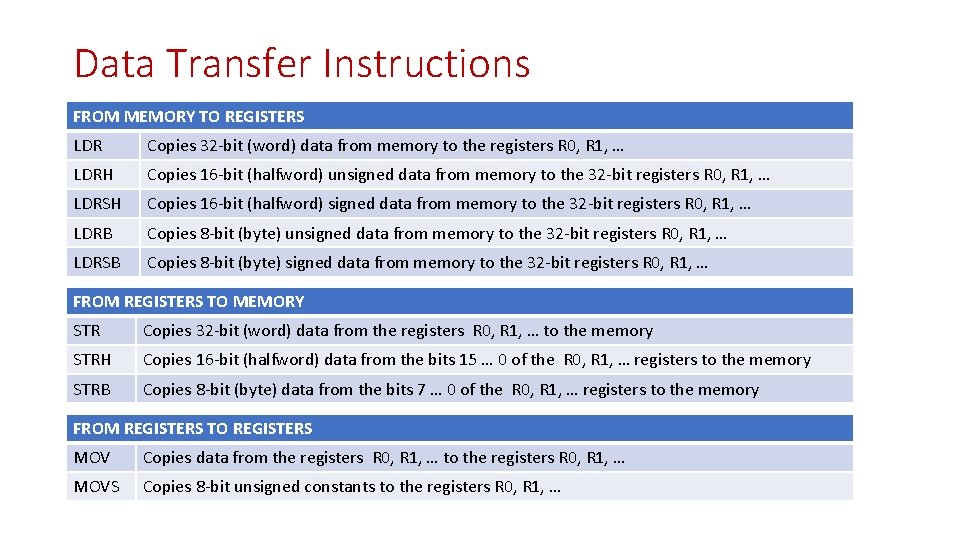

Data Transfer Instructions FROM MEMORY TO REGISTERS LDR Copies 32 -bit (word) data from memory to the registers R 0, R 1, … LDRH Copies 16 -bit (halfword) unsigned data from memory to the 32 -bit registers R 0, R 1, … LDRSH Copies 16 -bit (halfword) signed data from memory to the 32 -bit registers R 0, R 1, … LDRB Copies 8 -bit (byte) unsigned data from memory to the 32 -bit registers R 0, R 1, … LDRSB Copies 8 -bit (byte) signed data from memory to the 32 -bit registers R 0, R 1, … FROM REGISTERS TO MEMORY STR Copies 32 -bit (word) data from the registers R 0, R 1, … to the memory STRH Copies 16 -bit (halfword) data from the bits 15 … 0 of the R 0, R 1, … registers to the memory STRB Copies 8 -bit (byte) data from the bits 7 … 0 of the R 0, R 1, … registers to the memory FROM REGISTERS TO REGISTERS MOV Copies data from the registers R 0, R 1, … to the registers R 0, R 1, … MOVS Copies 8 -bit unsigned constants to the registers R 0, R 1, …

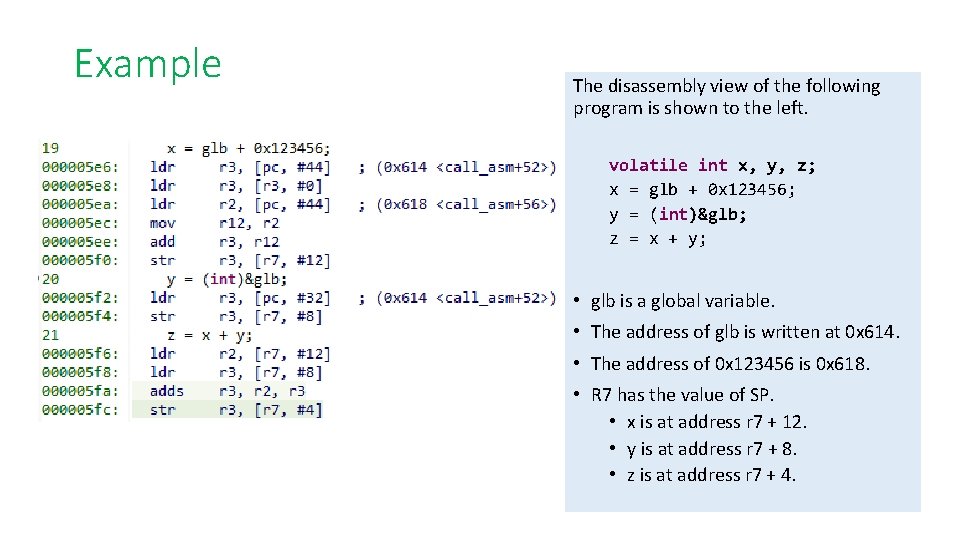

Example The disassembly view of the following program is shown to the left. volatile int x, y, z; x = glb + 0 x 123456; y = (int)&glb; z = x + y; • glb is a global variable. • The address of glb is written at 0 x 614. • The address of 0 x 123456 is 0 x 618. • R 7 has the value of SP. • x is at address r 7 + 12. • y is at address r 7 + 8. • z is at address r 7 + 4.

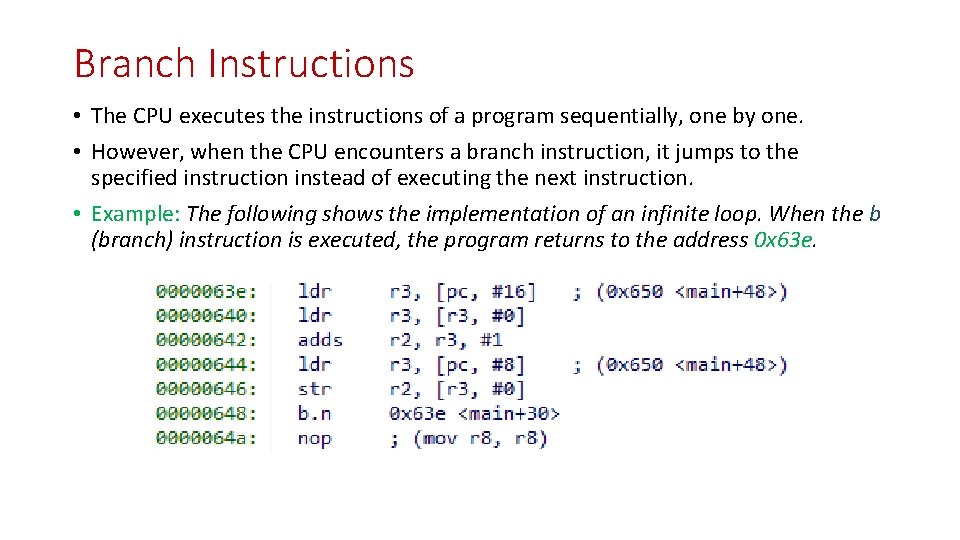

Branch Instructions • The CPU executes the instructions of a program sequentially, one by one. • However, when the CPU encounters a branch instruction, it jumps to the specified instruction instead of executing the next instruction. • Example: The following shows the implementation of an infinite loop. When the b (branch) instruction is executed, the program returns to the address 0 x 63 e.

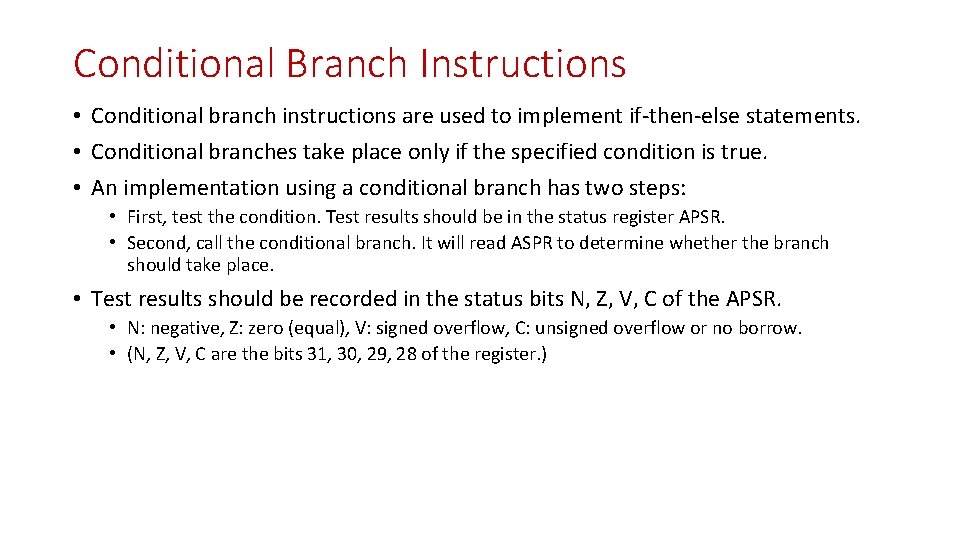

Conditional Branch Instructions • Conditional branch instructions are used to implement if-then-else statements. • Conditional branches take place only if the specified condition is true. • An implementation using a conditional branch has two steps: • First, test the condition. Test results should be in the status register APSR. • Second, call the conditional branch. It will read ASPR to determine whether the branch should take place. • Test results should be recorded in the status bits N, Z, V, C of the APSR. • N: negative, Z: zero (equal), V: signed overflow, C: unsigned overflow or no borrow. • (N, Z, V, C are the bits 31, 30, 29, 28 of the register. )

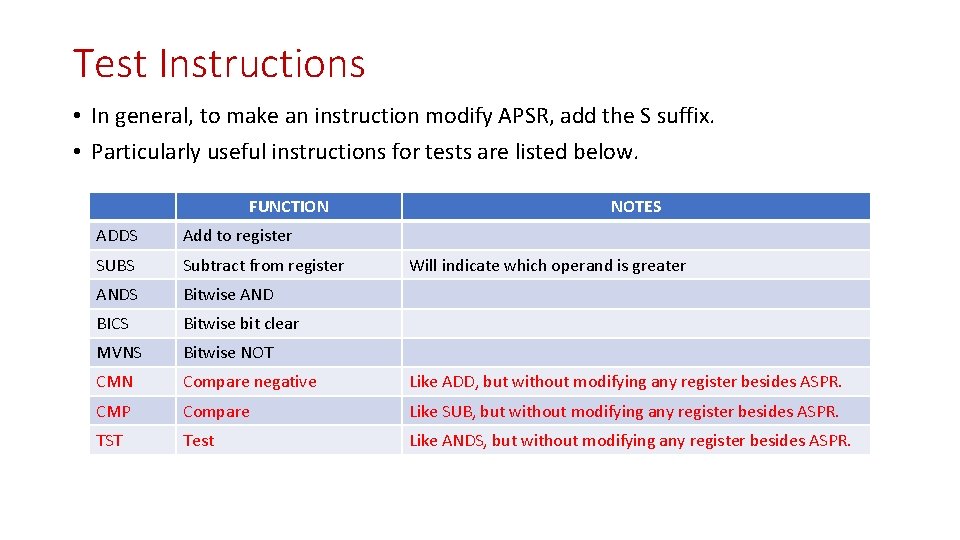

Test Instructions • In general, to make an instruction modify APSR, add the S suffix. • Particularly useful instructions for tests are listed below. FUNCTION NOTES ADDS Add to register SUBS Subtract from register ANDS Bitwise AND BICS Bitwise bit clear MVNS Bitwise NOT CMN Compare negative Like ADD, but without modifying any register besides ASPR. CMP Compare Like SUB, but without modifying any register besides ASPR. TST Test Like ANDS, but without modifying any register besides ASPR. Will indicate which operand is greater

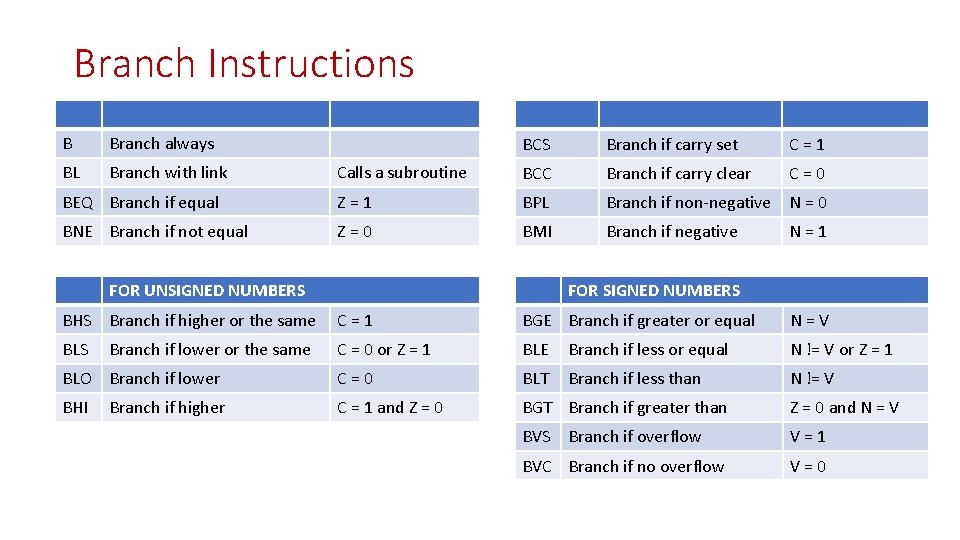

Branch Instructions B Branch always BL Branch with link BCS Branch if carry set C = 1 Calls a subroutine BCC Branch if carry clear C = 0 BEQ Branch if equal Z = 1 BPL Branch if non-negative N = 0 BNE Branch if not equal Z = 0 BMI Branch if negative FOR UNSIGNED NUMBERS N = 1 FOR SIGNED NUMBERS BHS Branch if higher or the same C = 1 BGE Branch if greater or equal N = V BLS C = 0 or Z = 1 BLE Branch if less or equal N != V or Z = 1 BLO Branch if lower C = 0 BLT Branch if less than N != V BHI C = 1 and Z = 0 BGT Branch if greater than Z = 0 and N = V BVS Branch if overflow V = 1 BVC Branch if no overflow V = 0 Branch if lower or the same Branch if higher

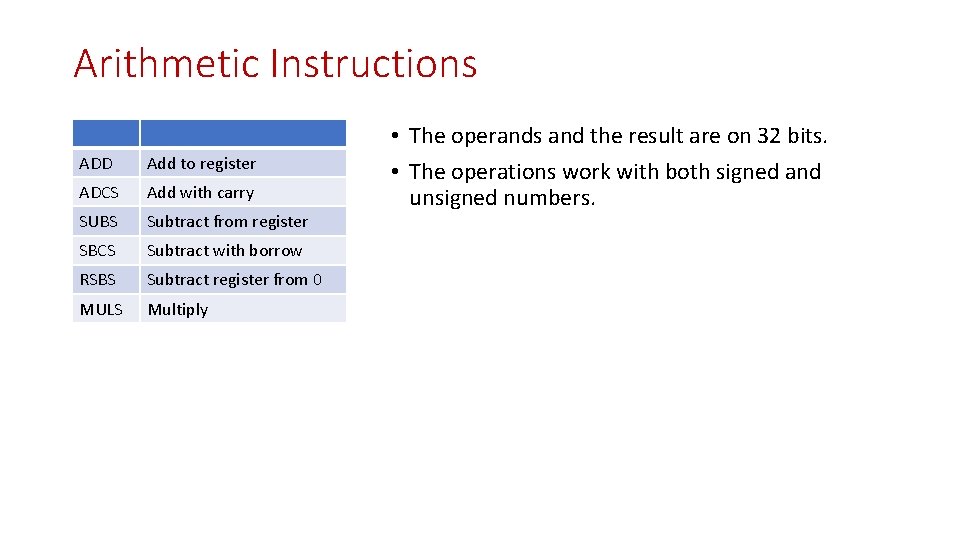

Arithmetic Instructions ADD Add to register ADCS Add with carry SUBS Subtract from register SBCS Subtract with borrow RSBS Subtract register from 0 MULS Multiply • The operands and the result are on 32 bits. • The operations work with both signed and unsigned numbers.

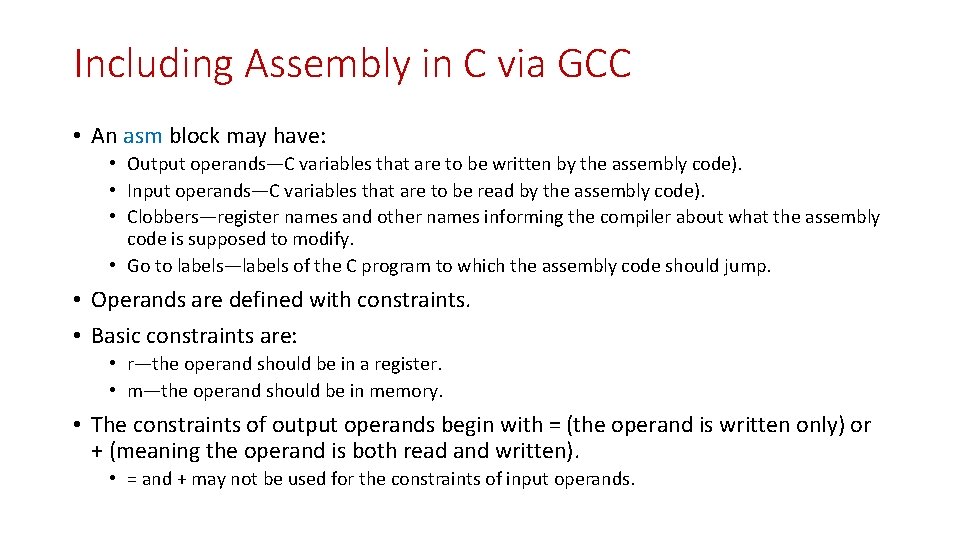

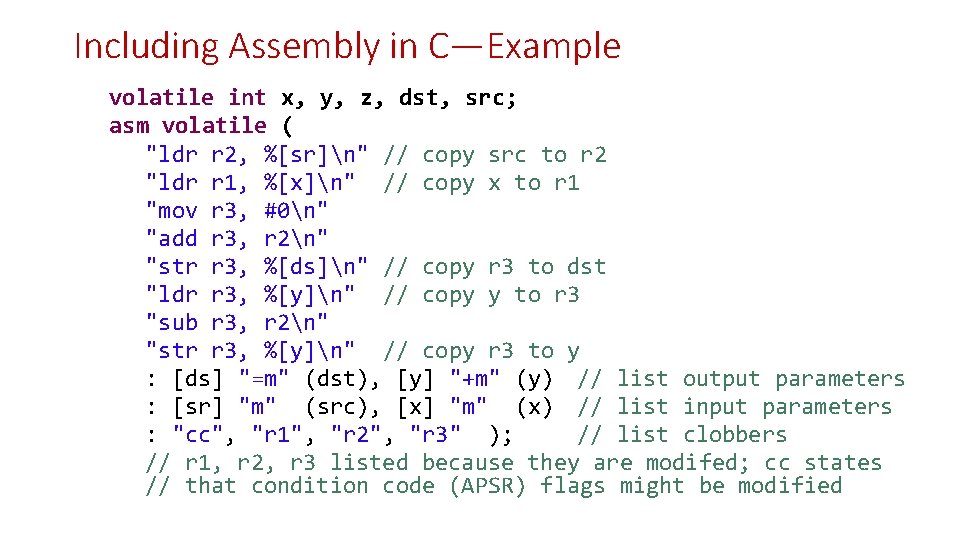

Including Assembly in C via GCC • An asm block may have: • Output operands—C variables that are to be written by the assembly code). • Input operands—C variables that are to be read by the assembly code). • Clobbers—register names and other names informing the compiler about what the assembly code is supposed to modify. • Go to labels—labels of the C program to which the assembly code should jump. • Operands are defined with constraints. • Basic constraints are: • r—the operand should be in a register. • m—the operand should be in memory. • The constraints of output operands begin with = (the operand is written only) or + (meaning the operand is both read and written). • = and + may not be used for the constraints of input operands.

Including Assembly in C—Example volatile int x, y, z, dst, src; asm volatile ( "ldr r 2, %[sr]n" // copy src to r 2 "ldr r 1, %[x]n" // copy x to r 1 "mov r 3, #0n" "add r 3, r 2n" "str r 3, %[ds]n" // copy r 3 to dst "ldr r 3, %[y]n" // copy y to r 3 "sub r 3, r 2n" "str r 3, %[y]n" // copy r 3 to y : [ds] "=m" (dst), [y] "+m" (y) // list output parameters : [sr] "m" (src), [x] "m" (x) // list input parameters : "cc", "r 1", "r 2", "r 3" ); // list clobbers // r 1, r 2, r 3 listed because they are modifed; cc states // that condition code (APSR) flags might be modified

- Slides: 14