Assembly Lang Intel 8086 Ch 7 Logic Shift

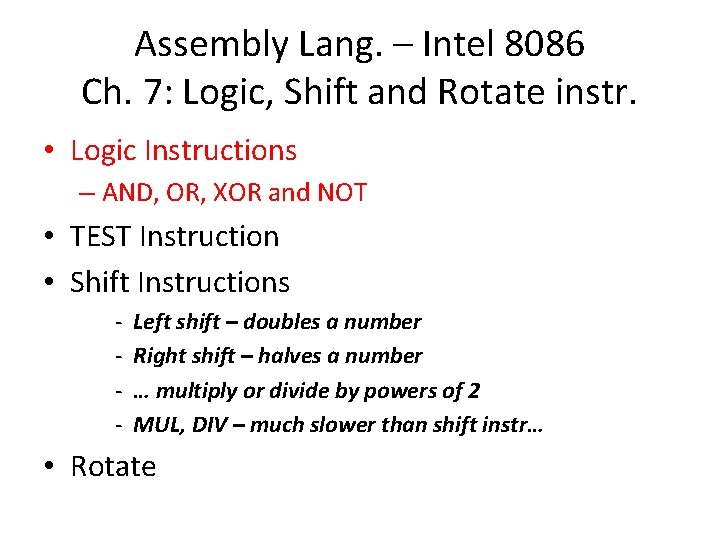

Assembly Lang. – Intel 8086 Ch. 7: Logic, Shift and Rotate instr. • Logic Instructions – AND, OR, XOR and NOT • TEST Instruction • Shift Instructions - Left shift – doubles a number Right shift – halves a number … multiply or divide by powers of 2 MUL, DIV – much slower than shift instr… • Rotate

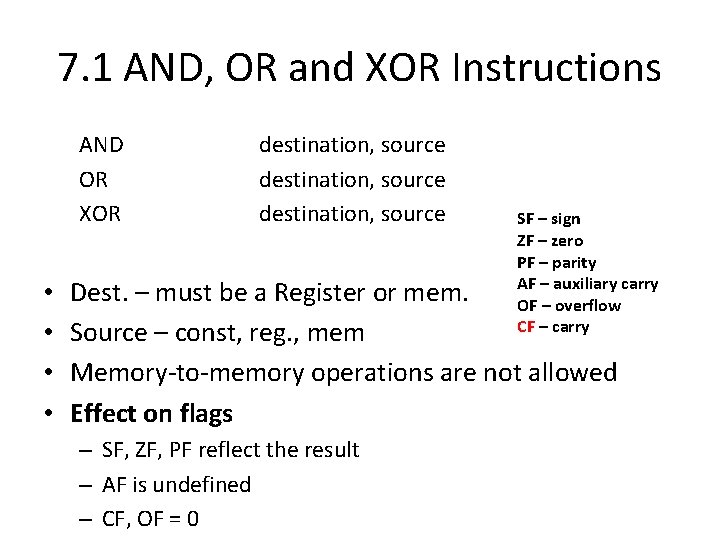

7. 1 AND, OR and XOR Instructions AND OR XOR • • destination, source SF – sign ZF – zero PF – parity AF – auxiliary carry OF – overflow CF – carry Dest. – must be a Register or mem. Source – const, reg. , mem Memory-to-memory operations are not allowed Effect on flags – SF, ZF, PF reflect the result – AF is undefined – CF, OF = 0

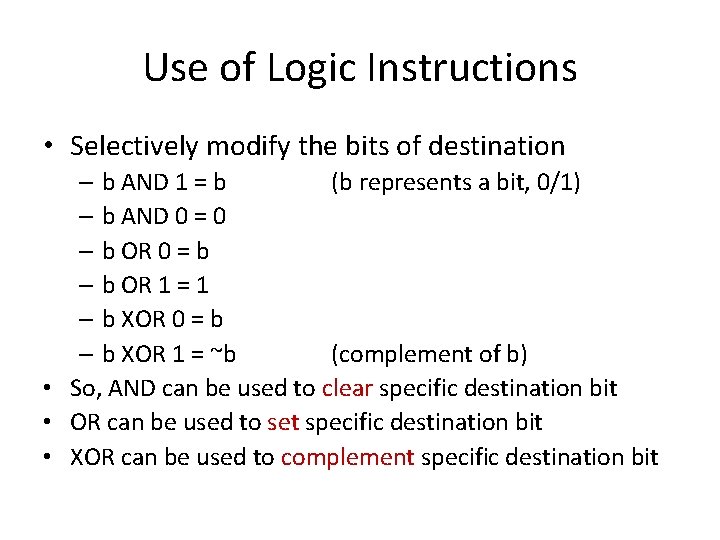

Use of Logic Instructions • Selectively modify the bits of destination – b AND 1 = b (b represents a bit, 0/1) – b AND 0 = 0 – b OR 0 = b – b OR 1 = 1 – b XOR 0 = b – b XOR 1 = ~b (complement of b) • So, AND can be used to clear specific destination bit • OR can be used to set specific destination bit • XOR can be used to complement specific destination bit

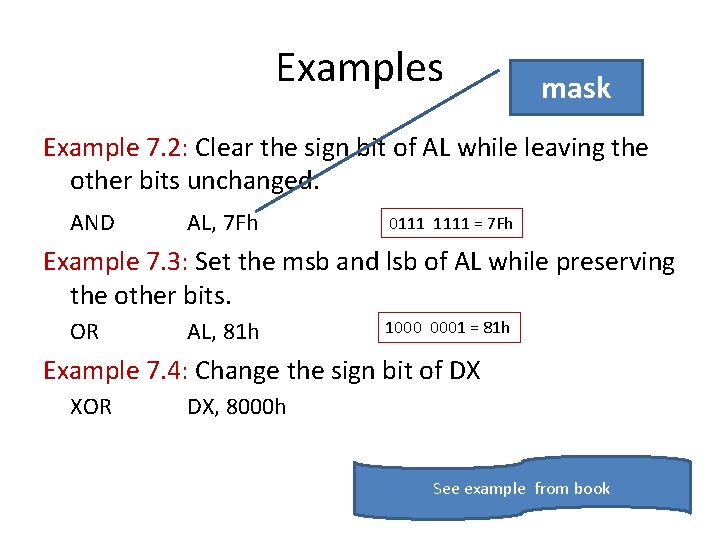

Examples mask Example 7. 2: Clear the sign bit of AL while leaving the other bits unchanged. AND AL, 7 Fh 0111 1111 = 7 Fh Example 7. 3: Set the msb and lsb of AL while preserving the other bits. OR AL, 81 h 1000 0001 = 81 h Example 7. 4: Change the sign bit of DX XOR DX, 8000 h See example from book

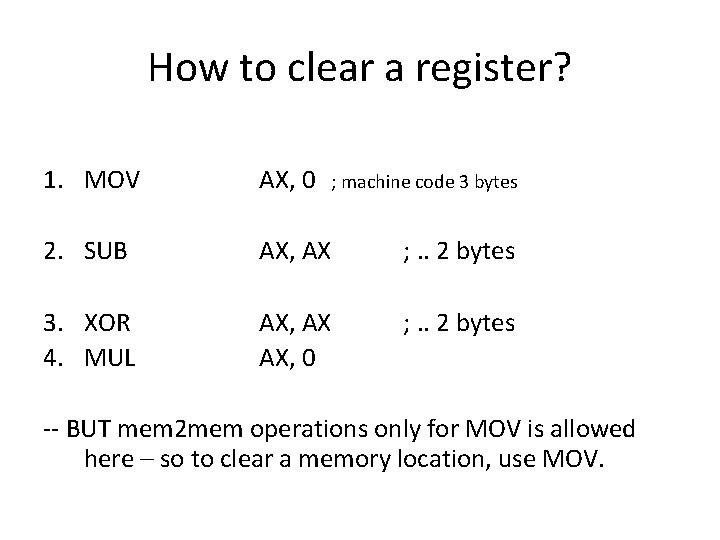

How to clear a register? 1. MOV AX, 0 2. SUB AX, AX ; . . 2 bytes 3. XOR 4. MUL AX, AX AX, 0 ; . . 2 bytes ; machine code 3 bytes -- BUT mem 2 mem operations only for MOV is allowed here – so to clear a memory location, use MOV.

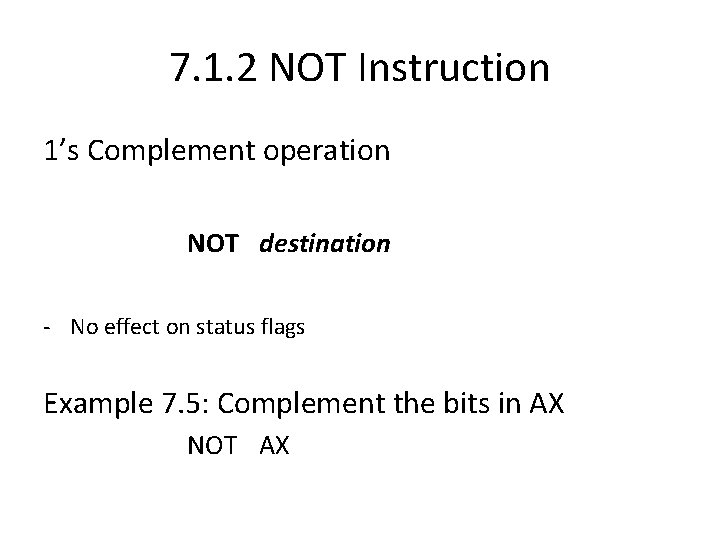

7. 1. 2 NOT Instruction 1’s Complement operation NOT destination - No effect on status flags Example 7. 5: Complement the bits in AX NOT AX

7 • Logic Instructions – AND, OR, XOR and NOT • • TEST Instruction Shift and Rotate Instructions Stack Operations Introduction to Procedures

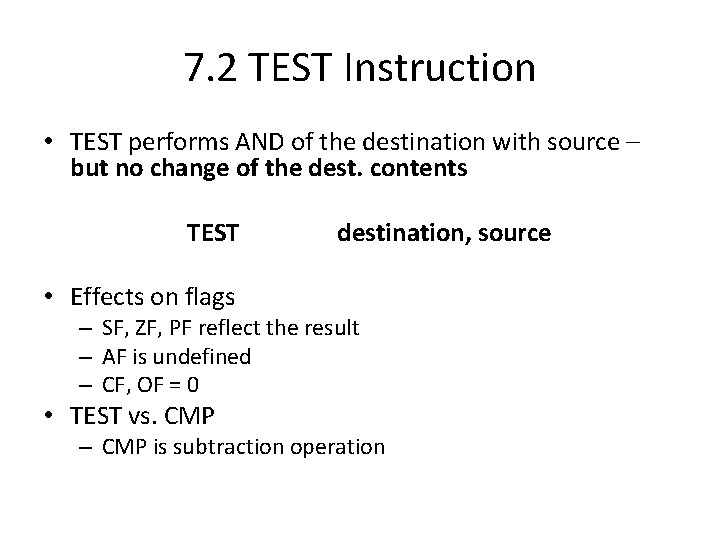

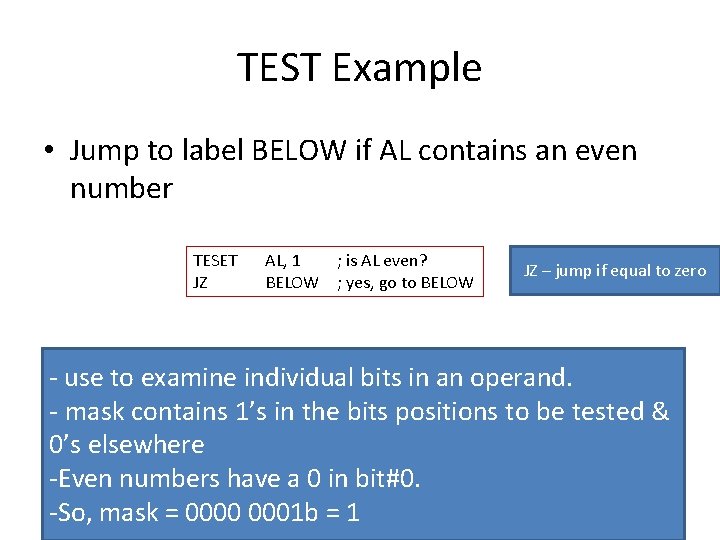

7. 2 TEST Instruction • TEST performs AND of the destination with source – but no change of the dest. contents TEST destination, source • Effects on flags – SF, ZF, PF reflect the result – AF is undefined – CF, OF = 0 • TEST vs. CMP – CMP is subtraction operation

TEST Example • Jump to label BELOW if AL contains an even number TESET JZ AL, 1 ; is AL even? BELOW ; yes, go to BELOW JZ – jump if equal to zero - use to examine individual bits in an operand. - mask contains 1’s in the bits positions to be tested & 0’s elsewhere -Even numbers have a 0 in bit#0. -So, mask = 0000 0001 b = 1

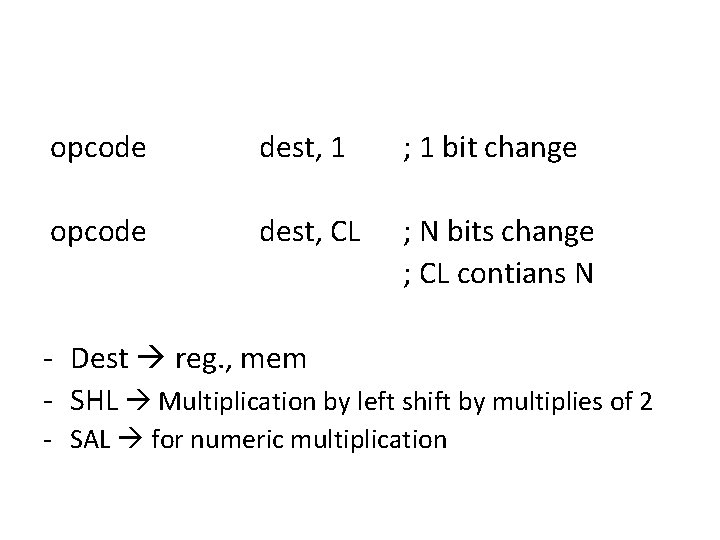

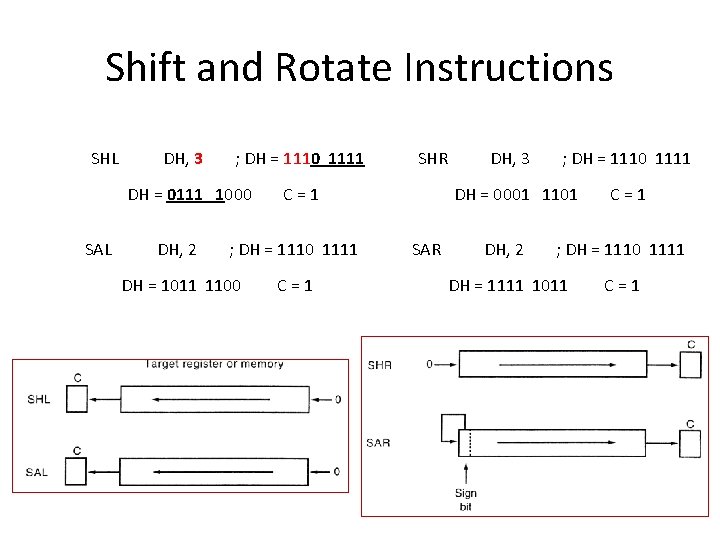

7. 2 Shift and Rotate Instructions • Two types of shift and rotate instructions – Logical Shift / Rotate – Arithmetic Shift/Rotate • Both logical and arithmetic left shift are identical • But right shifts are different

opcode dest, 1 ; 1 bit change opcode dest, CL ; N bits change ; CL contians N - Dest reg. , mem - SHL Multiplication by left shift by multiplies of 2 - SAL for numeric multiplication

Shift and Rotate Instructions SHL DH, 3 ; DH = 1110 1111 DH = 0111 1000 SAL DH, 2 C=1 ; DH = 1110 1111 DH = 1011 1100 SHR C=1 DH, 3 ; DH = 1110 1111 DH = 0001 1101 SAR DH, 2 C=1 ; DH = 1110 1111 DH = 1111 1011 C=1

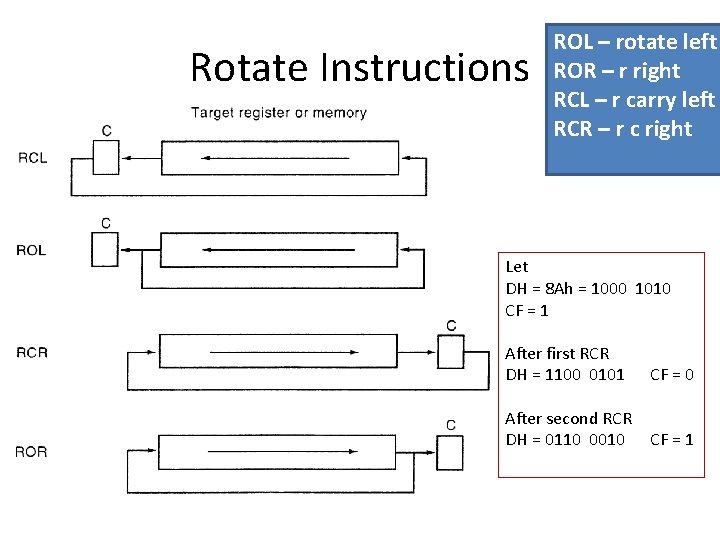

Rotate Instructions ROL – rotate left ROR – r right RCL – r carry left RCR – r c right Let DH = 8 Ah = 1000 1010 CF = 1 After first RCR DH = 1100 0101 CF = 0 After second RCR DH = 0110 0010 CF = 1

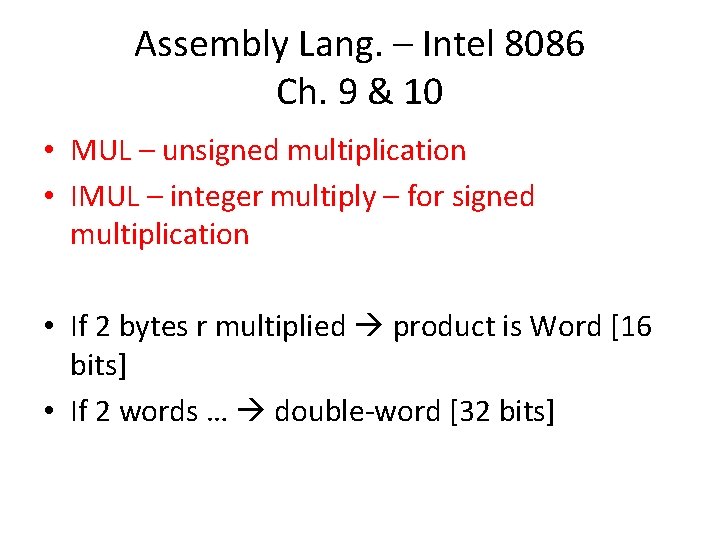

Assembly Lang. – Intel 8086 Ch. 9 & 10 • MUL – unsigned multiplication • IMUL – integer multiply – for signed multiplication • If 2 bytes r multiplied product is Word [16 bits] • If 2 words … double-word [32 bits]

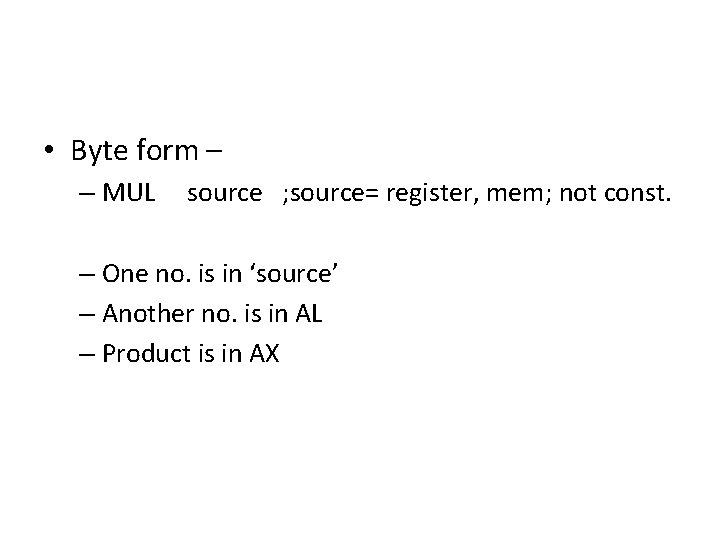

• Byte form – – MUL source ; source= register, mem; not const. – One no. is in ‘source’ – Another no. is in AL – Product is in AX

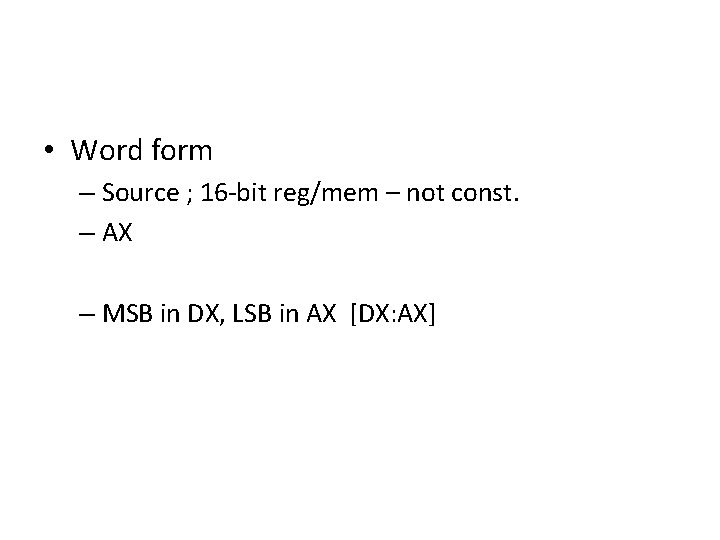

• Word form – Source ; 16 -bit reg/mem – not const. – AX – MSB in DX, LSB in AX [DX: AX]

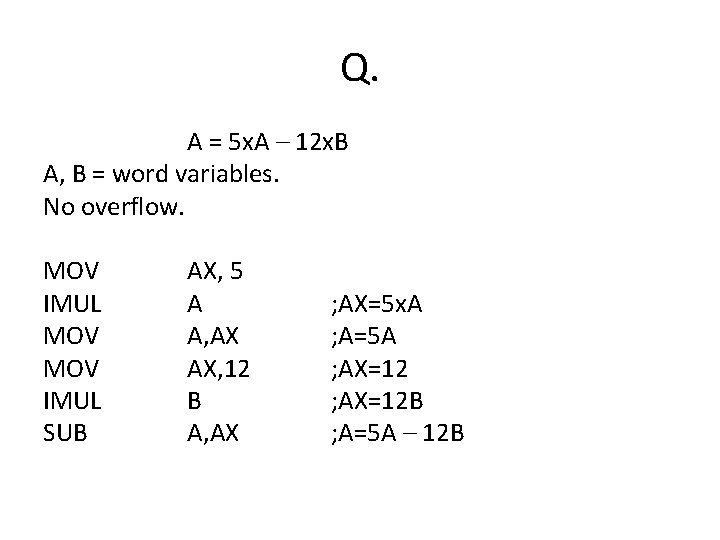

Q. A = 5 x. A – 12 x. B A, B = word variables. No overflow. MOV IMUL SUB AX, 5 A A, AX AX, 12 B A, AX ; AX=5 x. A ; A=5 A ; AX=12 B ; A=5 A – 12 B

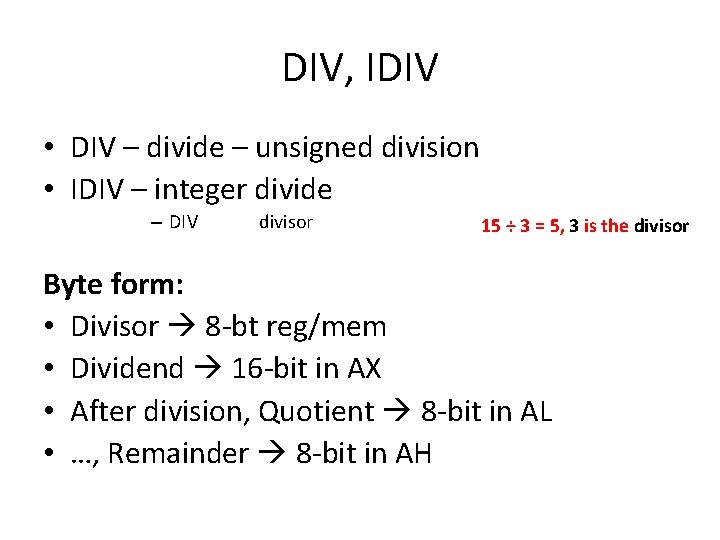

DIV, IDIV • DIV – divide – unsigned division • IDIV – integer divide – DIV divisor 15 ÷ 3 = 5, 3 is the divisor Byte form: • Divisor 8 -bt reg/mem • Dividend 16 -bit in AX • After division, Quotient 8 -bit in AL • …, Remainder 8 -bit in AH

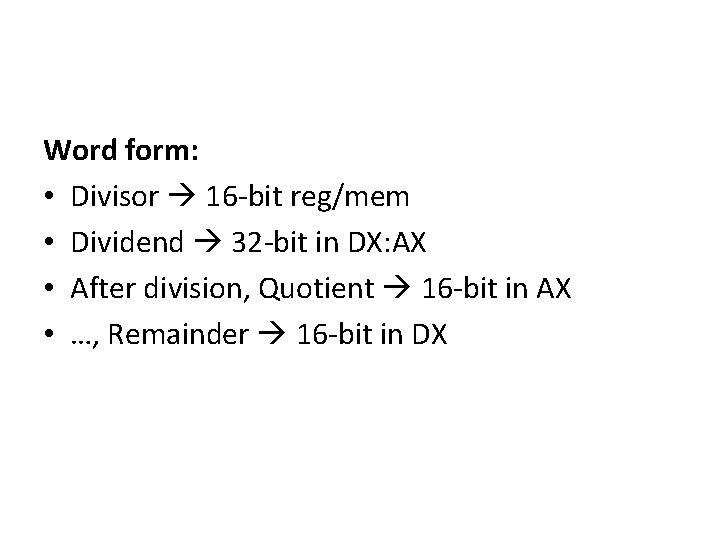

Word form: • Divisor 16 -bit reg/mem • Dividend 32 -bit in DX: AX • After division, Quotient 16 -bit in AX • …, Remainder 16 -bit in DX

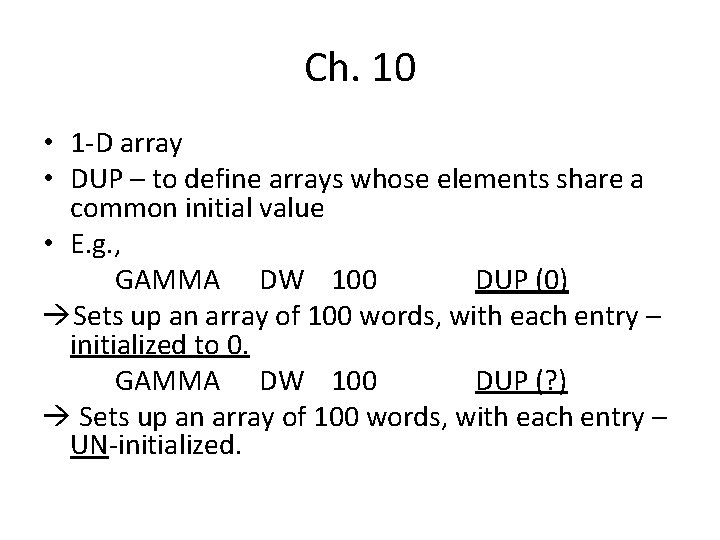

Ch. 10 • 1 -D array • DUP – to define arrays whose elements share a common initial value • E. g. , GAMMA DW 100 DUP (0) Sets up an array of 100 words, with each entry – initialized to 0. GAMMA DW 100 DUP (? ) Sets up an array of 100 words, with each entry – UN-initialized.

- Slides: 21