ASSEMBLING THE INC INSTRUCTION INC AX INC CX

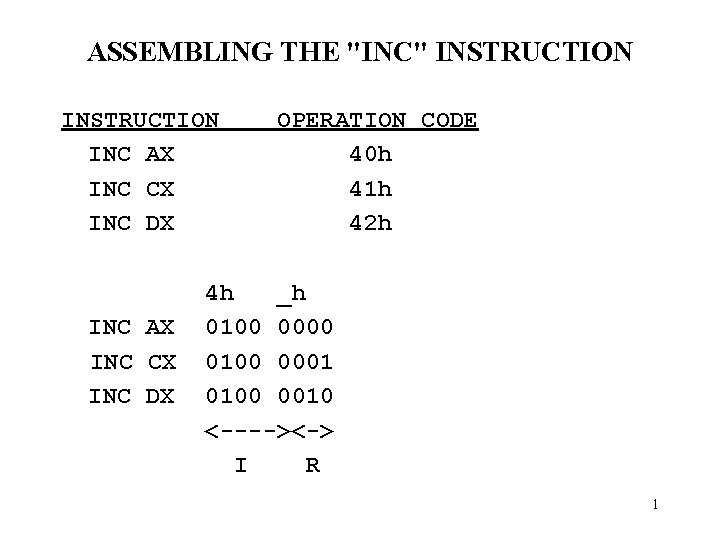

ASSEMBLING THE "INC" INSTRUCTION INC AX INC CX INC DX OPERATION CODE 40 h 41 h 42 h 4 h _h 0100 0000 0100 0001 0100 0010 <----><-> I R 1

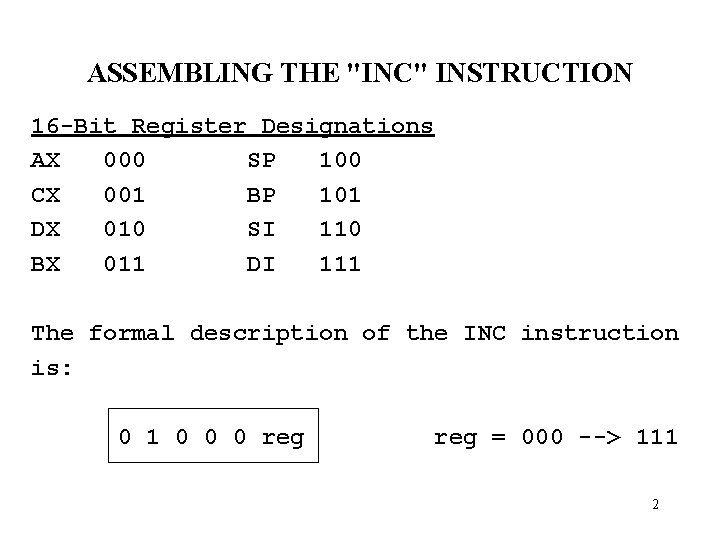

ASSEMBLING THE "INC" INSTRUCTION 16 -Bit Register Designations AX 000 SP 100 CX 001 BP 101 DX 010 SI 110 BX 011 DI 111 The formal description of the INC instruction is: 0 1 0 0 0 reg = 000 --> 111 2

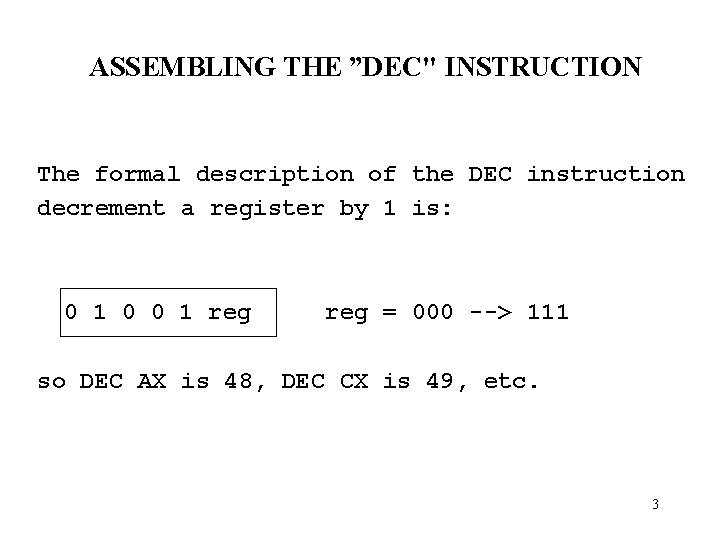

ASSEMBLING THE ”DEC" INSTRUCTION The formal description of the DEC instruction decrement a register by 1 is: 0 1 0 0 1 reg = 000 --> 111 so DEC AX is 48, DEC CX is 49, etc. 3

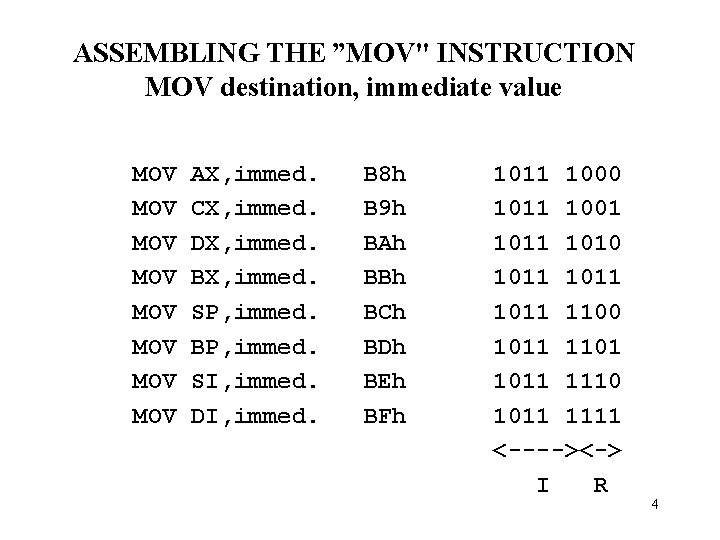

ASSEMBLING THE ”MOV" INSTRUCTION MOV destination, immediate value MOV MOV AX, immed. CX, immed. DX, immed. BX, immed. SP, immed. BP, immed. SI, immed. DI, immed. B 8 h B 9 h BAh BBh BCh BDh BEh BFh 1011 1000 1011 1001 1010 1011 1100 1011 1101 1011 1110 1011 1111 <----><-> I R 4

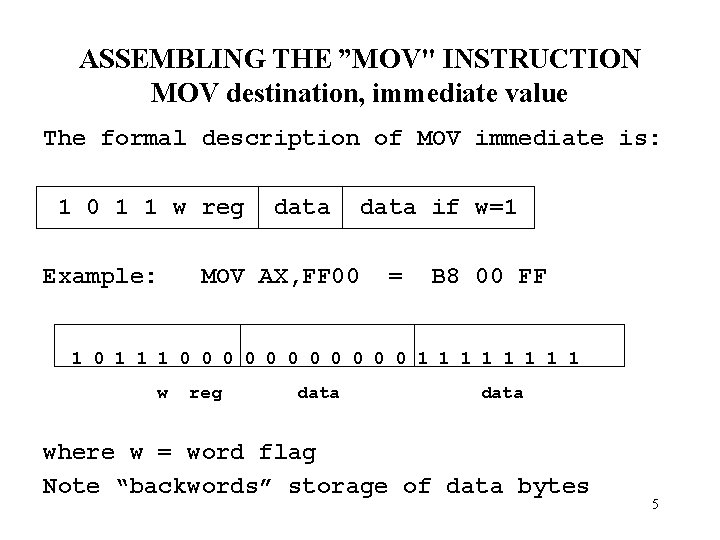

ASSEMBLING THE ”MOV" INSTRUCTION MOV destination, immediate value The formal description of MOV immediate is: 1 0 1 1 w reg Example: data MOV AX, FF 00 data if w=1 = B 8 00 FF 1 0 1 1 1 0 0 0 1 1 1 1 w reg data where w = word flag Note “backwords” storage of data bytes 5

ASSEMBLING THE ”MOV" INSTRUCTION MOV destination, immediate value Consider: MOV AL, FF = B 0 FF 1 0 1 1 0 0 1 1 1 1 w reg data The 8 -bit AL CL DL BL registers 000 001 010 011 are designated: AH 100 CH 101 DH 110 BH 111 6

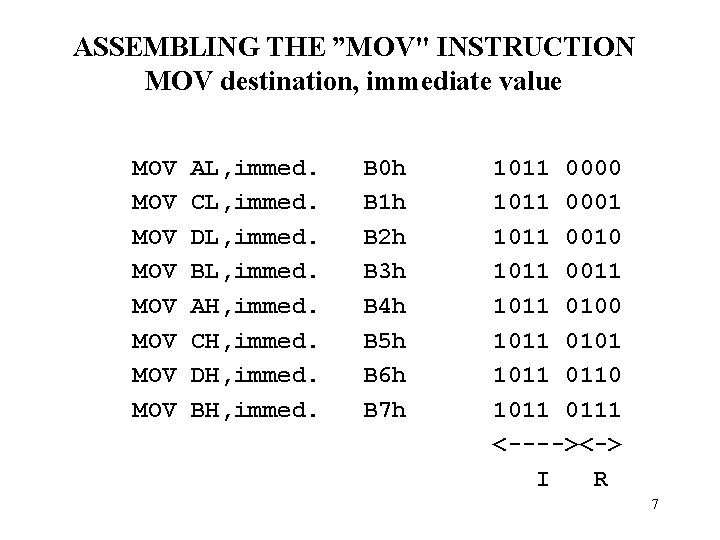

ASSEMBLING THE ”MOV" INSTRUCTION MOV destination, immediate value MOV MOV AL, immed. CL, immed. DL, immed. BL, immed. AH, immed. CH, immed. DH, immed. BH, immed. B 0 h B 1 h B 2 h B 3 h B 4 h B 5 h B 6 h B 7 h 1011 0000 1011 0001 1011 0010 1011 0011 1011 0100 1011 0101 1011 0110 1011 0111 <----><-> I R 7

ASSEMBLING THE ”MOV" INSTRUCTION MOV register, register 1 0 0 0 1 0 d w mod reg operation code EA byte r/m w = word flag: w=0: byte; w=1: word d = direction flag: d=1: reg is destination d=0: r/m is destination mod = mode indicator: 4 possible values: 00, 01, 10, 11 reg = register r/m = register or memory indicator EA = effective address: “move what to where” 8

ASSEMBLING THE ”MOV" INSTRUCTION MOV register, register Examples: MOV BX, BP 1 0 0 0 1 1 1 1 0 1 d w mod reg = r/m = BX BP 8 B DD MOV BP, BX 1 0 0 0 1 1 1 0 1 1 d w mod reg = r/m = BP BX 8 B EB MOV BP, BX 1 0 0 0 1 1 1 0 1 d w mod reg = r/m = BX BP 89 DD 9

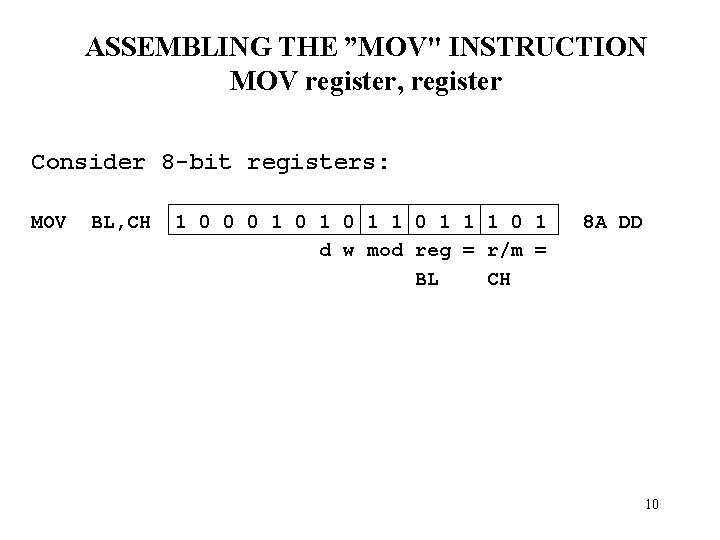

ASSEMBLING THE ”MOV" INSTRUCTION MOV register, register Consider 8 -bit registers: MOV BL, CH 1 0 0 0 1 0 1 1 1 0 1 d w mod reg = r/m = BL CH 8 A DD 10

ASSEMBLING THE ”MOV" INSTRUCTION MOV register, memory or MOV memory, register 1 0 0 0 1 0 d w mod reg r/m LSB of offset MSB of offset 1 0 0 0 1 1 0 0 0 0 0 1 1 0 0 d w mod reg r/m LSB of offset MOV BX, [F 000] = 8 B 1 E 00 F 0 • mod=00 and r/m=110 signify the bytes following the EA byte are an offset address • Implied segment is DS: [F 000] • Note “backwords” storage of F 000. 11

![ASSEMBLING THE ”MOV" INSTRUCTION MOV register, memory or MOV memory, register MOV [F 000], ASSEMBLING THE ”MOV" INSTRUCTION MOV register, memory or MOV memory, register MOV [F 000],](http://slidetodoc.com/presentation_image_h/9041bf4864f803db05473fca0488f3e9/image-12.jpg)

ASSEMBLING THE ”MOV" INSTRUCTION MOV register, memory or MOV memory, register MOV [F 000], BX Move the contents of register BX to location DS: F 000 1 0 0 0 1 1 0 0 0 0 0 F F 0 0 d w mod reg ADD [F 000], BX r/m LSB MSB Add register BX to the contents of location DS: F 000 CMP CX, [0080] Compare register CX with the byte at location DS: 0800 12

ASSEMBLING THE ”MOV" INSTRUCTION MOV register, memory or MOV memory, register MOD=00 (and R/M isn't 110) In this case r/m specifies a register in which to find an address, as in: mod reg r/m MOV AX, [SI] 1 0 0 0 1 0 0 d w AX -----SI---"Move the contents of the address in SI to AX. " The three registers that may be used in this way, along with their r/m values are: 100=SI, 101=DI, 111=BX. 13

- Slides: 13