ASIC buck converter prototypes for LHC upgrades S

ASIC buck converter prototypes for LHC upgrades S. Michelis 1, 3, C. Azra 3, B. Allongue 1, G. Blanchot 1, F. Faccio 1, C. Fuentes 1, 2, S. Orlandi 1 1 CERN – PH-ESE 2 UTFSM, Valparaiso, Chile 3 EPFL, Lausanne

Outline Introduction Ø AMIS 2 Ø l l l Ø IHP 1 l Ø Features Pinout Waveforms Efficiency Radiation results Noise performances Features Conclusions Twepp 09, Paris S. Michelis CERN/PH 2

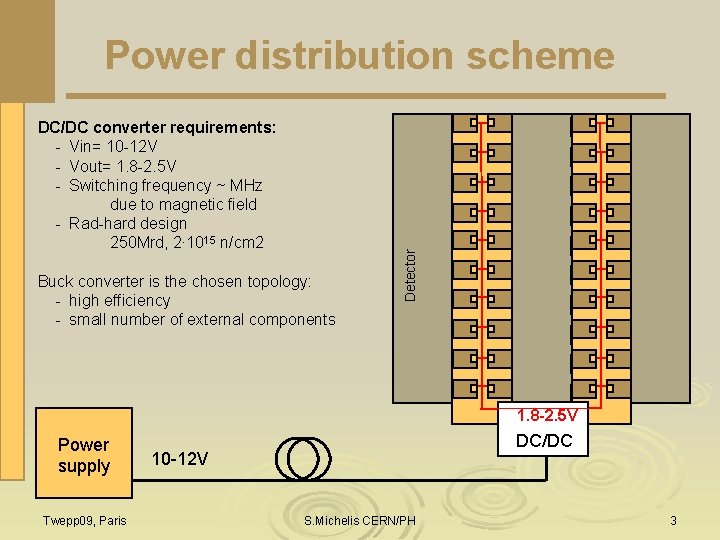

DC/DC converter requirements: - Vin= 10 -12 V - Vout= 1. 8 -2. 5 V - Switching frequency ~ MHz due to magnetic field - Rad-hard design 250 Mrd, 2∙ 1015 n/cm 2 Buck converter is the chosen topology: - high efficiency - small number of external components Detector Power distribution scheme 1. 8 -2. 5 V Power supply Twepp 09, Paris DC/DC 10 -12 V S. Michelis CERN/PH 3

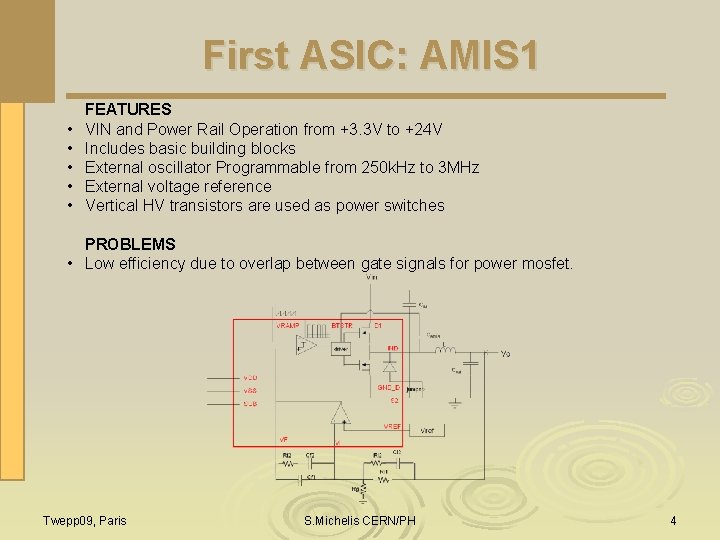

First ASIC: AMIS 1 • • • FEATURES VIN and Power Rail Operation from +3. 3 V to +24 V Includes basic building blocks External oscillator Programmable from 250 k. Hz to 3 MHz External voltage reference Vertical HV transistors are used as power switches PROBLEMS • Low efficiency due to overlap between gate signals for power mosfet. Twepp 09, Paris S. Michelis CERN/PH 4

Second ASIC: AMIS 2 • • FEATURES VIN and Power Rail Operation from +3. 3 V to +12 V Internal oscillator fixed at 1 Mhz, programmable up to 2. 5 MHz with external resistor Internal voltage reference Programmable delay between gate signals Integrated feedback loop with bandwidth of 20 Khz Different Vout can be set: 1. 2 V, 1. 8 V, 2. 5 V, 3 V, 5 V Lateral HV transistors are used as power switches Enable pin Twepp 09, Paris S. Michelis CERN/PH 5

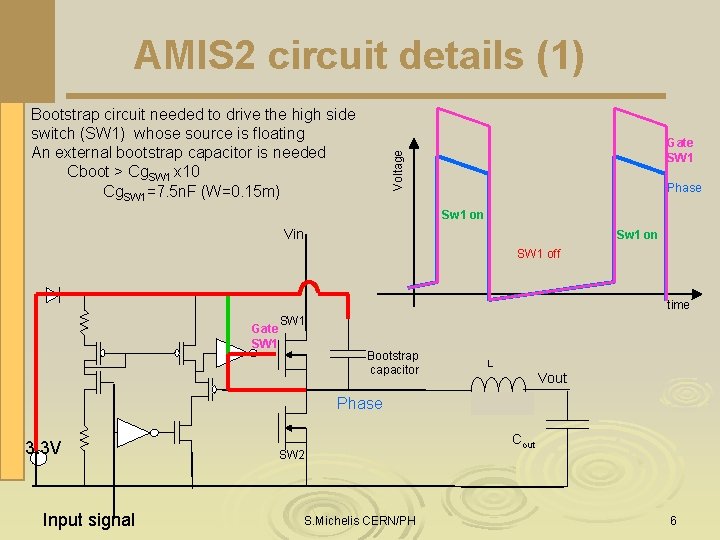

AMIS 2 circuit details (1) Gate SW 1 Voltage Bootstrap circuit needed to drive the high side switch (SW 1) whose source is floating An external bootstrap capacitor is needed Cboot > Cg. SW 1 x 10 Cg. SW 1=7. 5 n. F (W=0. 15 m) Phase Sw 1 on Vin Sw 1 on SW 1 off time Gate SW 1 Bootstrap capacitor L Vout Phase 3. 3 V Input signal SW 2 S. Michelis CERN/PH Cout 6

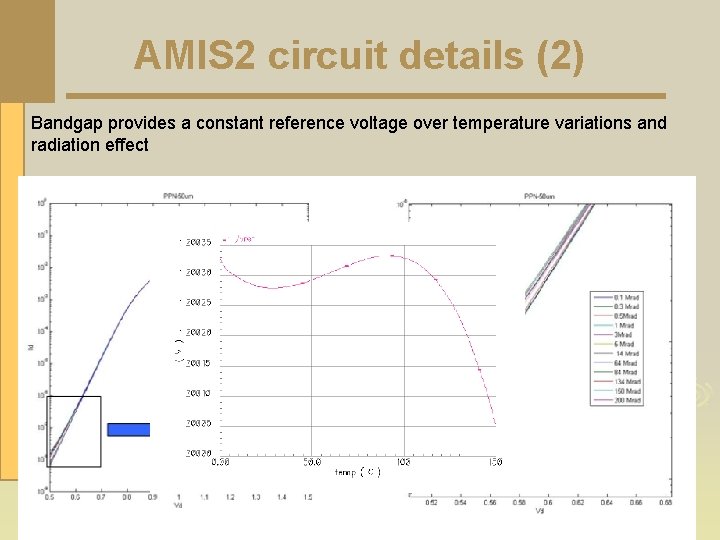

AMIS 2 circuit details (2) Bandgap provides a constant reference voltage over temperature variations and radiation effect Twepp 09, Paris S. Michelis CERN/PH 7

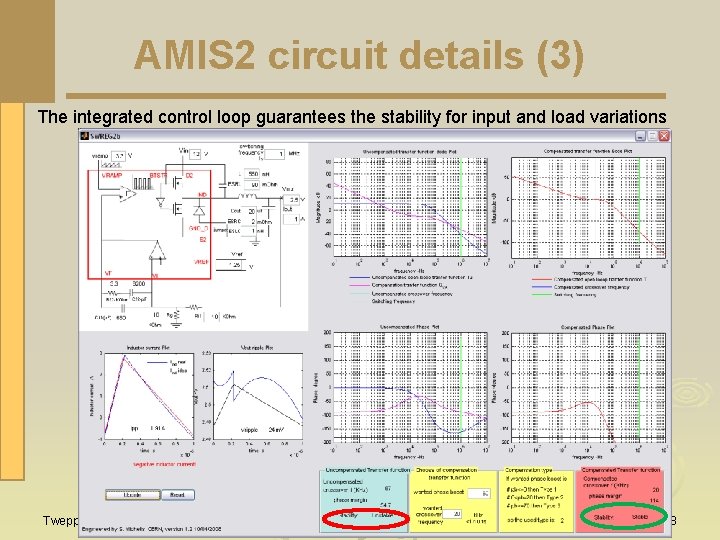

AMIS 2 circuit details (3) The integrated control loop guarantees the stability for input and load variations Twepp 09, Paris S. Michelis CERN/PH 8

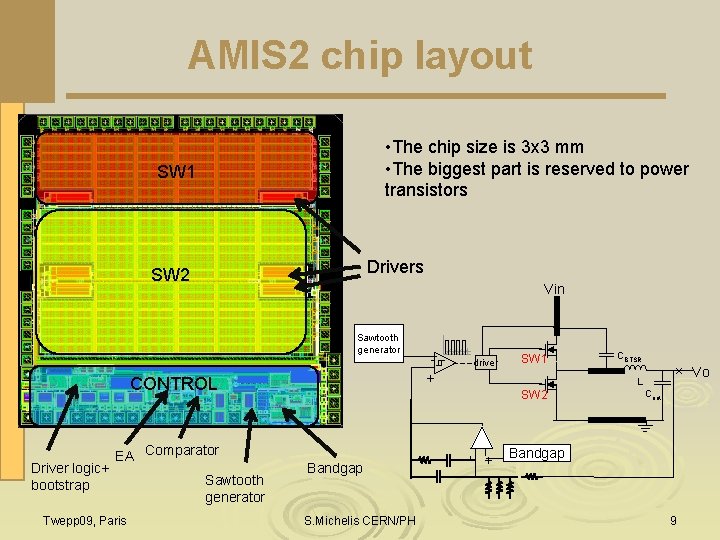

AMIS 2 chip layout • The chip size is 3 x 3 mm • The biggest part is reserved to power transistors SW 1 Drivers SW 2 Vin CONTROL Twepp 09, Paris Sawtooth generator driver SW 1 SW 2 Bandgap S. Michelis CERN/PH CBTSR Vo L + - Driver logic+ bootstrap EA Comparator + - Sawtooth generator Cout Bandgap 9

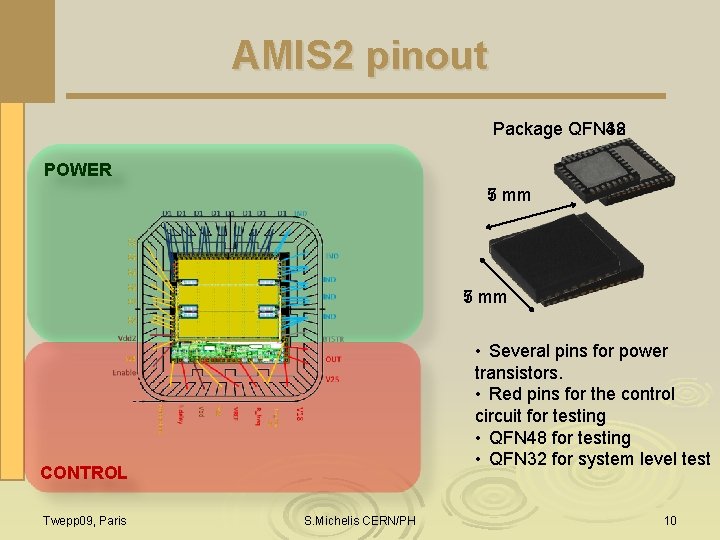

AMIS 2 pinout Package QFN 32 QFN 48 POWER 7 mm 5 7 5 mm • Several pins for power transistors. • Red pins for the control circuit for testing • QFN 48 for testing • QFN 32 for system level test CONTROL Twepp 09, Paris S. Michelis CERN/PH 10

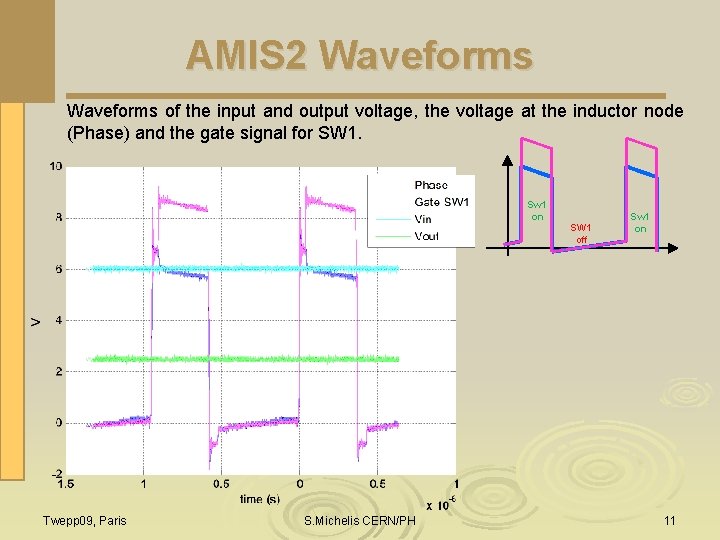

AMIS 2 Waveforms of the input and output voltage, the voltage at the inductor node (Phase) and the gate signal for SW 1. Sw 1 on Twepp 09, Paris S. Michelis CERN/PH SW 1 off Sw 1 on 11

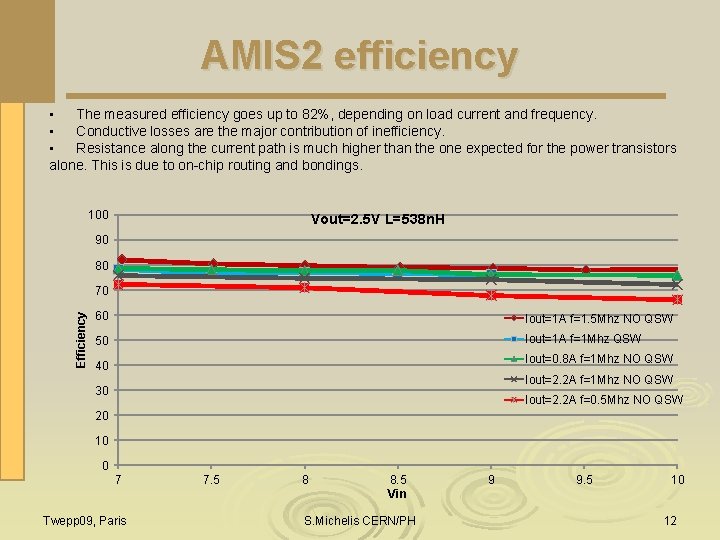

AMIS 2 efficiency • The measured efficiency goes up to 82%, depending on load current and frequency. • Conductive losses are the major contribution of inefficiency. • Resistance along the current path is much higher than the one expected for the power transistors alone. This is due to on-chip routing and bondings. 100 Vout=2. 5 V L=538 n. H 90 80 Efficiency 70 60 Iout=1 A f=1. 5 Mhz NO QSW 50 Iout=1 A f=1 Mhz QSW Iout=0. 8 A f=1 Mhz NO QSW 40 Iout=2. 2 A f=1 Mhz NO QSW 30 Iout=2. 2 A f=0. 5 Mhz NO QSW 20 10 0 7 Twepp 09, Paris 7. 5 8 8. 5 Vin S. Michelis CERN/PH 9 9. 5 10 12

Mos resistance Bonding RBond=80 mΩ Metals RM=50 mΩ Silicon RSi=30 mΩ Package QFN 48 Total resistance Rtot=RSi+RM+RBond=160 mΩ (more than RSi x 5) Big impact of bondings and metal routing QFN 32 will reduce a bit the bonding resistance Final integration maybe with flip chip. It can drastically reduce the conductive losses

AMIS 2 Radiation results The X-ray radiation tests shows a decrease of the efficiency mostly due to the radiation induced leakage current , compensated by the threshold voltage shift. 100 82 Efficiencyvs vs. TID 90 80 80 78 70 Efficiency (%) 76 60 Vin=10 50 74 Vin=9 Vin=8 40 72 Vin=7 30 70 20 68 10 66 0 Pre rad 1. 00 E+04 Twepp 09, Paris 1. 00 E+05 1. 00 E+06 1. 00 E+07 1. 00 E+08 TID(rad) S. Michelis CERN/PH Annealing 1. 00 E+09 1. 00 E+10 3 days 7 days 1. 00 E+11 14

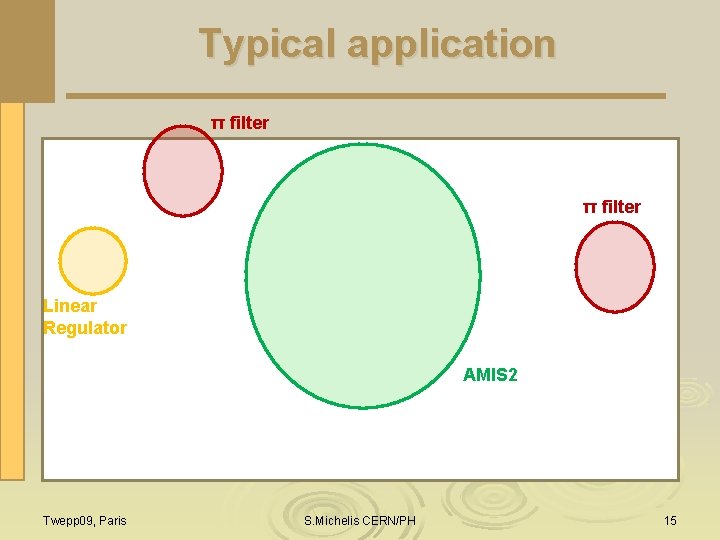

Typical application π filter Linear Regulator AMIS 2 Twepp 09, Paris S. Michelis CERN/PH 15

Noise tests with AMIS 2 Ø The AMIS 2 power ASIC was mounted on 3 different prototypes: same schematic, different layouts. Ø PCB and Coilcraft coils were tested. l Several placements were exercised. Ø CM, DM and LISN figures were acquired. l The reference setup was used. l Load = 0. 9 A x 2. 5 V, Switch frequency = 1. 55 MHz. Twepp 09, Paris S. Michelis CERN/PH 16

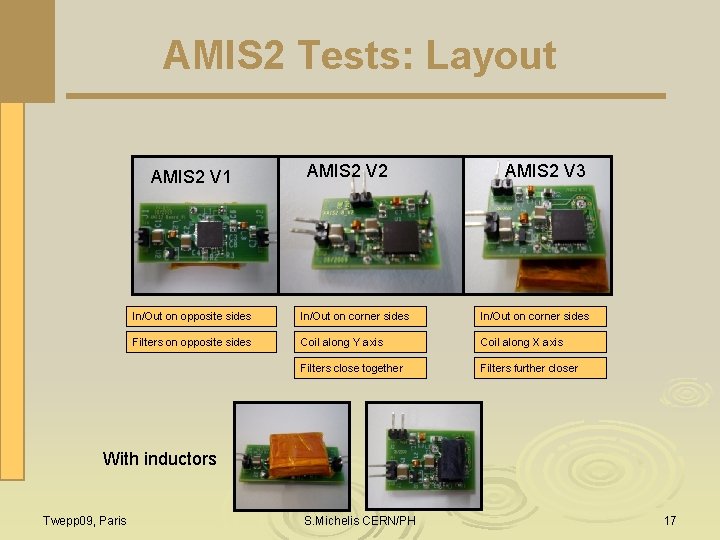

AMIS 2 Tests: Layout AMIS 2 V 1 AMIS 2 V 2 AMIS 2 V 3 In/Out on opposite sides In/Out on corner sides Filters on opposite sides Coil along Y axis Coil along X axis Filters close together Filters further closer With inductors Twepp 09, Paris S. Michelis CERN/PH 17

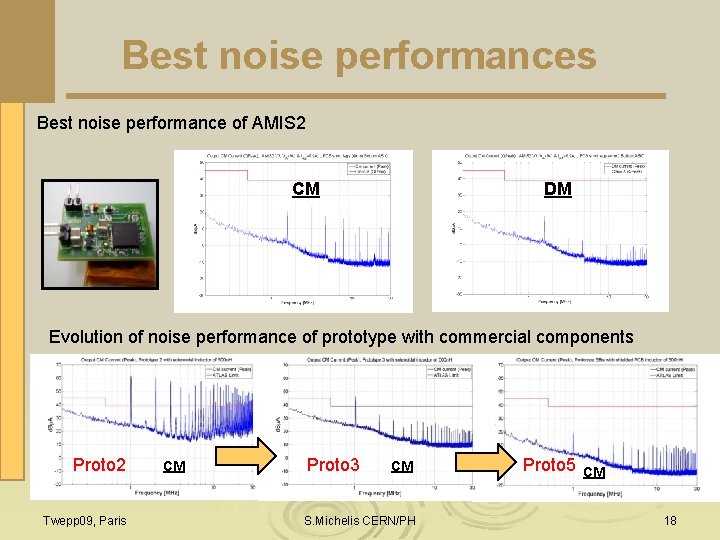

Best noise performances Best noise performance of AMIS 2 CM DM Evolution of noise performance of prototype with commercial components Proto 2 Twepp 09, Paris CM Proto 3 CM S. Michelis CERN/PH Proto 5 CM 18

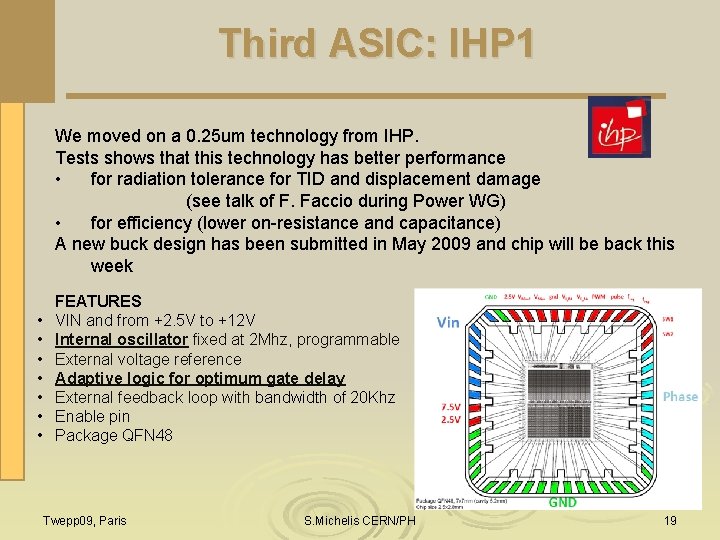

Third ASIC: IHP 1 We moved on a 0. 25 um technology from IHP. Tests shows that this technology has better performance • for radiation tolerance for TID and displacement damage (see talk of F. Faccio during Power WG) • for efficiency (lower on-resistance and capacitance) A new buck design has been submitted in May 2009 and chip will be back this week • • FEATURES VIN and from +2. 5 V to +12 V Internal oscillator fixed at 2 Mhz, programmable External voltage reference Adaptive logic for optimum gate delay External feedback loop with bandwidth of 20 Khz Enable pin Package QFN 48 Twepp 09, Paris S. Michelis CERN/PH 19

Conclusions Ø AMIS 2 has been tested and it shows good performances in term of l l l Ø Efficiency: up to 82% Noise: compliant with class A CISPR 11 standards and close to class B limit. Radiation: after annealing only 2% of efficiency is lost in the worst case (Vin=10 V and TID=300 Mrd) We have now moved to a 0. 25 um technology and first prototype has been delivered this week Twepp 09, Paris S. Michelis CERN/PH 20

- Slides: 20