Arquitetura e organizao de computadores Tratamento de execees

- Slides: 23

Arquitetura e organização de computadores. Tratamento de execeções Aula 13 Prof. Diovani Milhorim

Tipos de Exceções l Interrupção: salto assíncrono causado por eventos externos ao programa. Ex: timer, operações de E/S, etc. l Trap: salto síncrono causado por eventos determinados por programas. Ex: overflow, violação de memória protegida, etc

Tratadores de Exceção l Relembrando: l Etapas para Iniciar o Tratador: Salvamento de contexto ¡ Salvamento do endereço de retorno na pilha ¡ Endereço inicial do tratador de exceção é colocado no Apontador de Instrução (PC) ¡ Tratador é executado ¡ l Etapas para Finalizar o Tratador: Restaura contexto ¡ Restaura PC com endereço de retorno armazenado na pilha. ¡

Tratadores de Exceção: Ações do Hardware v v v Controlador do dispositivo ativa linha de interrupção do barramento. CPU reconhece ativando linha acknowledge do barramento Controlador responde ao reconhecimento da CPU colocando o nº do dispositivo nas linhas de dados do barramento (vetor de interrupção) CPU armazena o vetor de interrupção CPU salva o PC, onde o processo foi interrompido, e o registrador PSW (flags) na pilha. Endereço inicial do tratador de exceção é buscado em uma tabela que está no início da memória e o coloca no PC e o tratador é executado

Tratadores de Exceção: Ações do Software v v v v A rotina de tratamento de interrupção inicia armazenado os registradores ou na pilha ou em uma tabela do sistema Identificação do dispositivo causador da interrupção obtenção de informações de status (exemplo, erro de E/S) Controlador responde ao reconhecimento da CPU colocando o nº do dispositivo nas linhas de dados do barramento (vetor de interrupção) Trata-se a interrupção podendo gerar sinalização para indicar ao controlador que a interrupção foi tratada. Restaura os registradores salvos Restaura o PC (onde o processo foi interrompido) e o registrador PSW (flags) buscando da pilha. executa instrução RETORNE DA INTERRUPÇÃO

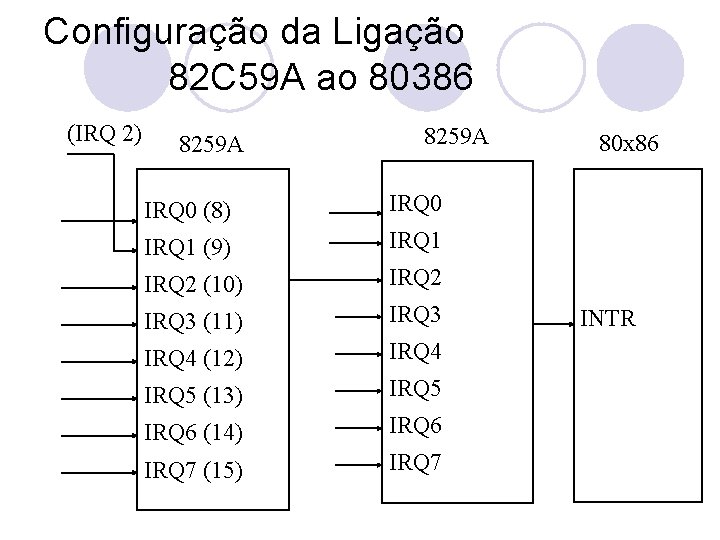

Múltiplas Interrupções l Como a arquitetura Intel 386/686 trata interrupções? ¡ 80 x 86 tem uma linha de interrupção ¡ Intel 82 C 59 A é um controlador de interrupção ¡ 82 C 59 A possui 8 linhas de interrupção

Seqüência de Eventos l 82 C 59 A aceita interrupção l 82 C 59 A determina a prioridade l 82 C 59 A sinaliza ao 80386 (INTR) l CPU reconhece l 82 C 59 A coloca o correto vetor de interrupção no barramento de dados l CPU processa a interrupção

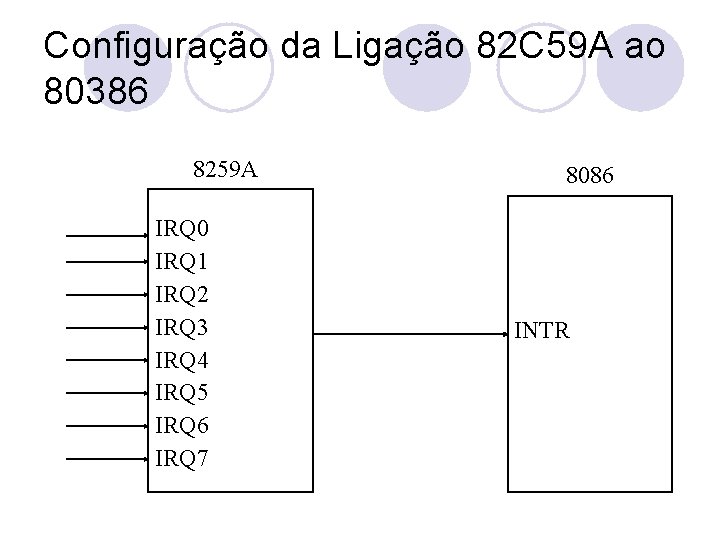

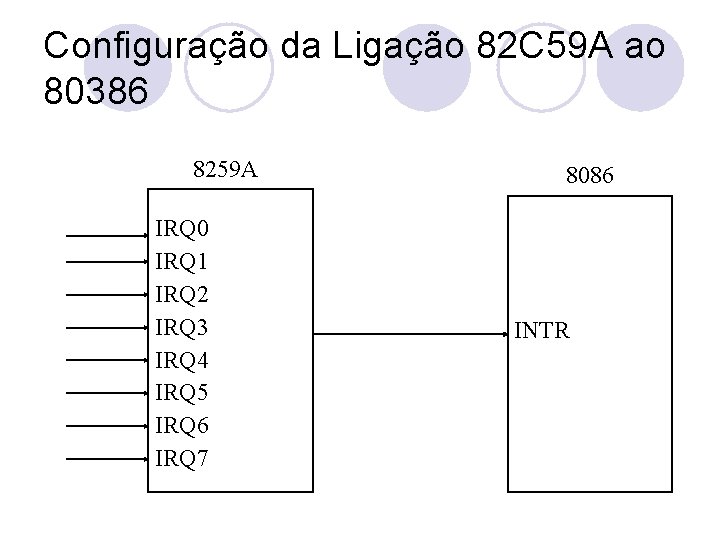

Configuração da Ligação 82 C 59 A ao 80386 8259 A IRQ 0 IRQ 1 IRQ 2 IRQ 3 IRQ 4 IRQ 5 IRQ 6 IRQ 7 8086 INTR

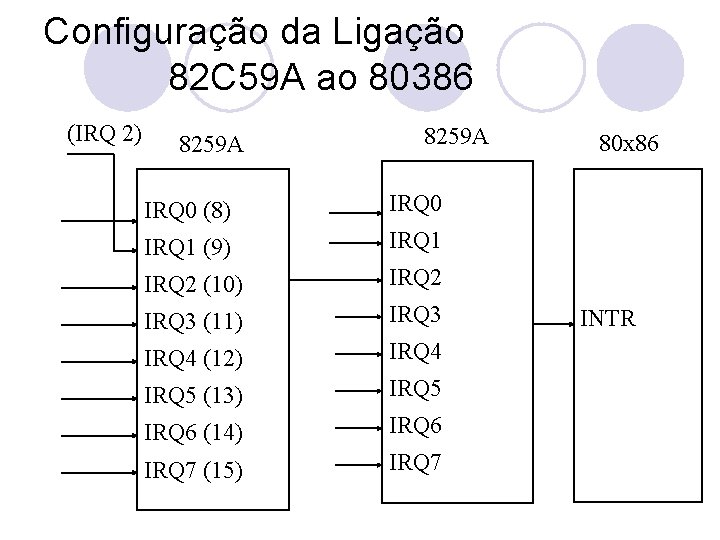

Configuração da Ligação 82 C 59 A ao 80386 (IRQ 2) 8259 A IRQ 0 (8) IRQ 0 IRQ 1 (9) IRQ 1 IRQ 2 (10) IRQ 2 IRQ 3 (11) IRQ 3 IRQ 4 (12) IRQ 4 IRQ 5 (13) IRQ 5 IRQ 6 (14) IRQ 6 IRQ 7 (15) IRQ 7 80 x 86 INTR

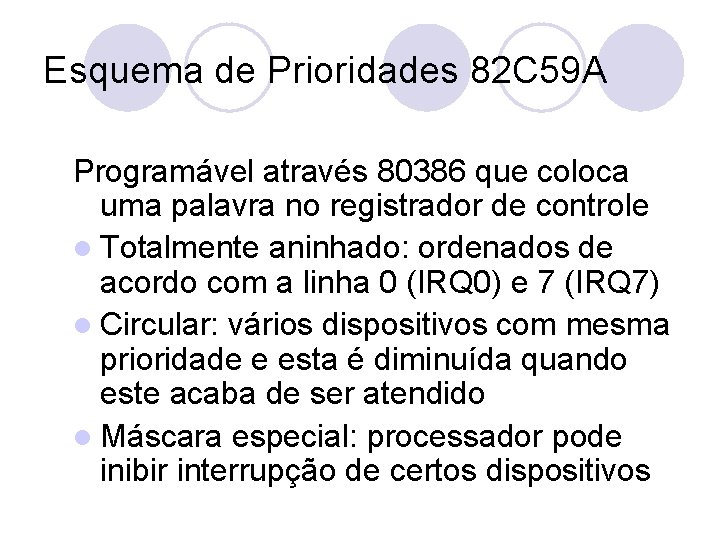

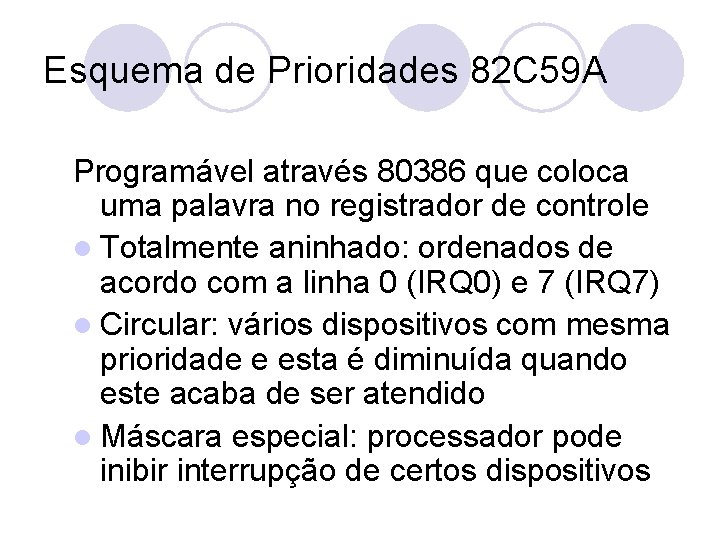

Esquema de Prioridades 82 C 59 A Programável através 80386 que coloca uma palavra no registrador de controle l Totalmente aninhado: ordenados de acordo com a linha 0 (IRQ 0) e 7 (IRQ 7) l Circular: vários dispositivos com mesma prioridade e esta é diminuída quando este acaba de ser atendido l Máscara especial: processador pode inibir interrupção de certos dispositivos

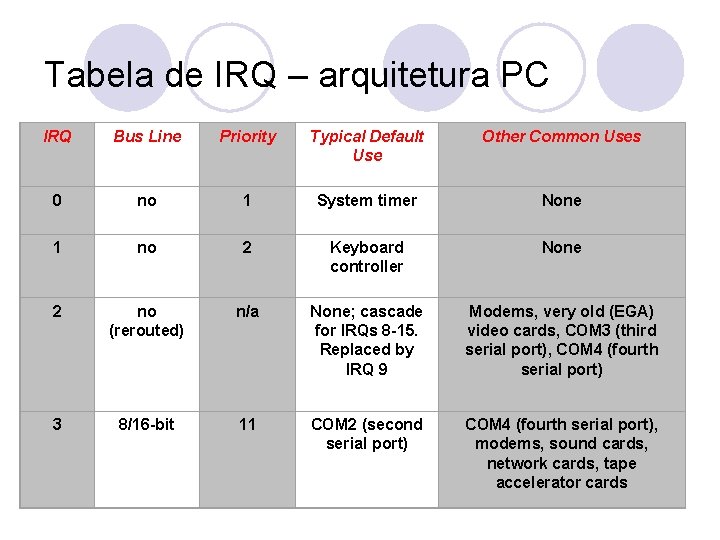

Prioridade de interrupção (PC) l. O PC processa interrupções de dispositivo de acordo com o nível de prioridade. A prioridade é dada pela linha de interrupção de entrada no controlador de interrupção, ou seja, pelo número da IRQ.

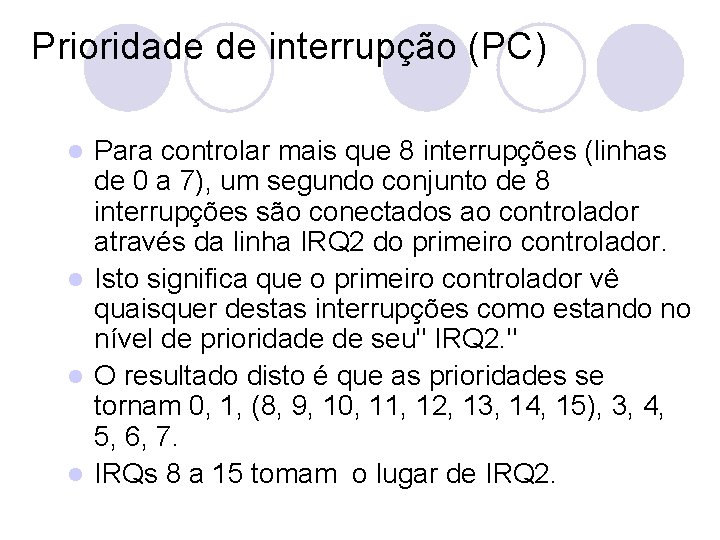

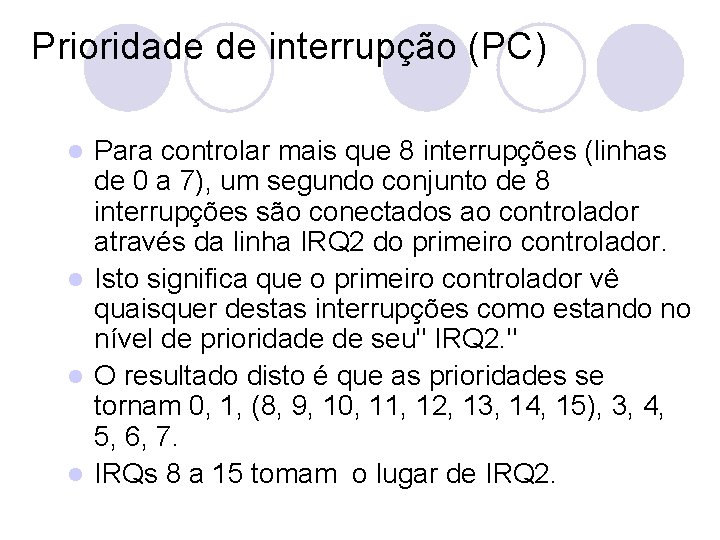

Prioridade de interrupção (PC) Para controlar mais que 8 interrupções (linhas de 0 a 7), um segundo conjunto de 8 interrupções são conectados ao controlador através da linha IRQ 2 do primeiro controlador. l Isto significa que o primeiro controlador vê quaisquer destas interrupções como estando no nível de prioridade de seu" IRQ 2. " l O resultado disto é que as prioridades se tornam 0, 1, (8, 9, 10, 11, 12, 13, 14, 15), 3, 4, 5, 6, 7. l IRQs 8 a 15 tomam o lugar de IRQ 2. l

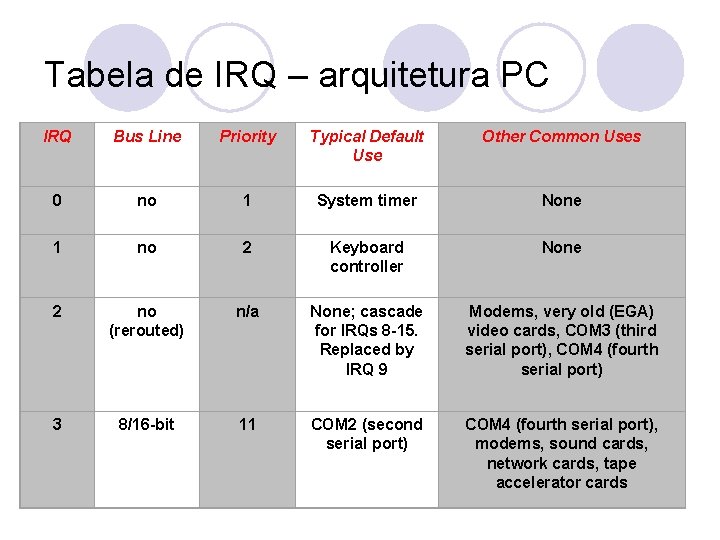

Tabela de IRQ – arquitetura PC IRQ Bus Line Priority Typical Default Use Other Common Uses 0 no 1 System timer None 1 no 2 Keyboard controller None 2 no (rerouted) n/a None; cascade for IRQs 8 -15. Replaced by IRQ 9 Modems, very old (EGA) video cards, COM 3 (third serial port), COM 4 (fourth serial port) 3 8/16 -bit 11 COM 2 (second serial port) COM 4 (fourth serial port), modems, sound cards, network cards, tape accelerator cards

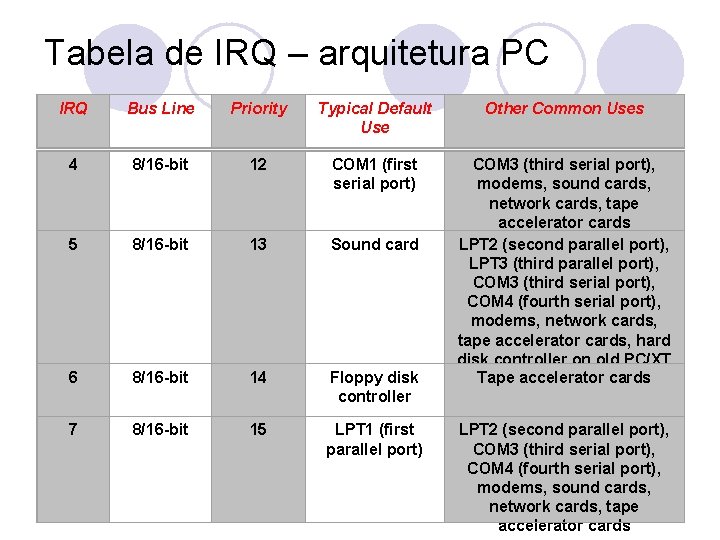

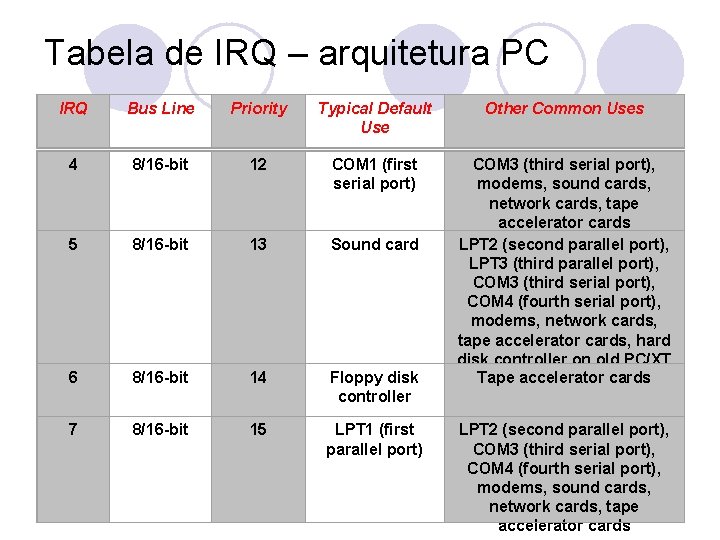

Tabela de IRQ – arquitetura PC IRQ Bus Line Priority Typical Default Use Other Common Uses 4 8/16 -bit 12 COM 1 (first serial port) 5 8/16 -bit 13 Sound card 6 8/16 -bit 14 Floppy disk controller COM 3 (third serial port), modems, sound cards, network cards, tape accelerator cards LPT 2 (second parallel port), LPT 3 (third parallel port), COM 3 (third serial port), COM 4 (fourth serial port), modems, network cards, tape accelerator cards, hard disk controller on old PC/XT Tape accelerator cards 7 8/16 -bit 15 LPT 1 (first parallel port) LPT 2 (second parallel port), COM 3 (third serial port), COM 4 (fourth serial port), modems, sound cards, network cards, tape accelerator cards

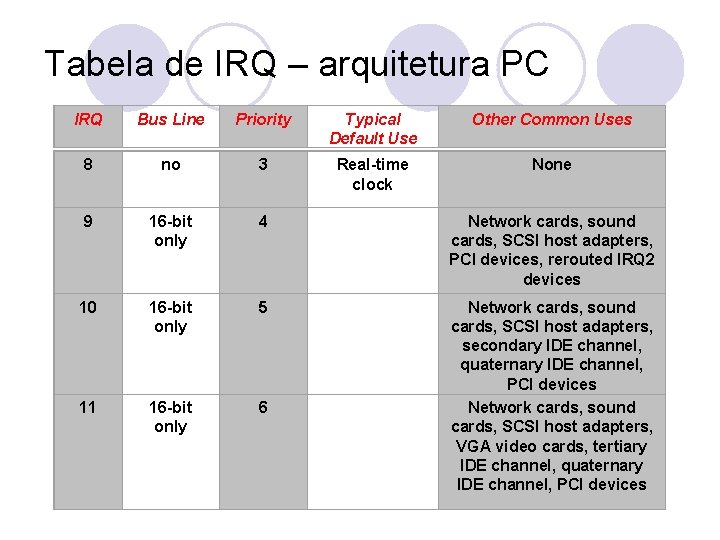

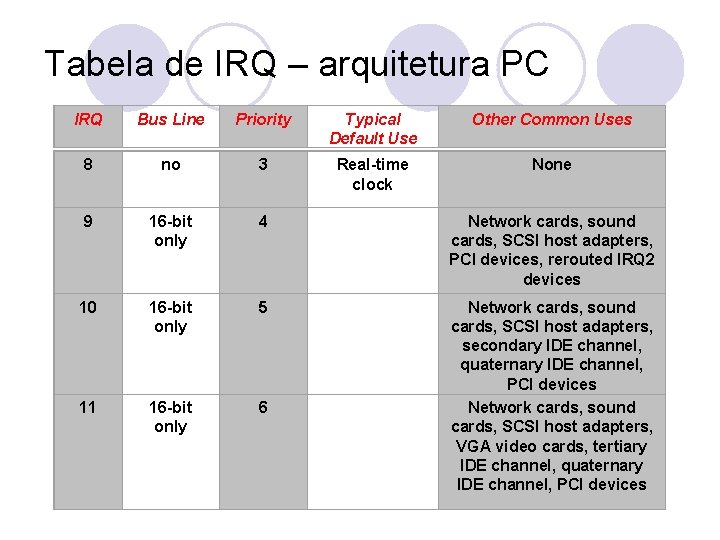

Tabela de IRQ – arquitetura PC IRQ Bus Line Priority Typical Default Use Other Common Uses 8 no 3 Real-time clock None 9 16 -bit only 4 Network cards, sound cards, SCSI host adapters, PCI devices, rerouted IRQ 2 devices 10 16 -bit only 5 11 16 -bit only 6 Network cards, sound cards, SCSI host adapters, secondary IDE channel, quaternary IDE channel, PCI devices Network cards, sound cards, SCSI host adapters, VGA video cards, tertiary IDE channel, quaternary IDE channel, PCI devices

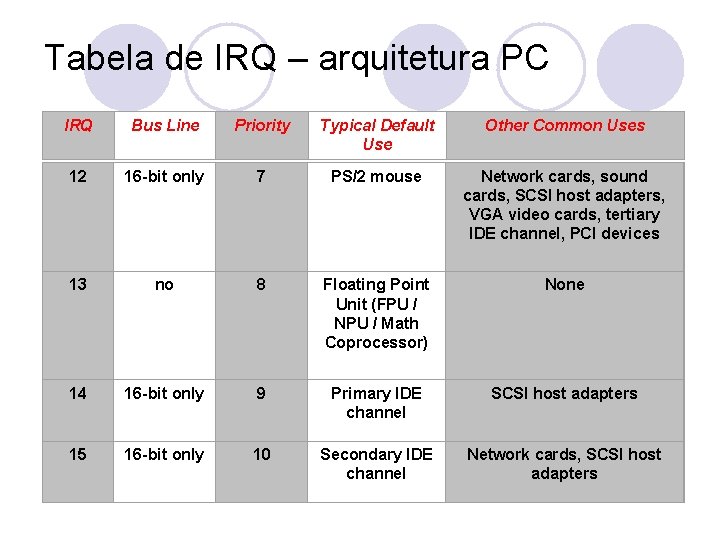

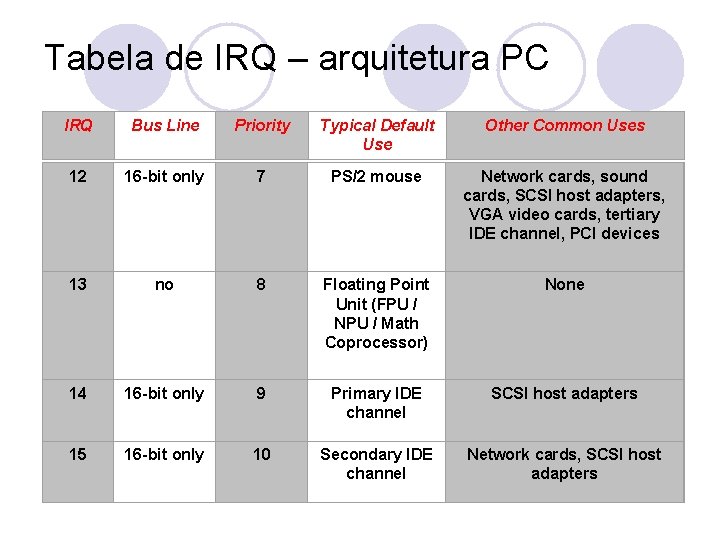

Tabela de IRQ – arquitetura PC IRQ Bus Line Priority Typical Default Use Other Common Uses 12 16 -bit only 7 PS/2 mouse Network cards, sound cards, SCSI host adapters, VGA video cards, tertiary IDE channel, PCI devices 13 no 8 Floating Point Unit (FPU / NPU / Math Coprocessor) None 14 16 -bit only 9 Primary IDE channel SCSI host adapters 15 16 -bit only 10 Secondary IDE channel Network cards, SCSI host adapters

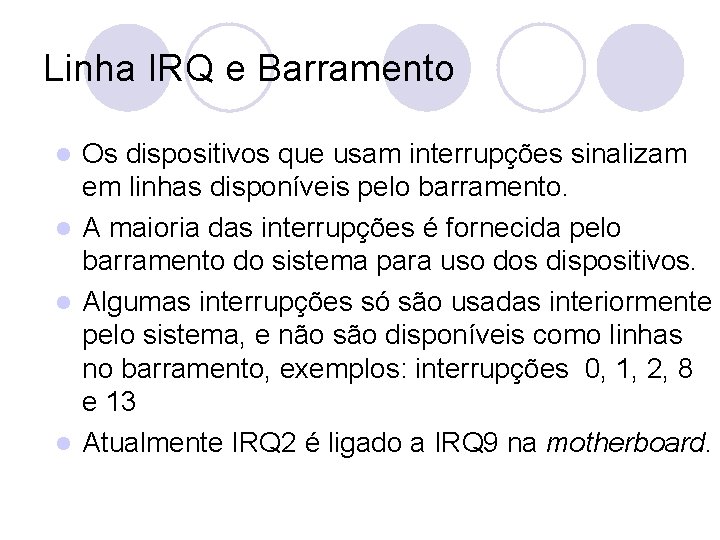

Linha IRQ e Barramento Os dispositivos que usam interrupções sinalizam em linhas disponíveis pelo barramento. l A maioria das interrupções é fornecida pelo barramento do sistema para uso dos dispositivos. l Algumas interrupções só são usadas interiormente pelo sistema, e não são disponíveis como linhas no barramento, exemplos: interrupções 0, 1, 2, 8 e 13 l Atualmente IRQ 2 é ligado a IRQ 9 na motherboard. l

Interrupções não-mascaráveis -Non. Maskable Interrupts (NMI) l Todas as interrupções normais que nos referimos através de números são chamadas de interrupções mascaráveis. l O processador pode mascarar, ou temporariamente ignorar, qualquer interrupção se precisar terminar qualquer outra coisa que está fazendo.

Interrupções não-mascaráveis -Non. Maskable Interrupts (NMI) l. O PC tem uma interrupção não-mascaráveis (NMI) que podem ser usadas em condições sérias que exigem a atenção imediata do processador. l O NMI não pode ser ignorado pelo sistema a menos que especificamente esteja desligado. l Quando um sinal de NMI é recebido, o processador pára tudo que estava fazendo imediatamente e atende a interrupção.

Interrupções não-mascaráveis -Non. Maskable Interrupts (NMI) l. O sinal de NMI normalmente é só usado para situações de problema críticas, como erros de hardware sérios. l O uso mais comum de NMI é sinalizar um erro de paridade do subsistema de memória. Este erro deve ser negociado imediatamente para prevenir possível corrupção de dados.

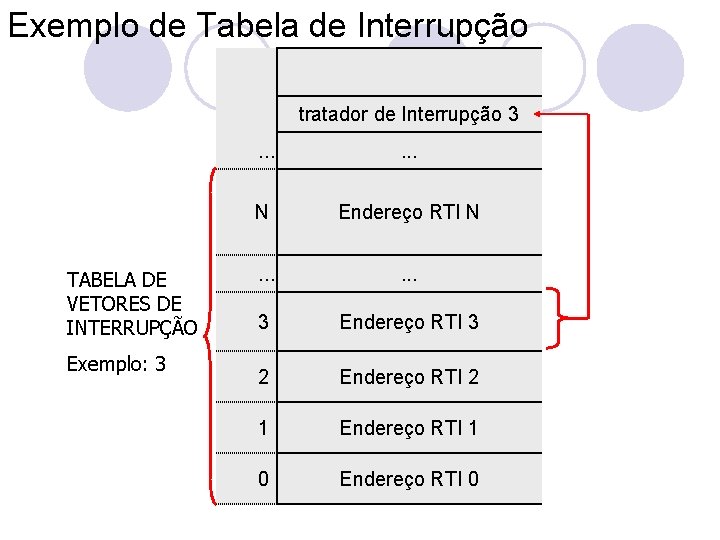

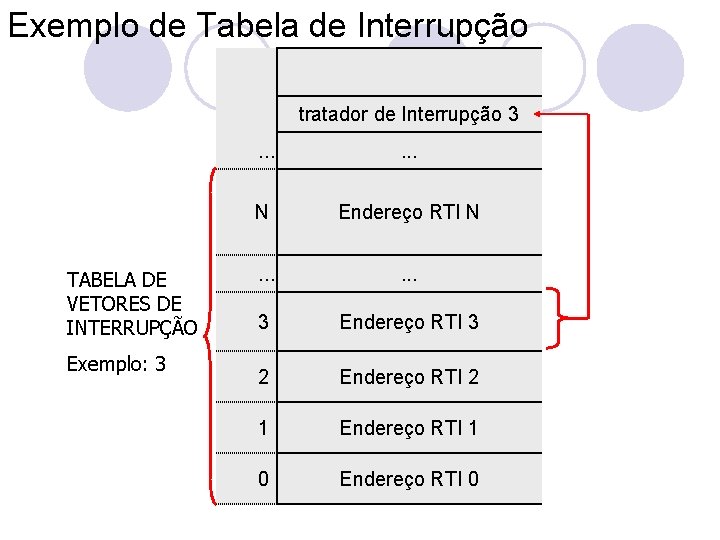

Exemplo de Tabela de Interrupção tratador de Interrupção 3 TABELA DE VETORES DE INTERRUPÇÃO Exemplo: 3 . . . N Endereço RTI N . . . 3 Endereço RTI 3 2 Endereço RTI 2 1 Endereço RTI 1 0 Endereço RTI 0

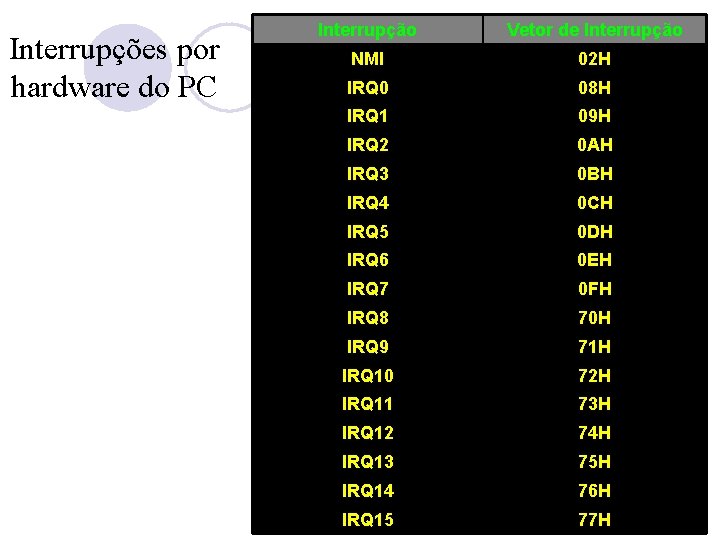

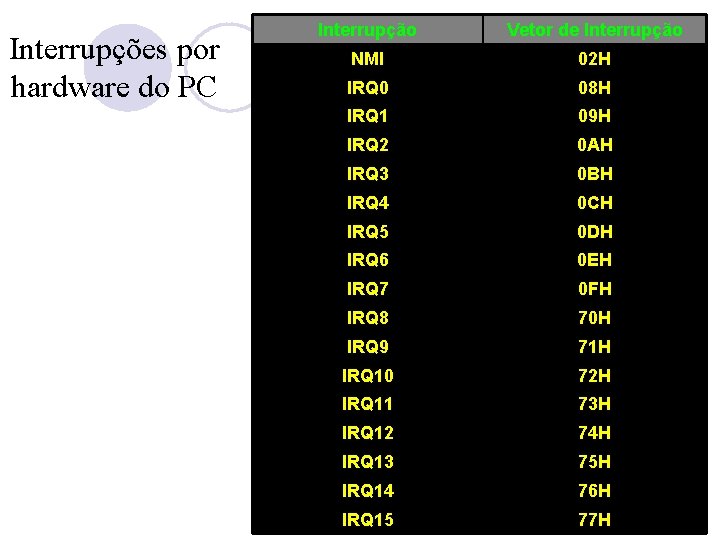

Interrupções por hardware do PC Interrupção Vetor de Interrupção NMI 02 H IRQ 0 08 H IRQ 1 09 H IRQ 2 0 AH IRQ 3 0 BH IRQ 4 0 CH IRQ 5 0 DH IRQ 6 0 EH IRQ 7 0 FH IRQ 8 70 H IRQ 9 71 H IRQ 10 72 H IRQ 11 73 H IRQ 12 74 H IRQ 13 75 H IRQ 14 76 H IRQ 15 77 H

Exercícios Diferencie interrupção e trap. 2) Desenhe o ciclo de instrução desconsiderando a existência de interrupções. 3) Desenhe o ciclo de instrução considerando a existência de interrupções. 1)