Arquitectura de Procesadores VLIW y DSP ILP Instruction

- Slides: 28

Arquitectura de Procesadores VLIW y DSP

ILP (Instruction Level Parallelism) • Familia de técnicas de diseño tanto del procesador como del compilador que incrementan la velocidad de ejecución permitiendo que operaciones individuales (instrucciones) tales como loads, stores, operaciones enteras y de CF, se ejecuten en paralelo. • A diferencia de los multiprocesadores tradicionales o máquinas masivamente paralelas, estas técnicas son transparentes al usuario. • Ejemplo de técnicas ILP aplicadas a procesadores: superescalares y VLIW • Ejemplo de técnicas ILP aplicadas al compilador: software pipelining y trace scheduling Unidad 5 VLIW y DSP 2

Surgimiento de VLIW • 1980’s: aparecen en el mercado como una natural evolución de los procesadores microprogramados horizontalmente. debido a los mismos cambios en la tecnología que motivaron la aparición de RISC: la desaparición del gap existente entre RAM y ROM. • El mercado de procesadores especializados, que tenían cableados importantes algoritmos como FFT, reemplazan la ROM de control con RAM, dándoles a los programadores acceso al ILP. Unidad 5 VLIW y DSP 3

Microprogramación • Horizontal: cada microinstrucción contiene n bits, cada uno de los cuales controla directamente cada pieza de hardware, evitando otros niveles de decodificación. Las microinstrucciones horizontales son más largas. • Vertical: cada microinstrucción tiene un pequeño número de campos, muy codificados, de forma que requieren más decodificación antes de aplicarse a los componentes individuales. Unidad 5 VLIW y DSP 4

Surgimiento de VLIW • Tanto en RISC como en VLIW, el tema crucial era el compilador. En el caso de VLIW, el compilador debía generar código “horizontal”: es decir debía especificar el paralelismo directamente. • Técnicas de generación de código se extendieron a partir de las existentes para microcódigo, y se desarrollaron nuevas para incorporar a los compiladores para que éstos extraigan mucho paralelismo. • Se construyeron pocas VLIW CPU’s de propósito general: Culler, Multiflow y Cydrome. A pesar de explotar mucho ILP, no tuvieron éxito comercial. Unidad 5 VLIW y DSP 5

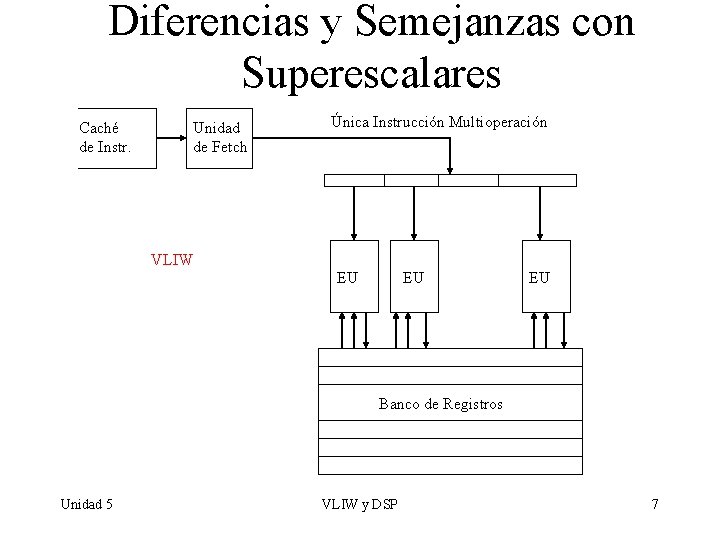

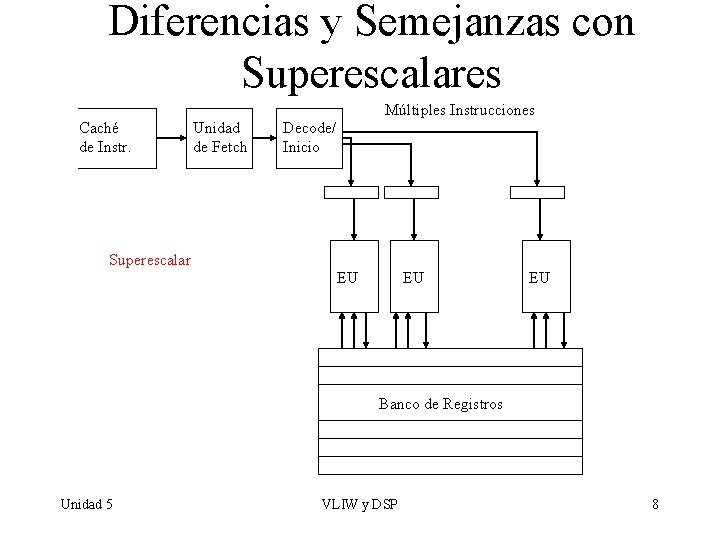

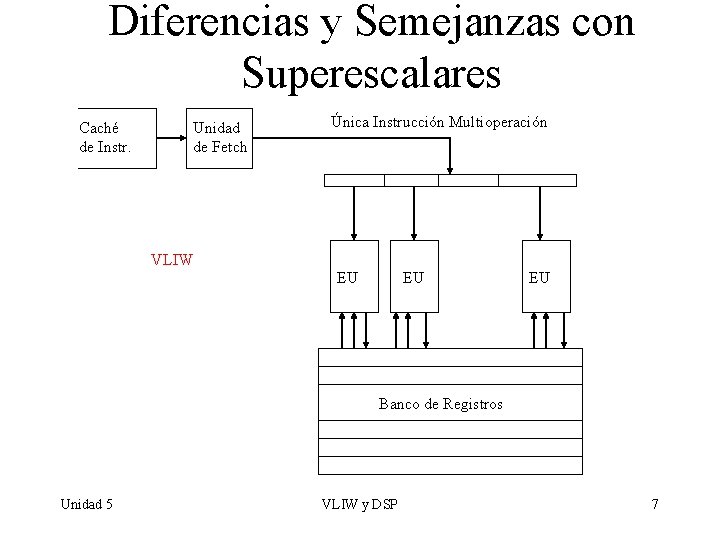

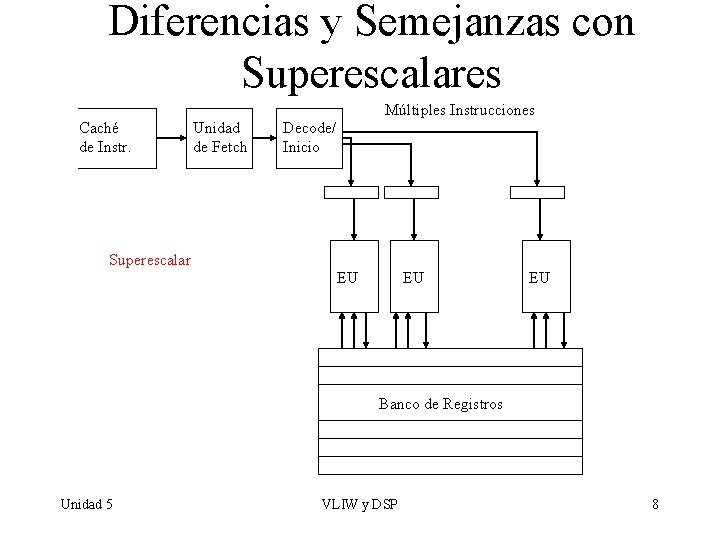

Diferencias y Semejanzas con Superescalares • Semejanzas: misma estructura básica compuesta por múltiples U. F. operando en paralelo, y un único Banco de Registros (o dos para FX y FP) • Diferencias: tipo de instrucciones y scheduling de instrucciones Unidad 5 VLIW y DSP 6

Diferencias y Semejanzas con Superescalares Caché de Instr. Unidad de Fetch Única Instrucción Multioperación VLIW EU EU EU Banco de Registros Unidad 5 VLIW y DSP 7

Diferencias y Semejanzas con Superescalares Múltiples Instrucciones Caché de Instr. Unidad de Fetch Decode/ Inicio Superescalar EU EU EU Banco de Registros Unidad 5 VLIW y DSP 8

Tipos de Instrucciones • Arquitecturas VLIW están controladas por instrucciones largas que contienen un campo de control por cada una de las UF disponibles en la arquitectura. • La longitud de la instrucción depende de dos factores: número de UF disponibles y número de bits necesarios para controlar cada UF. • El número de UF suele ser grande : de 5 a 30. El número de bits de control para cada UF suele ser de 16 o 32 ====> palabras de instrucción de 100 -1 kbit • Ejemplos: Trace 7/200 ejecuta 7 operaciones por ciclo y utiliza una palabra de instrucción de 256 bits. Unidad 5 VLIW y DSP 9

Scheduling de Instrucciones • Superescalares utilizan sheduling dinámico • VLIW utilizan scheduling estático: es responsabilidad del compilador. • Ventaja: – reduce la complejidad del hardware (no hay detección de riesgos, ni renombre, ni despacho en desorden, ni retiro ordenado, y además la etapa de decodificación es más sencilla) y permite incrementar la velocidad del reloj o aumentar el paralelismo o ambas a la vez. Unidad 5 VLIW y DSP 10

Scheduling de Instrucciones • Desventaja: – mayor complejidad en el compilador al que le tocan las tareas de detectar y eliminar los riesgos por dependencias de datos, control y recursos. – Pero además, el compilador, para poder realizar su tarea, necesita conocer todas las características del hardware, tales como: número, tipo, latencia, intervalo de iniciación de las UF, slot delay del load, muchos de los cuales dependen no sólo de la arquitectura sino de la tecnología de implementación. ===>>>un mismo compilador NO puede utilizarse para distintos modelos de la misma familia. !!!!! Unidad 5 VLIW y DSP 11

Scheduling de Instrucciones • Mas problemas: – Cache Misses : Debido a que el compilador no conoce cuando se producirán, debe considerar el caso peor de retardo al generan su scheduling. (loads especulativos. . . ) – El formato de la VL Instruction, que es fijo, no siempre contiene información útil en todos los campos ===>>pérdida de espacio y ancho de banda con memoria. – Debido a la alta complejidad de la tarea, los VLIW NO pueden ser programados en lenguaje ensamblador (!) Unidad 5 VLIW y DSP 12

DSP: Digital Signal Processing • Procesadores para procesado digital de señales: se utilizan para teléfonos celulares, modems, discos, contestadoras, etc. • Al bajar el precio de los microprocesadores, éstos pueden ser incorporados a productos del mercado que demandan bajo costo, rapidez, pequeñez y poco consumo de energía===> se desarrollan chips que implementan el procesado de señales. • El mercado de DSP está creciendo. (Forward Concepts reporta en 1997 un movimiento de 3 billones de dolares) Unidad 5 VLIW y DSP 19

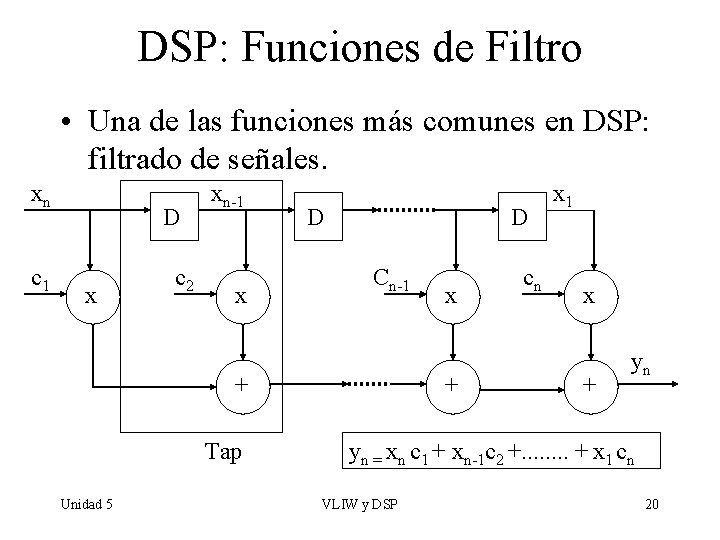

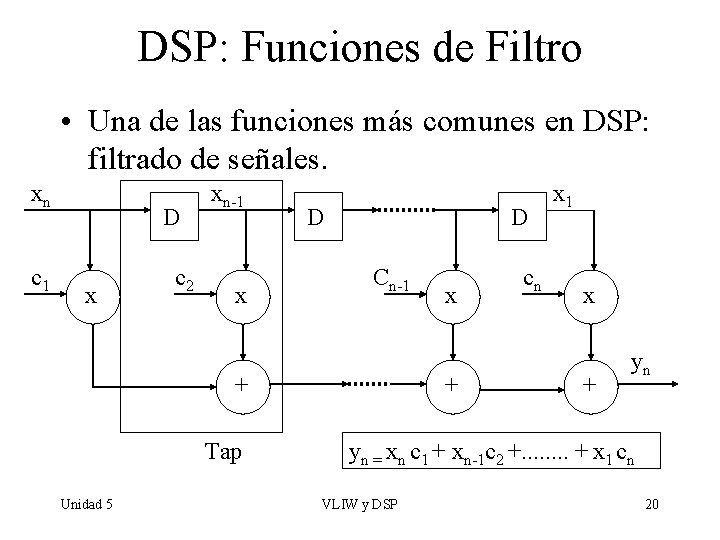

DSP: Funciones de Filtro • Una de las funciones más comunes en DSP: filtrado de señales. xn c 1 D x c 2 xn-1 x D D Cn-1 + Tap Unidad 5 x + cn x 1 x + yn yn = xn c 1 + xn-1 c 2 +. . . . + x 1 cn VLIW y DSP 20

DSP: instrucción MAC • El número de TAP’s, y los valores de los coeficientes definen las características del filtro. • La operación realizada (yk = yk-1 + xk cj) se llama MAC: multiply-accumulate. • Para soportar la MAC eficientemente, DSP tienen hardware especializado de multiplicación (multiplican en un ciclo) y registros acumuladores especiales (más grandes que los registros comunes) • Casi todos los procesadores DSP tienen una instrucción de MAC en su conjunto de instrucciones. • Esta es una diferencia con los GPP. Unidad 5 VLIW y DSP 21

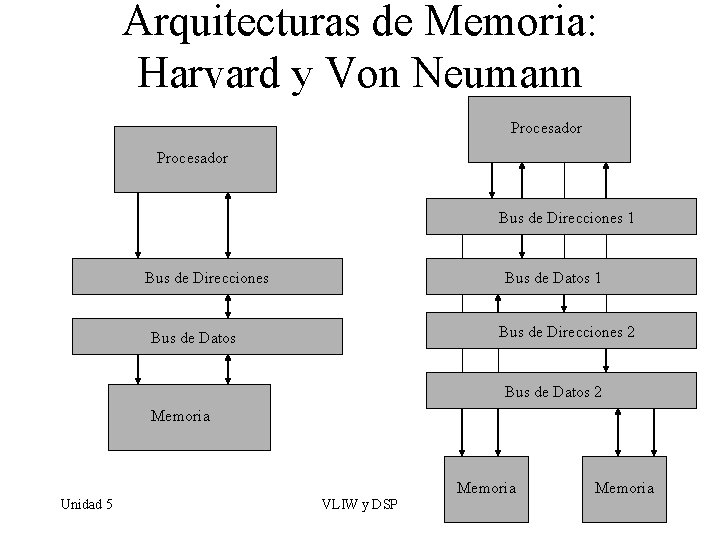

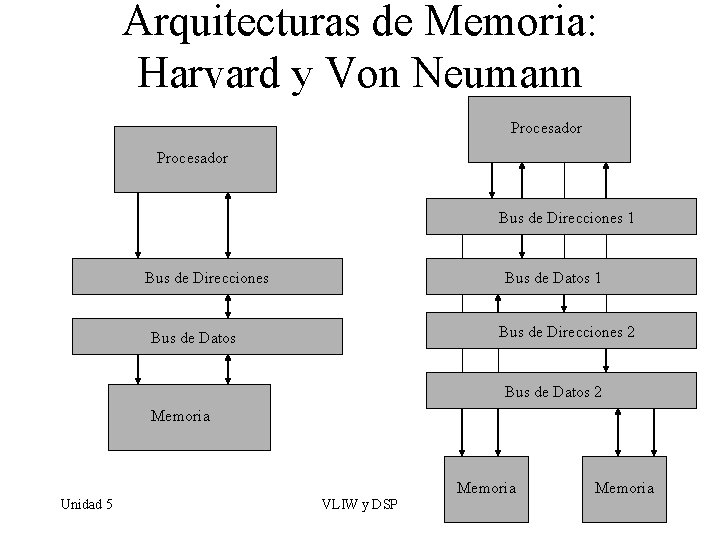

DSP: instrucción MAC • DSP requieren mucho ancho de banda con memoria: por ejemplo, para ejecutar un MAC por ciclo, se requieren 4 accesos a memoria por ciclo: – – fetch de la instrucción MAC leer el elemento x correspondiente leer el coeficiente escribir el resultado • DSP utilizan la arquitectura de memoria Harvard. Un típico GGP utiliza la arquitectura Von Neumann. Unidad 5 VLIW y DSP 22

Arquitecturas de Memoria: Harvard y Von Neumann Procesador Bus de Direcciones 1 Bus de Direcciones Bus de Datos 1 Bus de Direcciones 2 Bus de Datos 2 Memoria Unidad 5 VLIW y DSP Memoria 23

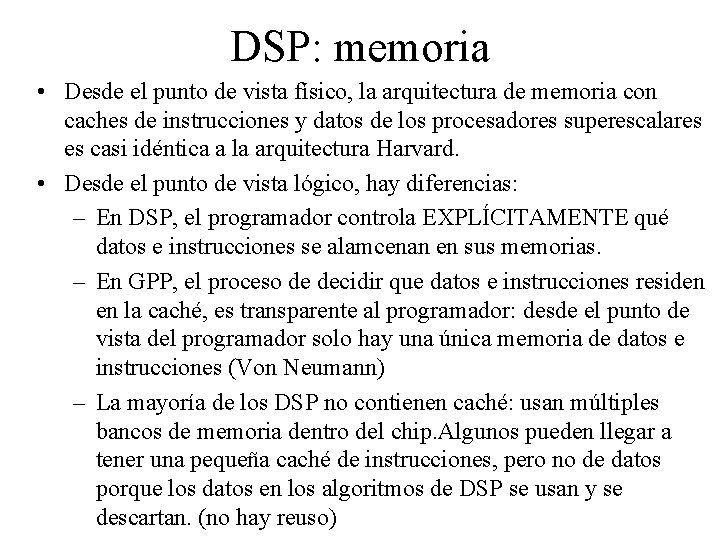

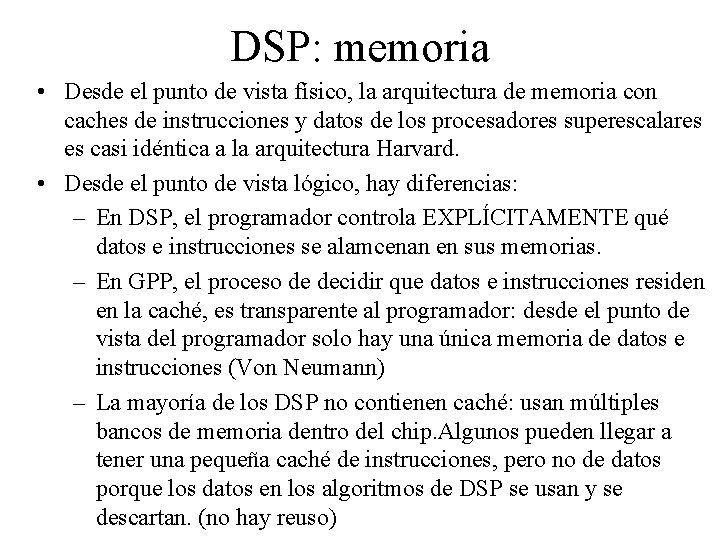

DSP: memoria • Desde el punto de vista físico, la arquitectura de memoria con caches de instrucciones y datos de los procesadores superescalares es casi idéntica a la arquitectura Harvard. • Desde el punto de vista lógico, hay diferencias: – En DSP, el programador controla EXPLÍCITAMENTE qué datos e instrucciones se alamcenan en sus memorias. – En GPP, el proceso de decidir que datos e instrucciones residen en la caché, es transparente al programador: desde el punto de vista del programador solo hay una única memoria de datos e instrucciones (Von Neumann) – La mayoría de los DSP no contienen caché: usan múltiples bancos de memoria dentro del chip. Algunos pueden llegar a tener una pequeña caché de instrucciones, pero no de datos porque los datos en los algoritmos de DSP se usan y se descartan. (no hay reuso)

DSP y GPP: diferencias • DSP: Zero overhead looping: hardware especializado para la ejecución de loops (instrucción loop) • GPP: predicción de saltos • DSP: aritmética entera, porque es menos costosa. • DSP: modos de direccionamiento especializados: modulo addressing y bit reversed addressing • DSP: aplicaciones de tiempo real. Esto requiere del programador el conocimiento exacto de cuanto tiempo de proceso requerirá cada muestra (o al menos, el peor caso). Unidad 5 VLIW y DSP 25

DSP y GPP: diferencias • GPP’s de alto rendimiento : es difícil predecir el tiempo de ejecución de un trozo de código: POCA PREDICTIBILIDAD, porque la ejecución especulativa hace que un mismo trozo de código consuma distinta cantidad de ciclos según la historia previa de ejecución • DSP, no tienen ejecución especulativa y, en caso de que hubiera caché de instrucciones, es el programador el que sabe que instrucciones están alli====> MUCHA PREDICTIBILIDAD. Unidad 5 VLIW y DSP 26

DSP y GPP: Instrucciones • DSP ISA’s diseñados para conseguir muchas instrucciones por ciclo y poco consumo de memoria ==> muchas operaciones en una única instrucción, pero muy especializadas ==> conjuntos de instrucciones irregulares y complicados. • Motorola DSP 56300: dos espacios de memoria X e Y MAC X 0, Y 0, A X: (R 0)+, X 0 Y: (R 4)+N 4, Y 0 – Multiplica X 0 por Y 0 – Suma el resultado a A (aumulador) – Carga registro X 0 con la posición apuntada por R 0 de memoria X – Carga registro Y 0 con la posición apuntada por R 4 de memoria Y – Postincrementa R 0 por 1 – Postincrementa R 4 por el contenido de N 4

DSP y GPP: Programación • GPP se programan en alto nivel. • DSP se programan en ensamblador porque la complejidad de la arquitectura (múltiples espacios de memoria, juego irregular de instrucciones y hardware especializado) hacen difícil escribir compiladores eficientes. • Optimización de código es esencial en DSP: mucha computación a bajo costo. Los vendedores de DSP proveen herramientas de optimización y simulación. Se mejora “a mano”el resultado del compilador.

Tipos de DSP • Bajo Costo, Bajo Rendimiento: – – TI TMS 320 C 2 xx, Motorola DSP 560 xx (Familias) Operan a razón de 20 -50 MIPS Nativos Poco consumo de energía, poca memoria. Uso: productos que requieren poco rendimiento pero tienen mucho consumo, por ejemplo disk drives, contestadoras • DSP medios: – – Mayor frecuencia de reloj : 100 -120 MIPS TI TMS 320 C 54 xx, Lucent Technologies DSP 16 xx (Familias) Hardware más sofisticado: pipeline, cachés de instrucciones Uso: productos que requieren alto rendimiento computacional y poco consumo, por ejemplo modems de alta velocidad.

Tipos de DSP • Alto Rendimiento: Procesamiento ultrarrápido, Diversidad de Arquitecturas. – Convencionales Mejorados – Inicio de Múltiples Instrucciones por Ciclo • Convencionales Mejorados: – Se agregan UF (Multiplicadores, Sumadores), soporte dentro del juego de instrucciones para el hardware adicional. – Ejemplo: Lucent Technologies DSP 16210 100 MIPS • Inicio Múltiple: – En GPP, el inicio múltiple se consigue con técnicas superescalares – En DSP, con VLIW

VLIW DSP’s • Texas Instruments TMS 320 C 6000 (Fabio) – 256 bits por instrucción, divididas en 8 palabras de 32 bits controlan 8 UF’s independientes – clock: 200 Mhz – MIPS: 1600 – Las subinstrucciones son más simples que las de los DSP convencionales – No siempre están ocupadas todas las UF – Consumen más energía y los programas ocupan más memoria que los DSP’s convencionales – Compiladores agrupan las instrucciones en palabras. Si no puede agrupar el conjunto completo de subinstrucciones, inserta NOP’s. – Mecanismo de compresión hardware y software para solucionar el problema del tamaño del código.

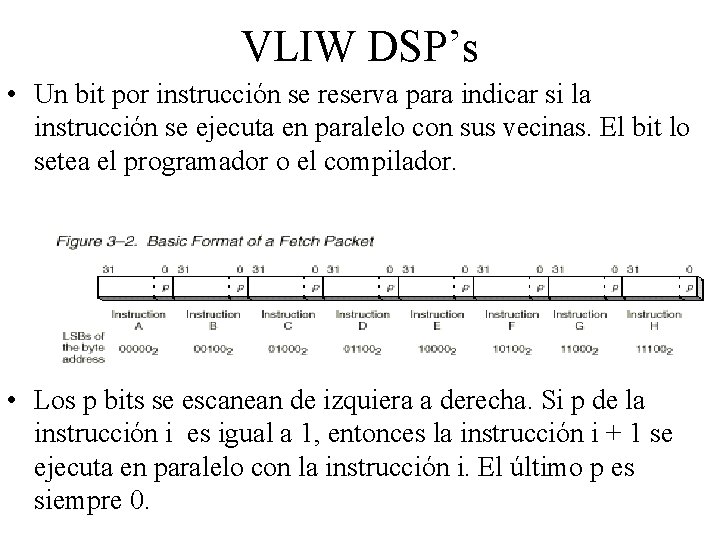

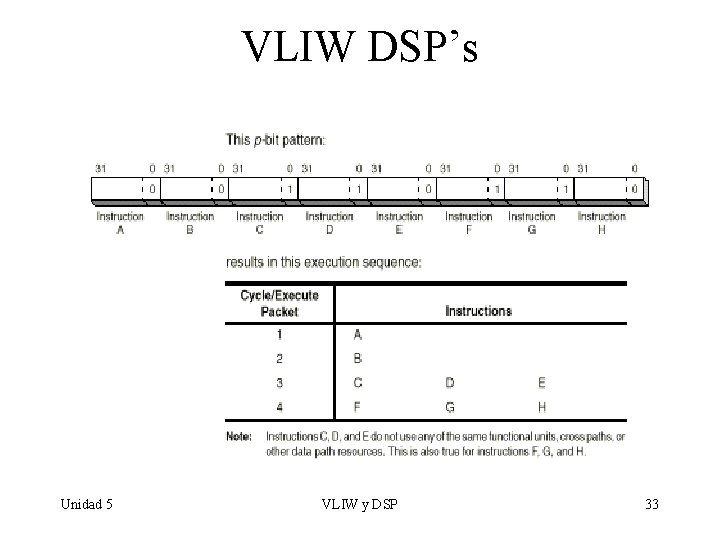

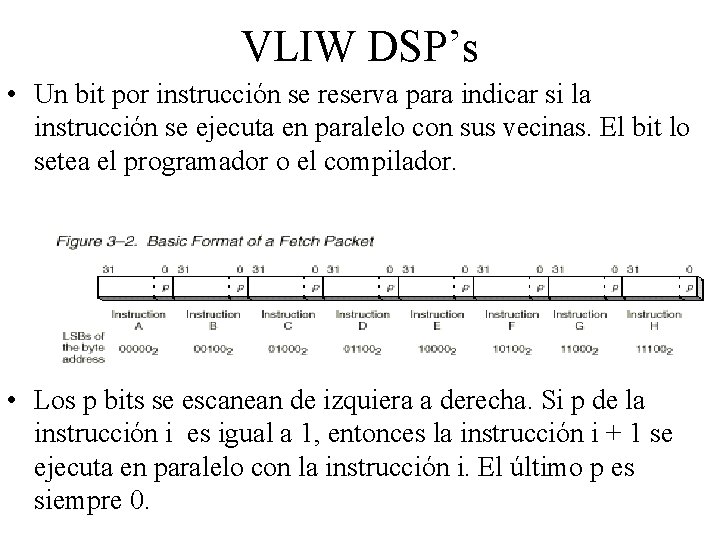

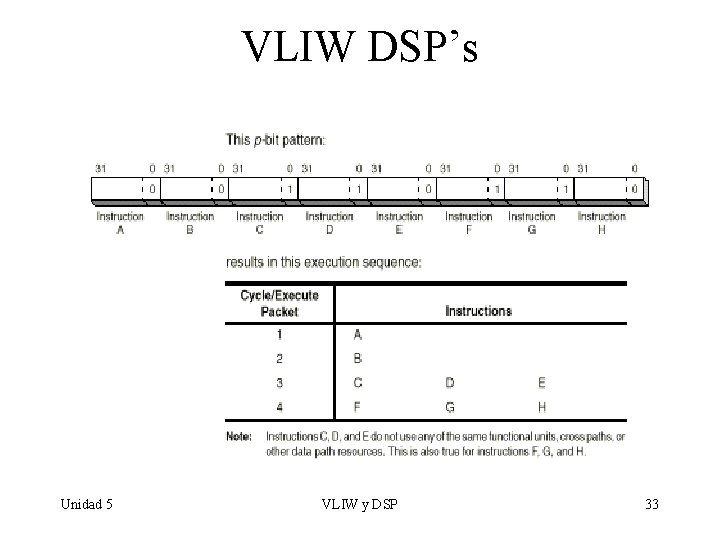

VLIW DSP’s • Un bit por instrucción se reserva para indicar si la instrucción se ejecuta en paralelo con sus vecinas. El bit lo setea el programador o el compilador. • Los p bits se escanean de izquiera a derecha. Si p de la instrucción i es igual a 1, entonces la instrucción i + 1 se ejecuta en paralelo con la instrucción i. El último p es siempre 0.

VLIW DSP’s Unidad 5 VLIW y DSP 33

Ejemplo de código MPY. M 1 A 0, A 1, A 2 || ADD. L 1 A 4, A 5, A 2 || ADD. L 1 X A 7, B 1, A 6 • El lenguaje ensamblador especifica, además de los registros, modos de direccionamiento y operación a ser realizada, la Unidad Funcional, los Caminos de Datos utilizados, y el paralelismo entre las instrucciones. Unidad 5 VLIW y DSP 34