ARM PROCESSORS By Seminartopics info CONTENTS ARM History

ARM PROCESSORS By, Seminartopics. info

CONTENTS § § § ARM History Applications ARM Members Architecture Arm CONTROLLERS INSTRUCTIONS

Brief history of ARM Ø Founded in 1990. Ø ARM -Advanced Risc Machines Ø 32 bit RISC processor from ARM Holdings. Ø ARM Holding is a joint venture between Acron computers, Apple computers and VLSI Technology.

ARM PARTNER Ø ARM Holdings - supplies ARM processor Core Ø doesn’t manufacture ARM processor chips. Ø designs the ARM processor core Ø licences its ARM IP to their networked partners.

ARM POWERED PRODUCTS

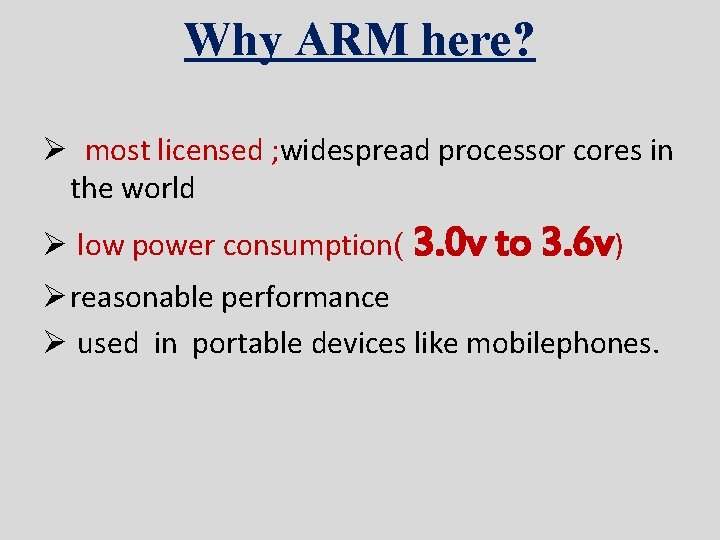

Why ARM here? Ø most licensed ; widespread processor cores in the world Ø low power consumption( 3. 0 v to 3. 6 v) Ø reasonable performance Ø used in portable devices like mobilephones.

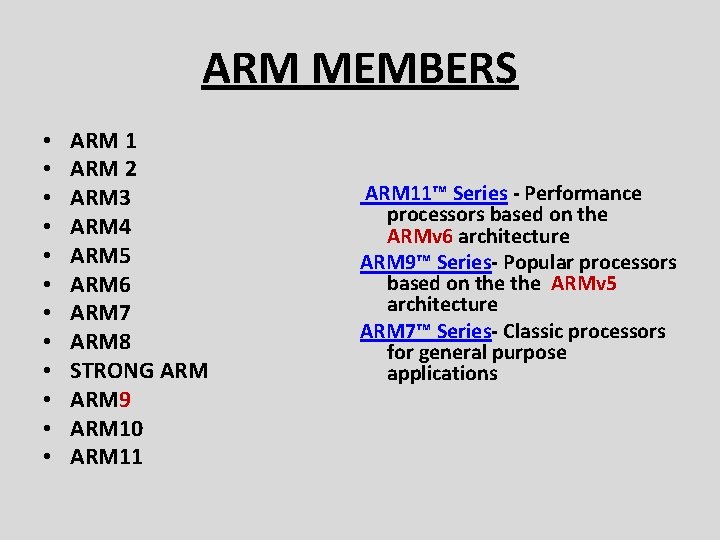

ARM MEMBERS • • • ARM 1 ARM 2 ARM 3 ARM 4 ARM 5 ARM 6 ARM 7 ARM 8 STRONG ARM 9 ARM 10 ARM 11™ Series - Performance processors based on the ARMv 6 architecture ARM 9™ Series- Popular processors based on the ARMv 5 architecture ARM 7™ Series- Classic processors for general purpose applications

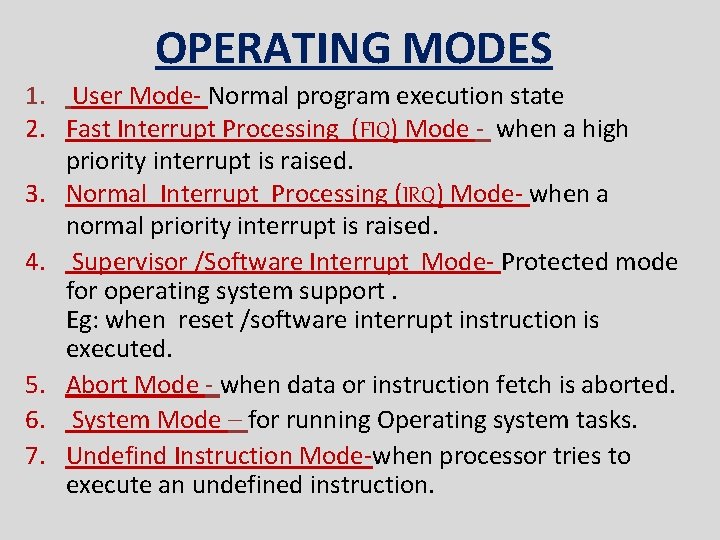

OPERATING MODES 1. User Mode- Normal program execution state 2. Fast Interrupt Processing (FIQ) Mode - when a high priority interrupt is raised. 3. Normal Interrupt Processing (IRQ) Mode- when a normal priority interrupt is raised. 4. Supervisor /Software Interrupt Mode- Protected mode for operating system support. Eg: when reset /software interrupt instruction is executed. 5. Abort Mode - when data or instruction fetch is aborted. 6. System Mode – for running Operating system tasks. 7. Undefind Instruction Mode-when processor tries to execute an undefined instruction.

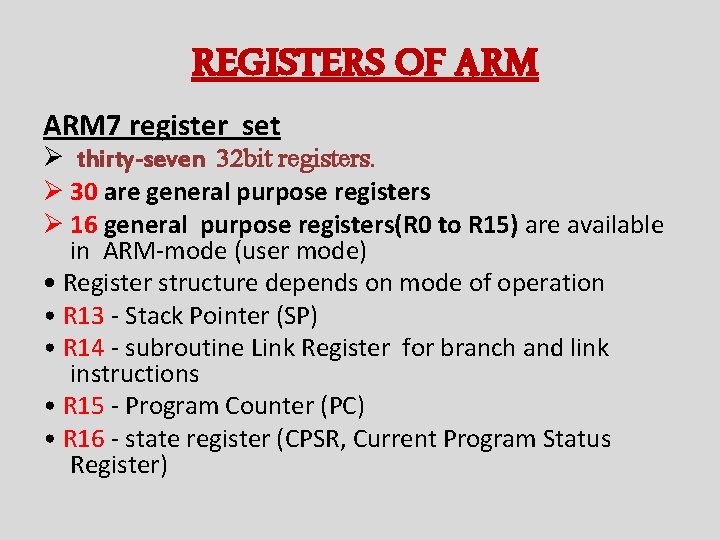

REGISTERS OF ARM 7 register set Ø thirty-seven 32 bit registers. Ø 30 are general purpose registers Ø 16 general purpose registers(R 0 to R 15) are available in ARM-mode (user mode) • Register structure depends on mode of operation • R 13 - Stack Pointer (SP) • R 14 - subroutine Link Register for branch and link instructions • R 15 - Program Counter (PC) • R 16 - state register (CPSR, Current Program Status Register)

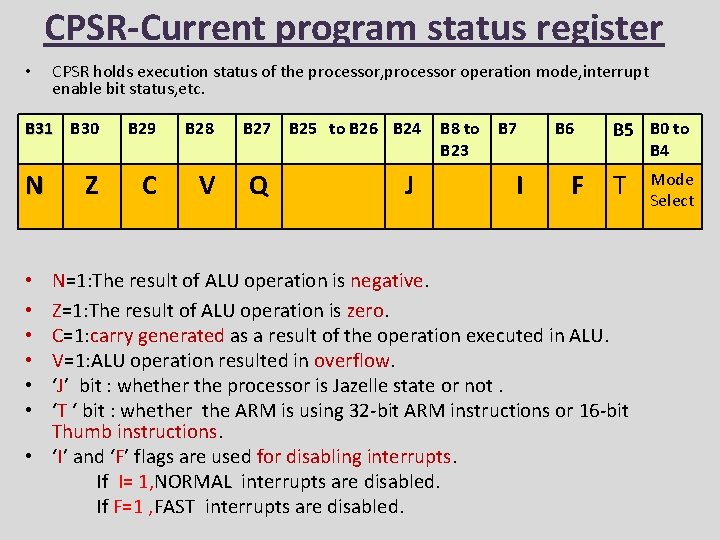

CPSR-Current program status register • CPSR holds execution status of the processor, processor operation mode, interrupt enable bit status, etc. B 31 B 30 N Z B 29 B 28 C V B 27 B 25 to B 26 B 24 Q J B 8 to B 7 B 23 I B 6 F B 5 B 0 to B 4 T N=1: The result of ALU operation is negative. Z=1: The result of ALU operation is zero. C=1: carry generated as a result of the operation executed in ALU. V=1: ALU operation resulted in overflow. ‘J’ bit : whether the processor is Jazelle state or not. ‘T ‘ bit : whether the ARM is using 32 -bit ARM instructions or 16 -bit Thumb instructions. • ‘I’ and ‘F’ flags are used for disabling interrupts. If I= 1, NORMAL interrupts are disabled. If F=1 , FAST interrupts are disabled. • • • Mode Select

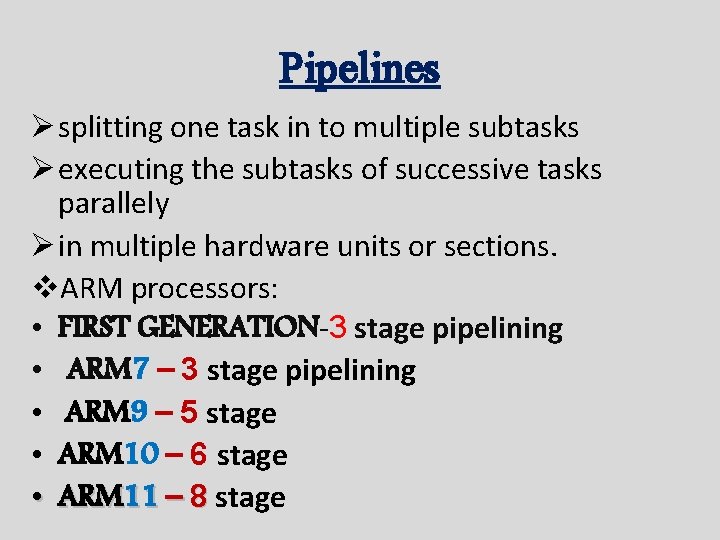

Pipelines Ø splitting one task in to multiple subtasks Ø executing the subtasks of successive tasks parallely Ø in multiple hardware units or sections. v. ARM processors: • FIRST GENERATION-3 stage pipelining • ARM 7 – 3 stage pipelining • ARM 9 – 5 stage • ARM 10 – 6 stage • ARM 11 – 8 stage

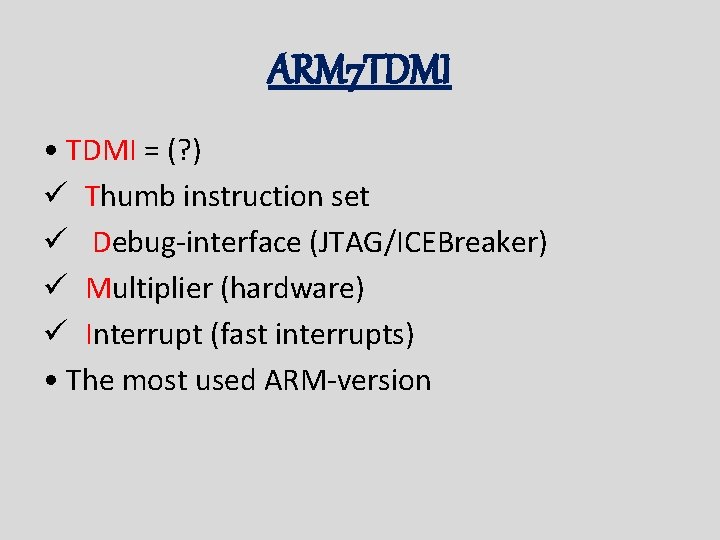

ARM 7 TDMI • TDMI = (? ) ü Thumb instruction set ü Debug-interface (JTAG/ICEBreaker) ü Multiplier (hardware) ü Interrupt (fast interrupts) • The most used ARM-version

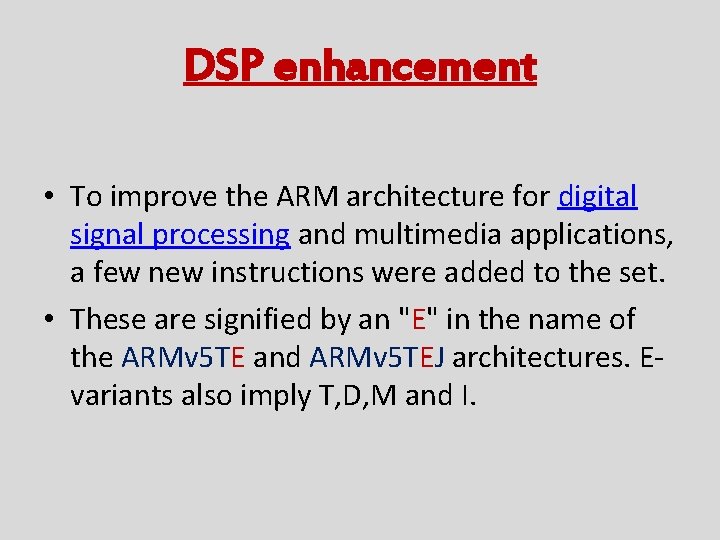

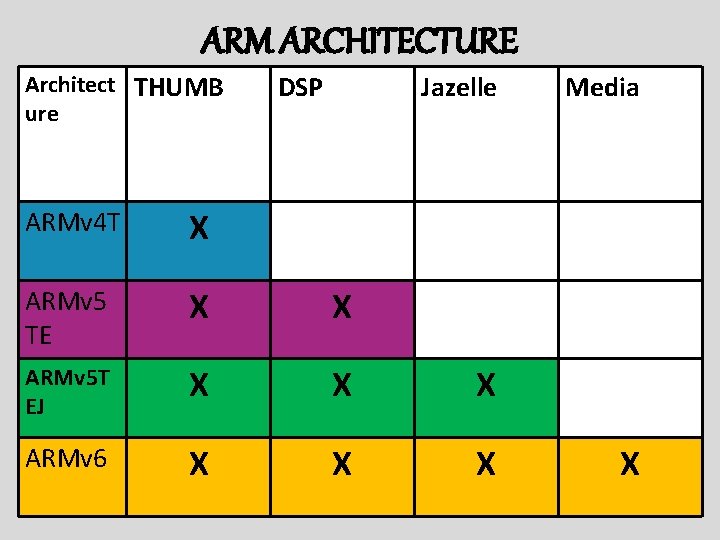

DSP enhancement • To improve the ARM architecture for digital signal processing and multimedia applications, a few new instructions were added to the set. • These are signified by an "E" in the name of the ARMv 5 TE and ARMv 5 TEJ architectures. Evariants also imply T, D, M and I.

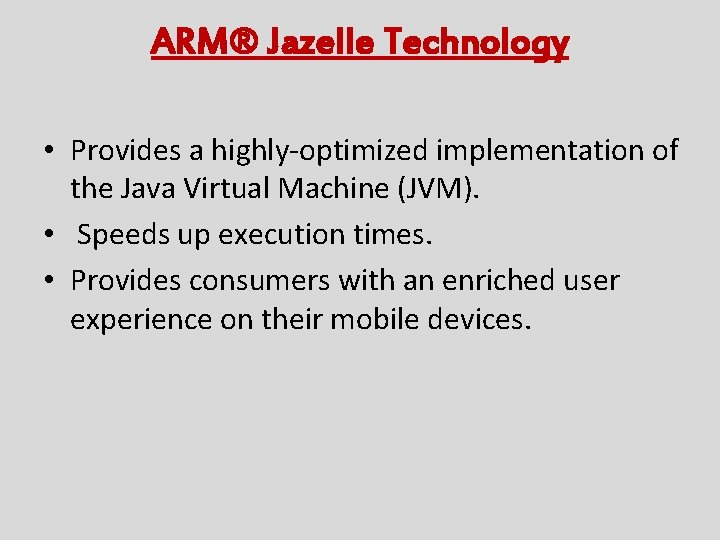

ARM® Jazelle Technology • Provides a highly-optimized implementation of the Java Virtual Machine (JVM). • Speeds up execution times. • Provides consumers with an enriched user experience on their mobile devices.

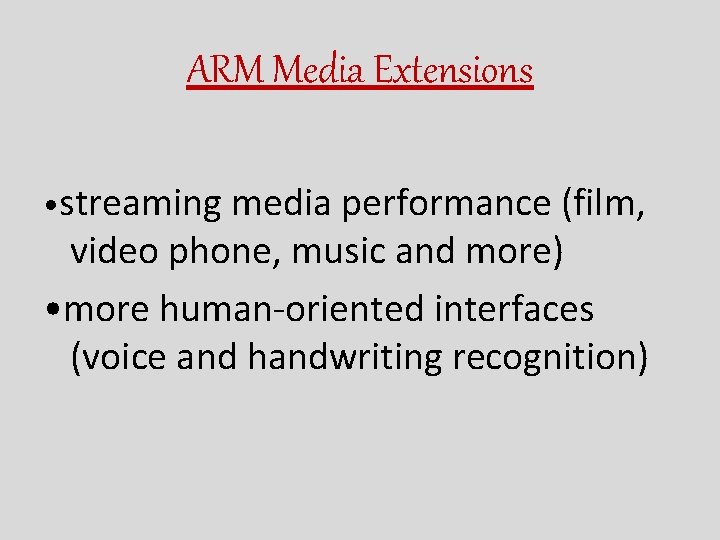

ARM Media Extensions • streaming media performance (film, video phone, music and more) • more human-oriented interfaces (voice and handwriting recognition)

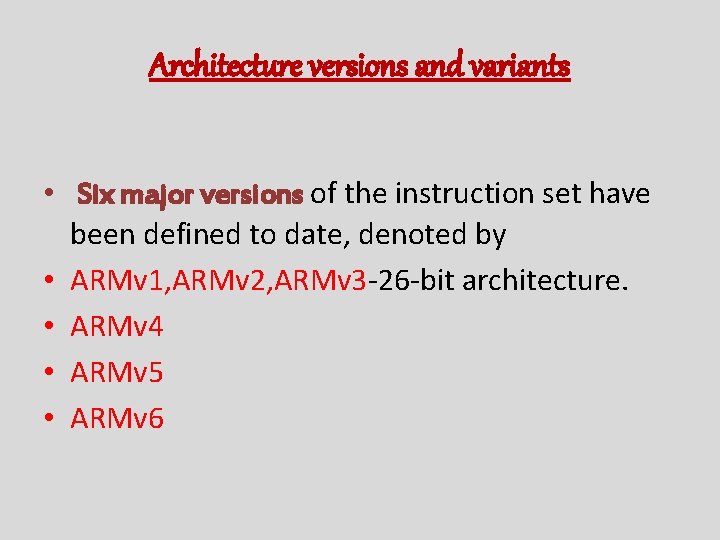

Architecture versions and variants • Six major versions of the instruction set have been defined to date, denoted by • ARMv 1, ARMv 2, ARMv 3 -26 -bit architecture. • ARMv 4 • ARMv 5 • ARMv 6

ARM ARCHITECTURE Architect THUMB ure DSP Jazelle ARMv 4 T X ARMv 5 TE X X ARMv 5 T EJ X X X ARMv 6 X X X Media X

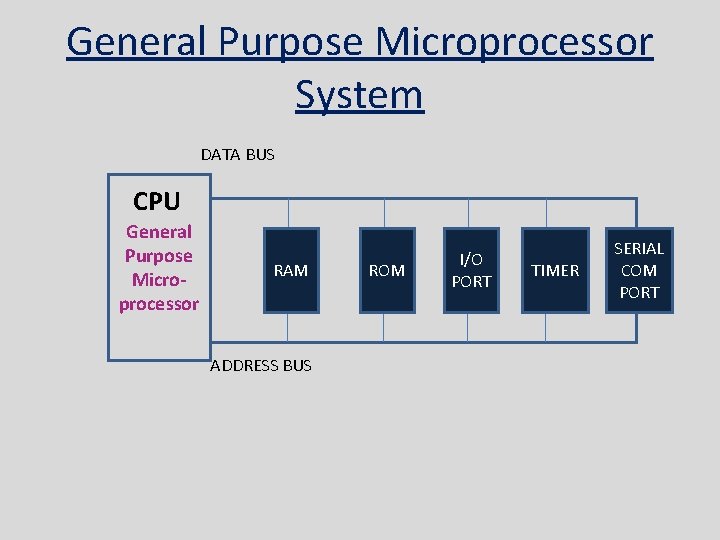

General Purpose Microprocessor System DATA BUS CPU General Purpose Microprocessor RAM ADDRESS BUS ROM I/O PORT TIMER SERIAL COM PORT

MICROCONTROLLERS based on ARM 7 TDMI • The LPC 2131/32 microcontrollers are based on 16/32 bit ARM 7 TDMI • One 8 channel 10 -bit A/D Converters , with conversion time as low as 2. 44 micro sec. • MULTIPLE Serial interfaces. • Two 32 -bit timer/counters.

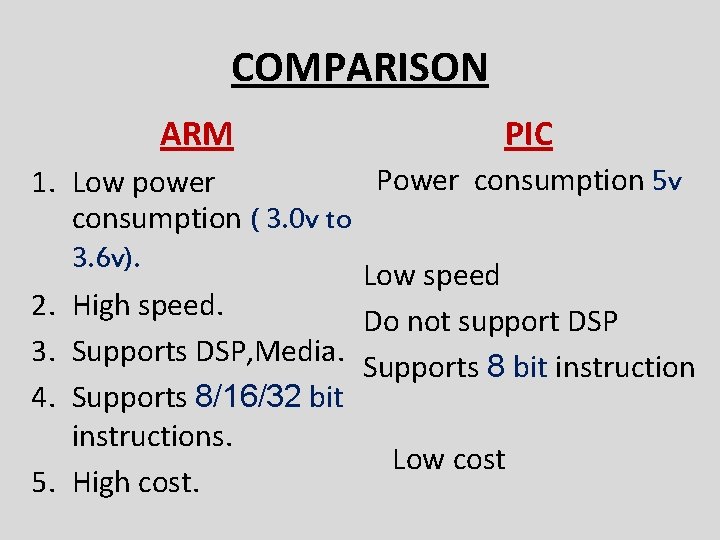

COMPARISON ARM PIC 1. Low power consumption ( 3. 0 v to 3. 6 v). 2. High speed. 3. Supports DSP, Media. 4. Supports 8/16/32 bit instructions. 5. High cost. Power consumption 5 v Low speed Do not support DSP Supports 8 bit instruction Low cost

ARM INSTRUCTIONS

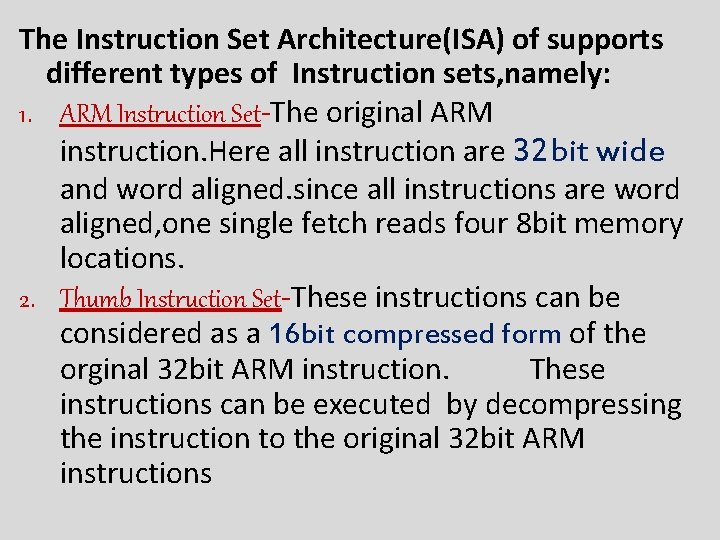

The Instruction Set Architecture(ISA) of supports different types of Instruction sets, namely: 1. ARM Instruction Set-The original ARM instruction. Here all instruction are 32 bit wide and word aligned. since all instructions are word aligned, one single fetch reads four 8 bit memory locations. 2. Thumb Instruction Set-These instructions can be considered as a 16 bit compressed form of the orginal 32 bit ARM instruction. These instructions can be executed by decompressing the instruction to the original 32 bit ARM instructions

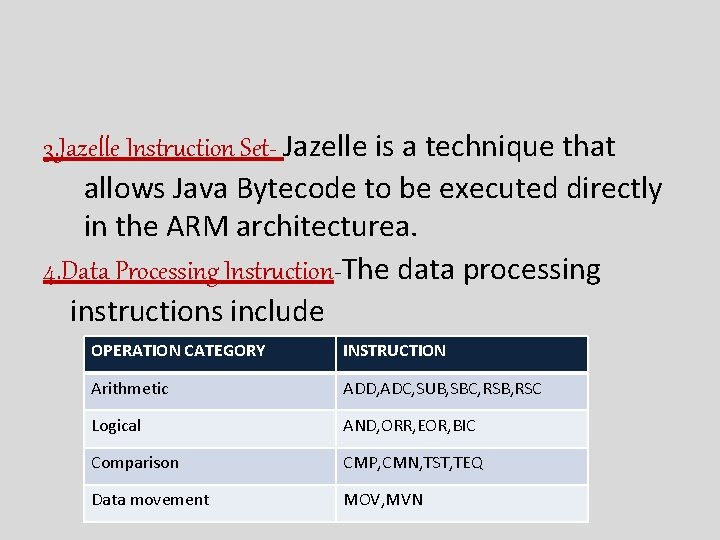

3. Jazelle Instruction Set- Jazelle is a technique that allows Java Bytecode to be executed directly in the ARM architecturea. 4. Data Processing Instruction-The data processing instructions include OPERATION CATEGORY INSTRUCTION Arithmetic ADD, ADC, SUB, SBC, RSB, RSC Logical AND, ORR, EOR, BIC Comparison CMP, CMN, TST, TEQ Data movement MOV, MVN

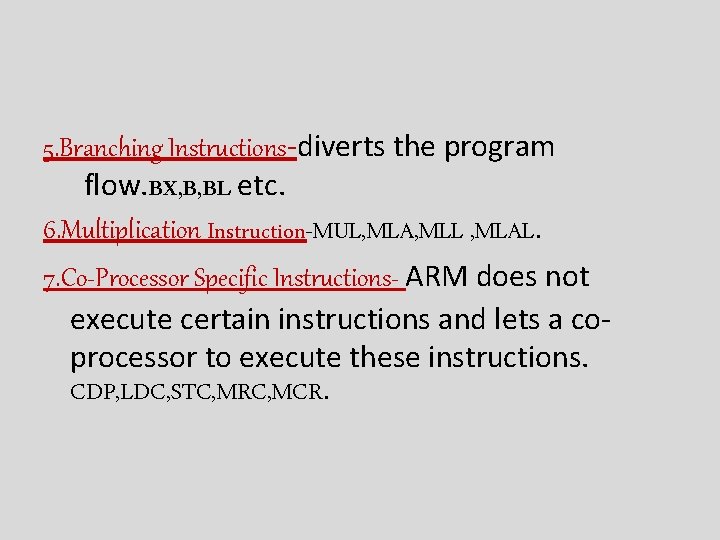

5. Branching Instructions-diverts the program flow. BX, B, BL etc. 6. Multiplication Instruction-MUL, MLA, MLL , MLAL. 7. Co-Processor Specific Instructions- ARM does not execute certain instructions and lets a coprocessor to execute these instructions. CDP, LDC, STC, MRC, MCR.

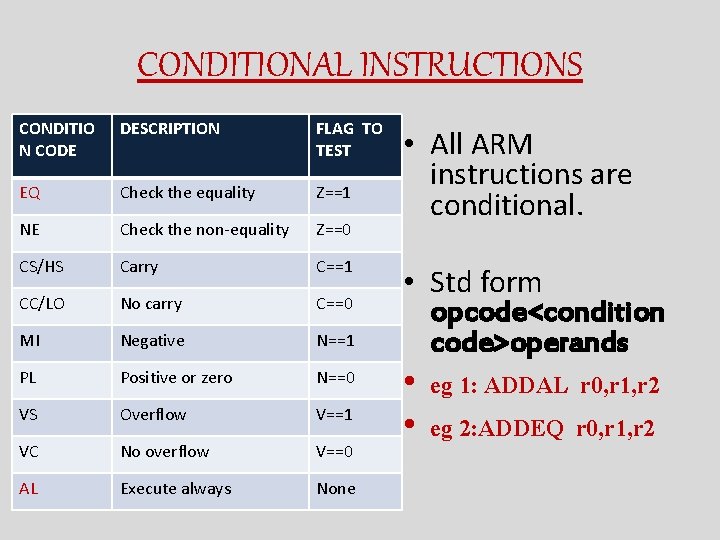

CONDITIONAL INSTRUCTIONS CONDITIO N CODE DESCRIPTION FLAG TO TEST EQ Check the equality Z==1 NE Check the non-equality Z==0 CS/HS Carry C==1 CC/LO No carry C==0 MI Negative N==1 PL Positive or zero N==0 VS Overflow V==1 VC No overflow V==0 AL Execute always None • All ARM instructions are conditional. • Std form opcode<condition code>operands • eg 1: ADDAL r 0, r 1, r 2 • eg 2: ADDEQ r 0, r 1, r 2

SUMMARY Ø 32 -bit RISC-processor core (32 -bit instructions) Ø 37 pieces of 32 -bit integer registers (16 available) Ø Pipelined (ARM 7: 3 stages) Ø Cached (depending on the implementation) Ø Von Neuman-type bus structure (ARM 7), Harvard (ARM 9) Ø 8 / 16 / 32 -bit data types Ø 7 modes of operation (usr, fiq, irq, svc, abt, sys, und) Ø Simple structure Ø Good speed/powerconsumption ratio

REFERENCES • Computer organisation and architecture-carl hamacher. • The 8051 microcontrollers-Muhammad ali mazidi • www. armprocessorsmanuval. com • www. arm. architecture. com • www. arm 7 processors, family. com

THANK YOU

- Slides: 28