Arithmetic Circuits 2 COE 202 Digital Logic Design

![Incrementor Circuit X[3: 0] X 3 X 2 X 1 X 0 4 cout Incrementor Circuit X[3: 0] X 3 X 2 X 1 X 0 4 cout](https://slidetodoc.com/presentation_image_h/1db38870752447bde18756f918b48b3f/image-15.jpg)

- Slides: 15

Arithmetic Circuits 2 COE 202 Digital Logic Design Dr. Muhamed Mudawar King Fahd University of Petroleum and Minerals

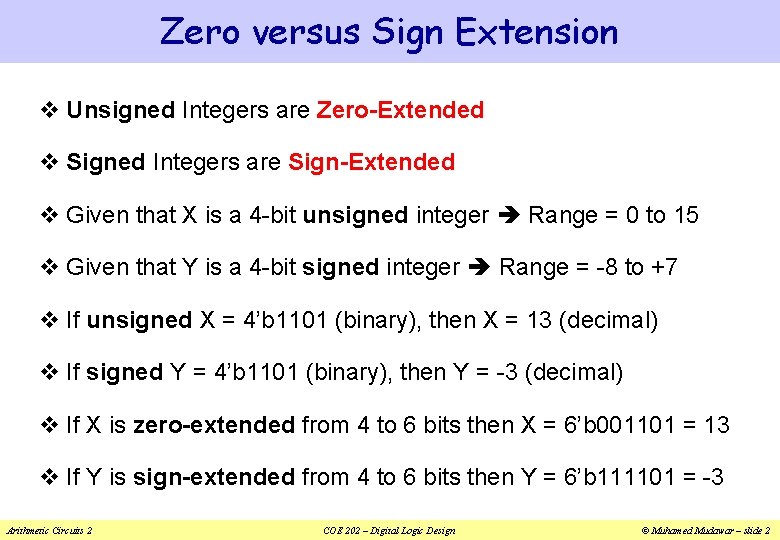

Zero versus Sign Extension v Unsigned Integers are Zero-Extended v Signed Integers are Sign-Extended v Given that X is a 4 -bit unsigned integer Range = 0 to 15 v Given that Y is a 4 -bit signed integer Range = -8 to +7 v If unsigned X = 4’b 1101 (binary), then X = 13 (decimal) v If signed Y = 4’b 1101 (binary), then Y = -3 (decimal) v If X is zero-extended from 4 to 6 bits then X = 6’b 001101 = 13 v If Y is sign-extended from 4 to 6 bits then Y = 6’b 111101 = -3 Arithmetic Circuits 2 COE 202 – Digital Logic Design © Muhamed Mudawar – slide 2

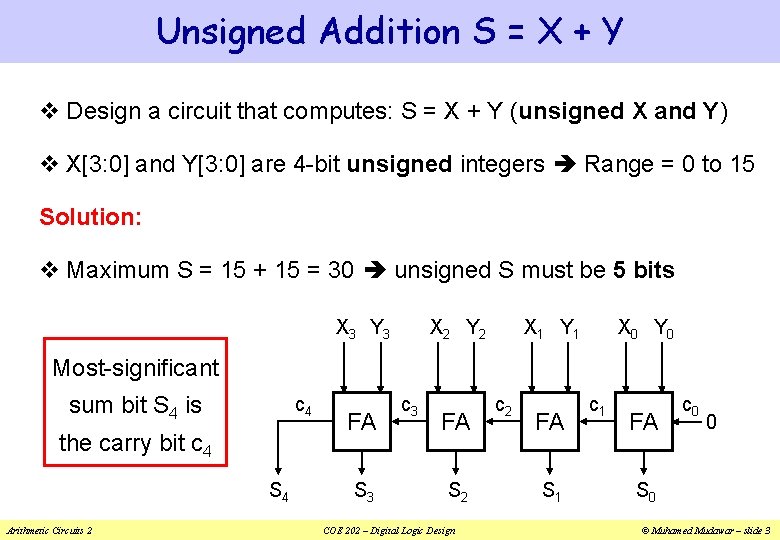

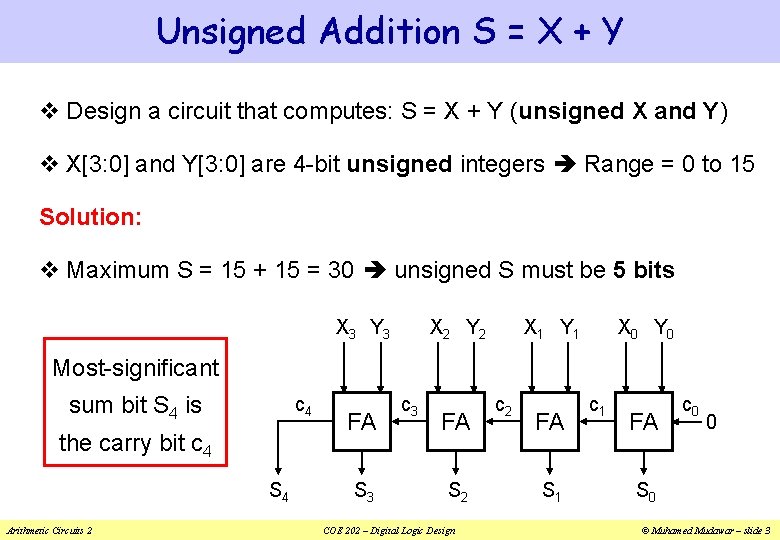

Unsigned Addition S = X + Y v Design a circuit that computes: S = X + Y (unsigned X and Y) v X[3: 0] and Y[3: 0] are 4 -bit unsigned integers Range = 0 to 15 Solution: v Maximum S = 15 + 15 = 30 unsigned S must be 5 bits X 3 Y 3 X 2 Y 2 X 1 Y 1 X 0 Y 0 Most-significant sum bit S 4 is c 4 the carry bit c 4 S 4 Arithmetic Circuits 2 FA S 3 c 3 FA S 2 COE 202 – Digital Logic Design c 2 FA S 1 c 1 FA c 0 0 S 0 © Muhamed Mudawar – slide 3

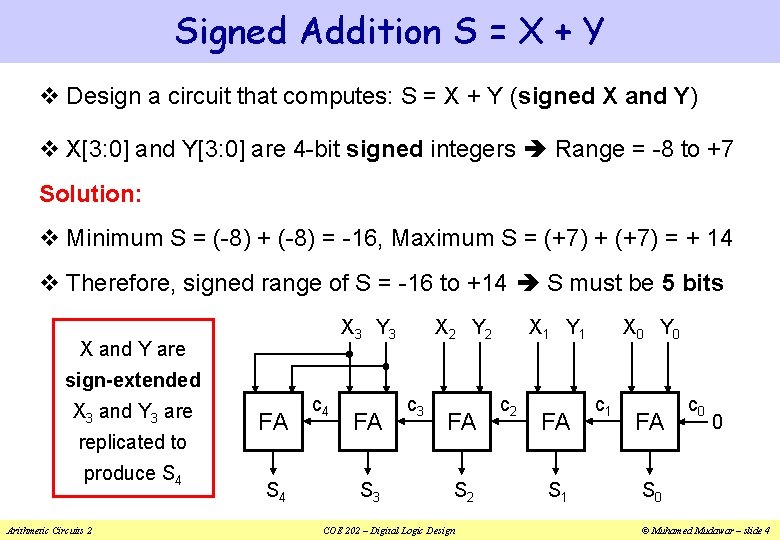

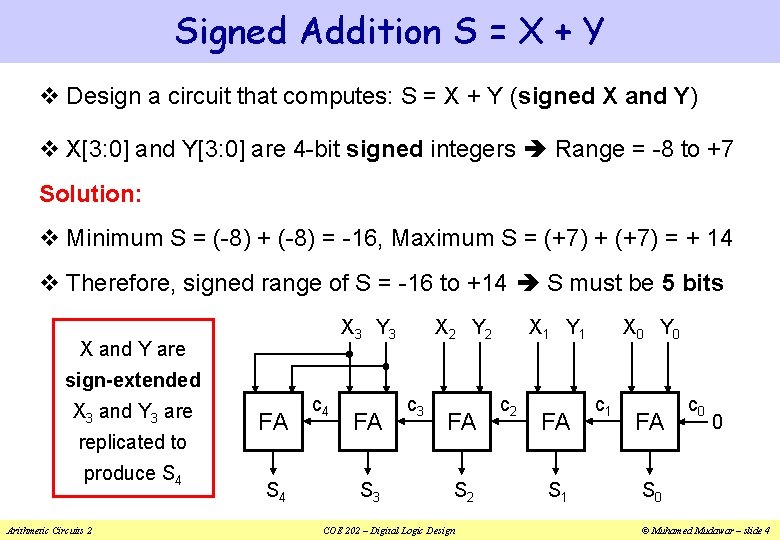

Signed Addition S = X + Y v Design a circuit that computes: S = X + Y (signed X and Y) v X[3: 0] and Y[3: 0] are 4 -bit signed integers Range = -8 to +7 Solution: v Minimum S = (-8) + (-8) = -16, Maximum S = (+7) + (+7) = + 14 v Therefore, signed range of S = -16 to +14 S must be 5 bits X 3 Y 3 X and Y are X 2 Y 2 X 1 Y 1 X 0 Y 0 sign-extended X 3 and Y 3 are replicated to produce S 4 Arithmetic Circuits 2 FA S 4 c 4 FA S 3 c 3 FA S 2 COE 202 – Digital Logic Design c 2 FA S 1 c 1 FA c 0 0 S 0 © Muhamed Mudawar – slide 4

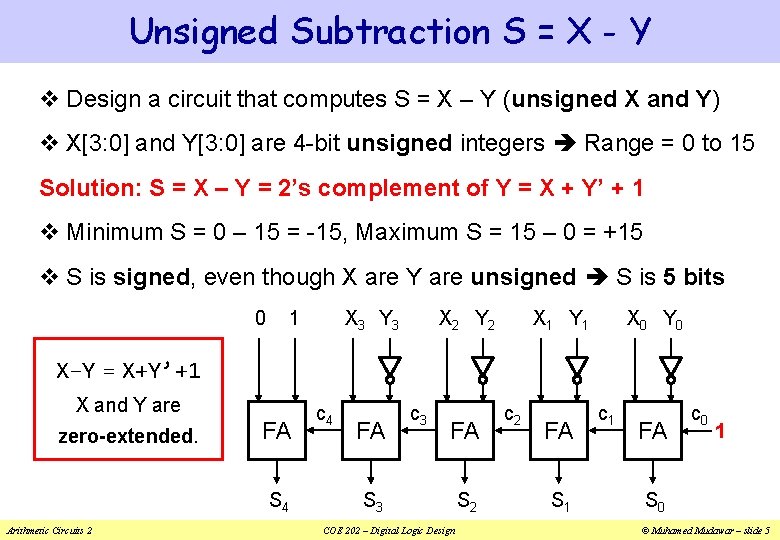

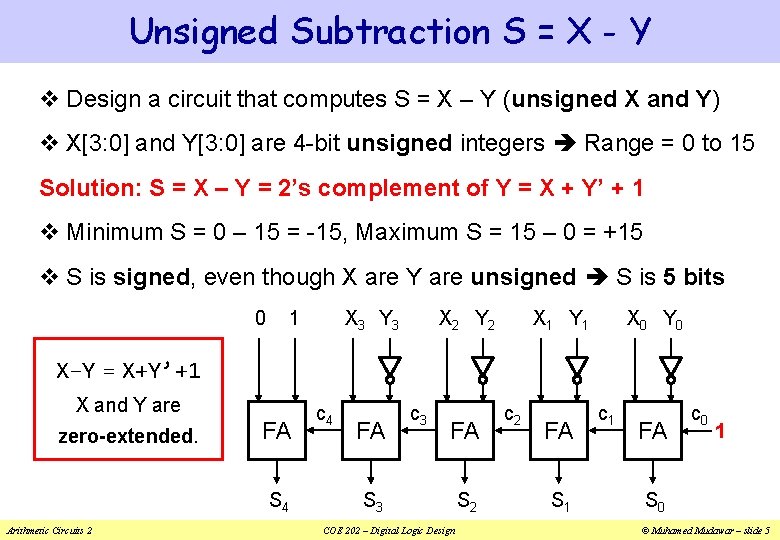

Unsigned Subtraction S = X - Y v Design a circuit that computes S = X – Y (unsigned X and Y) v X[3: 0] and Y[3: 0] are 4 -bit unsigned integers Range = 0 to 15 Solution: S = X – Y = 2’s complement of Y = X + Y’ + 1 v Minimum S = 0 – 15 = -15, Maximum S = 15 – 0 = +15 v S is signed, even though X are Y are unsigned S is 5 bits 0 X 3 Y 3 1 X 2 Y 2 X 1 Y 1 X 0 Y 0 X–Y = X+Y’+1 X and Y are zero-extended. FA S 4 Arithmetic Circuits 2 c 4 FA c 3 FA S 3 COE 202 – Digital Logic Design S 2 c 2 FA S 1 c 1 FA c 0 1 S 0 © Muhamed Mudawar – slide 5

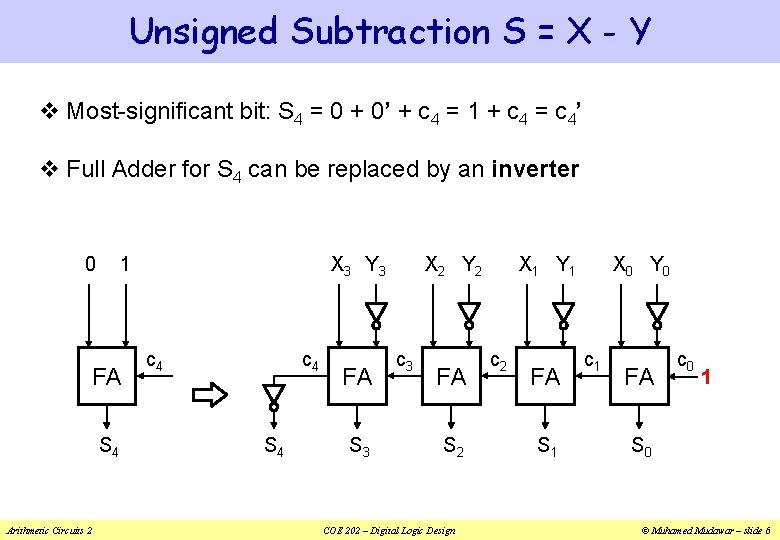

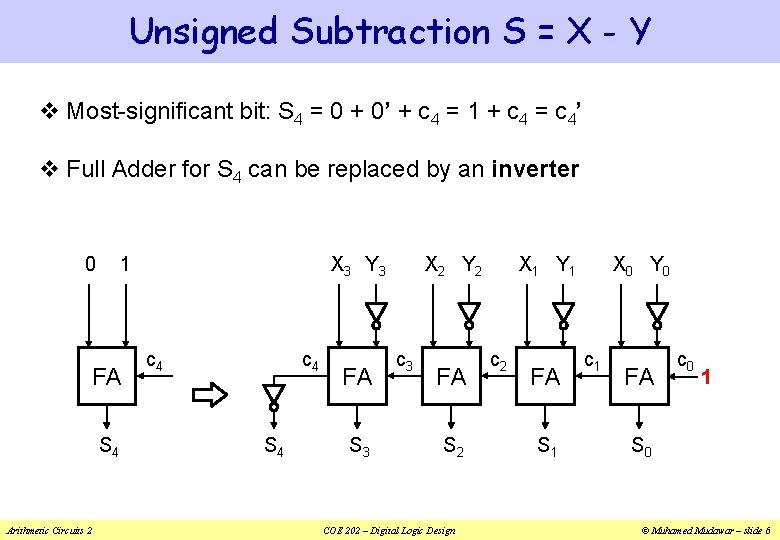

Unsigned Subtraction S = X - Y v Most-significant bit: S 4 = 0 + 0’ + c 4 = 1 + c 4 = c 4’ v Full Adder for S 4 can be replaced by an inverter 0 FA S 4 Arithmetic Circuits 2 X 3 Y 3 1 c 4 S 4 FA S 3 X 2 Y 2 c 3 FA S 2 COE 202 – Digital Logic Design X 1 Y 1 c 2 FA S 1 X 0 Y 0 c 1 FA c 0 1 S 0 © Muhamed Mudawar – slide 6

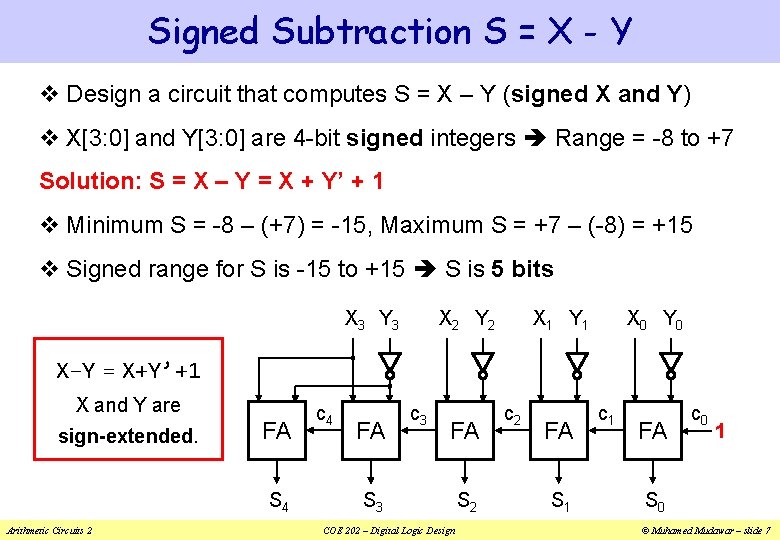

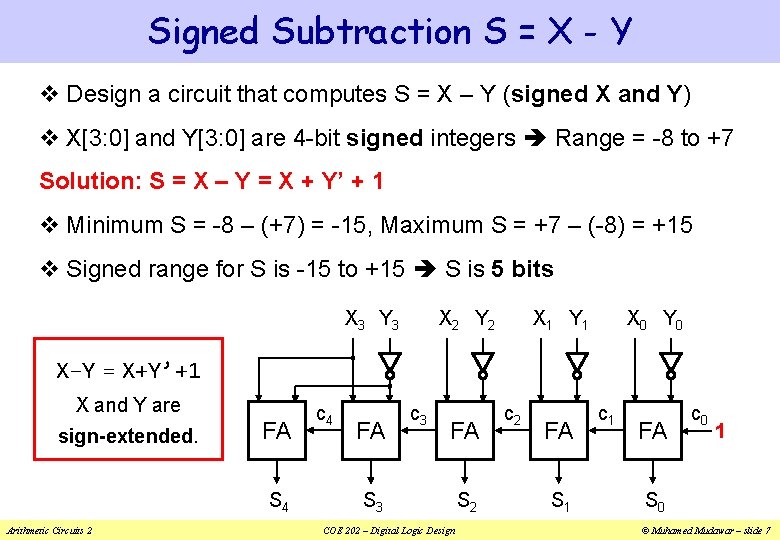

Signed Subtraction S = X - Y v Design a circuit that computes S = X – Y (signed X and Y) v X[3: 0] and Y[3: 0] are 4 -bit signed integers Range = -8 to +7 Solution: S = X – Y = X + Y’ + 1 v Minimum S = -8 – (+7) = -15, Maximum S = +7 – (-8) = +15 v Signed range for S is -15 to +15 S is 5 bits X 3 Y 3 X 2 Y 2 X 1 Y 1 X 0 Y 0 X–Y = X+Y’+1 X and Y are sign-extended. FA S 4 Arithmetic Circuits 2 c 4 FA c 3 FA S 3 COE 202 – Digital Logic Design S 2 c 2 FA S 1 c 1 FA c 0 1 S 0 © Muhamed Mudawar – slide 7

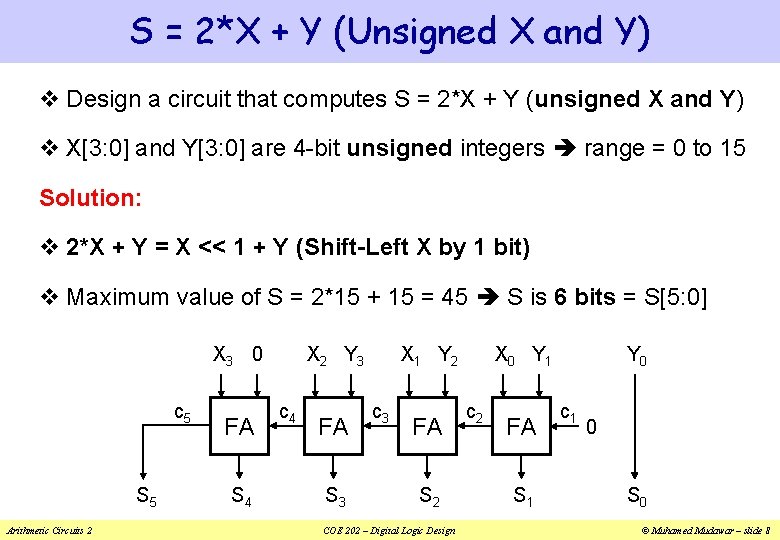

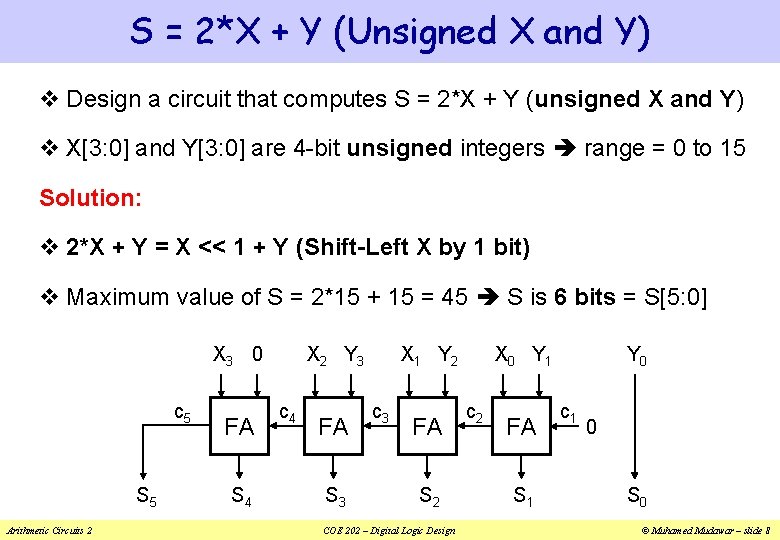

S = 2*X + Y (Unsigned X and Y) v Design a circuit that computes S = 2*X + Y (unsigned X and Y) v X[3: 0] and Y[3: 0] are 4 -bit unsigned integers range = 0 to 15 Solution: v 2*X + Y = X << 1 + Y (Shift-Left X by 1 bit) v Maximum value of S = 2*15 + 15 = 45 S is 6 bits = S[5: 0] X 3 0 c 5 S 5 Arithmetic Circuits 2 FA S 4 X 2 Y 3 c 4 FA S 3 X 1 Y 2 c 3 FA S 2 COE 202 – Digital Logic Design X 0 Y 1 c 2 FA S 1 Y 0 c 1 0 S 0 © Muhamed Mudawar – slide 8

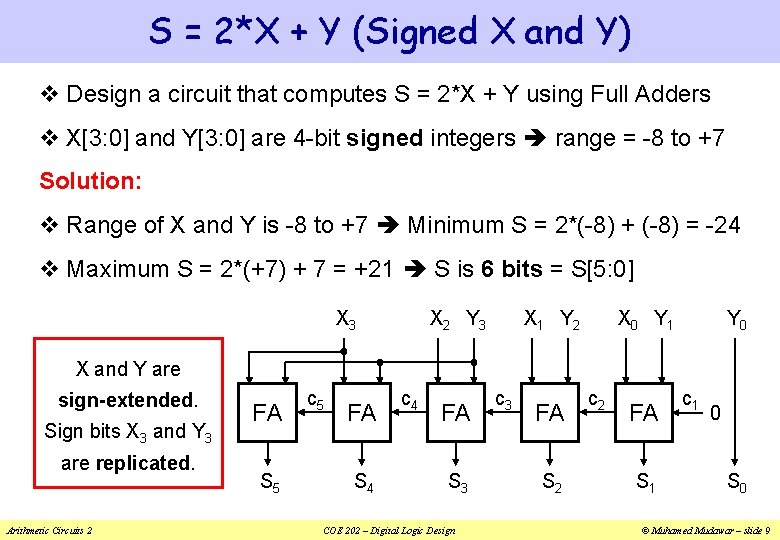

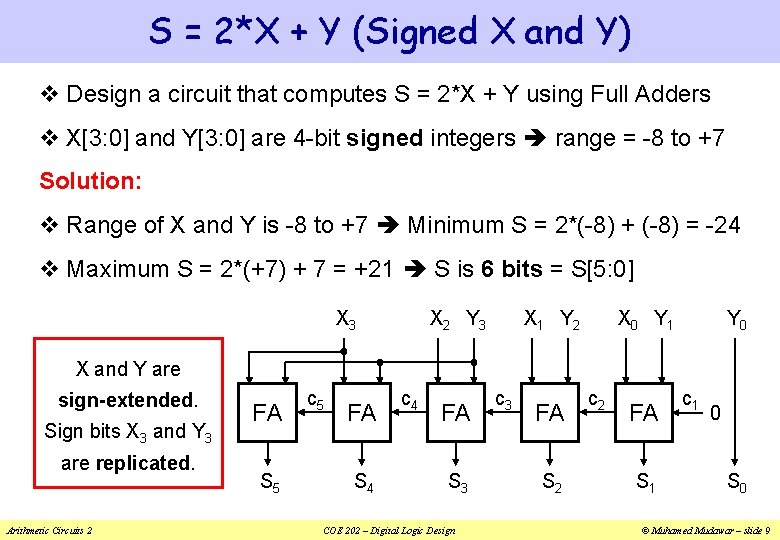

S = 2*X + Y (Signed X and Y) v Design a circuit that computes S = 2*X + Y using Full Adders v X[3: 0] and Y[3: 0] are 4 -bit signed integers range = -8 to +7 Solution: v Range of X and Y is -8 to +7 Minimum S = 2*(-8) + (-8) = -24 v Maximum S = 2*(+7) + 7 = +21 S is 6 bits = S[5: 0] X 3 X 2 Y 3 X 1 Y 2 X 0 Y 1 Y 0 X and Y are sign-extended. Sign bits X 3 and Y 3 are replicated. Arithmetic Circuits 2 FA S 5 c 5 FA S 4 c 4 FA S 3 COE 202 – Digital Logic Design c 3 FA S 2 c 2 FA S 1 c 1 0 S 0 © Muhamed Mudawar – slide 9

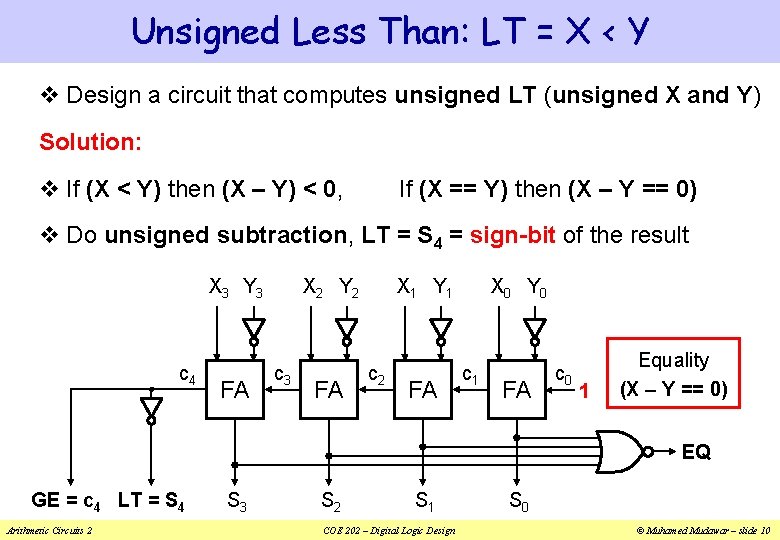

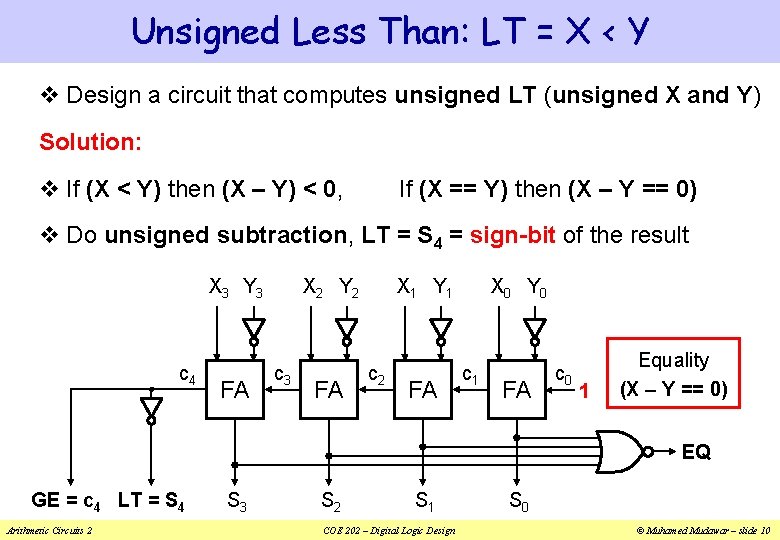

Unsigned Less Than: LT = X < Y v Design a circuit that computes unsigned LT (unsigned X and Y) Solution: v If (X < Y) then (X – Y) < 0, If (X == Y) then (X – Y == 0) v Do unsigned subtraction, LT = S 4 = sign-bit of the result X 3 Y 3 c 4 FA X 2 Y 2 c 3 FA X 1 Y 1 c 2 FA X 0 Y 0 c 1 FA c 0 1 Equality (X – Y == 0) EQ GE = c 4 LT = S 4 Arithmetic Circuits 2 S 3 S 2 S 1 COE 202 – Digital Logic Design S 0 © Muhamed Mudawar – slide 10

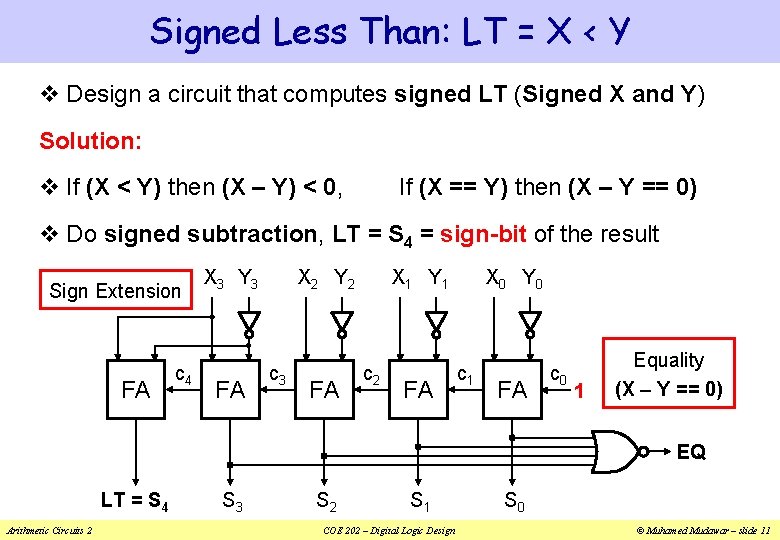

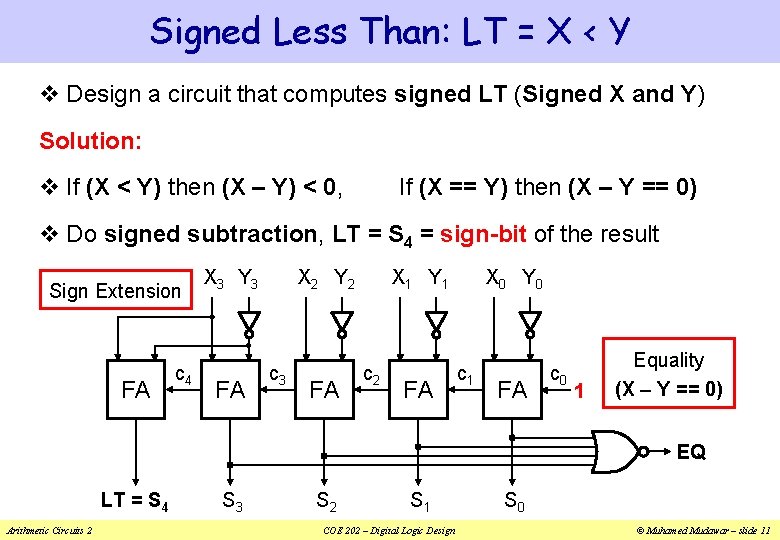

Signed Less Than: LT = X < Y v Design a circuit that computes signed LT (Signed X and Y) Solution: v If (X < Y) then (X – Y) < 0, If (X == Y) then (X – Y == 0) v Do signed subtraction, LT = S 4 = sign-bit of the result Sign Extension FA c 4 X 3 Y 3 FA X 2 Y 2 c 3 FA X 1 Y 1 c 2 FA X 0 Y 0 c 1 FA c 0 1 Equality (X – Y == 0) EQ LT = S 4 Arithmetic Circuits 2 S 3 S 2 S 1 COE 202 – Digital Logic Design S 0 © Muhamed Mudawar – slide 11

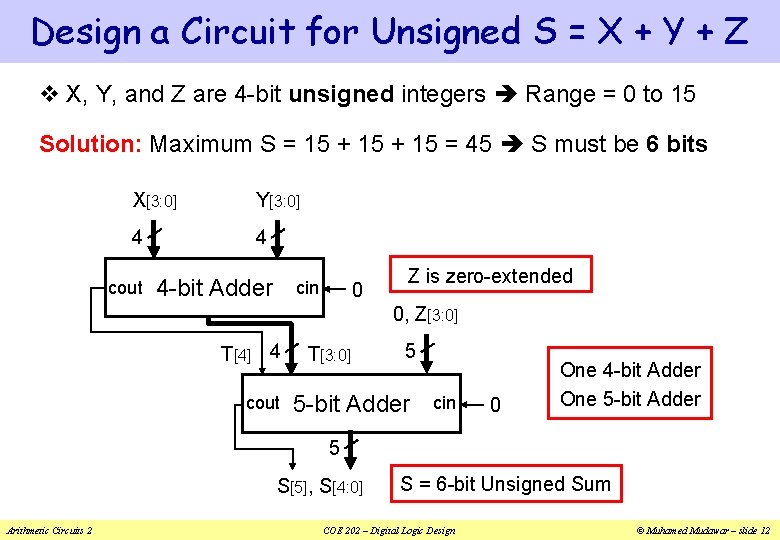

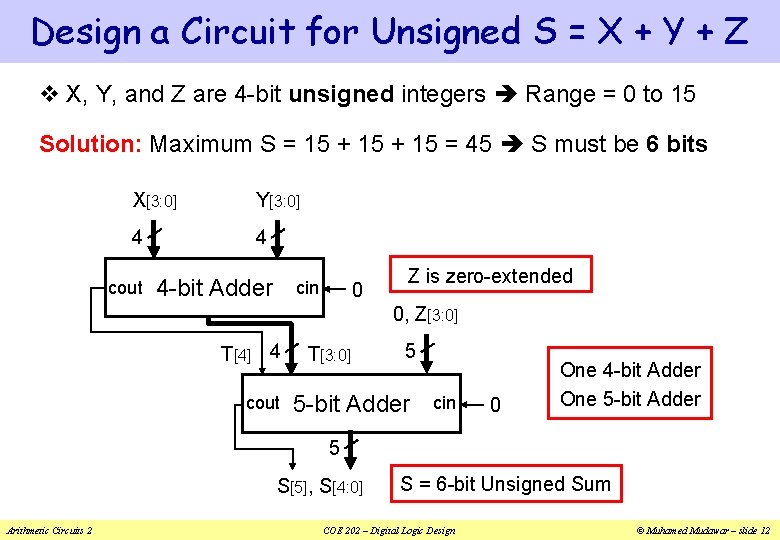

Design a Circuit for Unsigned S = X + Y + Z v X, Y, and Z are 4 -bit unsigned integers Range = 0 to 15 Solution: Maximum S = 15 + 15 = 45 S must be 6 bits X[3: 0] Y[3: 0] 4 4 cout 4 -bit Adder cin 0 Z is zero-extended 0, Z[3: 0] T[4] 4 cout T[3: 0] 5 5 -bit Adder cin 0 One 4 -bit Adder One 5 -bit Adder 5 S[5], S[4: 0] Arithmetic Circuits 2 S = 6 -bit Unsigned Sum COE 202 – Digital Logic Design © Muhamed Mudawar – slide 12

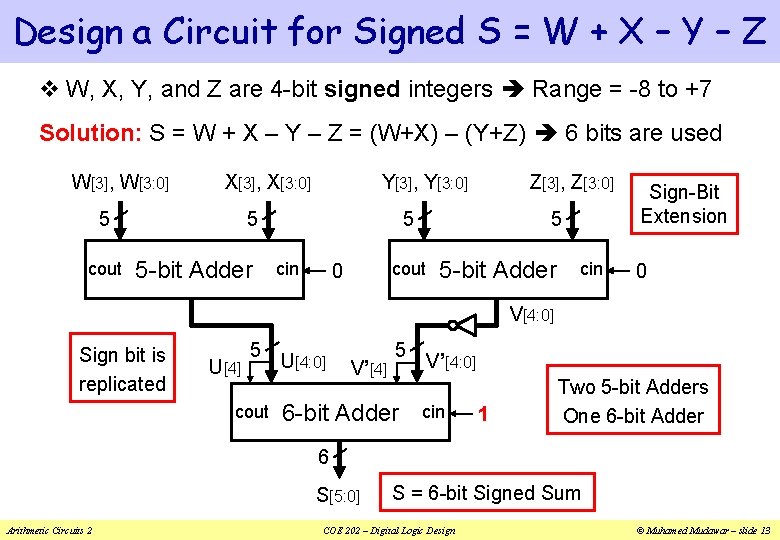

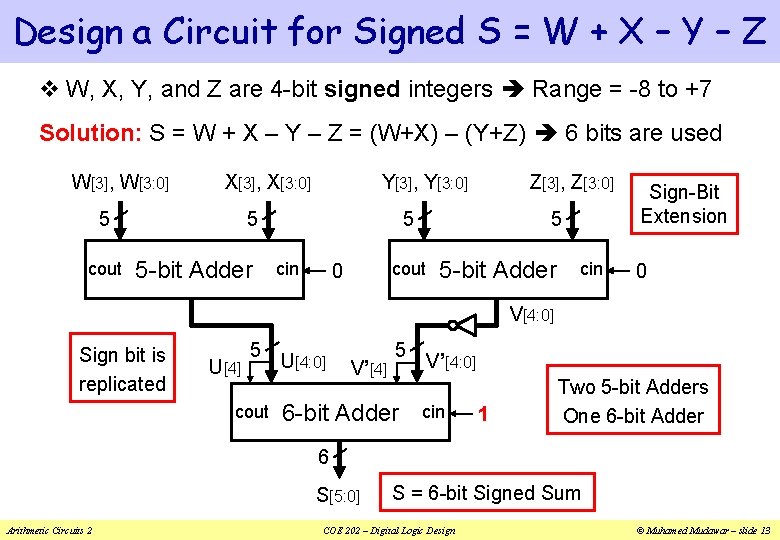

Design a Circuit for Signed S = W + X – Y – Z v W, X, Y, and Z are 4 -bit signed integers Range = -8 to +7 Solution: S = W + X – Y – Z = (W+X) – (Y+Z) 6 bits are used W[3], W[3: 0] X[3], X[3: 0] 5 cout Y[3], Y[3: 0] 5 5 -bit Adder Z[3], Z[3: 0] 5 cin 5 cout 0 5 -bit Adder cin Sign-Bit Extension 0 V[4: 0] Sign bit is replicated U[4] 5 cout U[4: 0] V’[4] 5 6 -bit Adder V’[4: 0] cin 1 Two 5 -bit Adders One 6 -bit Adder 6 S[5: 0] Arithmetic Circuits 2 S = 6 -bit Signed Sum COE 202 – Digital Logic Design © Muhamed Mudawar – slide 13

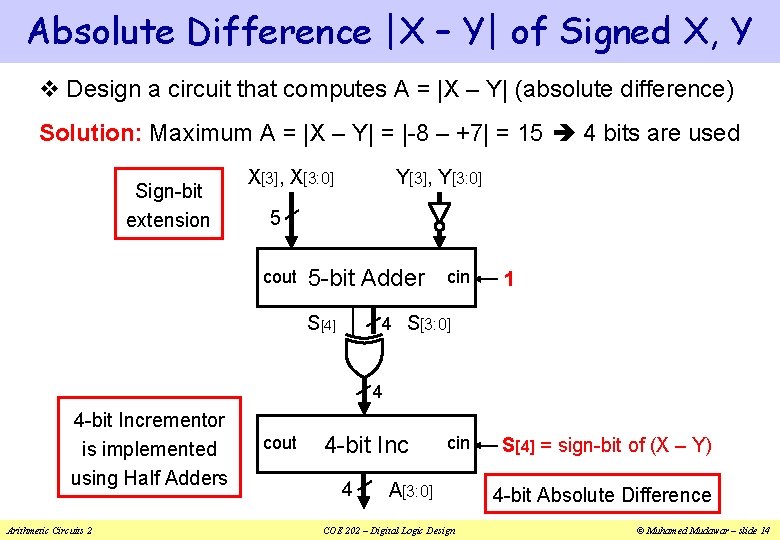

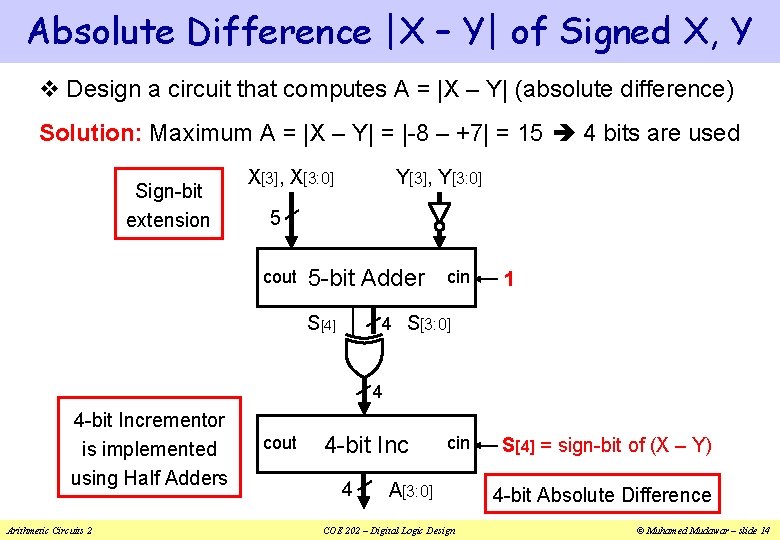

Absolute Difference |X – Y| of Signed X, Y v Design a circuit that computes A = |X – Y| (absolute difference) Solution: Maximum A = |X – Y| = |-8 – +7| = 15 4 bits are used Sign-bit extension X[3], X[3: 0] Y[3], Y[3: 0] 5 cout 5 -bit Adder S[4] cin 1 4 S[3: 0] 4 4 -bit Incrementor is implemented using Half Adders Arithmetic Circuits 2 cout 4 -bit Inc 4 cin A[3: 0] COE 202 – Digital Logic Design S[4] = sign-bit of (X – Y) 4 -bit Absolute Difference © Muhamed Mudawar – slide 14

![Incrementor Circuit X3 0 X 3 X 2 X 1 X 0 4 cout Incrementor Circuit X[3: 0] X 3 X 2 X 1 X 0 4 cout](https://slidetodoc.com/presentation_image_h/1db38870752447bde18756f918b48b3f/image-15.jpg)

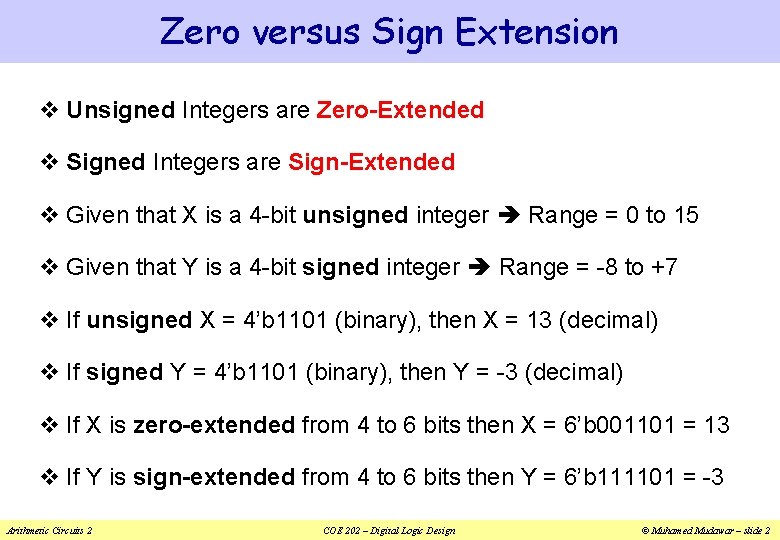

Incrementor Circuit X[3: 0] X 3 X 2 X 1 X 0 4 cout cin Incrementor cout HA c 3 HA c 2 HA c 1 HA cin 4 Y[3: 0] Y 3 X 3 cout X 2 c 3 Y 3 Arithmetic Circuits 2 Y 2 X 1 c 2 Y 1 X 0 c 1 Y 1 COE 202 – Digital Logic Design Y 0 cin Y 0 © Muhamed Mudawar – slide 15