Arithmetic and Logic Chapter 3 Sepehr Naimi Sarmad

- Slides: 20

Arithmetic and Logic Chapter 3 Sepehr Naimi Sarmad Naimi www. Nicer. Land. com

Objectives • • • Add, subtract, multiply, and divide Carry Logic instructions Shift and Rotate BCD, Packed BCD and ASCII conversion. 2

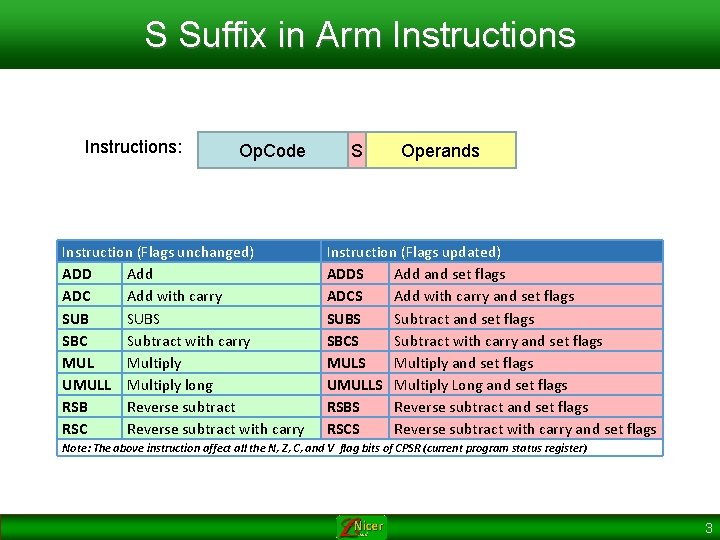

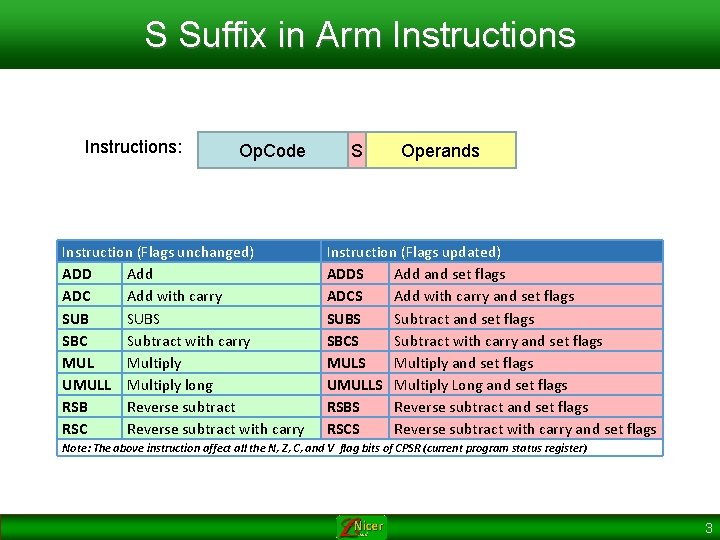

S Suffix in Arm Instructions: Op. Code Instruction (Flags unchanged) ADD Add ADC Add with carry SUBS SBC Subtract with carry MUL Multiply UMULL Multiply long RSB Reverse subtract RSC Reverse subtract with carry S Operands Instruction (Flags updated) ADDS Add and set flags ADCS Add with carry and set flags SUBS Subtract and set flags SBCS Subtract with carry and set flags MULS Multiply and set flags UMULLS Multiply Long and set flags RSBS Reverse subtract and set flags RSCS Reverse subtract with carry and set flags Note: The above instruction affect all the N, Z, C, and V flag bits of CPSR (current program status register) 3

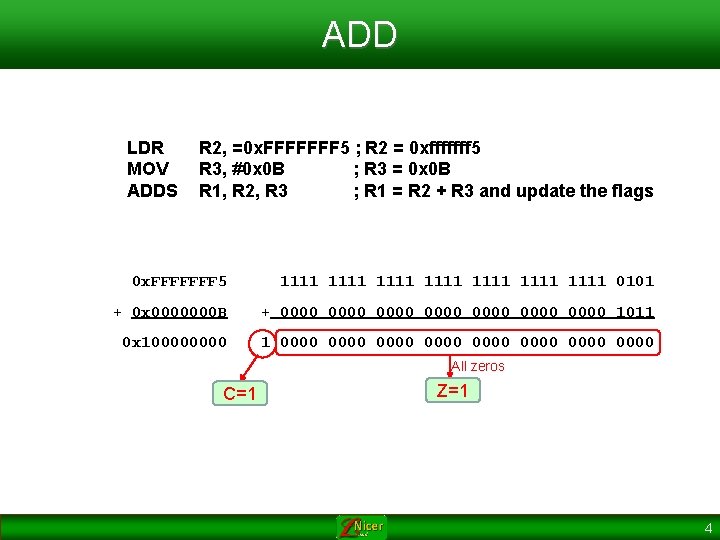

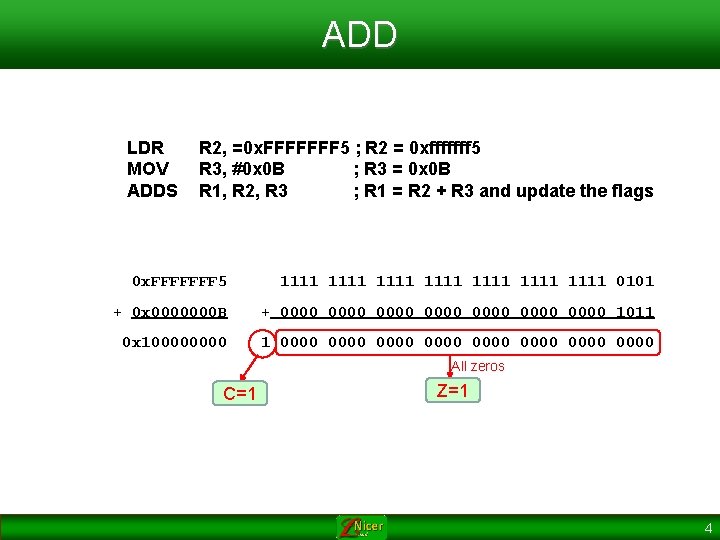

ADD LDR MOV ADDS R 2, =0 x. FFFFFFF 5 ; R 2 = 0 xfffffff 5 R 3, #0 x 0 B ; R 3 = 0 x 0 B R 1, R 2, R 3 ; R 1 = R 2 + R 3 and update the flags 0 x. FFFFFFF 5 1111 1111 0101 + 0 x 0000000 B + 0000 0000 1011 0 x 10000 1 0000 0000 All zeros C=1 Z=1 4

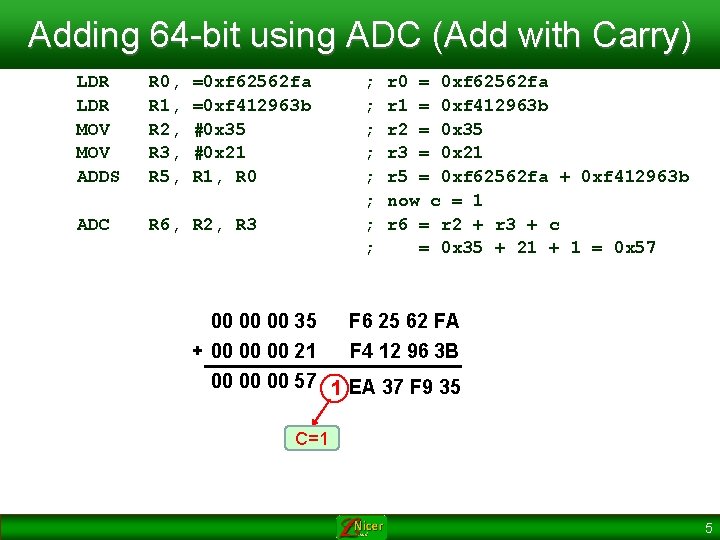

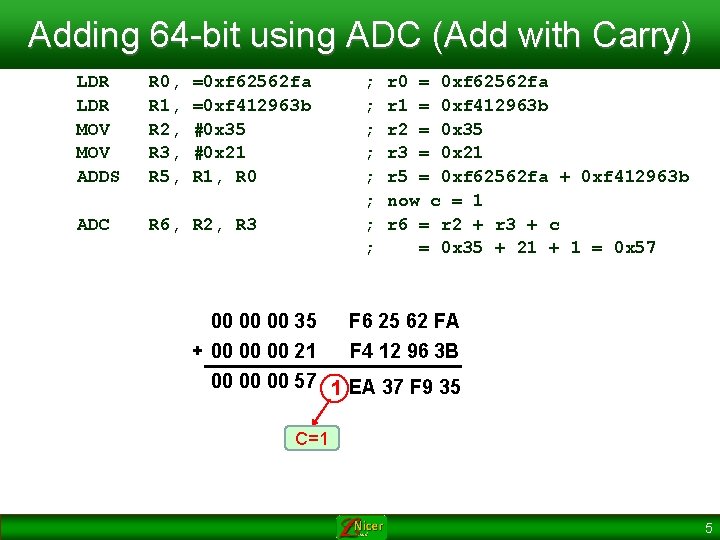

Adding 64 -bit using ADC (Add with Carry) LDR MOV ADDS R 0, R 1, R 2, R 3, R 5, =0 xf 62562 fa =0 xf 412963 b #0 x 35 #0 x 21 R 1, R 0 ADC R 6, R 2, R 3 ; ; ; ; r 0 = 0 xf 62562 fa r 1 = 0 xf 412963 b r 2 = 0 x 35 r 3 = 0 x 21 r 5 = 0 xf 62562 fa + 0 xf 412963 b now c = 1 r 6 = r 2 + r 3 + c = 0 x 35 + 21 + 1 = 0 x 57 00 00 00 35 F 6 25 62 FA + 00 00 00 21 F 4 12 96 3 B 00 00 00 57 1 EA 37 F 9 35 C=1 5

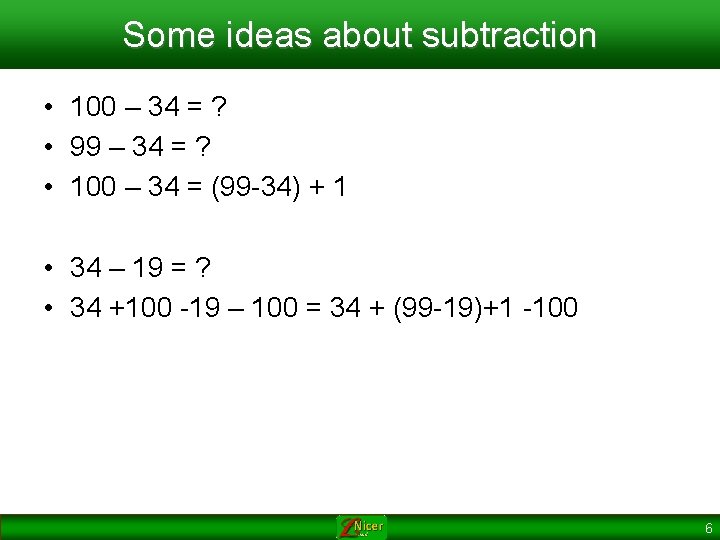

Some ideas about subtraction • 100 – 34 = ? • 99 – 34 = ? • 100 – 34 = (99 -34) + 1 • 34 – 19 = ? • 34 +100 -19 – 100 = 34 + (99 -19)+1 -100 6

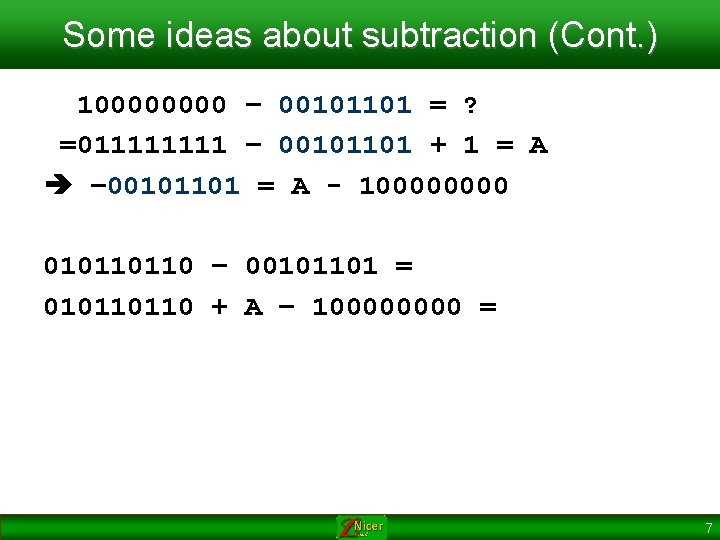

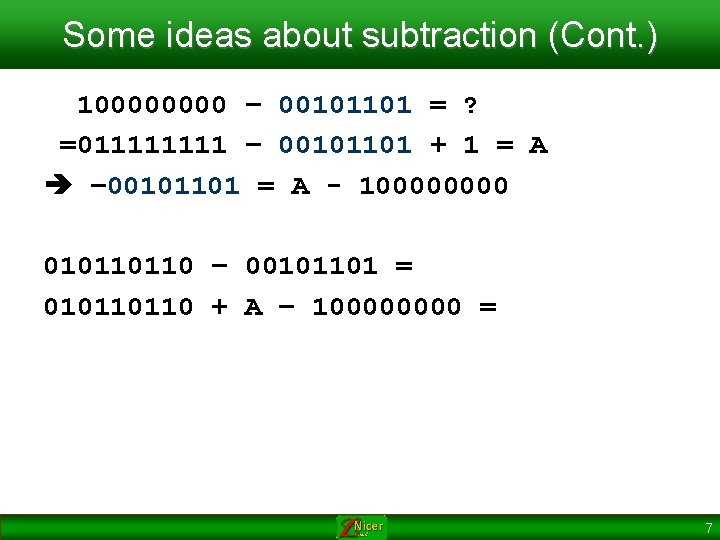

Some ideas about subtraction (Cont. ) 10000 – 00101101 = ? =01111 – 00101101 + 1 = A – 00101101 = A - 10000 010110110 – 00101101 = 010110110 + A – 10000 = 7

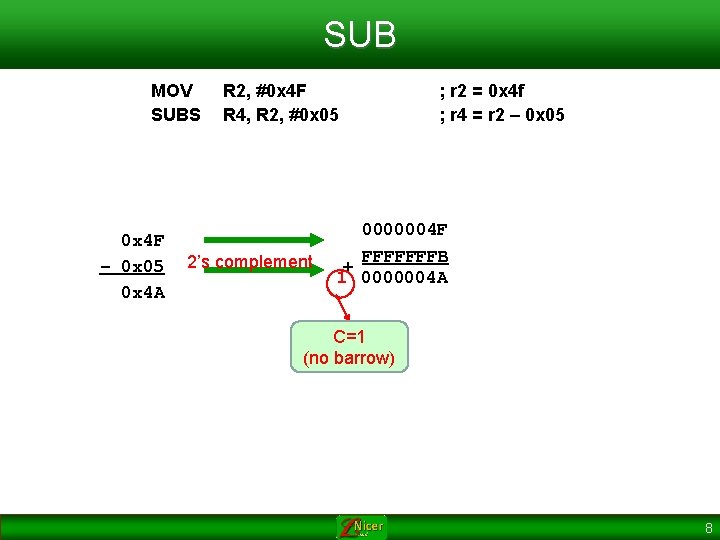

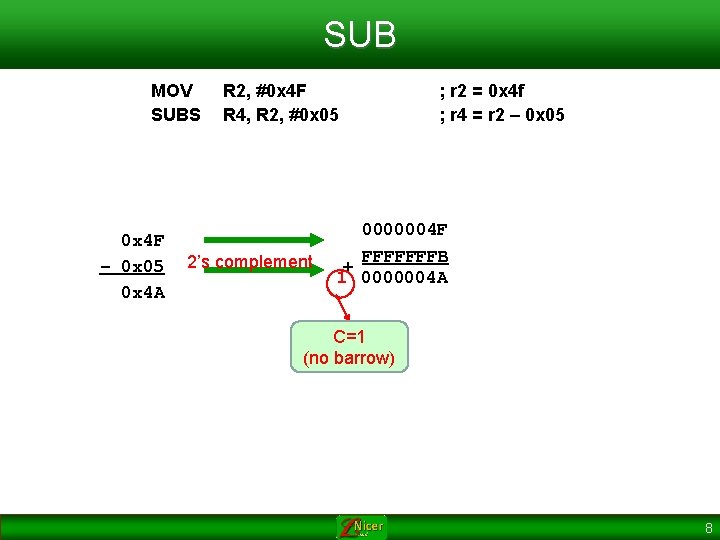

SUB MOV SUBS 0 x 4 F – 0 x 05 0 x 4 A R 2, #0 x 4 F R 4, R 2, #0 x 05 2’s complement ; r 2 = 0 x 4 f ; r 4 = r 2 – 0 x 05 0000004 F FFFFFFFB + 1 0000004 A C=1 (no barrow) 8

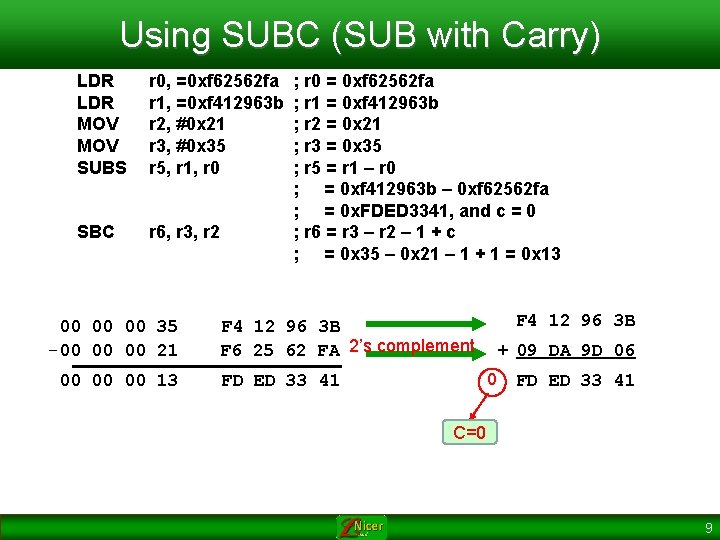

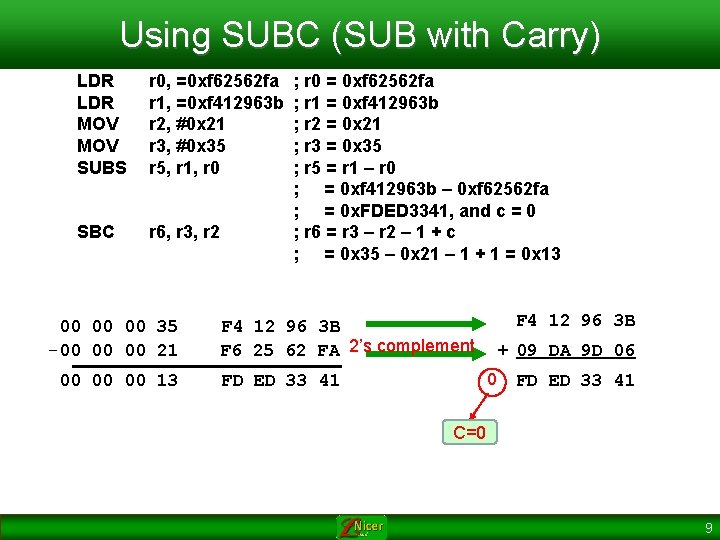

Using SUBC (SUB with Carry) LDR MOV SUBS r 0, =0 xf 62562 fa r 1, =0 xf 412963 b r 2, #0 x 21 r 3, #0 x 35 r 5, r 1, r 0 SBC r 6, r 3, r 2 00 00 00 35 – 00 00 00 21 00 00 00 13 ; r 0 = 0 xf 62562 fa ; r 1 = 0 xf 412963 b ; r 2 = 0 x 21 ; r 3 = 0 x 35 ; r 5 = r 1 – r 0 ; = 0 xf 412963 b – 0 xf 62562 fa ; = 0 x. FDED 3341, and c = 0 ; r 6 = r 3 – r 2 – 1 + c ; = 0 x 35 – 0 x 21 – 1 + 1 = 0 x 13 F 4 12 96 3 B F 6 25 62 FA 2’s complement F 4 12 96 3 B + 09 DA 9 D 06 0 FD ED 33 41 C=0 9

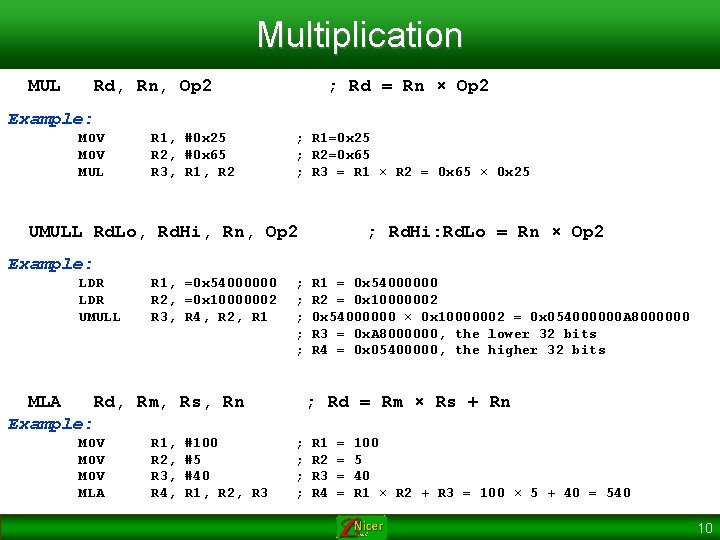

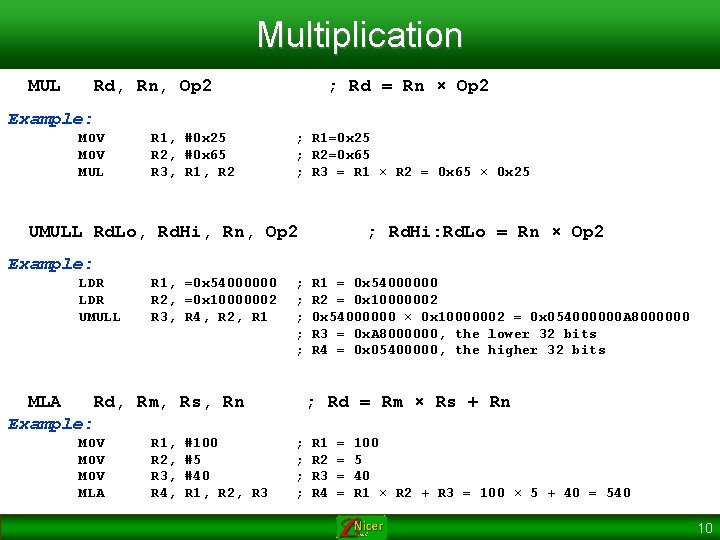

Multiplication MUL Rd, Rn, Op 2 ; Rd = Rn × Op 2 Example: MOV MUL R 1, #0 x 25 R 2, #0 x 65 R 3, R 1, R 2 ; R 1=0 x 25 ; R 2=0 x 65 ; R 3 = R 1 × R 2 = 0 x 65 × 0 x 25 UMULL Rd. Lo, Rd. Hi, Rn, Op 2 ; Rd. Hi: Rd. Lo = Rn × Op 2 Example: LDR UMULL R 1, =0 x 54000000 R 2, =0 x 10000002 R 3, R 4, R 2, R 1 ; ; ; MLA Rd, Rm, Rs, Rn Example: MOV MOV MLA R 1, R 2, R 3, R 4, #100 #5 #40 R 1, R 2, R 3 R 1 = 0 x 54000000 R 2 = 0 x 10000002 0 x 54000000 × 0 x 10000002 = 0 x 054000000 A 8000000 R 3 = 0 x. A 8000000, the lower 32 bits R 4 = 0 x 05400000, the higher 32 bits ; Rd = Rm × Rs + Rn ; ; R 1 R 2 R 3 R 4 = = 100 5 40 R 1 × R 2 + R 3 = 100 × 5 + 40 = 540 10

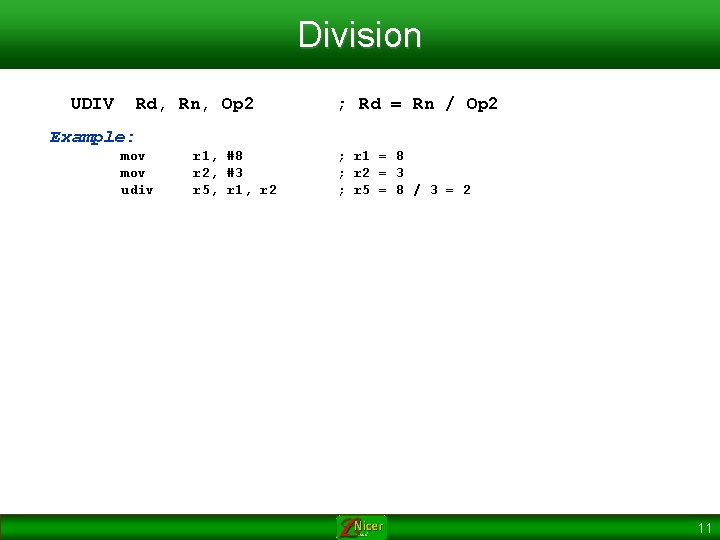

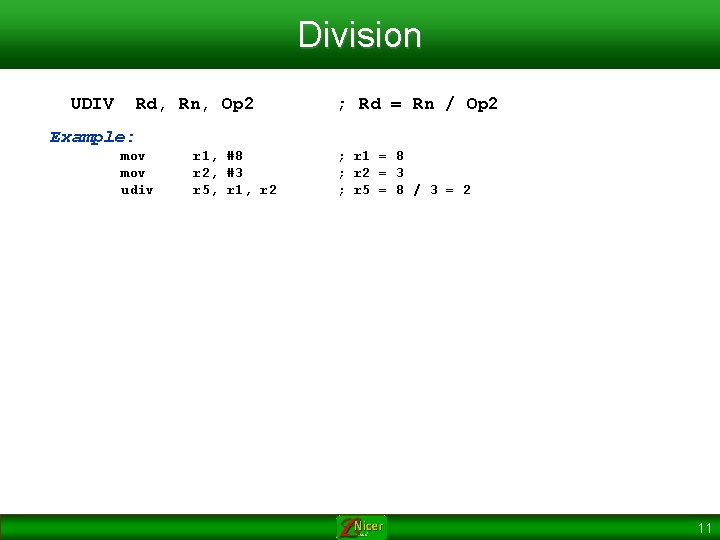

Division UDIV Rd, Rn, Op 2 ; Rd = Rn / Op 2 Example: mov udiv r 1, #8 r 2, #3 r 5, r 1, r 2 ; r 1 = 8 ; r 2 = 3 ; r 5 = 8 / 3 = 2 11

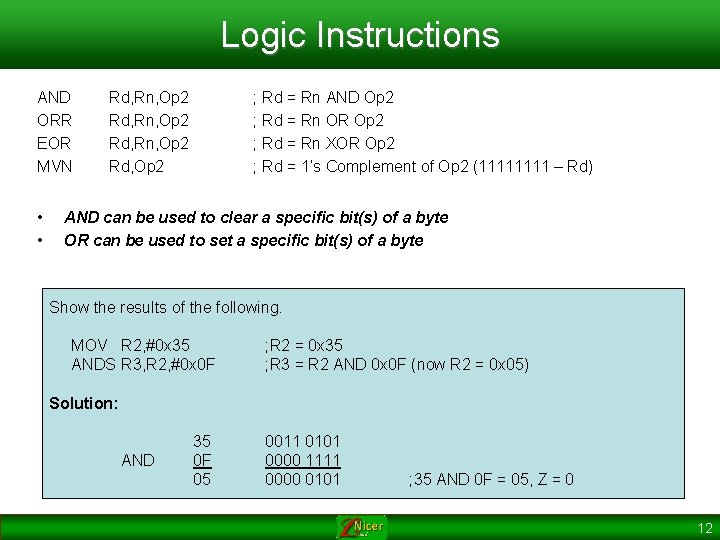

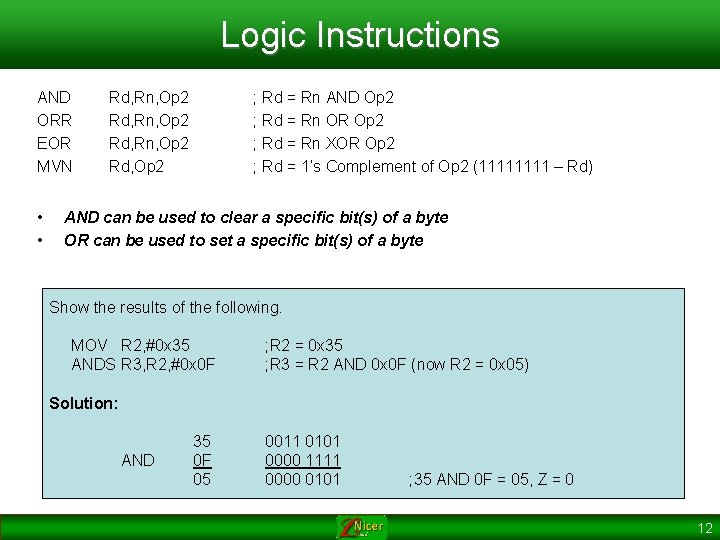

Logic Instructions AND ORR EOR MVN • • Rd, Rn, Op 2 Rd, Op 2 ; Rd = Rn AND Op 2 ; Rd = Rn OR Op 2 ; Rd = Rn XOR Op 2 ; Rd = 1’s Complement of Op 2 (1111 – Rd) AND can be used to clear a specific bit(s) of a byte OR can be used to set a specific bit(s) of a byte Show the results of the following. MOV R 2, #0 x 35 ANDS R 3, R 2, #0 x 0 F ; R 2 = 0 x 35 ; R 3 = R 2 AND 0 x 0 F (now R 2 = 0 x 05) Solution: AND 35 0 F 05 0011 0101 0000 1111 0000 0101 ; 35 AND 0 F = 05, Z = 0 12

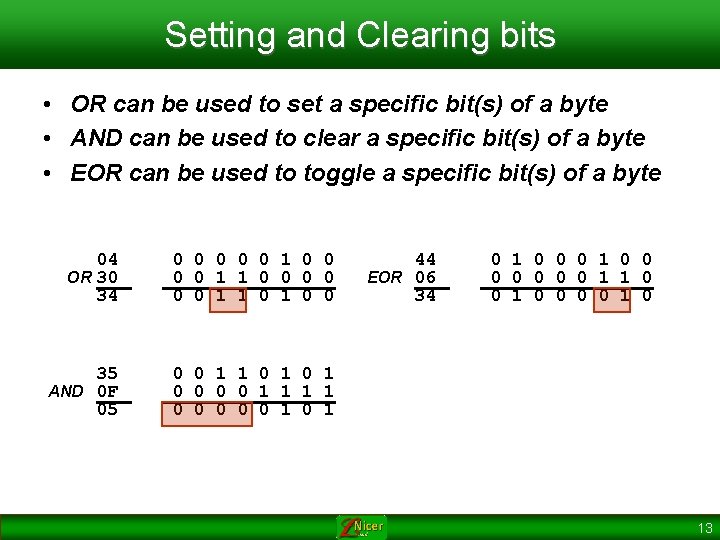

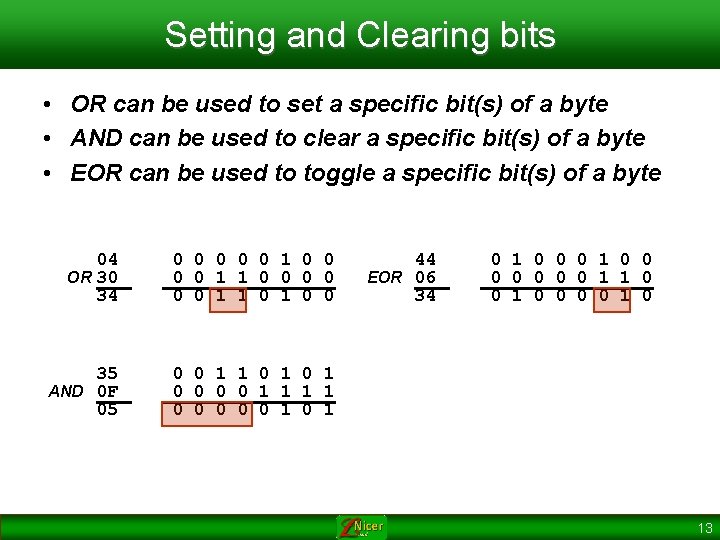

Setting and Clearing bits • OR can be used to set a specific bit(s) of a byte • AND can be used to clear a specific bit(s) of a byte • EOR can be used to toggle a specific bit(s) of a byte 04 OR 30 34 0 0 0 1 1 0 0 0 1 1 0 0 35 AND 0 F 05 0 0 1 1 0 1 0 0 1 1 0 0 0 1 44 EOR 06 34 0 1 0 0 0 0 0 1 1 0 0 0 0 13

Rotate and Shift Instructions 14

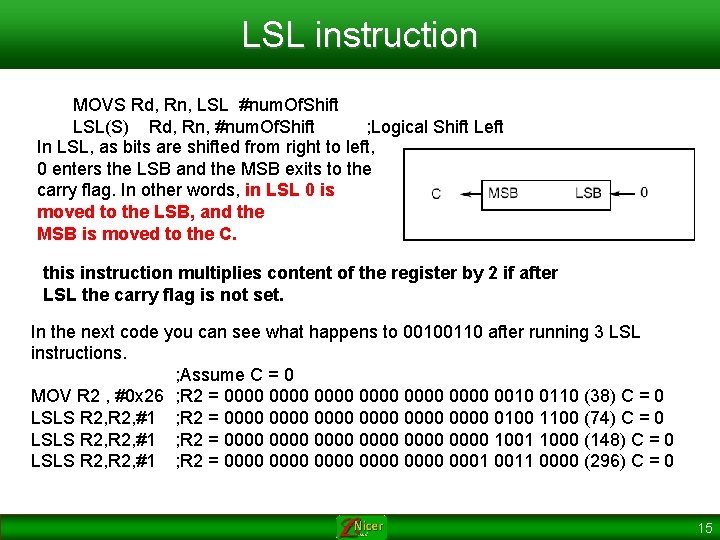

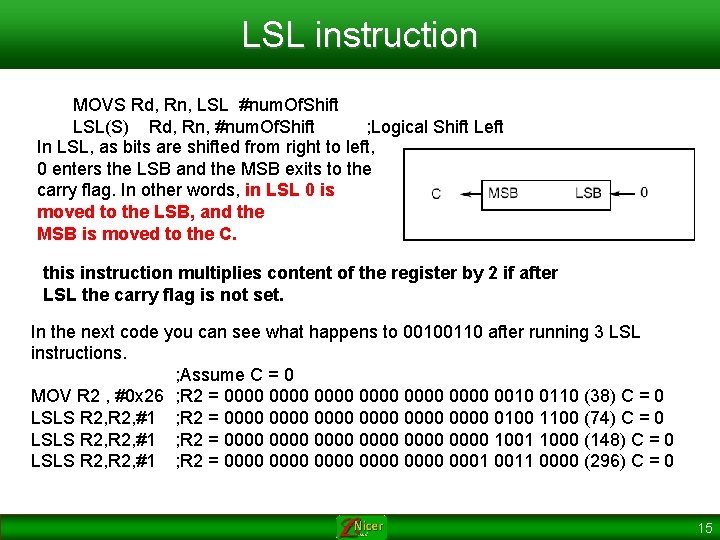

LSL instruction MOVS Rd, Rn, LSL #num. Of. Shift LSL(S) Rd, Rn, #num. Of. Shift ; Logical Shift Left In LSL, as bits are shifted from right to left, 0 enters the LSB and the MSB exits to the carry flag. In other words, in LSL 0 is moved to the LSB, and the MSB is moved to the C. this instruction multiplies content of the register by 2 if after LSL the carry flag is not set. In the next code you can see what happens to 00100110 after running 3 LSL instructions. ; Assume C = 0 MOV R 2 , #0 x 26 ; R 2 = 0000 0000 0010 0110 (38) C = 0 LSLS R 2, #1 ; R 2 = 0000 0000 0100 1100 (74) C = 0 LSLS R 2, #1 ; R 2 = 0000 0000 1001 1000 (148) C = 0 LSLS R 2, #1 ; R 2 = 0000 0000 0001 0011 0000 (296) C = 0 15

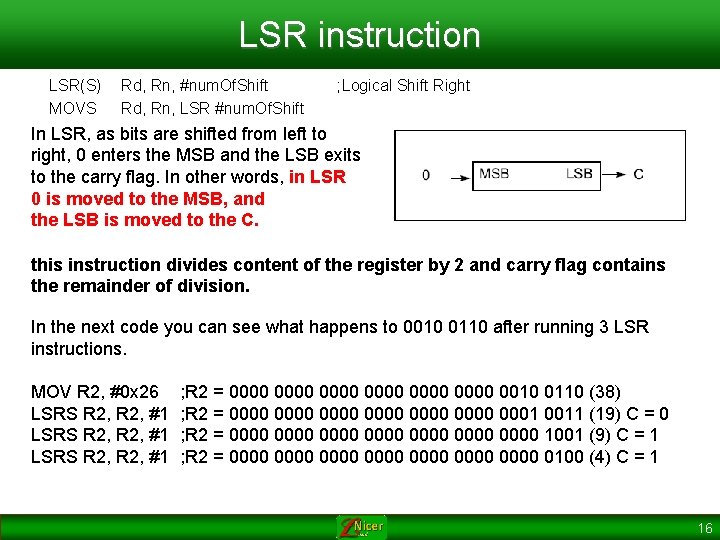

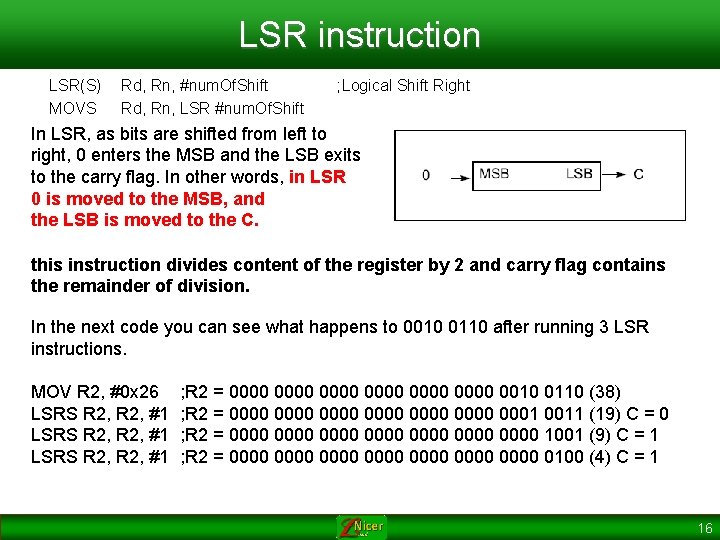

LSR instruction LSR(S) MOVS Rd, Rn, #num. Of. Shift Rd, Rn, LSR #num. Of. Shift ; Logical Shift Right In LSR, as bits are shifted from left to right, 0 enters the MSB and the LSB exits to the carry flag. In other words, in LSR 0 is moved to the MSB, and the LSB is moved to the C. this instruction divides content of the register by 2 and carry flag contains the remainder of division. In the next code you can see what happens to 0010 0110 after running 3 LSR instructions. MOV R 2, #0 x 26 LSRS R 2, #1 LSRS R 2, #1 ; R 2 = 0000 0000 0010 0110 (38) ; R 2 = 0000 0000 0001 0011 (19) C = 0 ; R 2 = 0000 0000 1001 (9) C = 1 ; R 2 = 0000 0000 0100 (4) C = 1 16

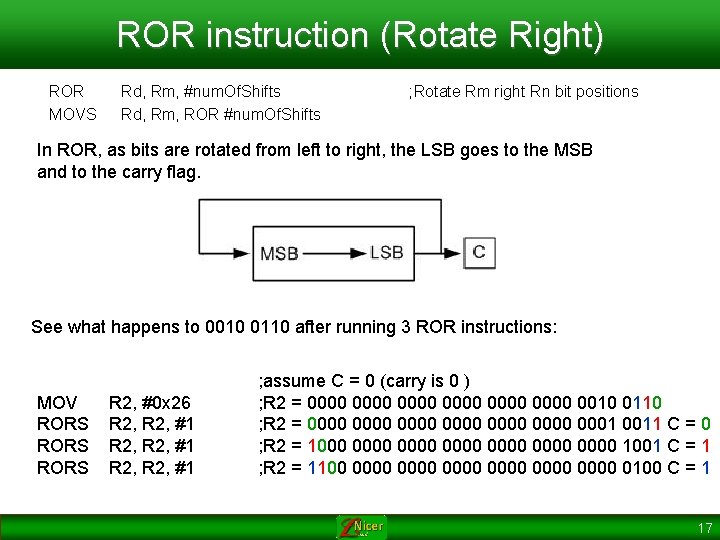

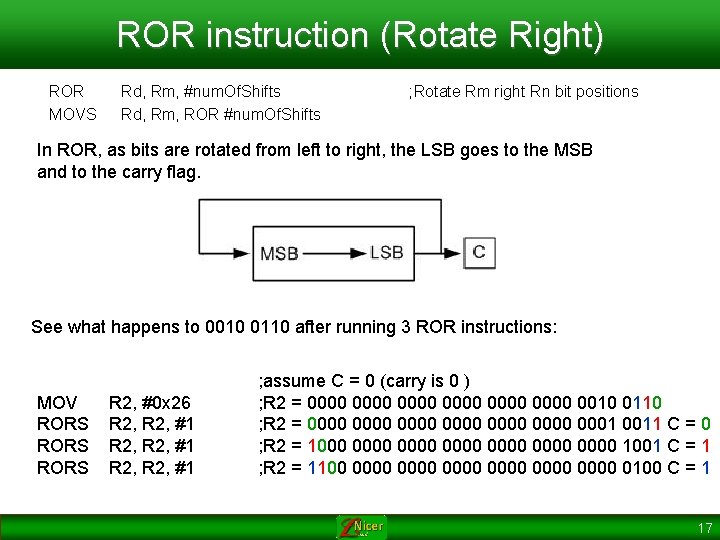

ROR instruction (Rotate Right) ROR MOVS Rd, Rm, #num. Of. Shifts Rd, Rm, ROR #num. Of. Shifts ; Rotate Rm right Rn bit positions In ROR, as bits are rotated from left to right, the LSB goes to the MSB and to the carry flag. See what happens to 0010 0110 after running 3 ROR instructions: MOV RORS R 2, #0 x 26 R 2, #1 R 2, #1 ; assume C = 0 (carry is 0 ) ; R 2 = 0000 0000 0010 0110 ; R 2 = 0000 0000 0001 0011 C = 0 ; R 2 = 1000 0000 0000 1001 C = 1 ; R 2 = 1100 0000 0000 0100 C = 1 17

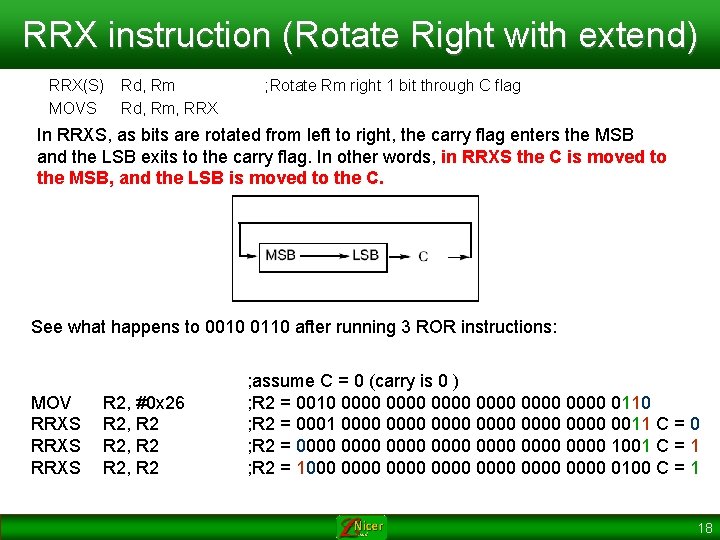

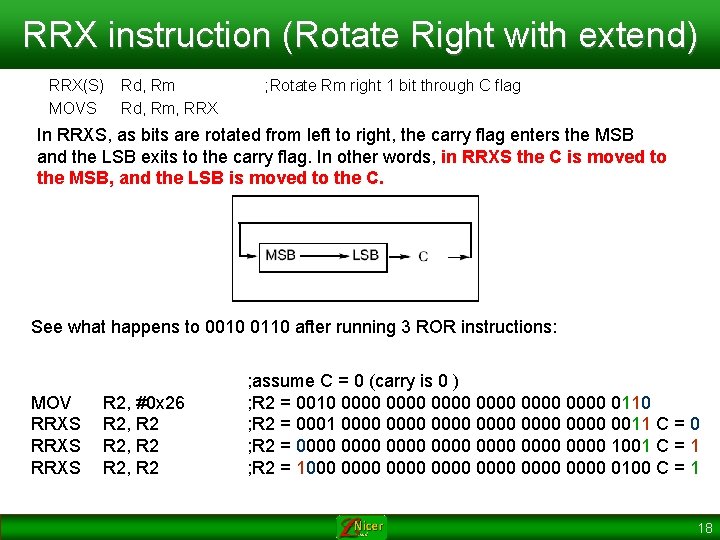

RRX instruction (Rotate Right with extend) RRX(S) MOVS Rd, Rm, RRX ; Rotate Rm right 1 bit through C flag In RRXS, as bits are rotated from left to right, the carry flag enters the MSB and the LSB exits to the carry flag. In other words, in RRXS the C is moved to the MSB, and the LSB is moved to the C. See what happens to 0010 0110 after running 3 ROR instructions: MOV RRXS R 2, #0 x 26 R 2, R 2 ; assume C = 0 (carry is 0 ) ; R 2 = 0010 0000 0000 0110 ; R 2 = 0001 0000 0000 0011 C = 0 ; R 2 = 0000 0000 1001 C = 1 ; R 2 = 1000 0000 0000 0100 C = 1 18

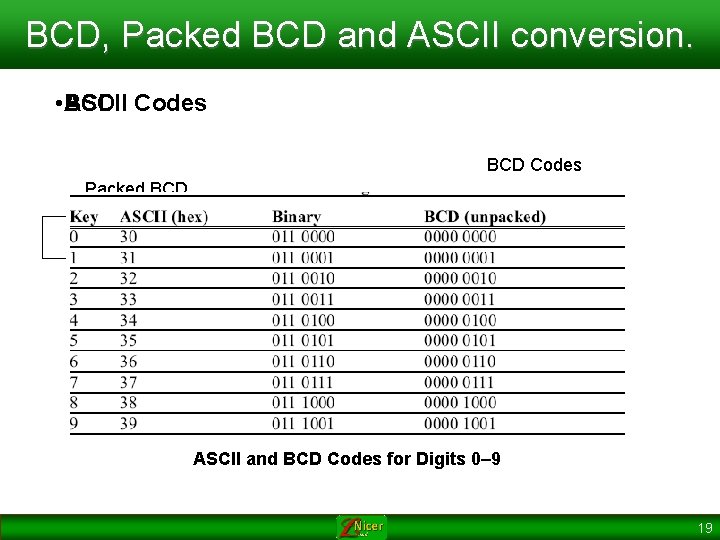

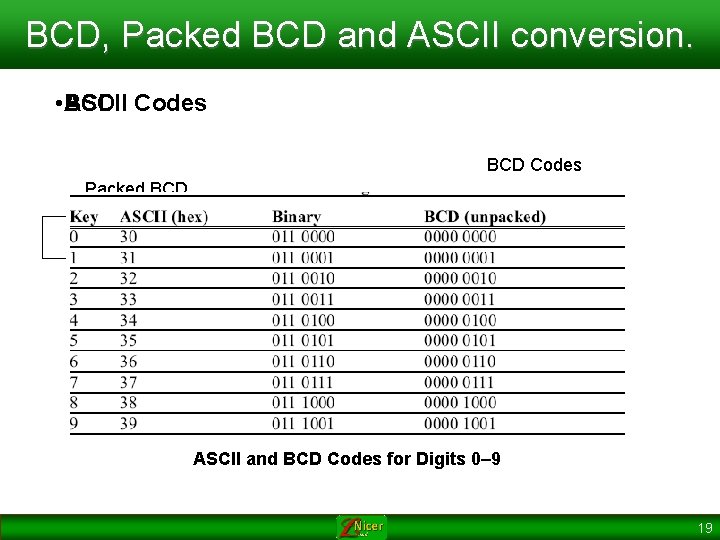

BCD, Packed BCD and ASCII conversion. • ASCII BCD Codes Packed BCD 1 BCD 0 ASCII and BCD Codes for Digits 0– 9 19

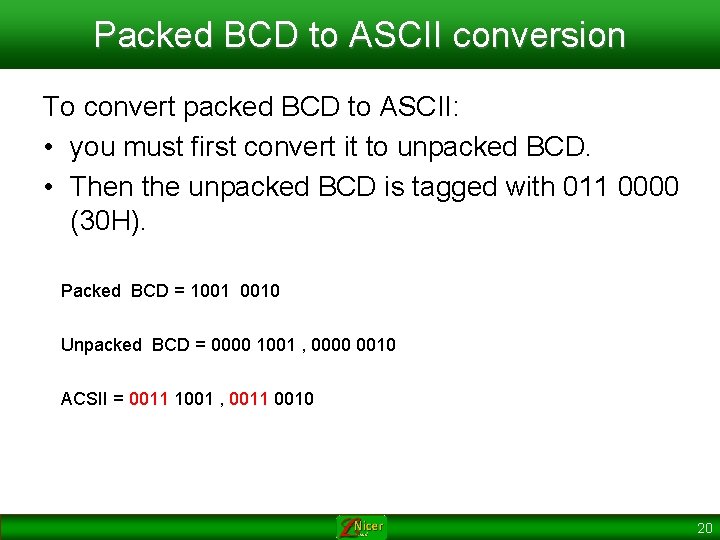

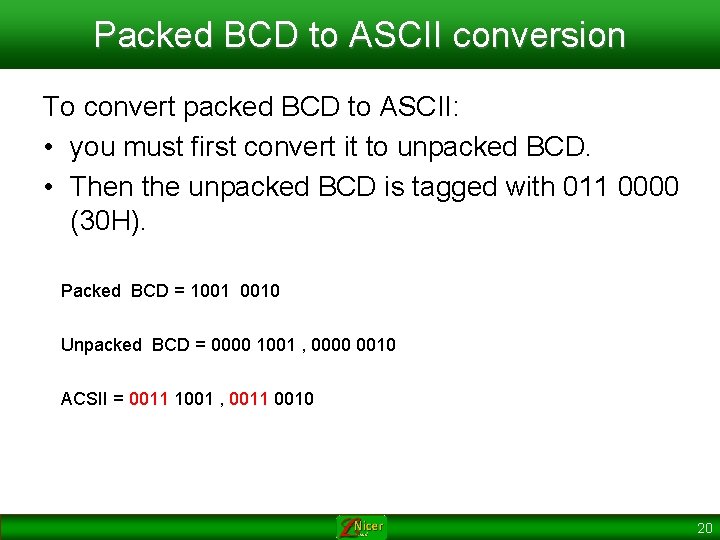

Packed BCD to ASCII conversion To convert packed BCD to ASCII: • you must first convert it to unpacked BCD. • Then the unpacked BCD is tagged with 011 0000 (30 H). Packed BCD = 1001 0010 Unpacked BCD = 0000 1001 , 0000 0010 ACSII = 0011 1001 , 0011 0010 20