ARHITEKTURA RAUNARA Opti izgled arhitekture raunara CPU Komunikacije

- Slides: 62

ARHITEKTURA RAČUNARA

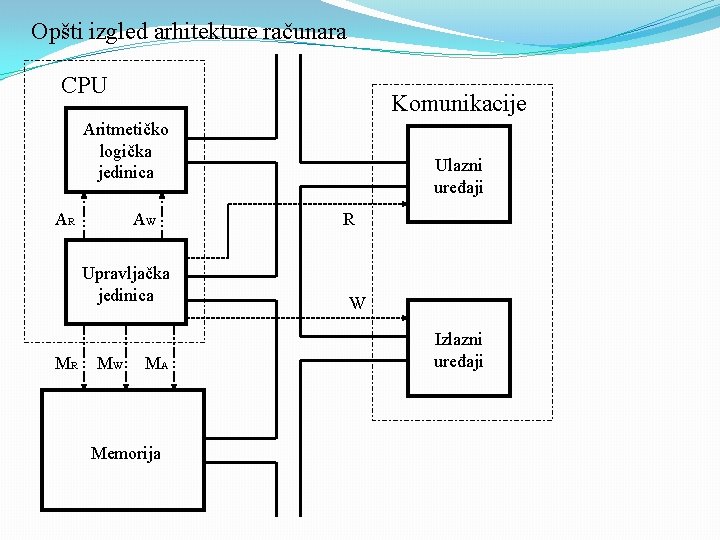

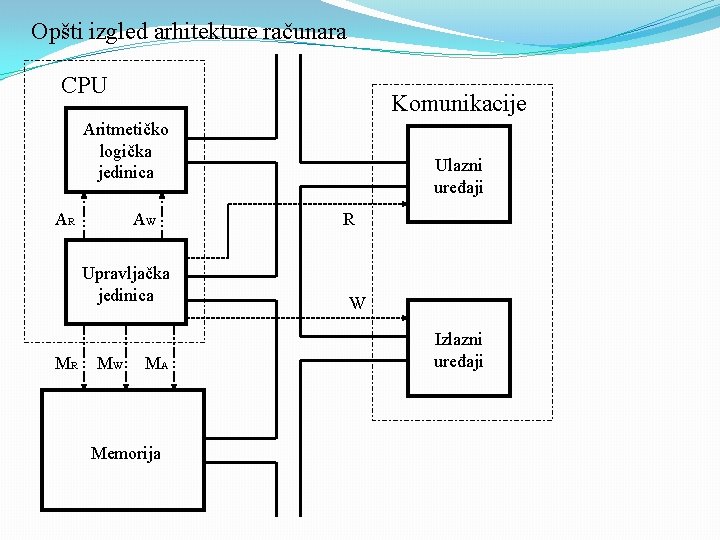

Opšti izgled arhitekture računara CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

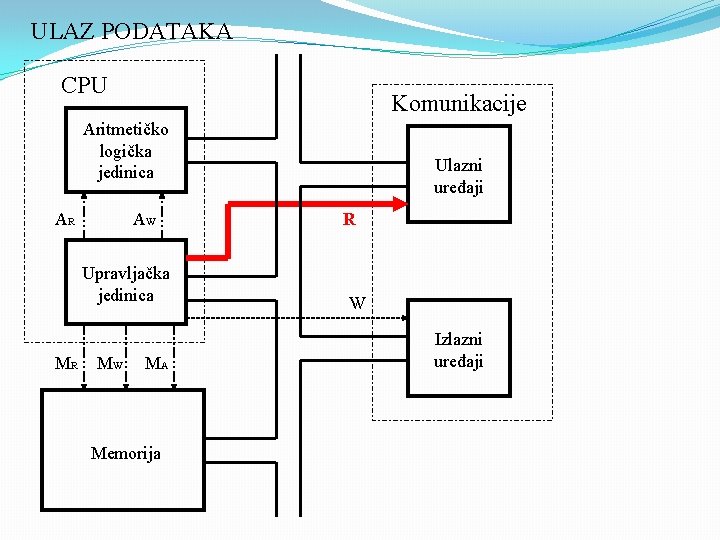

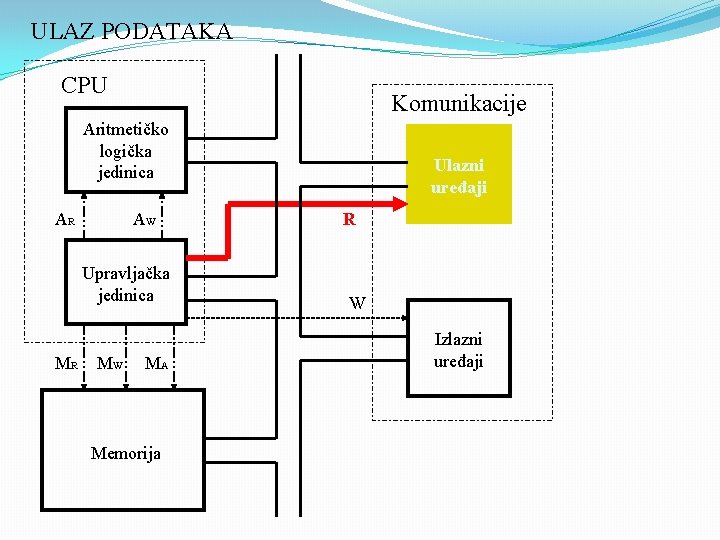

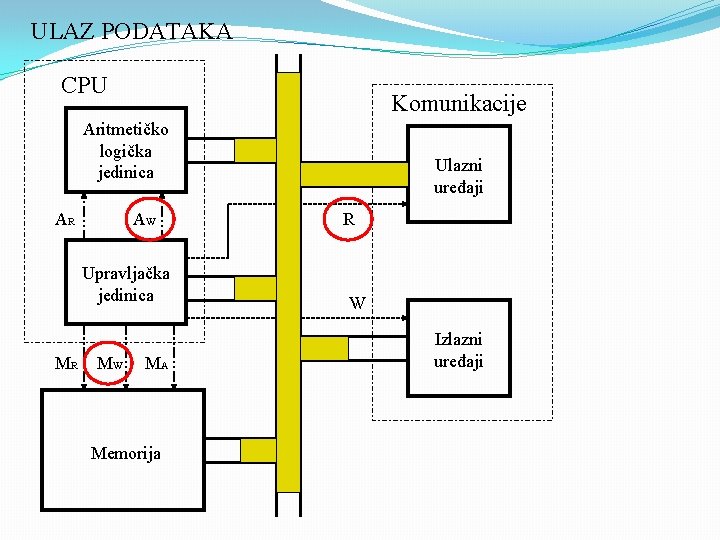

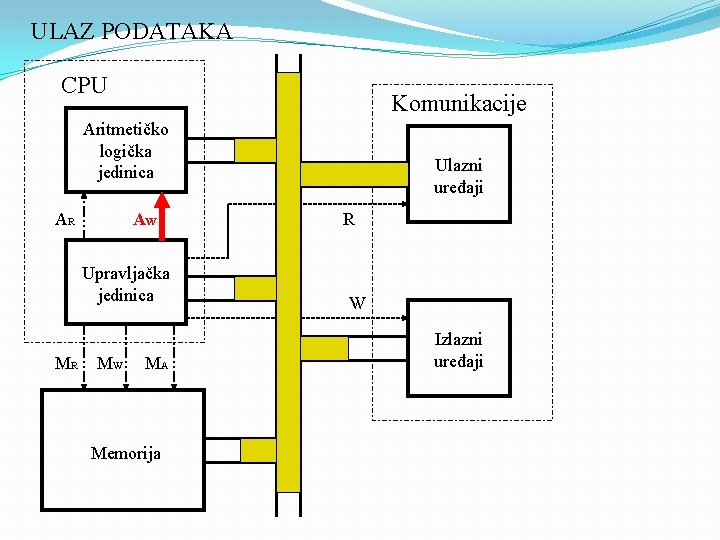

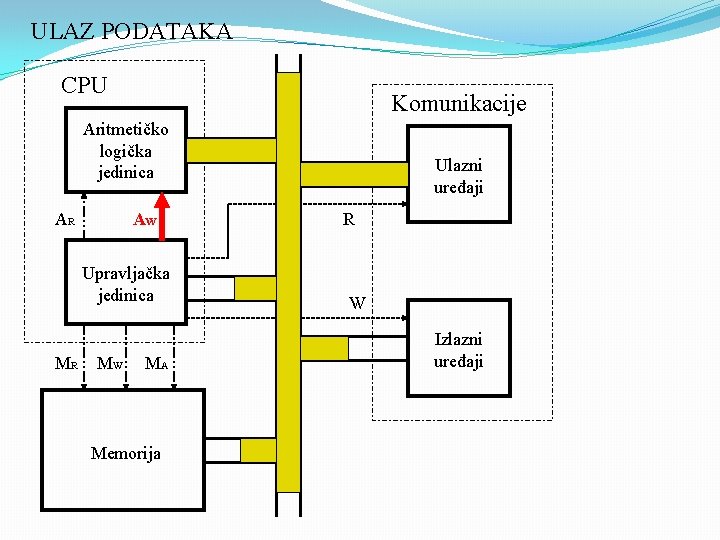

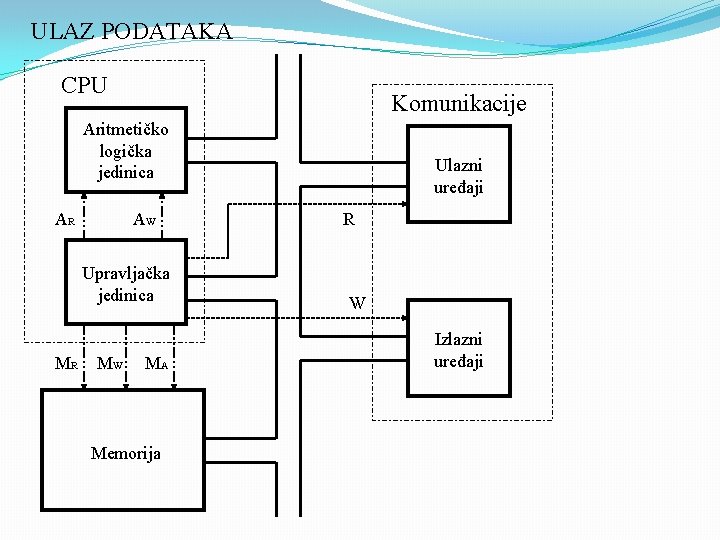

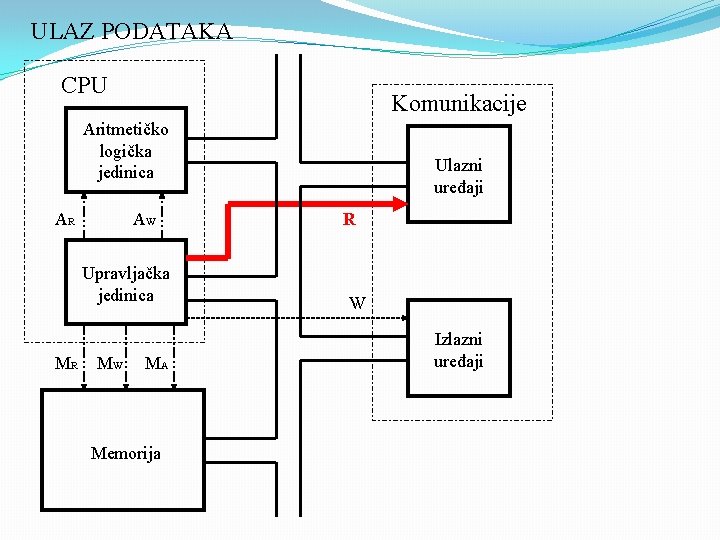

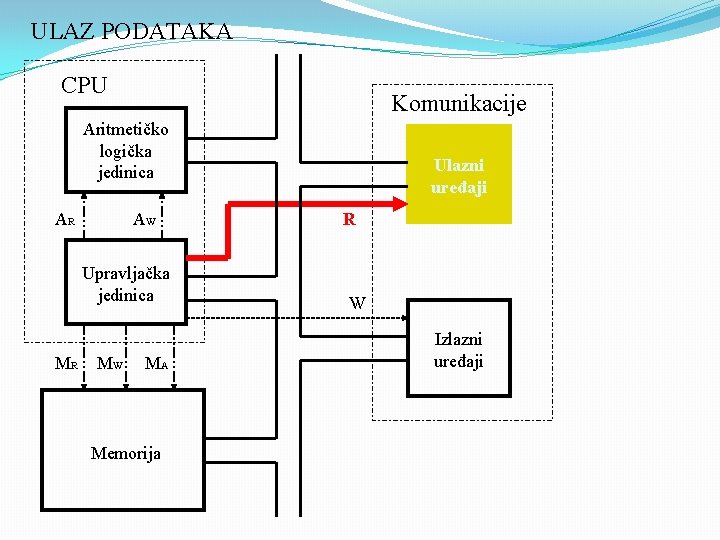

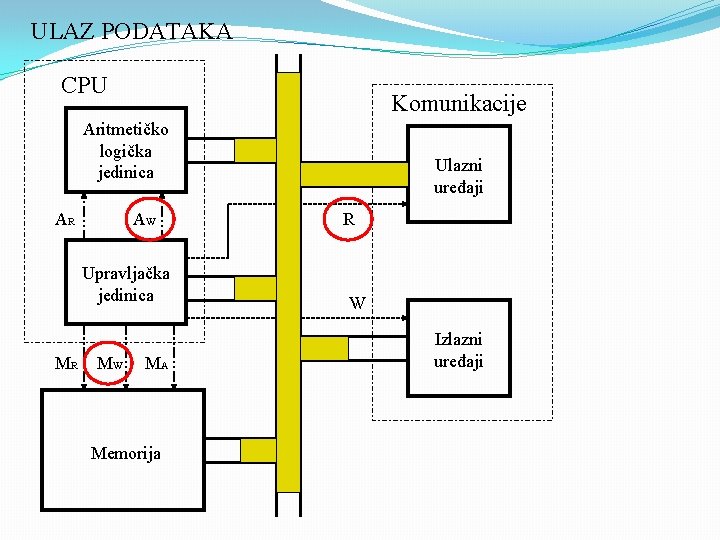

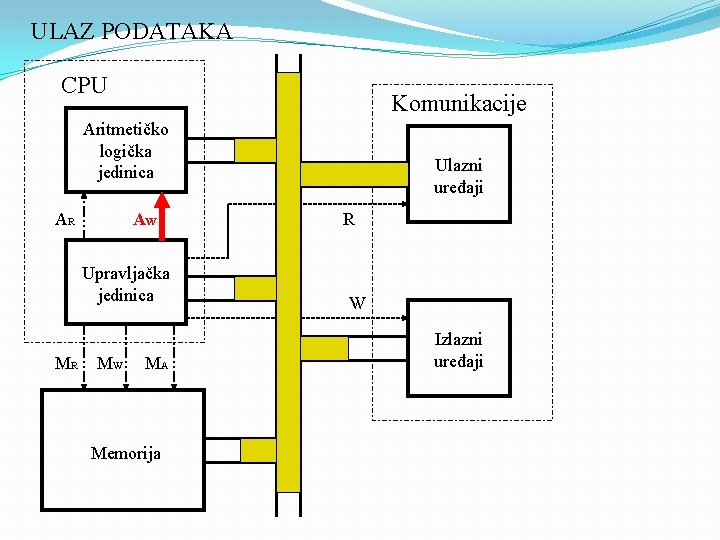

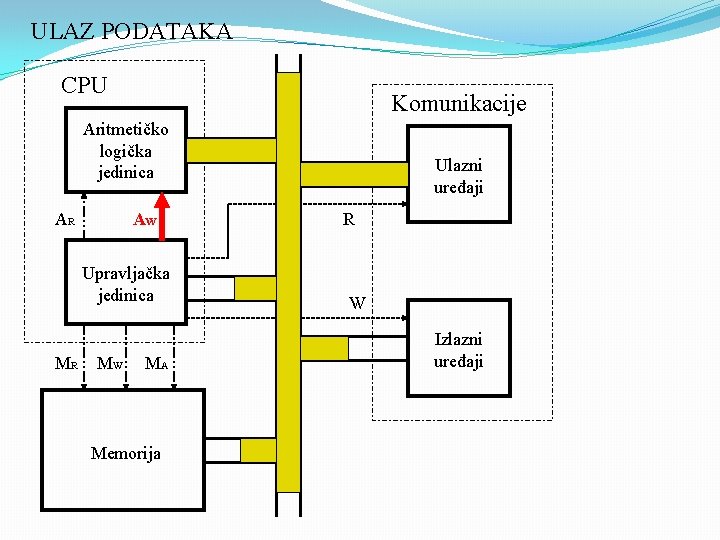

ULAZ PODATAKA

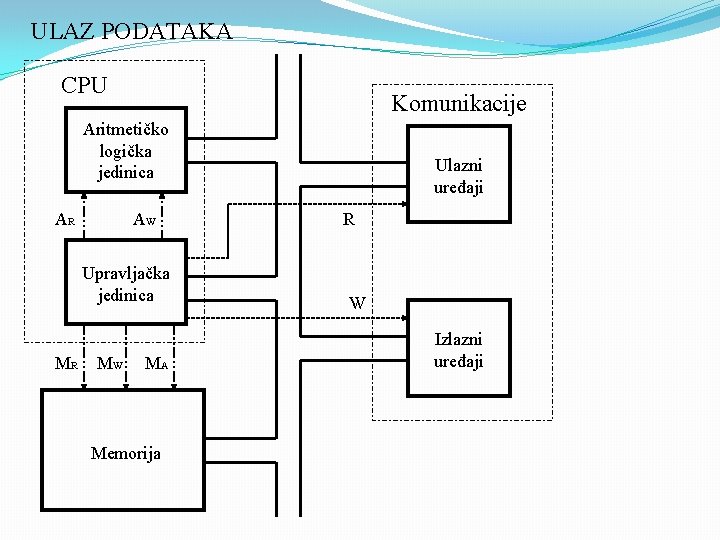

ULAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

ULAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

ULAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

ULAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

ULAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

ULAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

ULAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

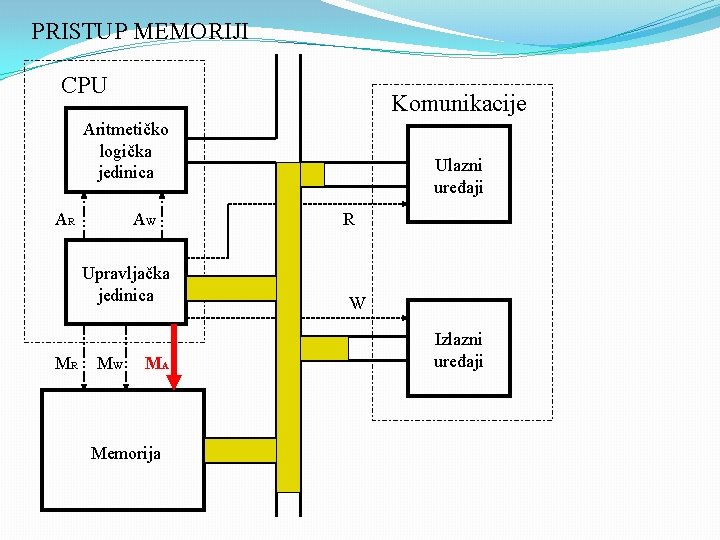

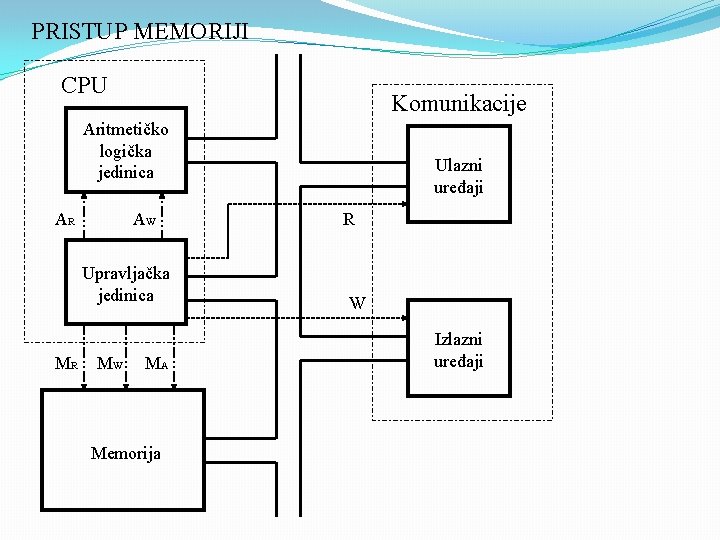

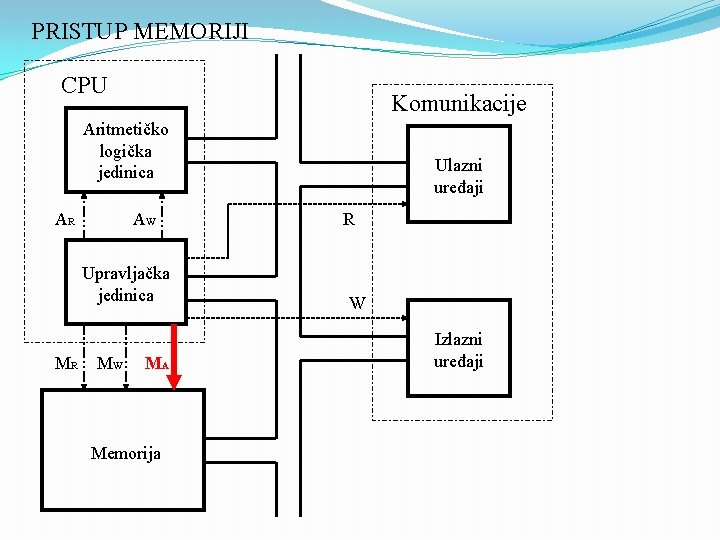

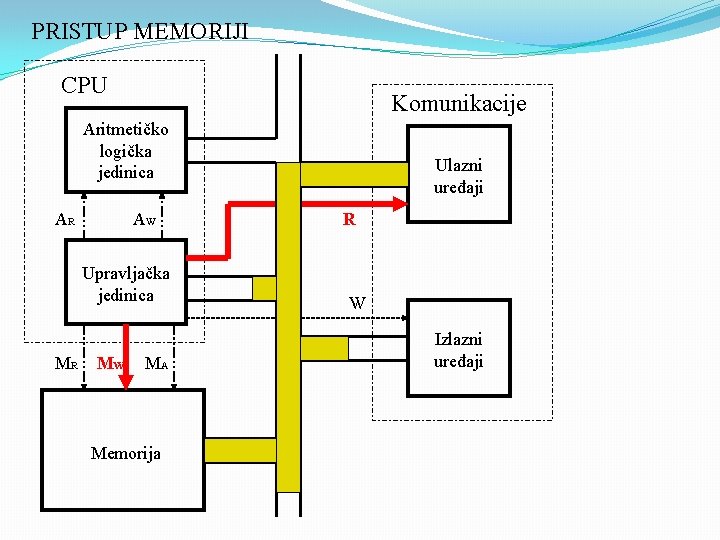

PRISTUP MEMORIJI

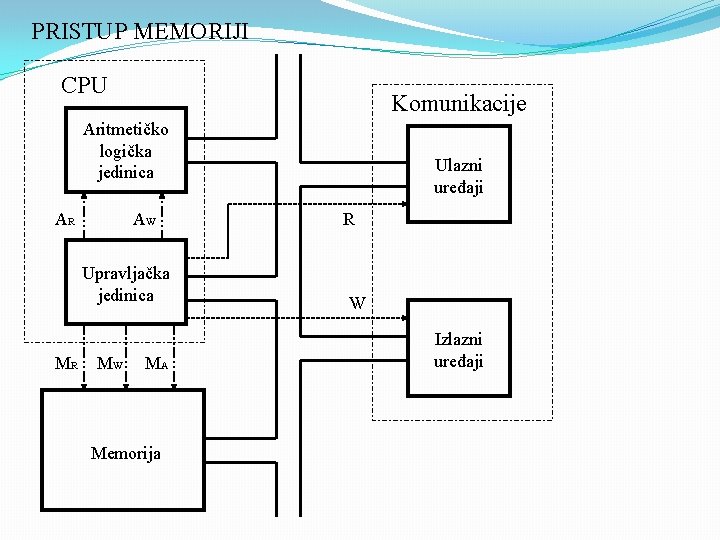

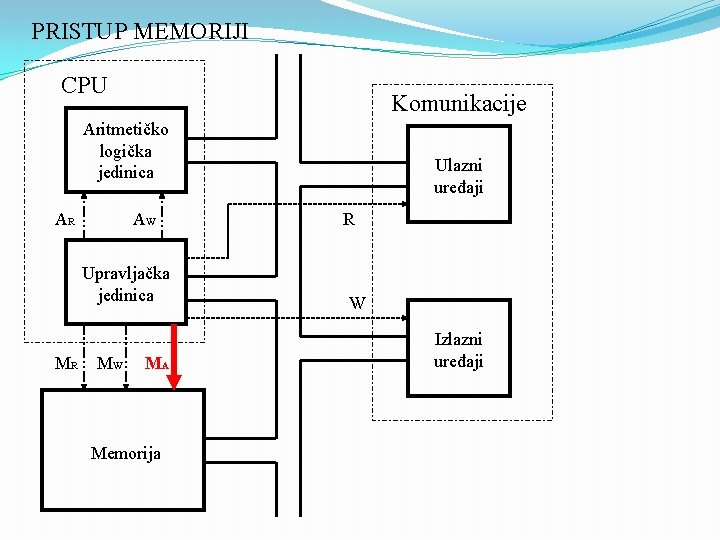

PRISTUP MEMORIJI CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

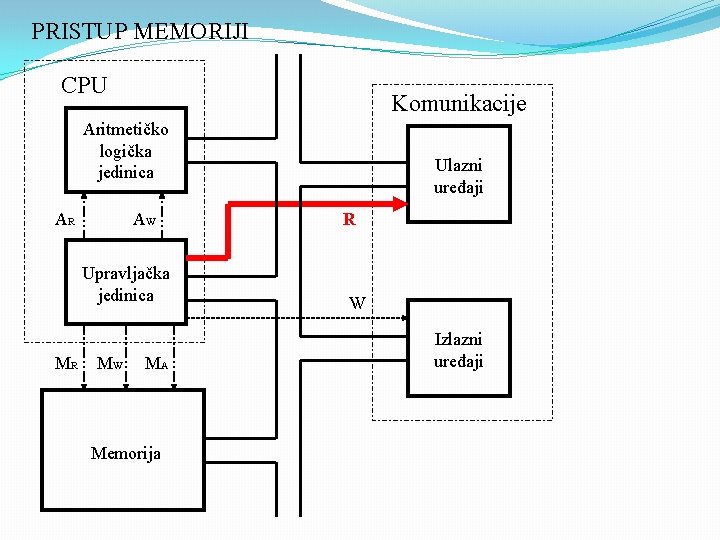

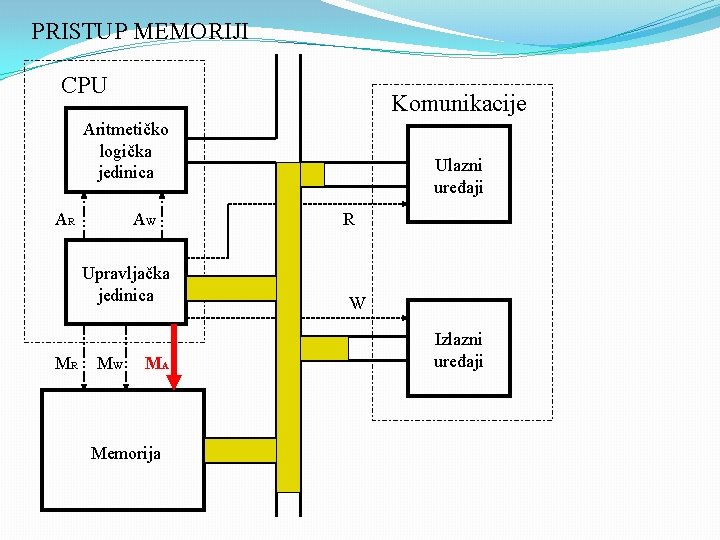

PRISTUP MEMORIJI CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

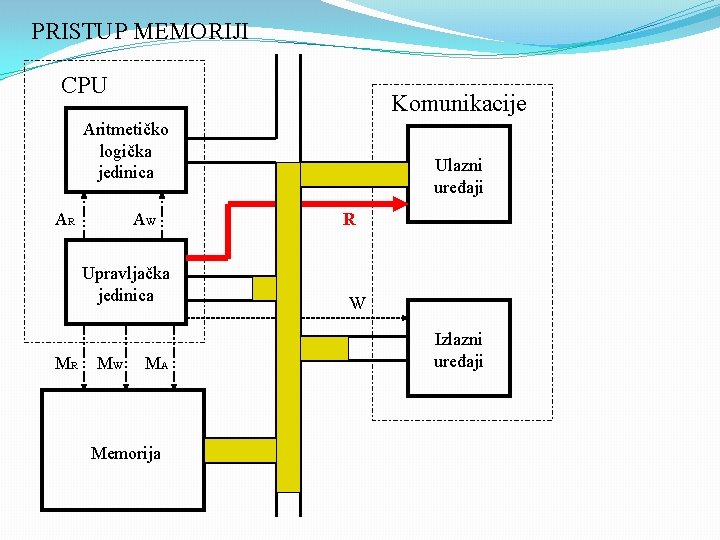

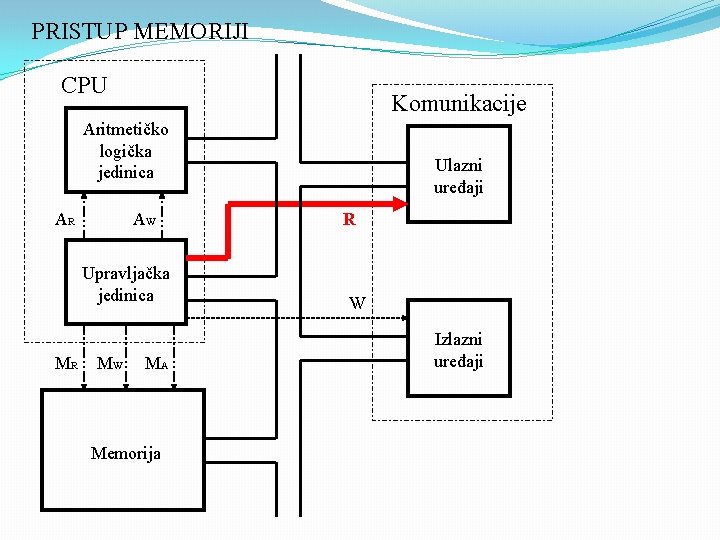

PRISTUP MEMORIJI CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

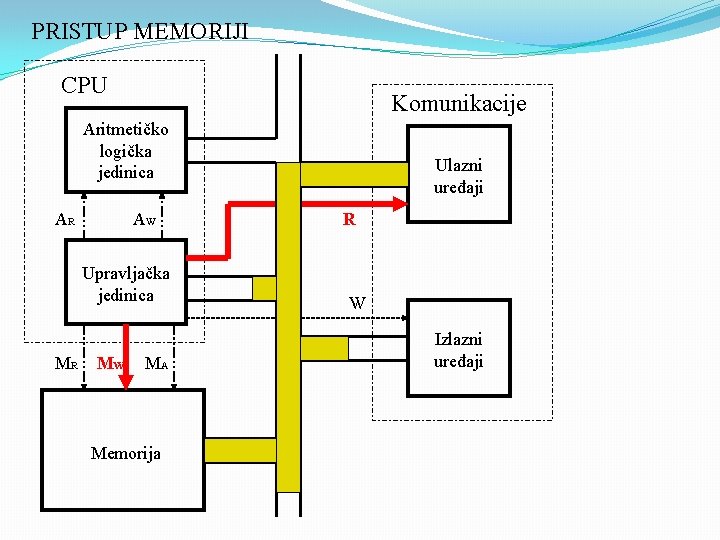

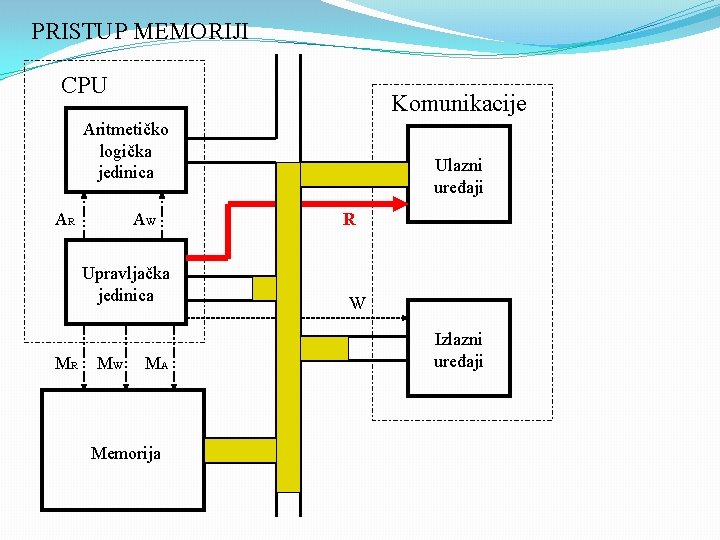

PRISTUP MEMORIJI CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

PRISTUP MEMORIJI CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

PRISTUP MEMORIJI CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

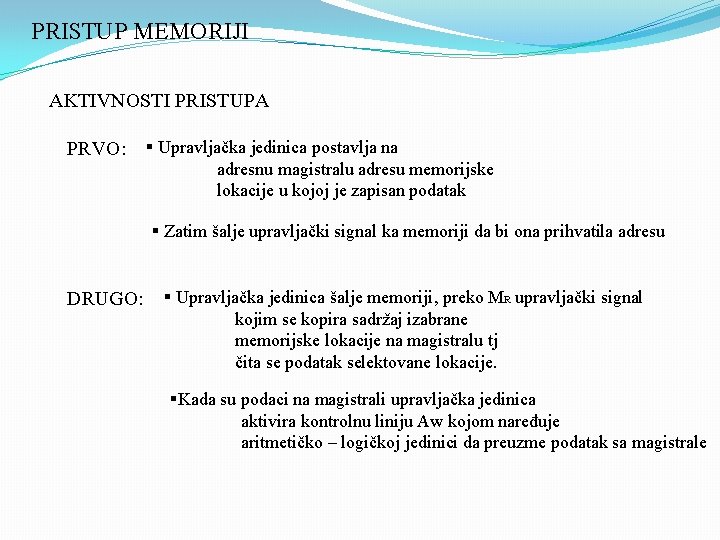

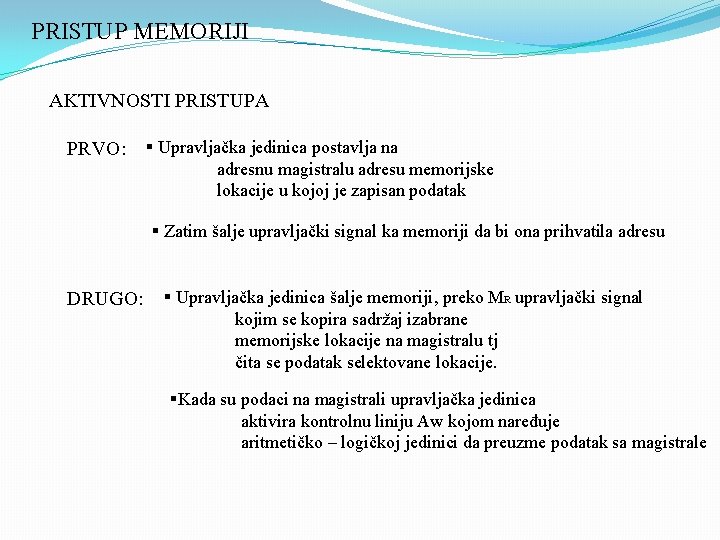

PRISTUP MEMORIJI AKTIVNOSTI PRISTUPA PRVO: § Upravljačka jedinica postavlja na adresnu magistralu adresu memorijske lokacije u kojoj je zapisan podatak § Zatim šalje upravljački signal ka memoriji da bi ona prihvatila adresu DRUGO: § Upravljačka jedinica šalje memoriji, preko MR upravljački signal kojim se kopira sadržaj izabrane memorijske lokacije na magistralu tj čita se podatak selektovane lokacije. §Kada su podaci na magistrali upravljačka jedinica aktivira kontrolnu liniju Aw kojom naređuje aritmetičko – logičkoj jedinici da preuzme podatak sa magistrale

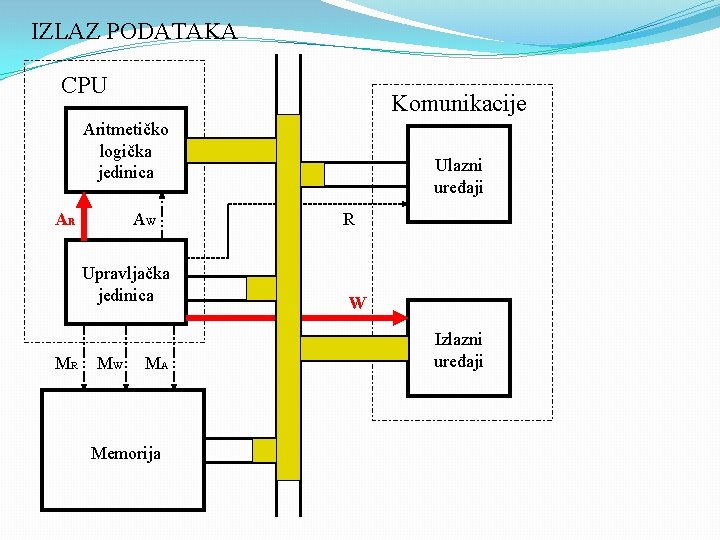

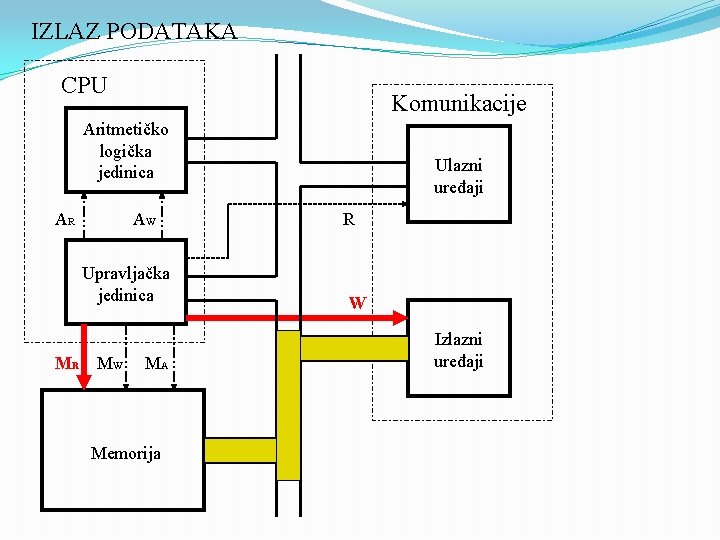

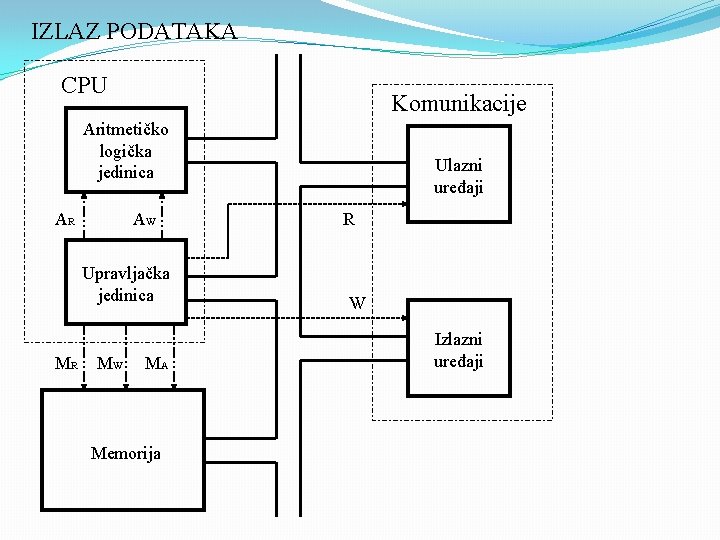

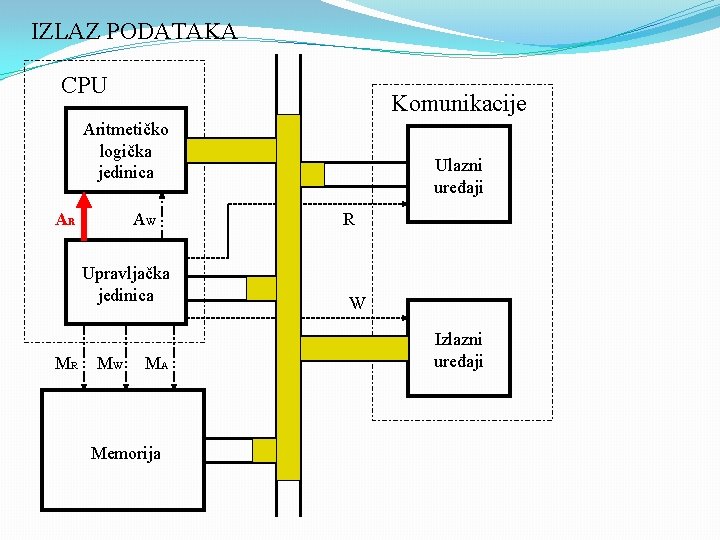

IZLAZ PODATAKA

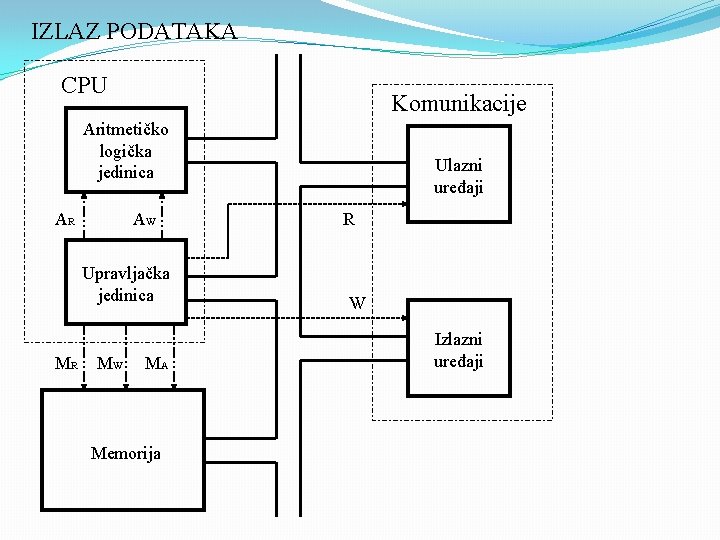

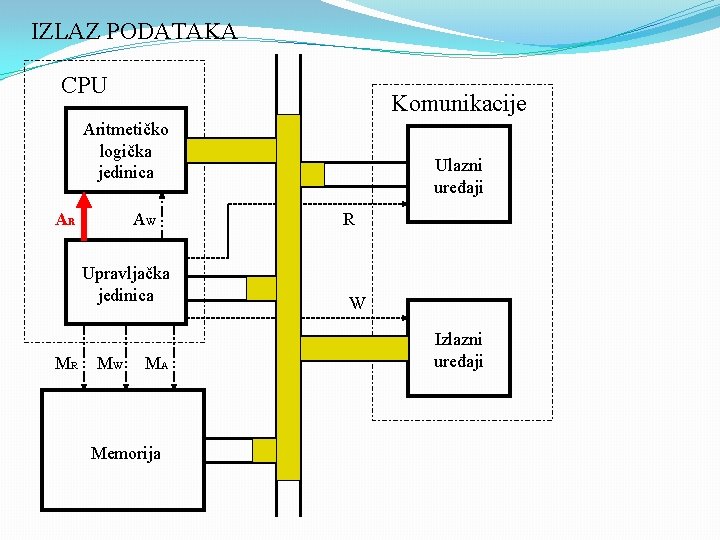

IZLAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

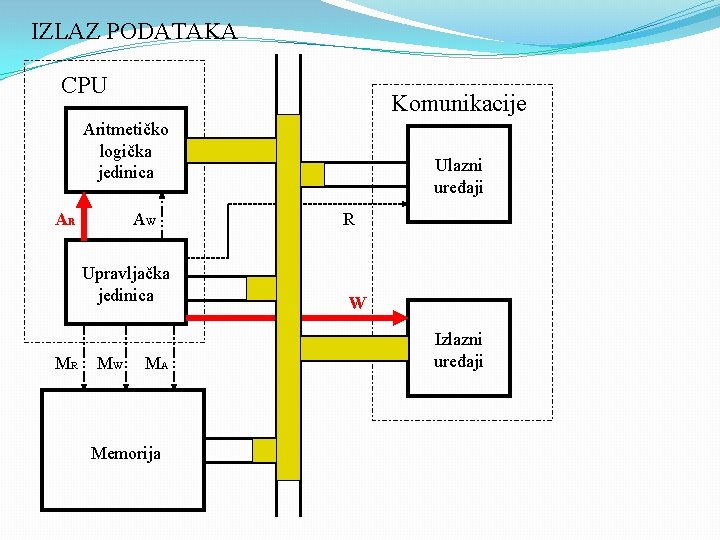

IZLAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

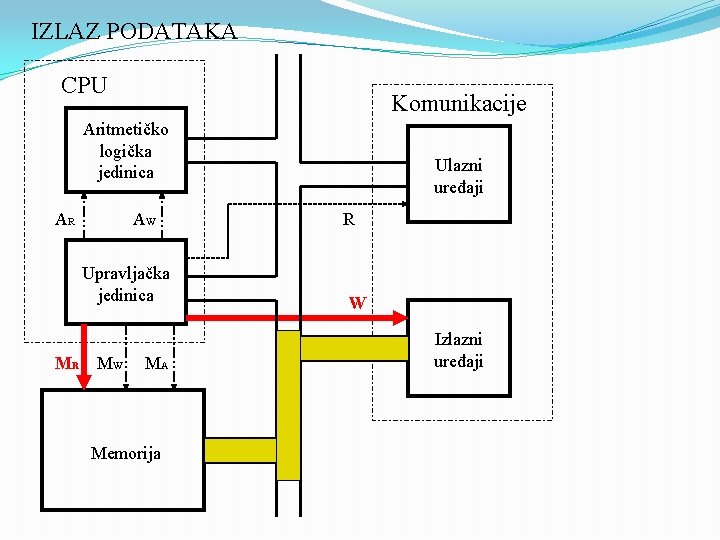

IZLAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

IZLAZ PODATAKA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica M R MW MA Memorija Ulazni uređaji R W Izlazni uređaji

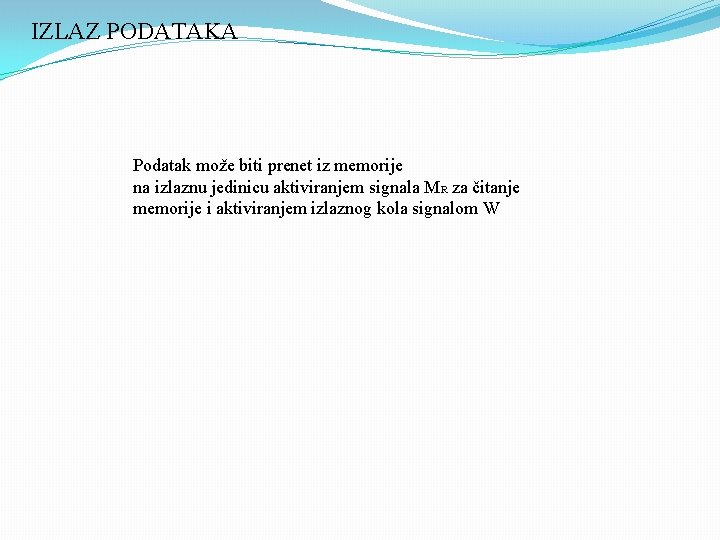

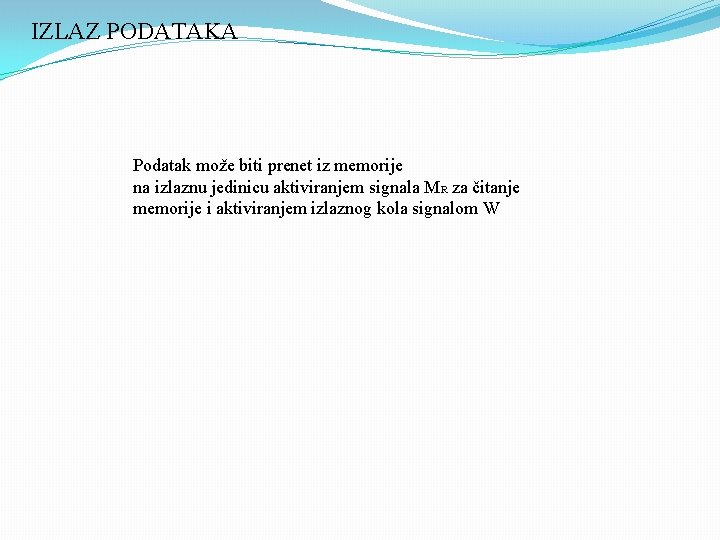

IZLAZ PODATAKA Podatak može biti prenet iz memorije na izlaznu jedinicu aktiviranjem signala MR za čitanje memorije i aktiviranjem izlaznog kola signalom W

P R I B A V Lj A Nj E INSTRUKCIJA

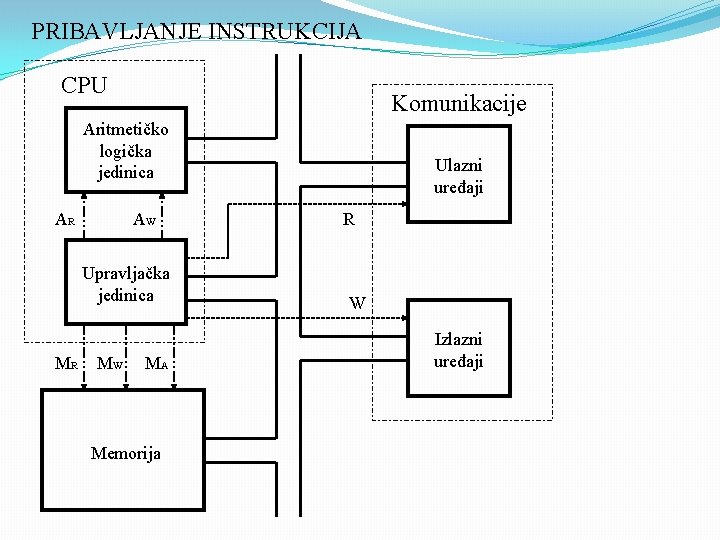

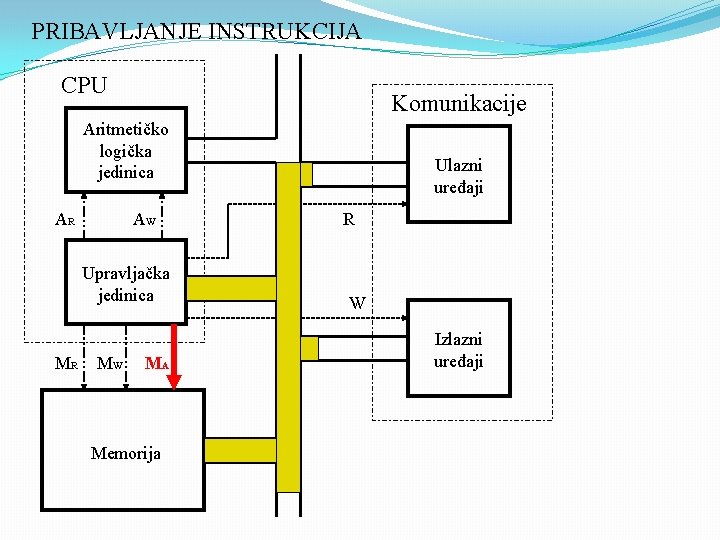

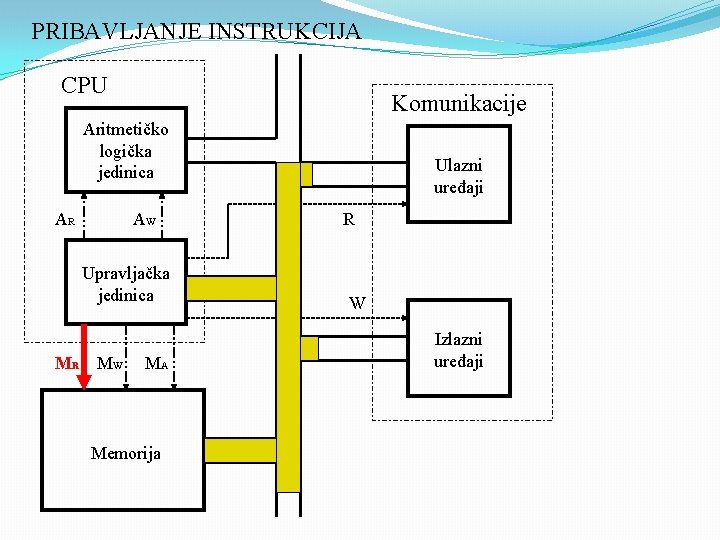

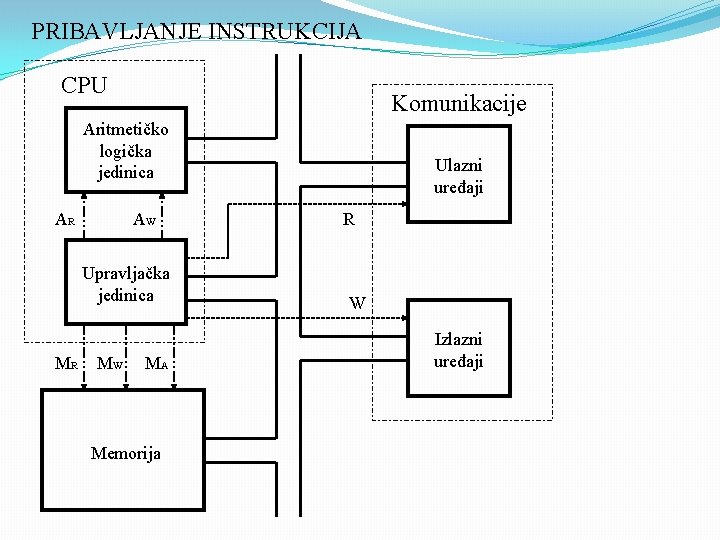

PRIBAVLJANJE INSTRUKCIJA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

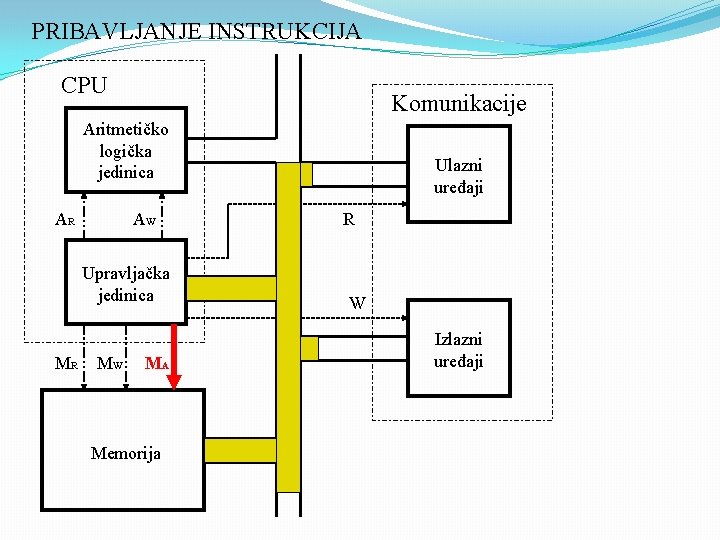

PRIBAVLJANJE INSTRUKCIJA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica MR MW MA Memorija Ulazni uređaji R W Izlazni uređaji

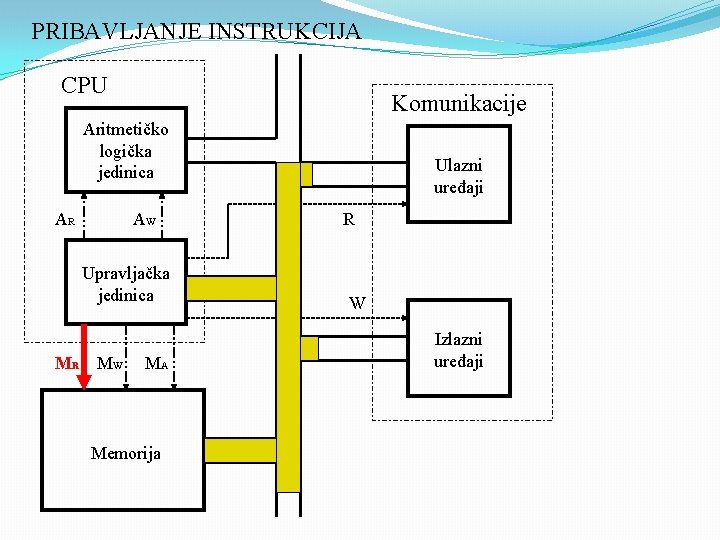

PRIBAVLJANJE INSTRUKCIJA CPU Komunikacije Aritmetičko logička jedinica AR AW Upravljačka jedinica M R MW MA Memorija Ulazni uređaji R W Izlazni uređaji

PRIBAVLJANJE INSTRUKCIJA §Upravljačka jedinica memoriji šalje adresu lokacije na kojoj se nalazi instrukcija §Postaljanjem željene lokacije, upravljačka jedinica zahteva od memorije da kopira sadržaj te lokacije (instrukciju) na magistralu

F A Z A P R I B A V LJ A NJ A MAŠINSKIH INSTRUKCIJA

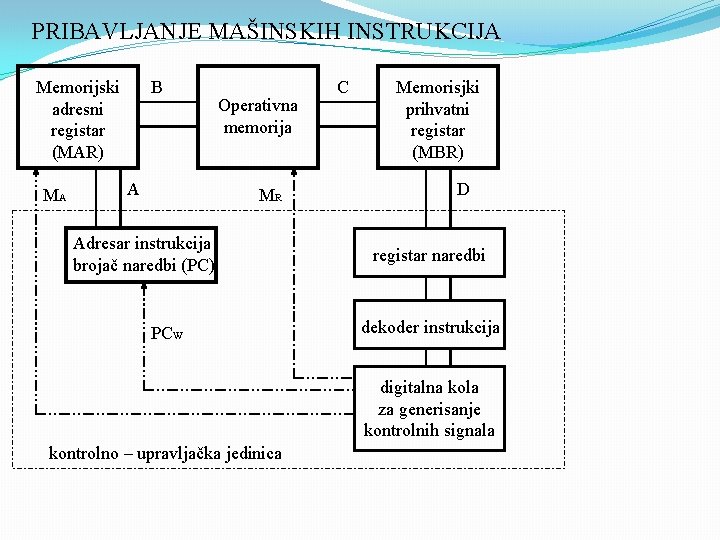

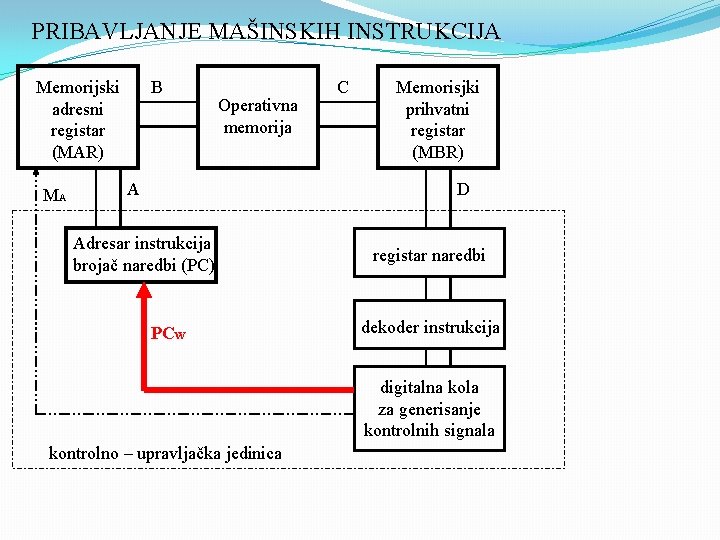

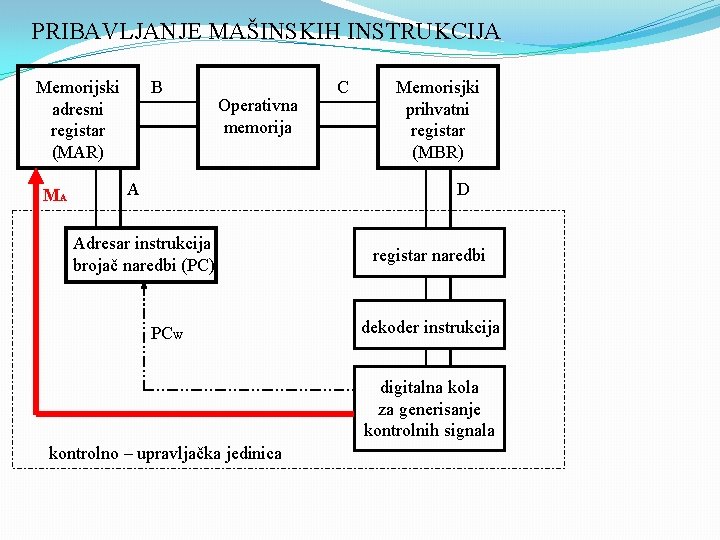

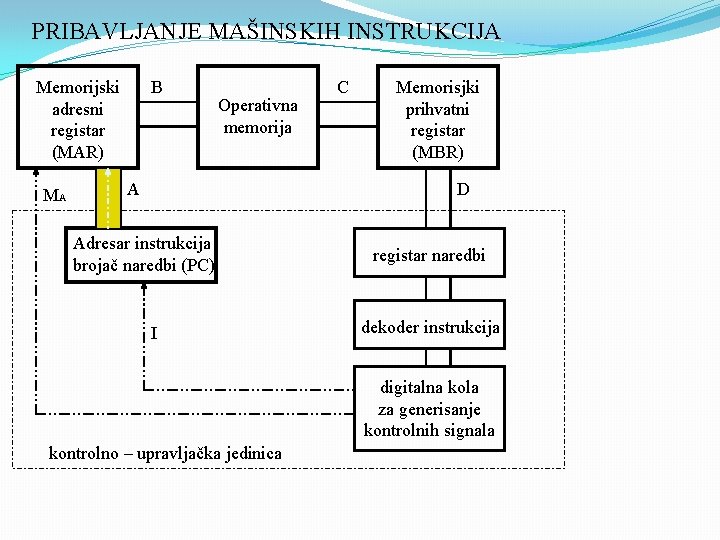

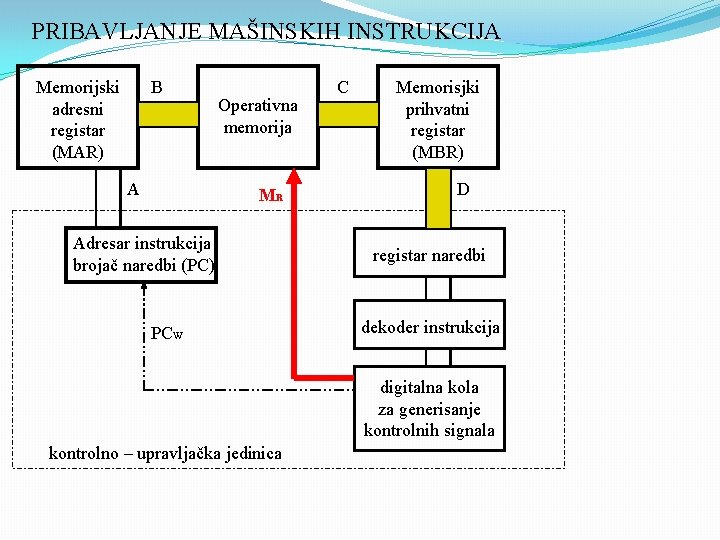

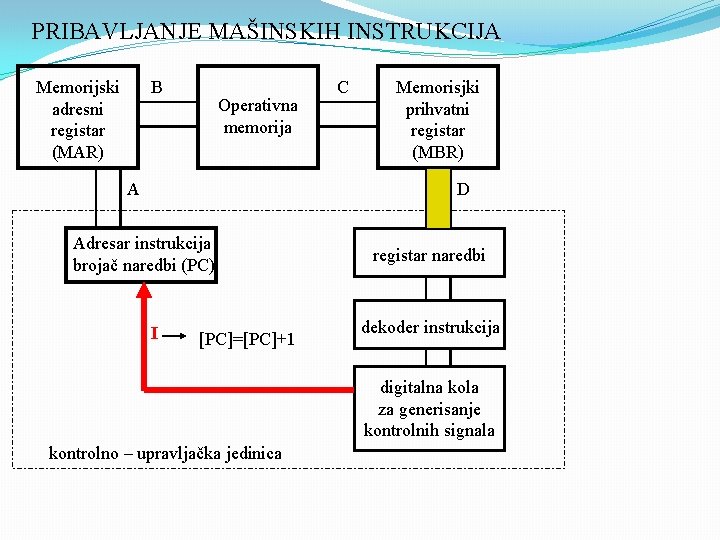

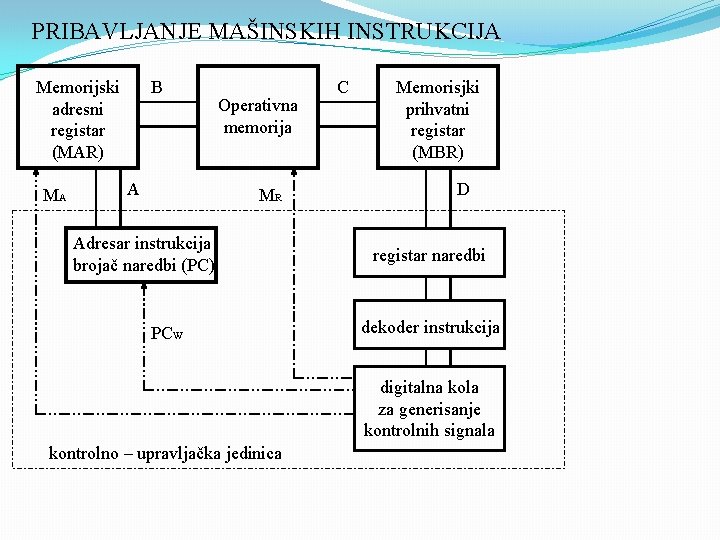

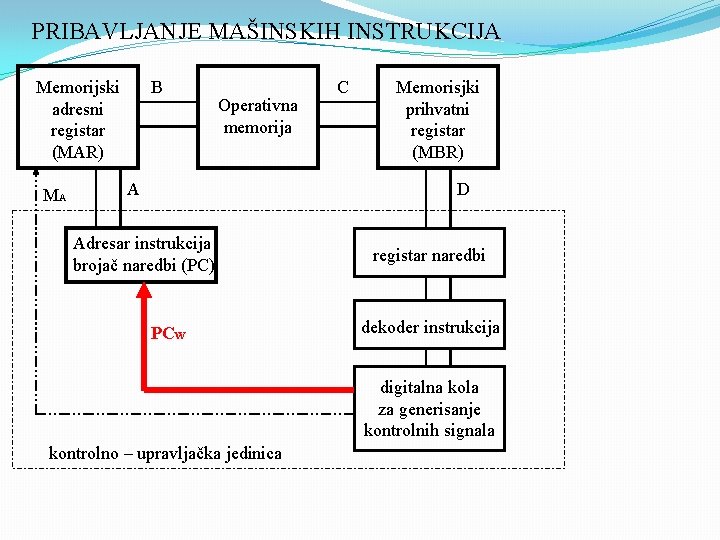

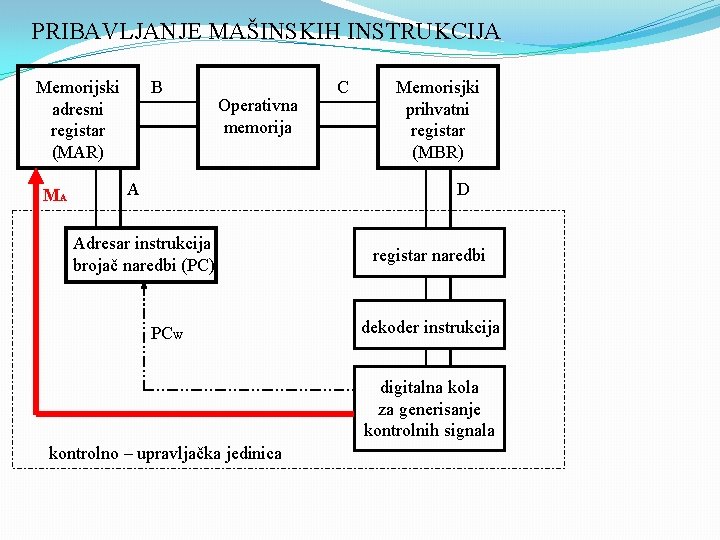

PRIBAVLJANJE MAŠINSKIH INSTRUKCIJA B Memorijski adresni registar (MAR) MA A Operativna memorija MR Adresar instrukcija brojač naredbi (PC) PCW C Memorisjki prihvatni registar (MBR) D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

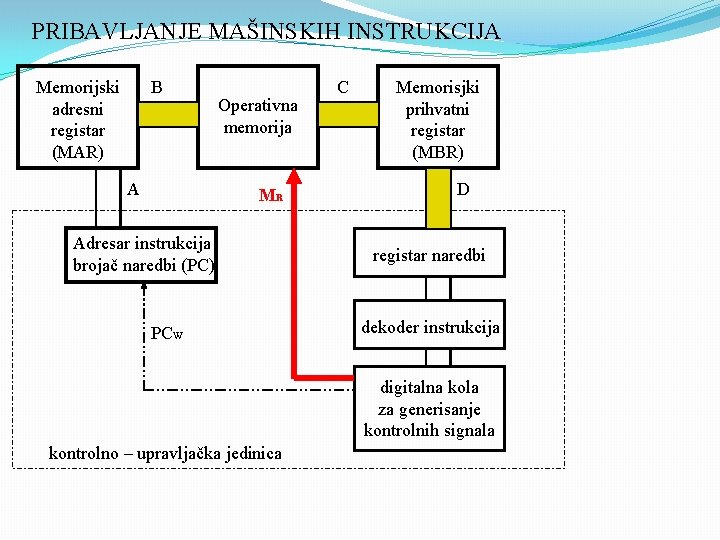

PRIBAVLJANJE MAŠINSKIH INSTRUKCIJA B Memorijski adresni registar (MAR) MA Operativna memorija A C Memorisjki prihvatni registar (MBR) D Adresar instrukcija brojač naredbi (PC) PCW registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

PRIBAVLJANJE MAŠINSKIH INSTRUKCIJA B Memorijski adresni registar (MAR) MA Operativna memorija A C Memorisjki prihvatni registar (MBR) D Adresar instrukcija brojač naredbi (PC) PCW registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

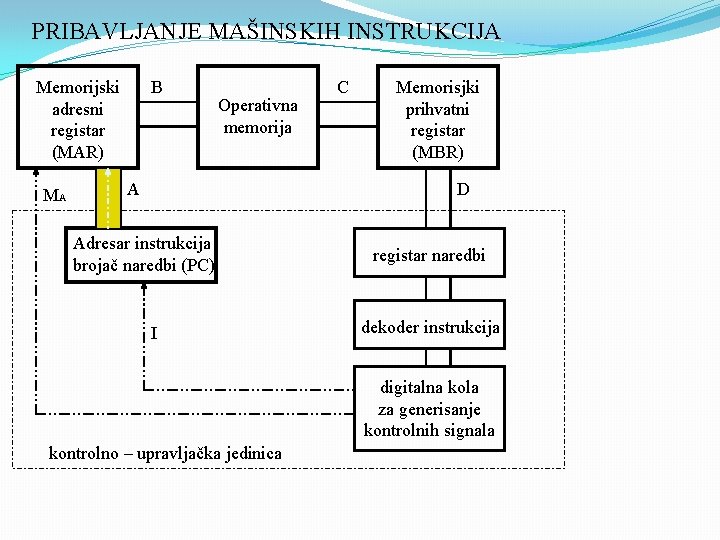

PRIBAVLJANJE MAŠINSKIH INSTRUKCIJA B Memorijski adresni registar (MAR) MA Operativna memorija A C Memorisjki prihvatni registar (MBR) D Adresar instrukcija brojač naredbi (PC) I registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

PRIBAVLJANJE MAŠINSKIH INSTRUKCIJA B Memorijski adresni registar (MAR) A Operativna memorija MR Adresar instrukcija brojač naredbi (PC) PCW C Memorisjki prihvatni registar (MBR) D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

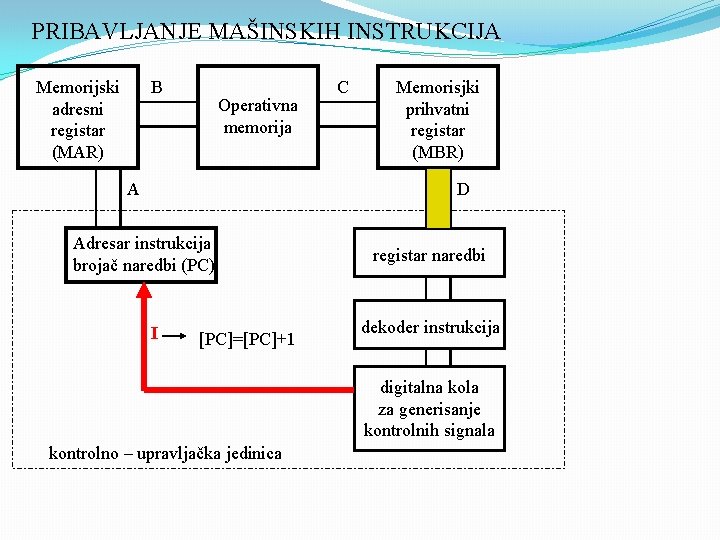

PRIBAVLJANJE MAŠINSKIH INSTRUKCIJA B Memorijski adresni registar (MAR) Operativna memorija A C Memorisjki prihvatni registar (MBR) D Adresar instrukcija brojač naredbi (PC) I [PC]=[PC]+1 registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

F A Z A I Z V R Š A V A Nj A MAŠINSKIH INSTRUKCIJA

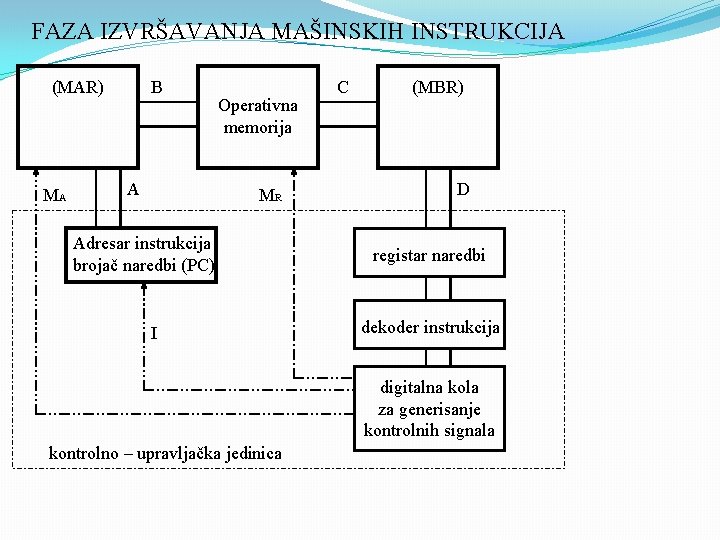

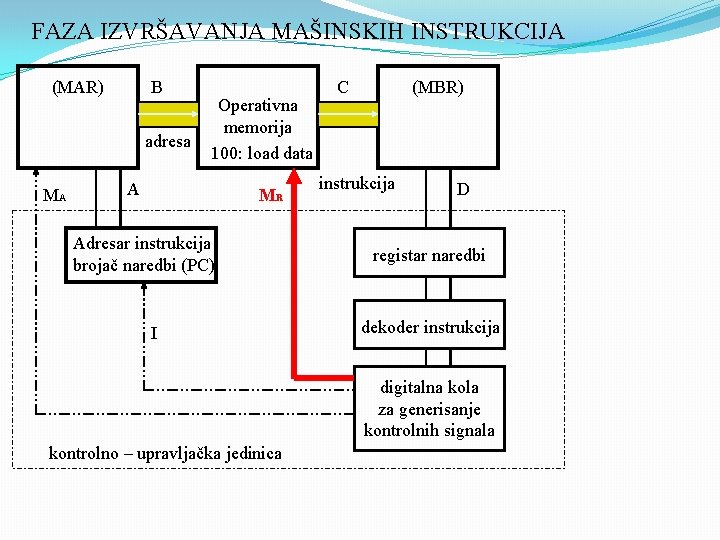

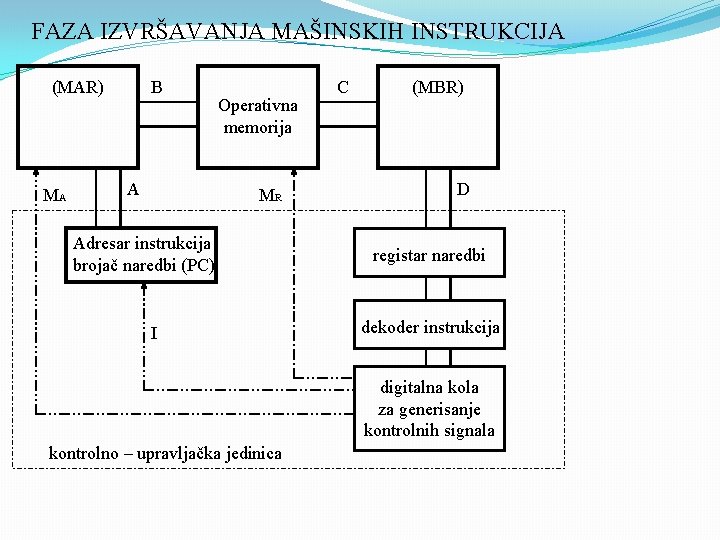

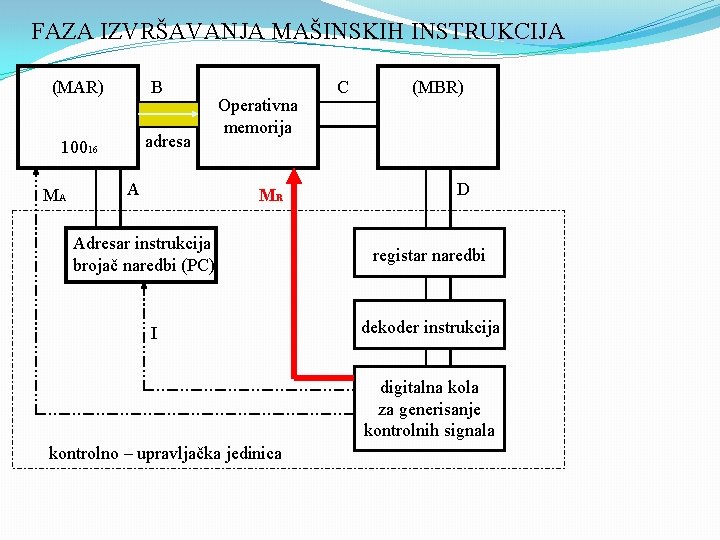

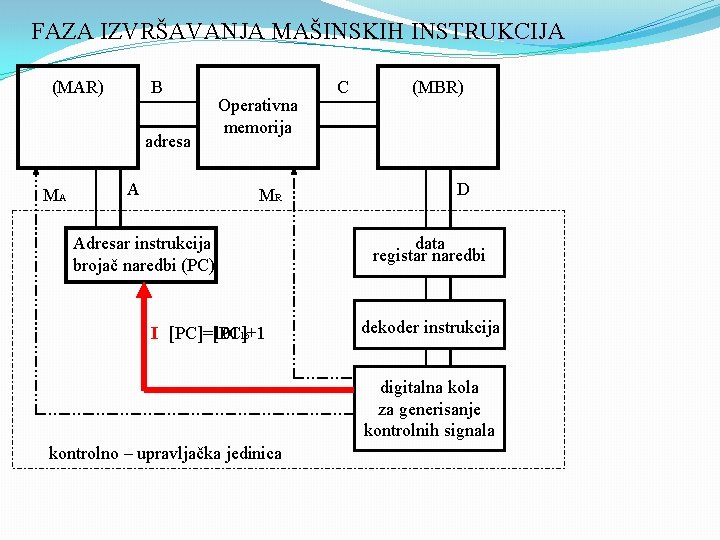

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA B (MAR) MA A Operativna memorija MR Adresar instrukcija brojač naredbi (PC) I C (MBR) D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

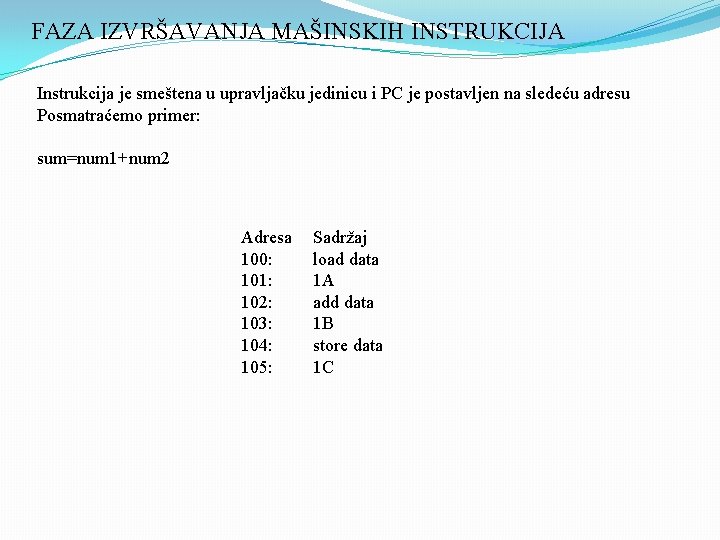

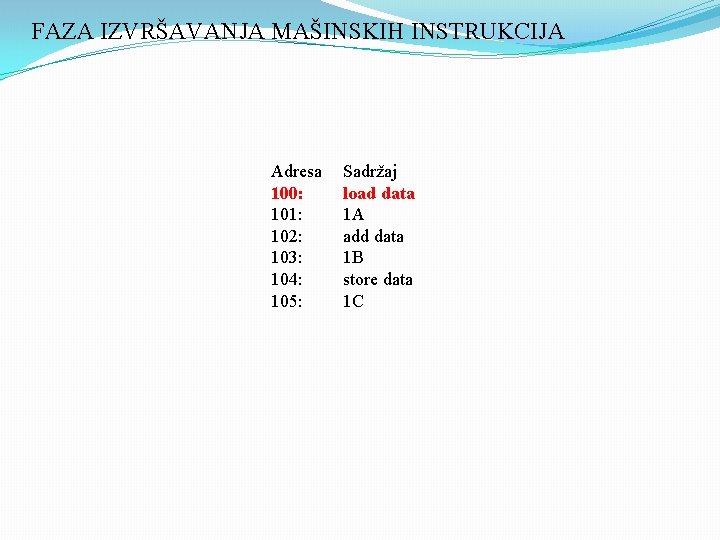

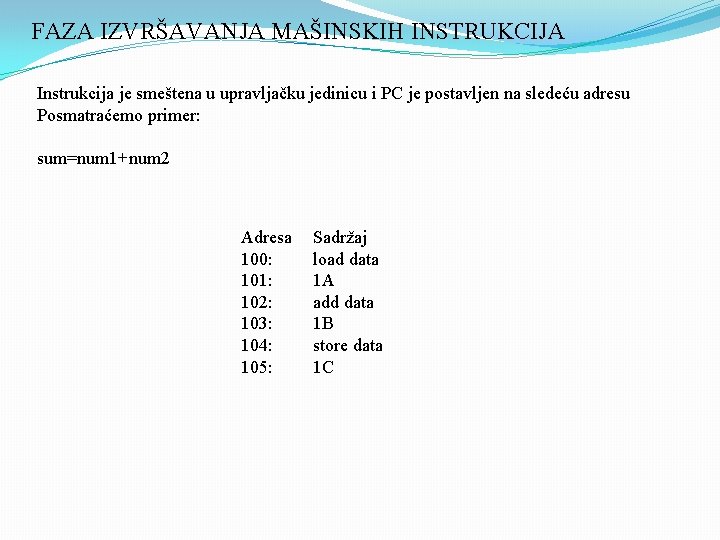

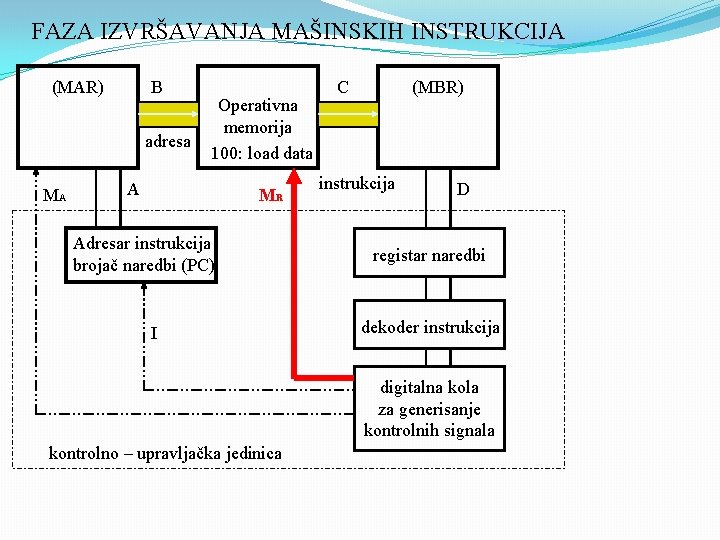

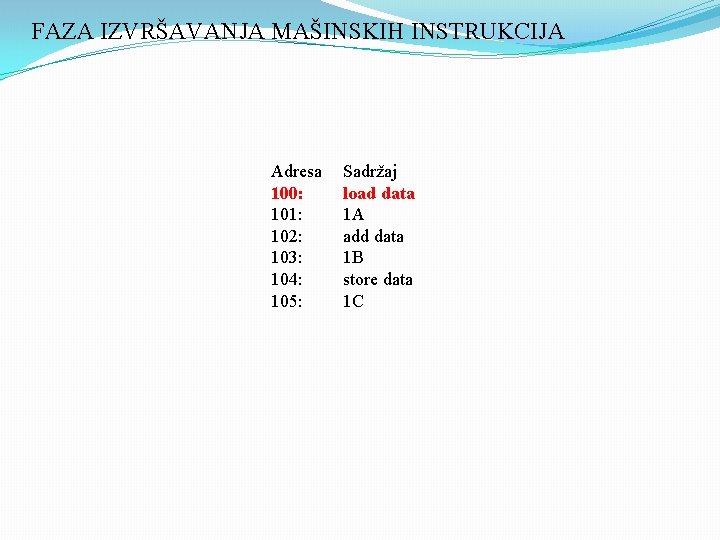

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA Instrukcija je smeštena u upravljačku jedinicu i PC je postavljen na sledeću adresu Posmatraćemo primer: sum=num 1+num 2 Adresa 100: 101: 102: 103: 104: 105: Sadržaj load data 1 A add data 1 B store data 1 C

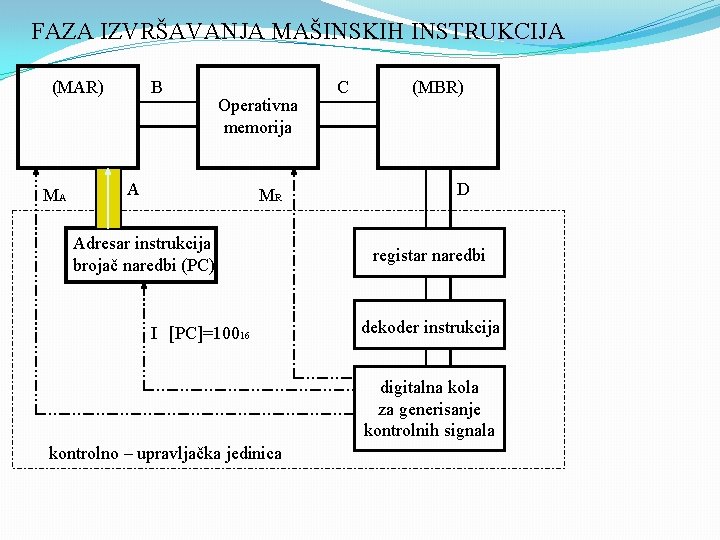

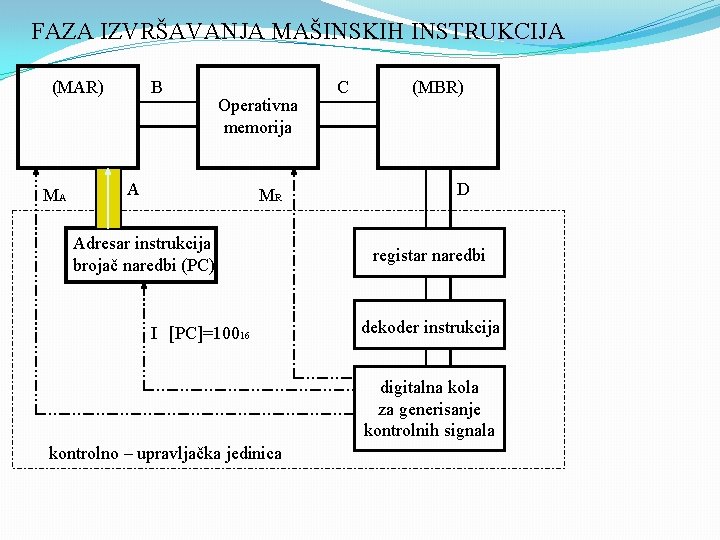

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA B (MAR) MA Operativna memorija A MR Adresar instrukcija brojač naredbi (PC) I [PC]=10016 C (MBR) D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

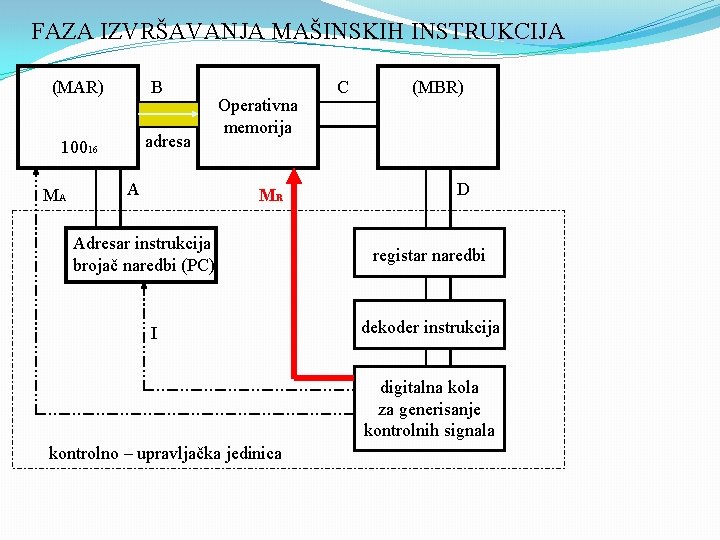

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA B (MAR) adresa 10016 MA A Operativna memorija MR Adresar instrukcija brojač naredbi (PC) I C (MBR) D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA B (MAR) adresa MA Operativna memorija 100: load data A MR Adresar instrukcija brojač naredbi (PC) I C (MBR) instrukcija D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

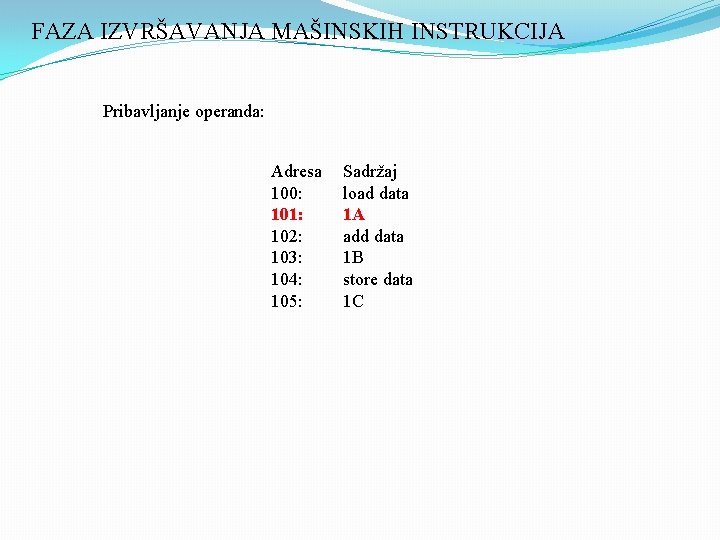

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA Adresa 100: 101: 102: 103: 104: 105: Sadržaj load data 1 A add data 1 B store data 1 C

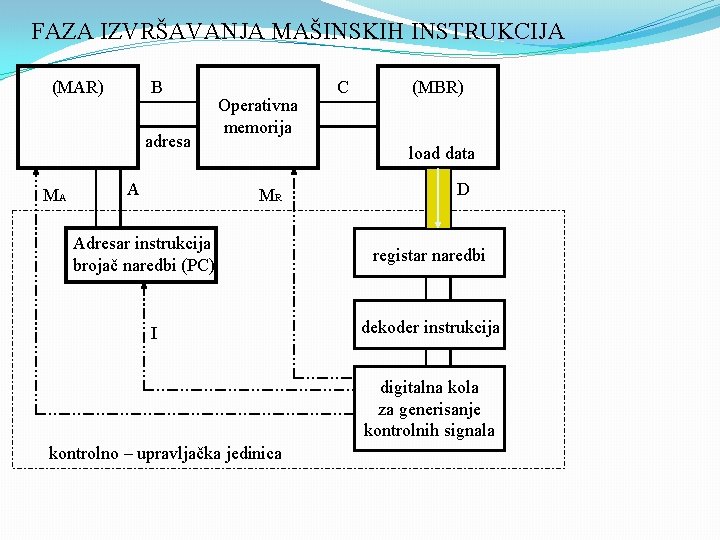

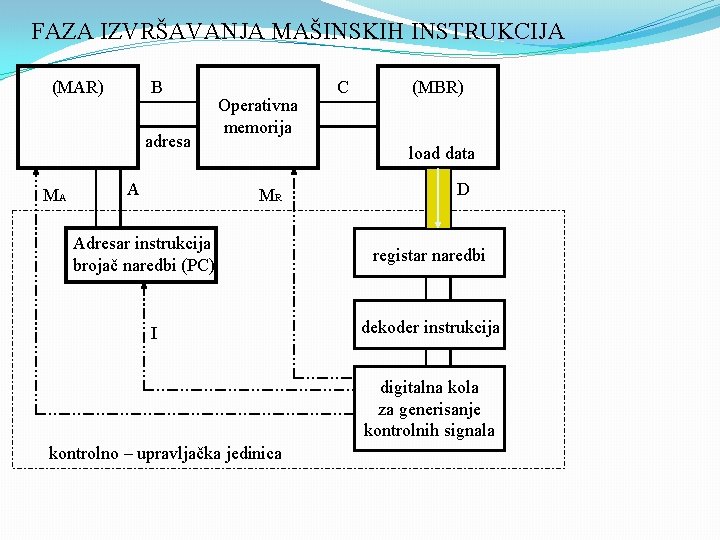

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA B (MAR) adresa MA A Operativna memorija C (MBR) load data MR Adresar instrukcija brojač naredbi (PC) I D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

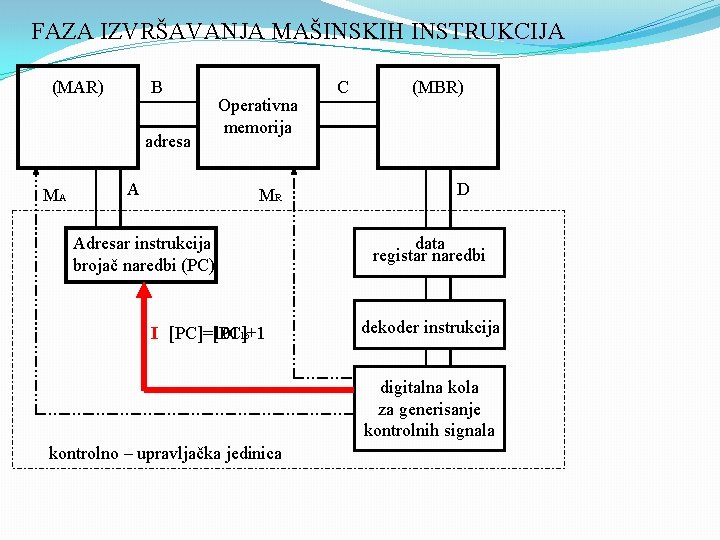

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA B (MAR) adresa MA A Operativna memorija MR Adresar instrukcija brojač naredbi (PC) I [PC]=[PC]+1 [PC]=10116 C (MBR) D data registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica

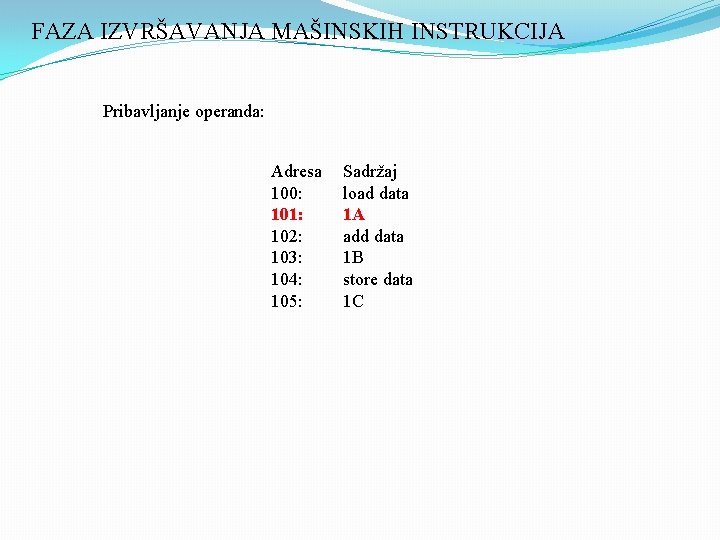

FAZA IZVRŠAVANJA MAŠINSKIH INSTRUKCIJA Pribavljanje operanda: Adresa 100: 101: 102: 103: 104: 105: Sadržaj load data 1 A add data 1 B store data 1 C

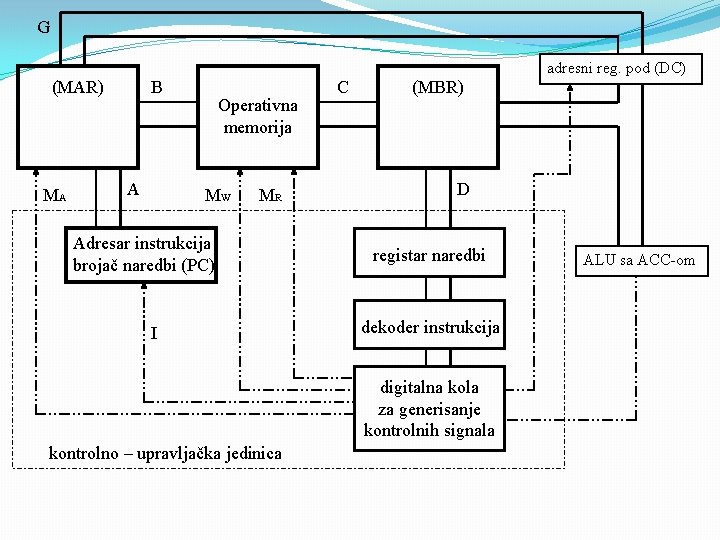

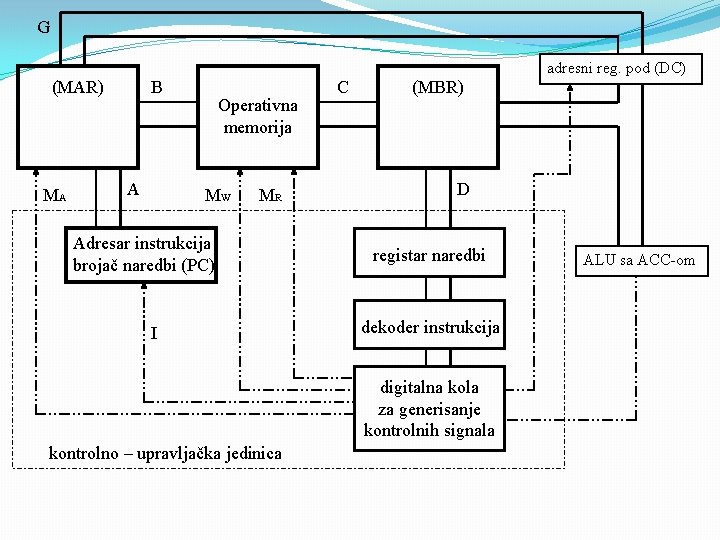

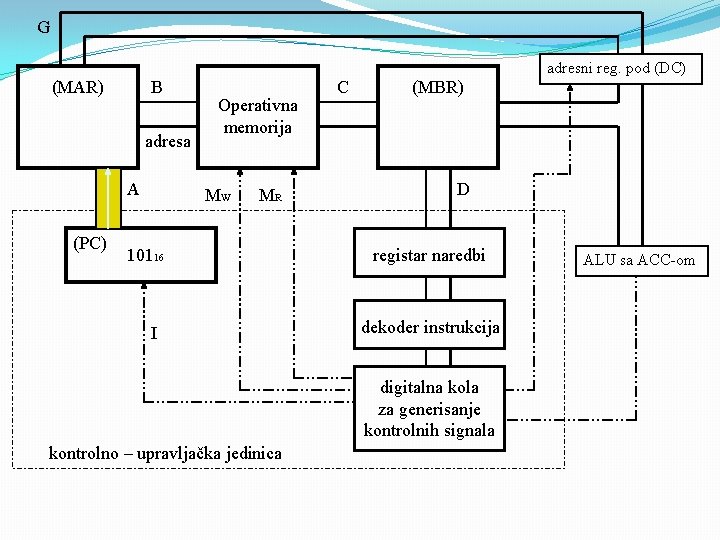

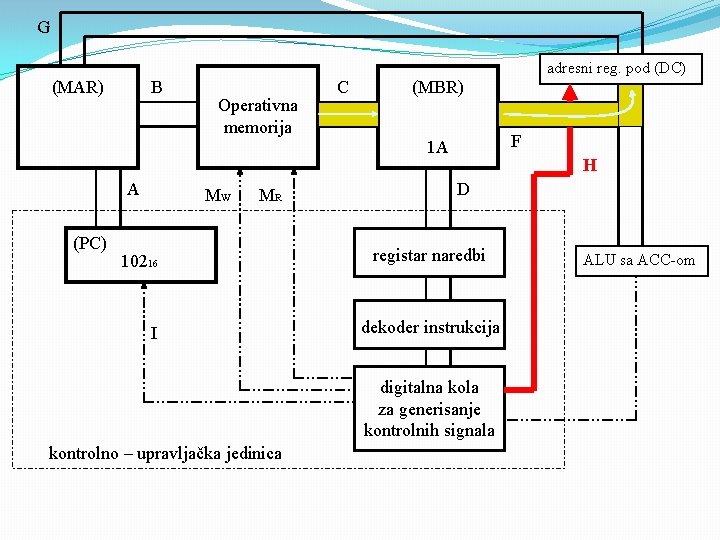

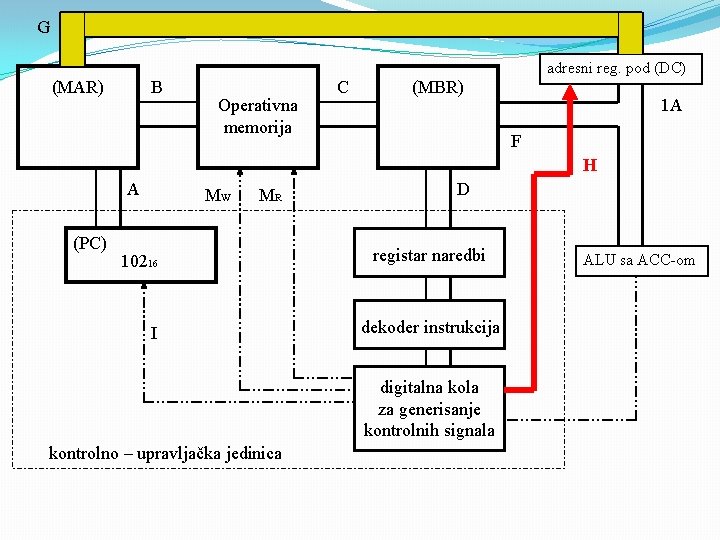

G adresni reg. pod (DC) B (MAR) MA A Operativna memorija MW MR Adresar instrukcija brojač naredbi (PC) I C (MBR) D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

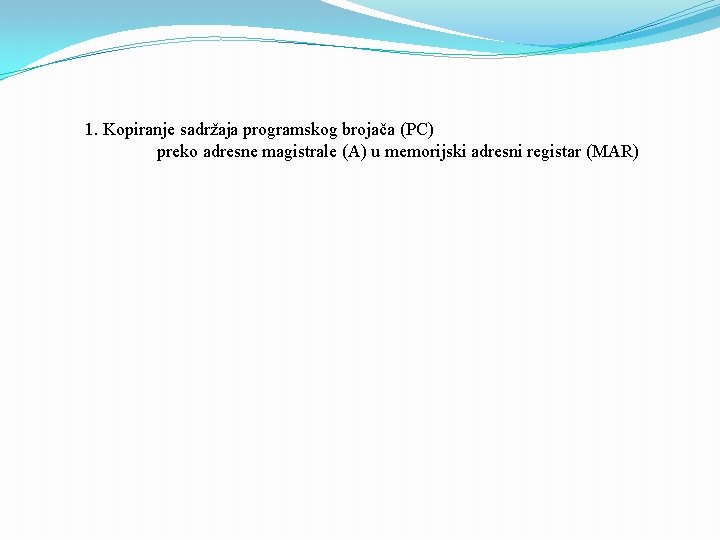

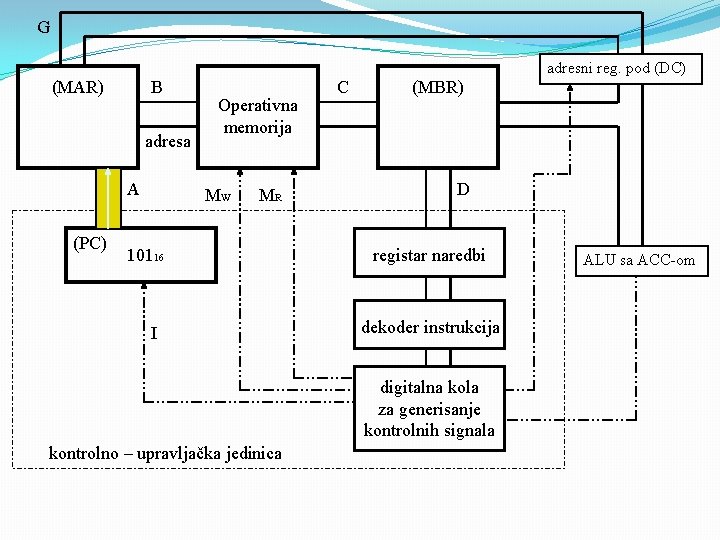

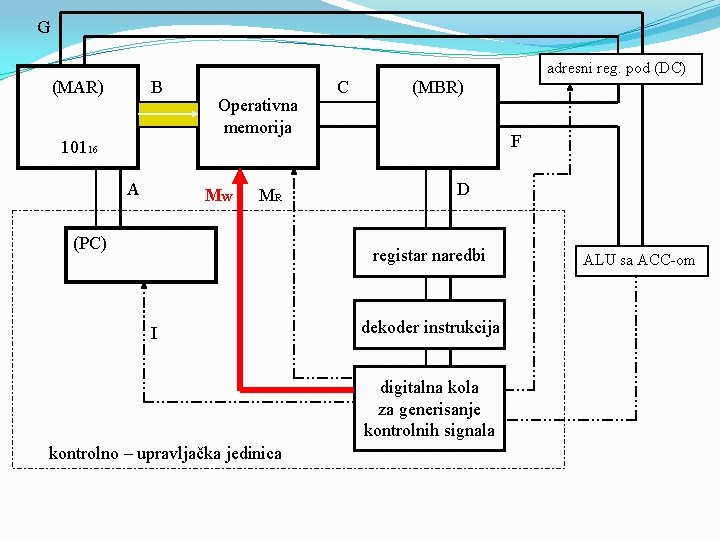

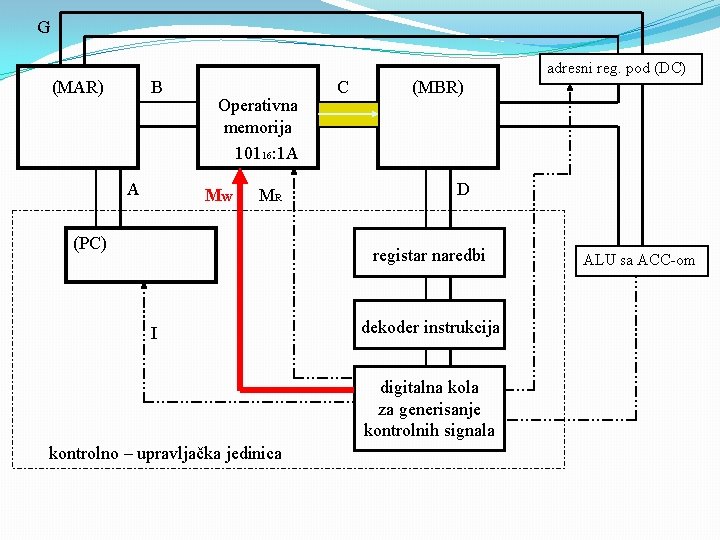

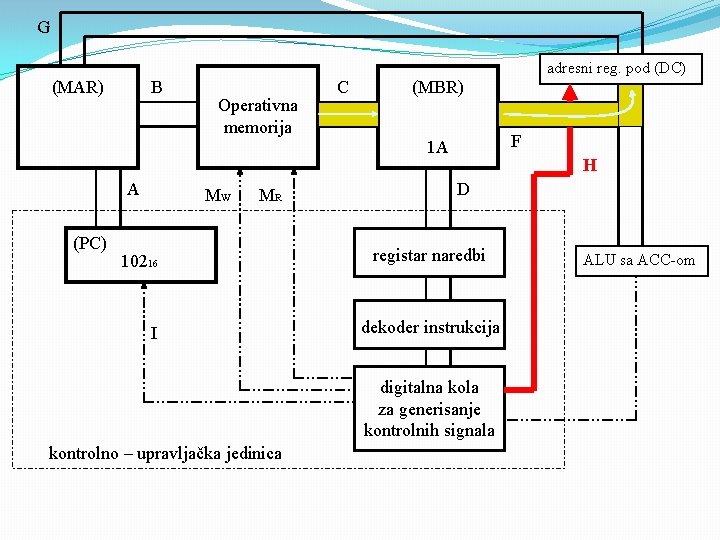

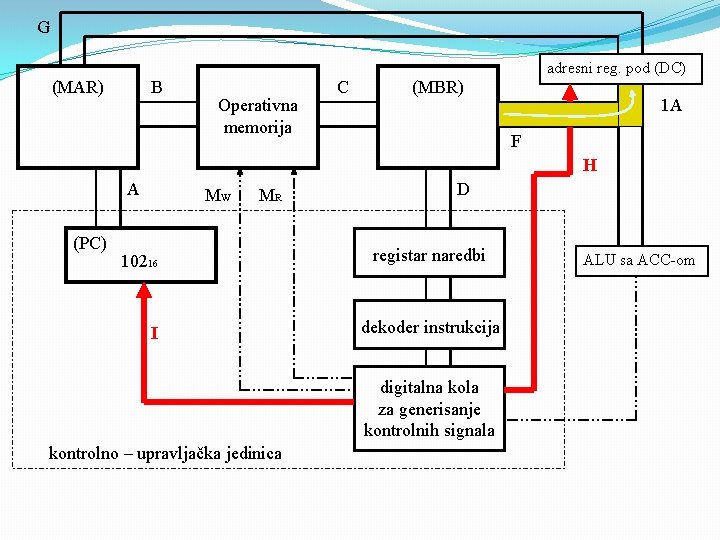

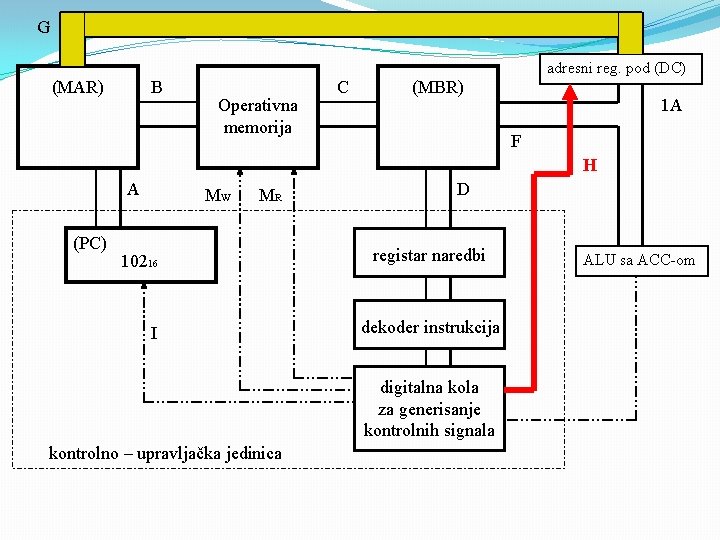

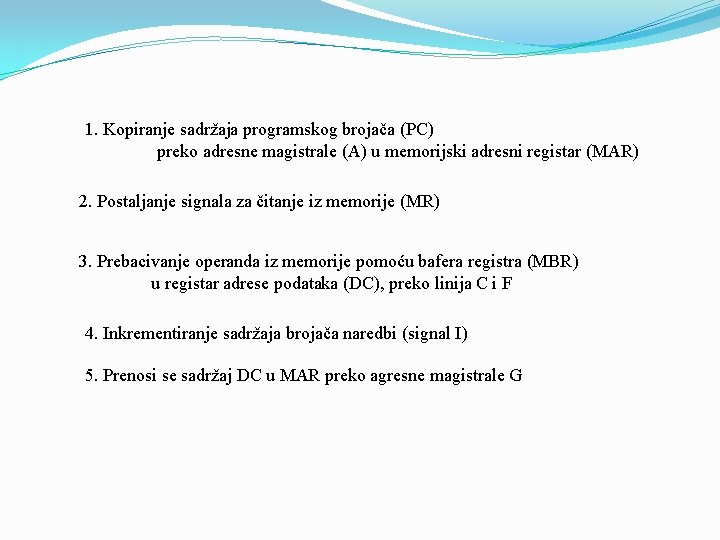

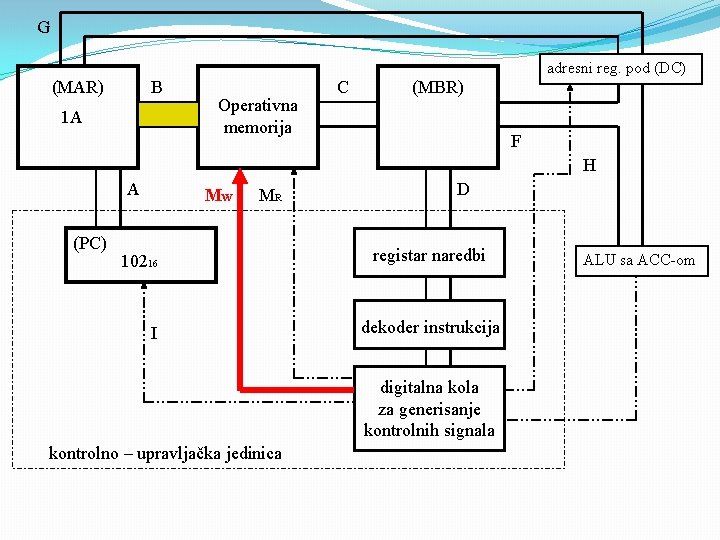

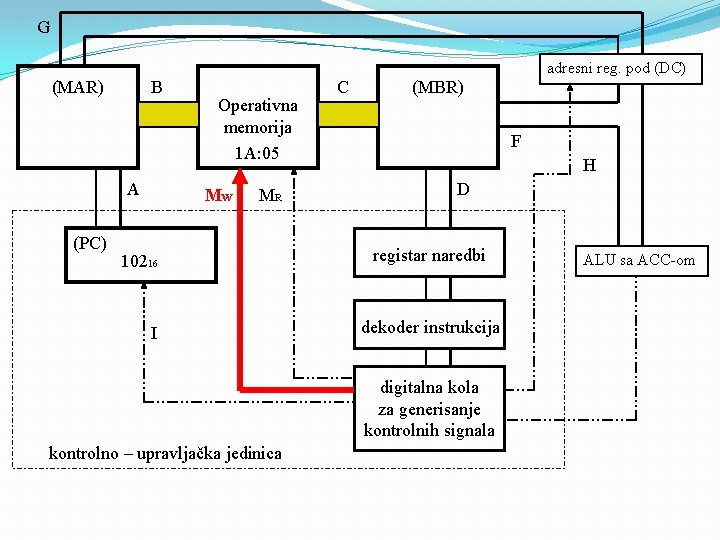

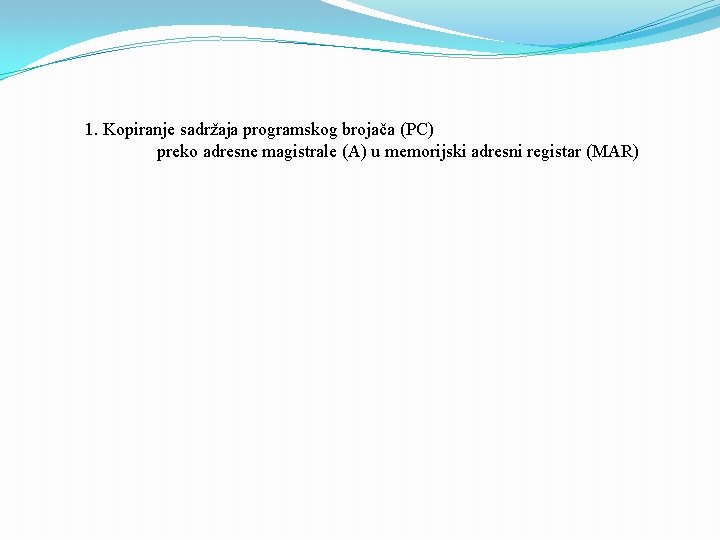

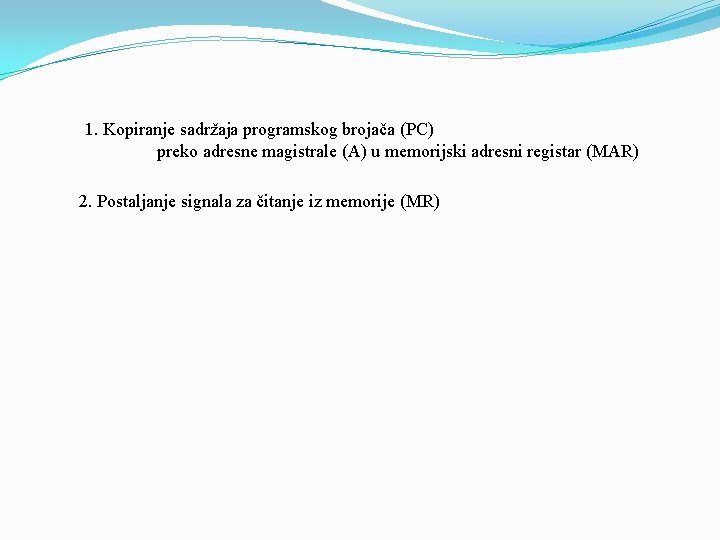

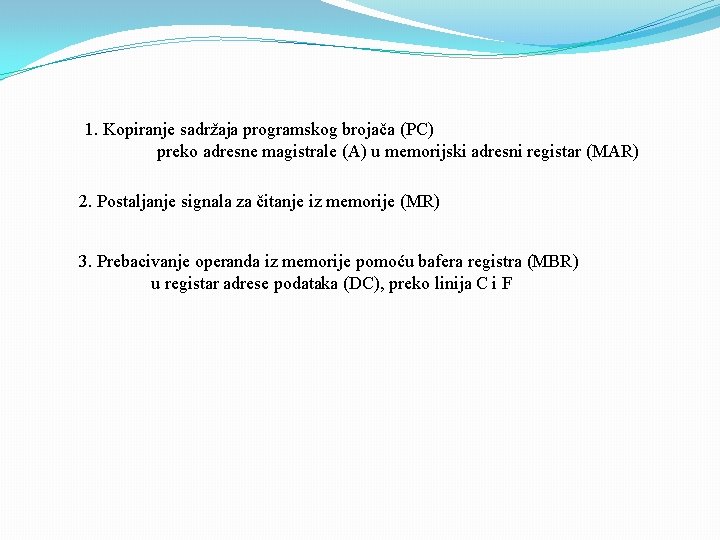

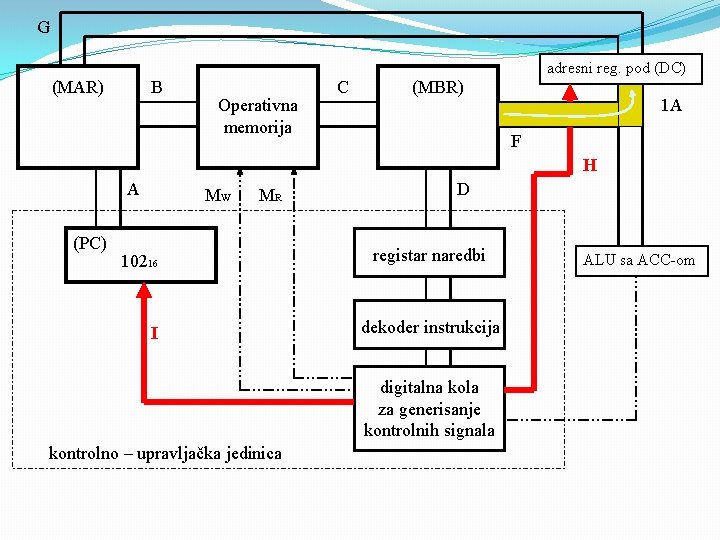

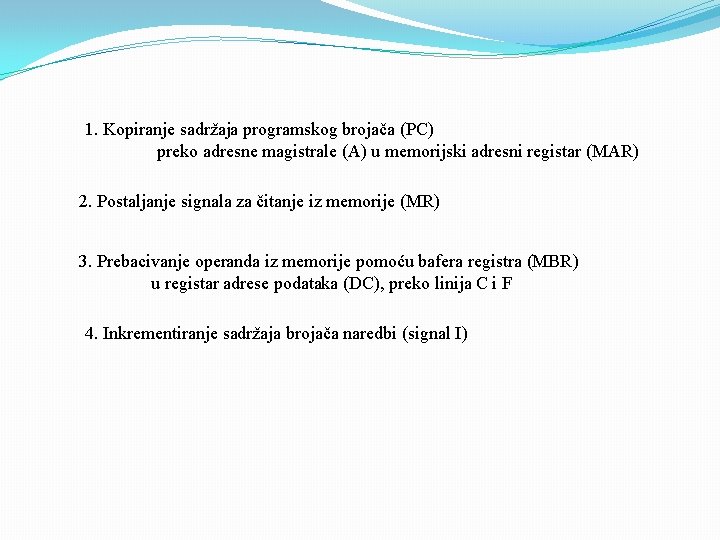

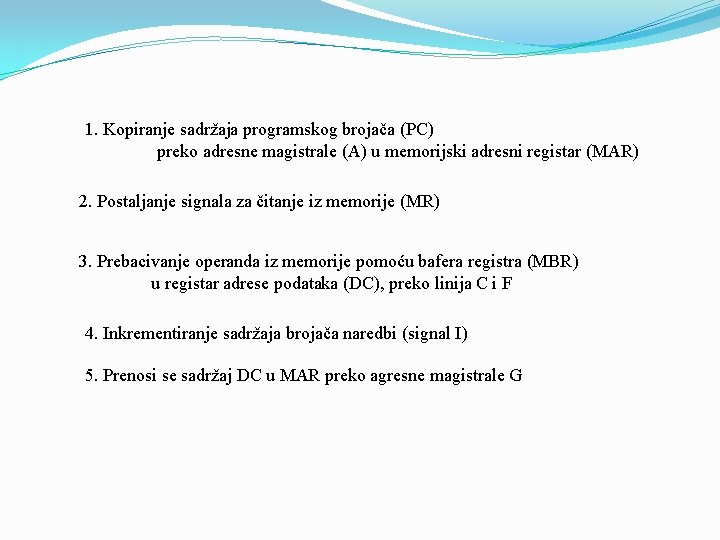

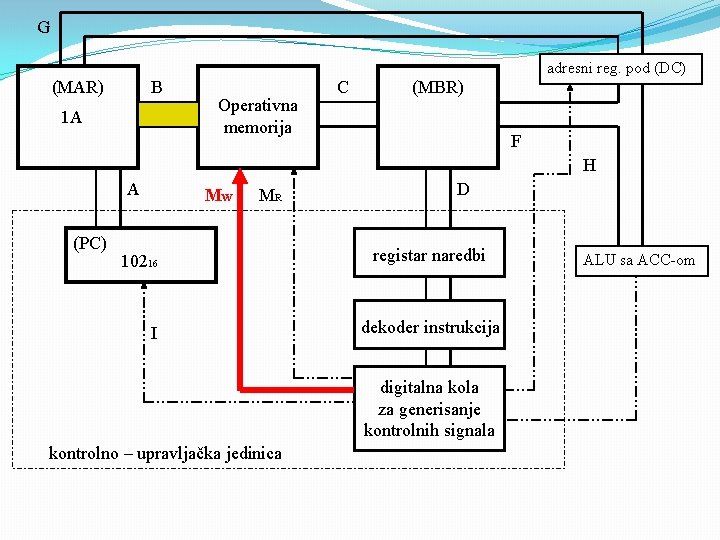

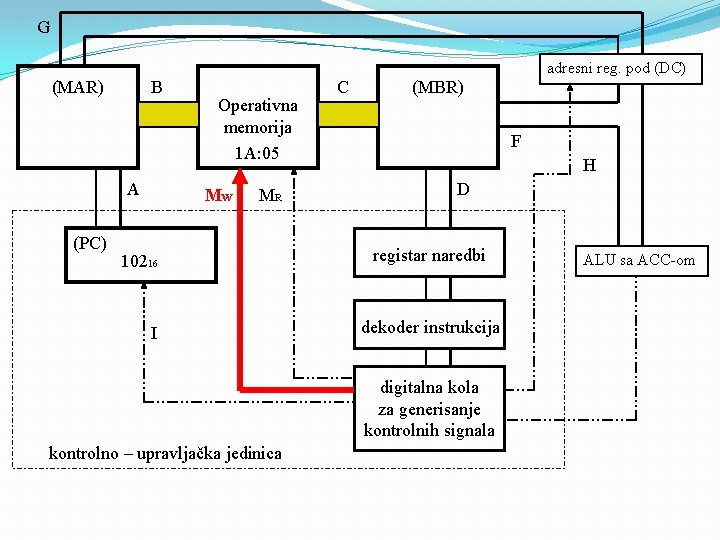

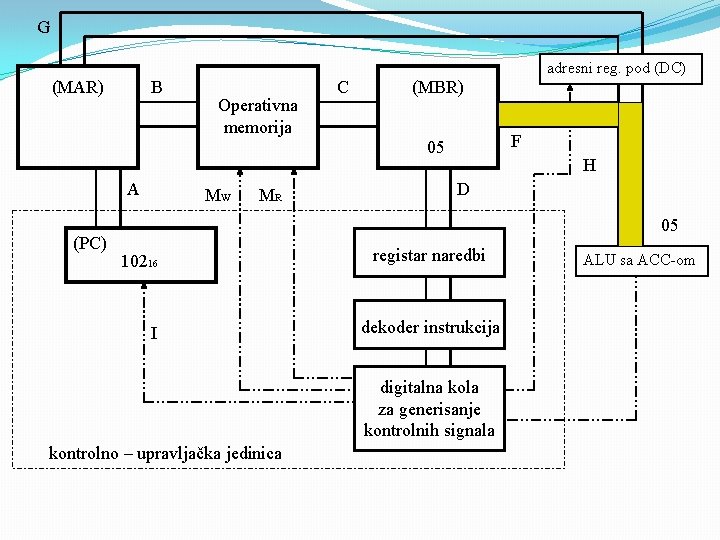

1. Kopiranje sadržaja programskog brojača (PC) preko adresne magistrale (A) u memorijski adresni registar (MAR)

G adresni reg. pod (DC) B (MAR) adresa A (PC) Operativna memorija MW MR 10116 I C (MBR) D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

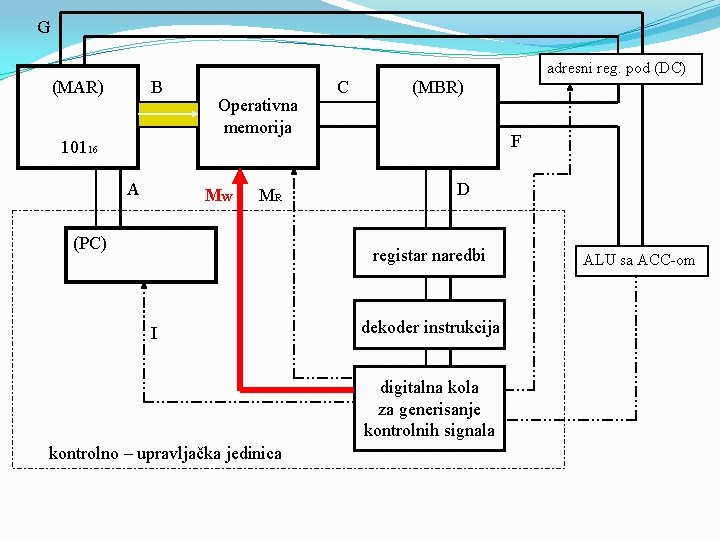

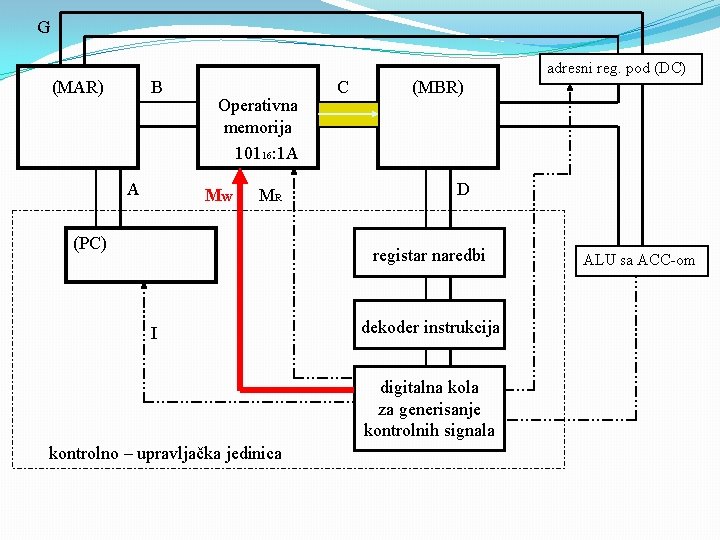

1. Kopiranje sadržaja programskog brojača (PC) preko adresne magistrale (A) u memorijski adresni registar (MAR) 2. Postaljanje signala za čitanje iz memorije (MR)

G adresni reg. pod (DC) B (MAR) Operativna memorija C (MBR) F 10116 A MW MR (PC) D registar naredbi I dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

G adresni reg. pod (DC) B (MAR) A Operativna memorija 10116: 1 A MW MR (PC) C (MBR) D registar naredbi I dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

G adresni reg. pod (DC) B (MAR) Operativna memorija C (MBR) F 1 A A (PC) MW MR 10216 I H D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

1. Kopiranje sadržaja programskog brojača (PC) preko adresne magistrale (A) u memorijski adresni registar (MAR) 2. Postaljanje signala za čitanje iz memorije (MR) 3. Prebacivanje operanda iz memorije pomoću bafera registra (MBR) u registar adrese podataka (DC), preko linija C i F

G adresni reg. pod (DC) B (MAR) Operativna memorija C (MBR) 1 A F H A (PC) MW MR 10216 I D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

1. Kopiranje sadržaja programskog brojača (PC) preko adresne magistrale (A) u memorijski adresni registar (MAR) 2. Postaljanje signala za čitanje iz memorije (MR) 3. Prebacivanje operanda iz memorije pomoću bafera registra (MBR) u registar adrese podataka (DC), preko linija C i F 4. Inkrementiranje sadržaja brojača naredbi (signal I)

G adresni reg. pod (DC) B (MAR) Operativna memorija C (MBR) 1 A F H A (PC) MW MR 10216 I D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

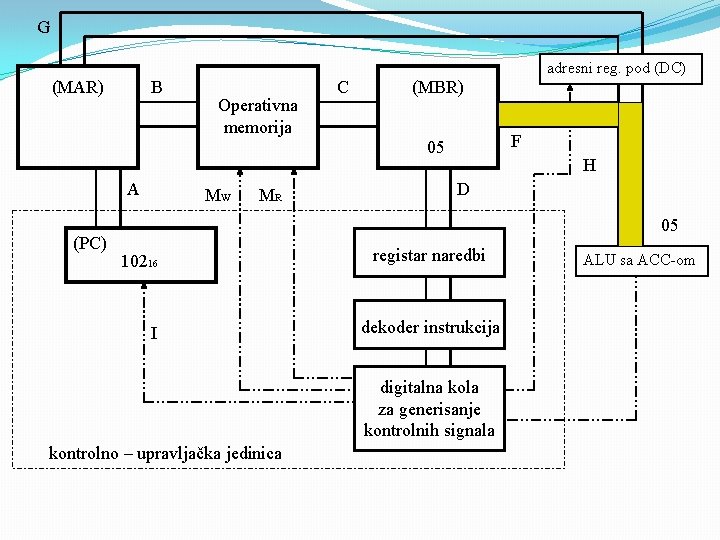

1. Kopiranje sadržaja programskog brojača (PC) preko adresne magistrale (A) u memorijski adresni registar (MAR) 2. Postaljanje signala za čitanje iz memorije (MR) 3. Prebacivanje operanda iz memorije pomoću bafera registra (MBR) u registar adrese podataka (DC), preko linija C i F 4. Inkrementiranje sadržaja brojača naredbi (signal I) 5. Prenosi se sadržaj DC u MAR preko agresne magistrale G

G adresni reg. pod (DC) B (MAR) 1 A Operativna memorija C (MBR) F H A (PC) MW MR 10216 I D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

G adresni reg. pod (DC) B (MAR) A (PC) Operativna memorija 1 A: 05 MW MR 10216 I C (MBR) F H D registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

G adresni reg. pod (DC) B (MAR) Operativna memorija C (MBR) F 05 A (PC) MW MR H D 05 10216 I registar naredbi dekoder instrukcija digitalna kola za generisanje kontrolnih signala kontrolno – upravljačka jedinica ALU sa ACC-om

6. Šalje se nov zahtev za čitanje iz memorije MR 7. Prihvata se podatak u MBR preko linije C 8. Preuzimanje podatka iz registra dozvolom kontrolnog signala H 9. Preko magistrale F kopira se podatak u ACC