Architetture di bus per System OnChip Massimo Bocchi

Architetture di bus per System -On-Chip Massimo Bocchi Corso di Architettura dei Sistemi Integrati A. A. 2002/2003

Outline n System-on-chip definition n Intellectual property reuse n Bus architectures n AMBA specification n AHB-Lite specification n Multi-Layer AHB specification Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

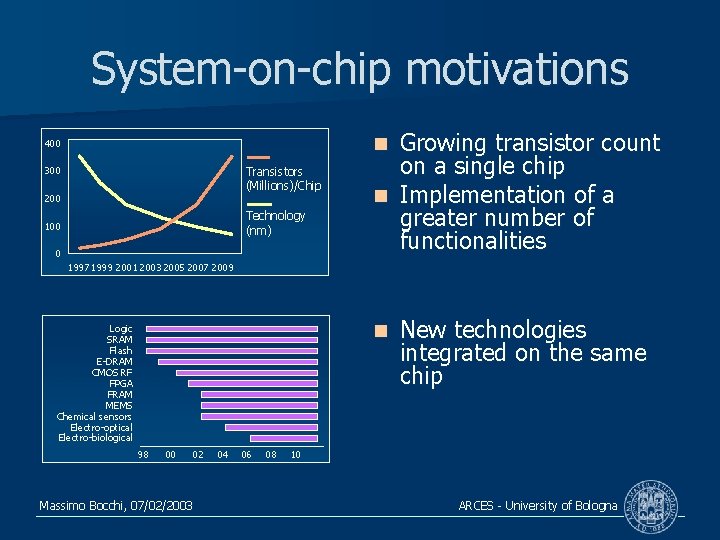

System-on-chip motivations Growing transistor count on a single chip n Implementation of a greater number of functionalities n 400 Transistors (Millions)/Chip 300 200 Technology (nm) 100 0 1997 1999 2001 2003 2005 2007 2009 n Logic SRAM Flash E-DRAM CMOS RF FPGA FRAM MEMS Chemical sensors Electro-optical Electro-biological 98 00 02 Massimo Bocchi, 07/02/2003 04 06 08 New technologies integrated on the same chip 10 ARCES - University of Bologna

Outline n System-on-chip definition n Intellectual property reuse n Bus architectures n AMBA specification n AHB-Lite specification n Multi-Layer AHB specification Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

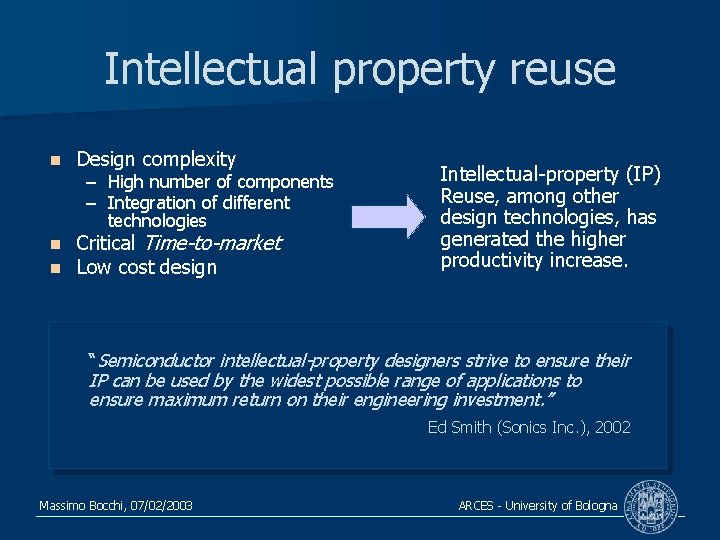

Intellectual property reuse n Design complexity n n Critical Time-to-market Low cost design – High number of components – Integration of different technologies Intellectual-property (IP) Reuse, among other design technologies, has generated the higher productivity increase. “Semiconductor intellectual-property designers strive to ensure their IP can be used by the widest possible range of applications to ensure maximum return on their engineering investment. ” Ed Smith (Sonics Inc. ), 2002 Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

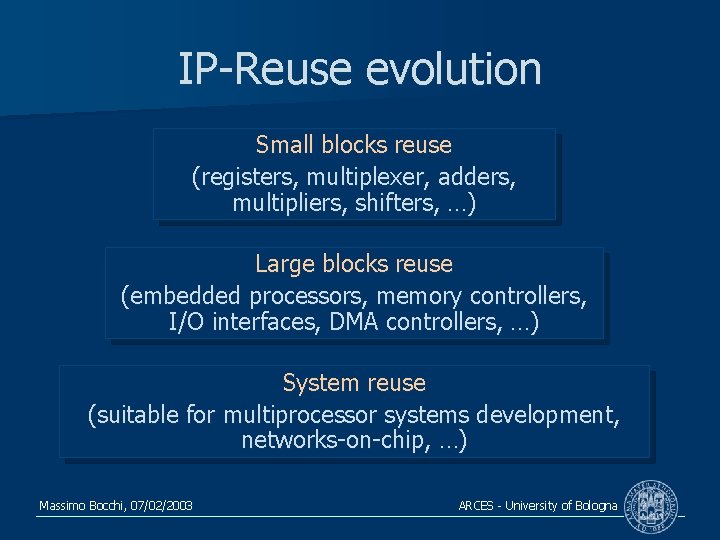

IP-Reuse evolution Small blocks reuse (registers, multiplexer, adders, multipliers, shifters, …) Large blocks reuse (embedded processors, memory controllers, I/O interfaces, DMA controllers, …) System reuse (suitable for multiprocessor systems development, networks-on-chip, …) Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

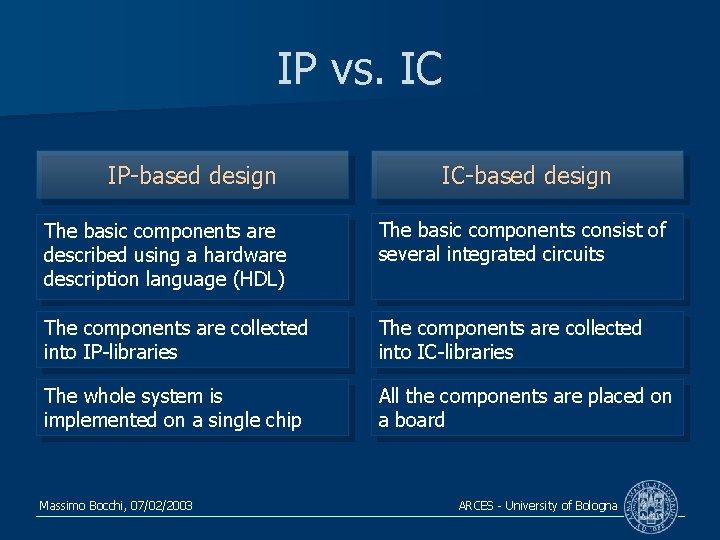

IP vs. IC IP-based design IC-based design The basic components are described using a hardware description language (HDL) The basic components consist of several integrated circuits The components are collected into IP-libraries The components are collected into IC-libraries The whole system is implemented on a single chip All the components are placed on a board Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

Outline n System-on-chip definition n Intellectual property reuse n Bus architectures n AMBA specification n AHB-Lite specification n Multi-Layer AHB specification Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

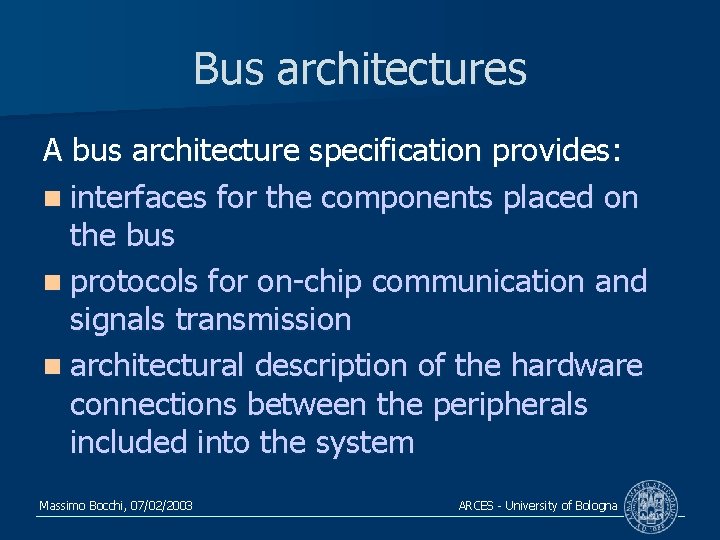

Bus architectures A bus architecture specification provides: n interfaces for the components placed on the bus n protocols for on-chip communication and signals transmission n architectural description of the hardware connections between the peripherals included into the system Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

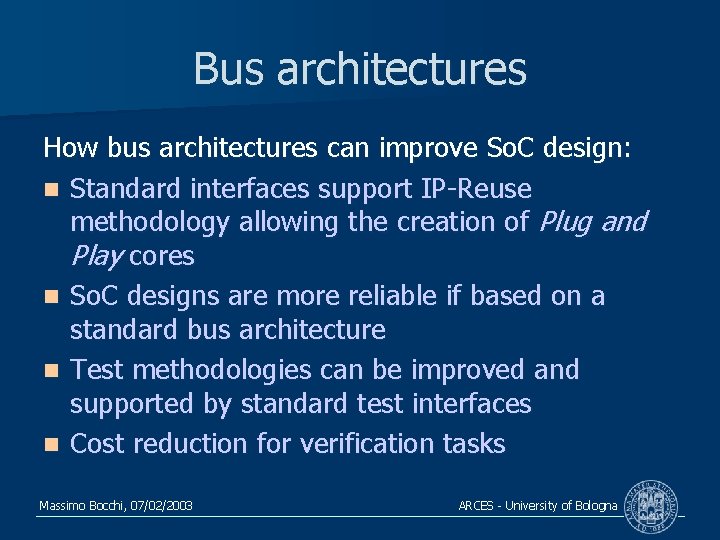

Bus architectures How bus architectures can improve So. C design: n Standard interfaces support IP-Reuse methodology allowing the creation of Plug and Play cores n So. C designs are more reliable if based on a standard bus architecture n Test methodologies can be improved and supported by standard test interfaces n Cost reduction for verification tasks Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

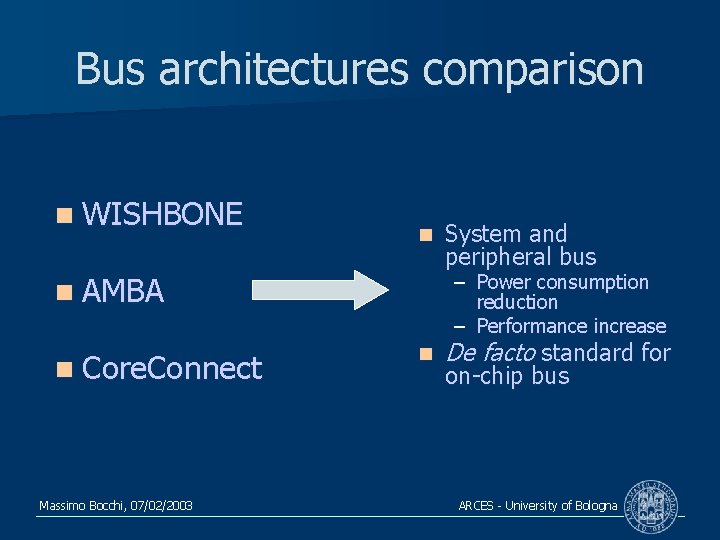

Bus architectures comparison n WISHBONE n – Power consumption reduction – Performance increase n AMBA n Core. Connect Massimo Bocchi, 07/02/2003 System and peripheral bus n De facto standard for on-chip bus ARCES - University of Bologna

Outline n System-on-chip definition n Intellectual property reuse n Bus architectures n AMBA specification n AHB-Lite specification n Multi-Layer AHB specification Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

AMBA specification n n n AMBA is an open standard developed by ARM Ltd. (www. arm. com) A typical AMBA-based So. C consists of a high performance system bus (AHB) and peripheral bus (APB) A standard test methodology is included in the AMBA specification The full AHB specification is contained in the AMBA 2. 0 documentation AHB-Lite is a subset to the full AHB specification Multi-layer AHB is an extension to the AHB protocol, providing parallel communication paths between masters and slaves Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

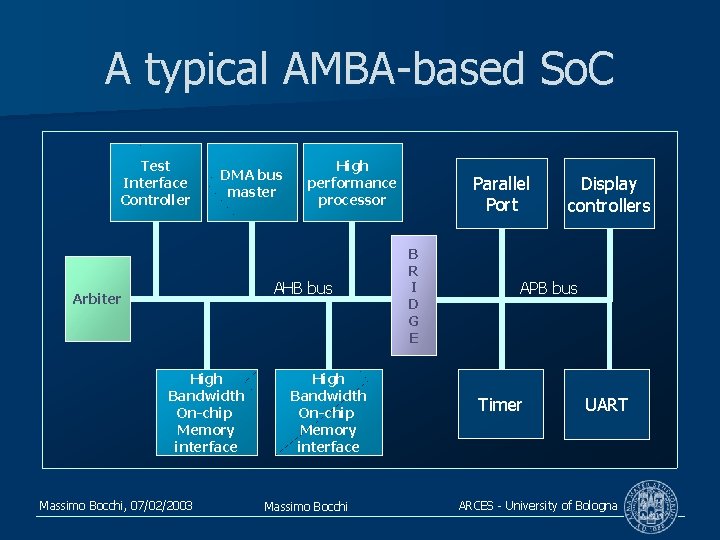

A typical AMBA-based So. C Test Interface Controller DMA bus master High performance processor AHB bus Arbiter High Bandwidth On-chip Memory interface Massimo Bocchi, 07/02/2003 High Bandwidth On-chip Memory interface Massimo Bocchi Parallel Port B R I D G E Display controllers APB bus Timer UART ARCES - University of Bologna

AMBA AHB main features n Pipelined operation n Multiple bus masters n Burst transfers n Split transactions n Non-tristate implementation n Wide data bus configurations (up to 128 bits) Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

AMBA APB main features n Low power consumption n Simple interface n Latched address and control n Suitable for many peripherals Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

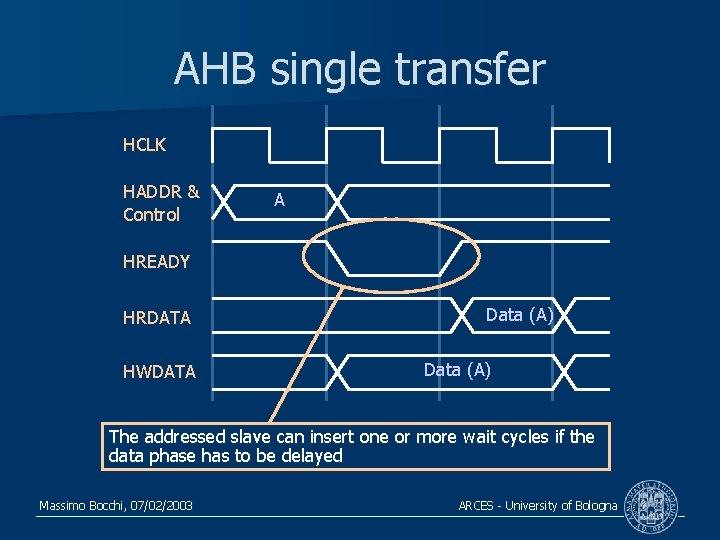

AHB single transfer HCLK HADDR & Control A HREADY HRDATA HWDATA Data (A) The addressed slave can insert one or more wait cycles if the data phase has to be delayed Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

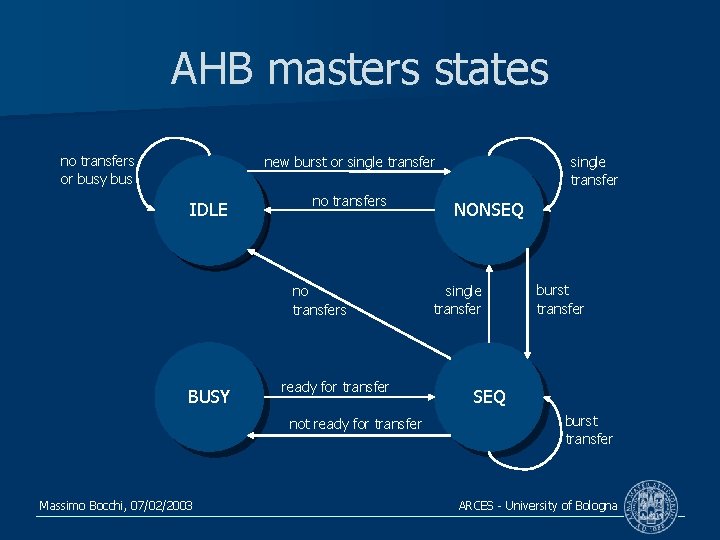

AHB masters states no transfers or busy bus new burst or single transfer IDLE no transfers BUSY ready for transfer not ready for transfer Massimo Bocchi, 07/02/2003 single transfer NONSEQ single transfer burst transfer SEQ burst transfer ARCES - University of Bologna

AHB slaves responses OKAY: the transfer has been completed successfully n ERROR: there was an error during the transfer; the master should reinitiate the transfer n RETRY: the slave has not yet completed the transfer; the master should retry a new transfer n SPLIT: the slave cannot complete the transfer immediately; another higher-priority master can get access to the bus and the current transfer will be completed later n Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

Burst transfers Type Description SINGLE Single transfer INCR Incrementing burst of unspecified length WRAP 4 4 -beat wrapping burst INCR 4 4 -beat incrementing burst WRAP 8 8 -beat wrapping burst INCR 8 8 -beat incrementing burst WRAP 16 16 -beat wrapping burst INCR 16 16 -beat incrementing burst Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

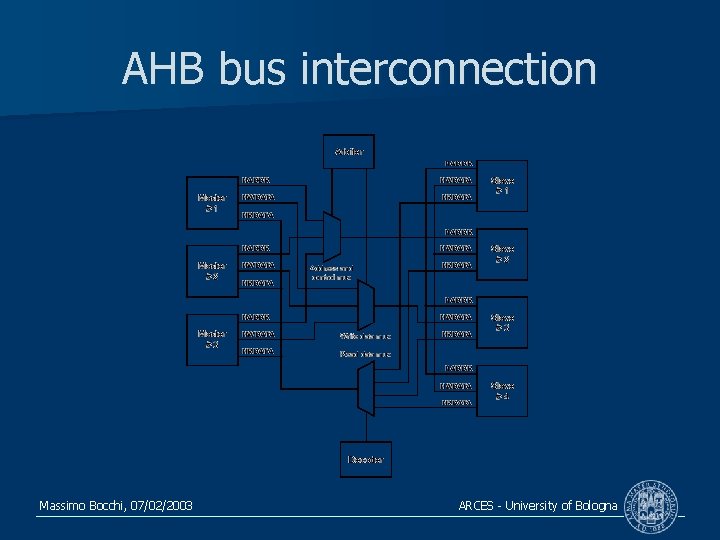

AHB bus interconnection Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

APB transfers n The BRIDGE operates signal conversions from the AHB protocol to the APB one n APB features a very simple communication protocol n APB slaves cannot insert any wait cycle; the duration of transfers is fixed Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

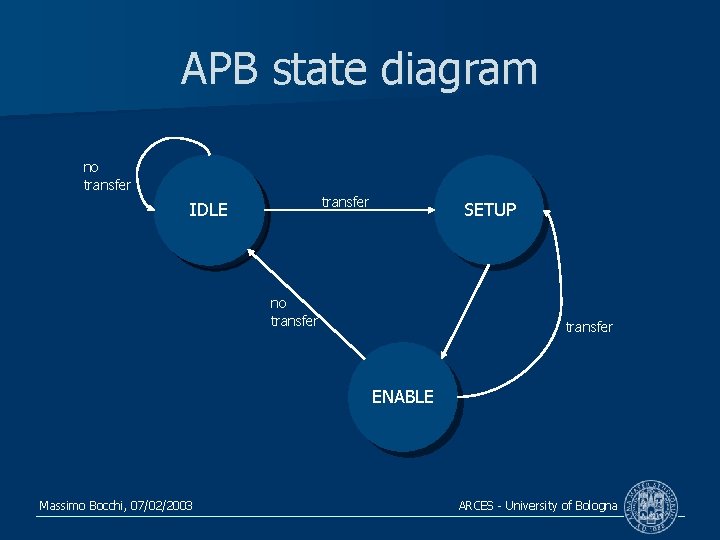

APB state diagram no transfer IDLE SETUP no transfer ENABLE Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

Outline n System-on-chip definition n Intellectual property reuse n Bus architectures n AMBA specification n AHB-Lite specification n Multi-Layer AHB specification Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

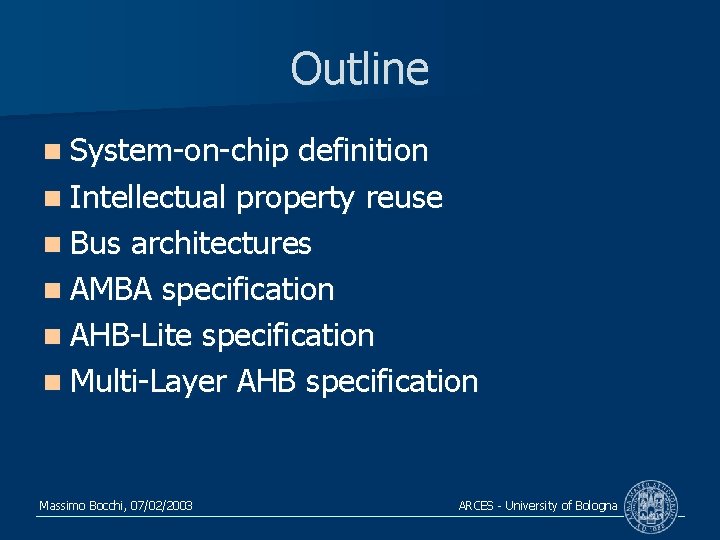

AHB-Lite specification Only one bus master is supported n The resulting system can be: n – a simple system containing only one bus master – a Multi-layer AHB system containing only one bus master per layer n AHB-Lite simplifies the full AHB specification: – no arbitration is required, since the Request/Grant protocol is not used – the AHB slaves don’t have to support Split/Retry responses Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

Outline n System-on-chip definition n Intellectual property reuse n Bus architectures n AMBA specification n AHB-Lite specification n Multi-Layer AHB specification Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

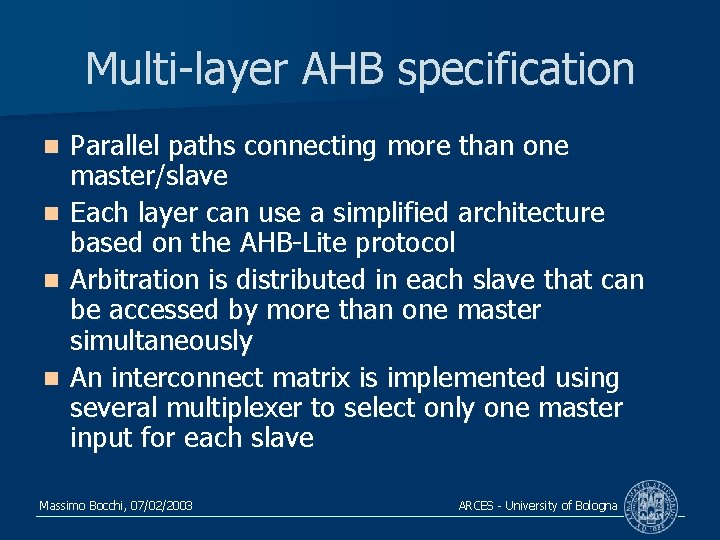

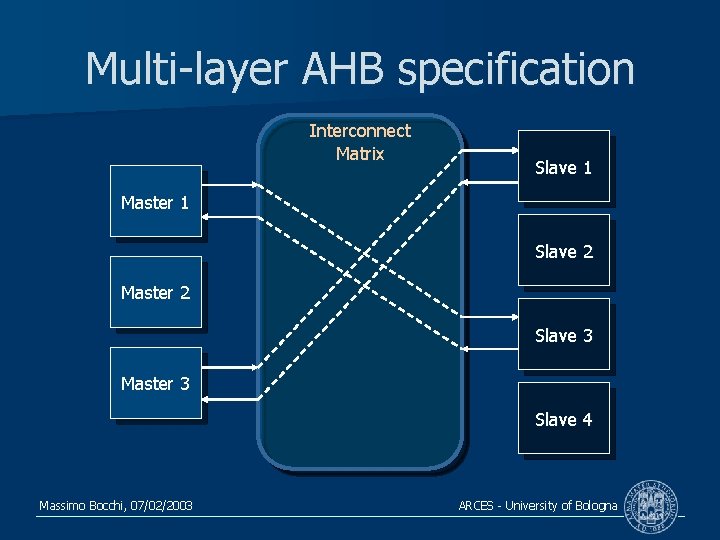

Multi-layer AHB specification Parallel paths connecting more than one master/slave n Each layer can use a simplified architecture based on the AHB-Lite protocol n Arbitration is distributed in each slave that can be accessed by more than one master simultaneously n An interconnect matrix is implemented using several multiplexer to select only one master input for each slave n Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

Multi-layer AHB specification Interconnect Matrix Slave 1 Master 1 Slave 2 Master 2 Slave 3 Master 3 Slave 4 Massimo Bocchi, 07/02/2003 ARCES - University of Bologna

- Slides: 28