Architectures des ordinateurs Processeur Philippe Bancquart Plan Architecture

Architectures des ordinateurs Processeur Philippe Bancquart

Plan Architecture d’un processeur Processeur 8086 Assembleur Pile et Procédures Systèmes d’exploitation et appels systèmes

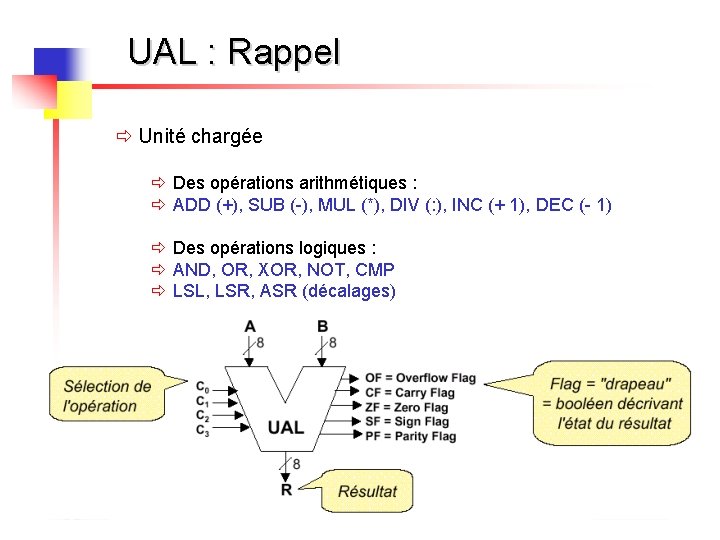

UAL : Rappel ð Unité chargée ð Des opérations arithmétiques : ð ADD (+), SUB (-), MUL (*), DIV (: ), INC (+ 1), DEC (- 1) ð Des opérations logiques : ð AND, OR, XOR, NOT, CMP ð LSL, LSR, ASR (décalages)

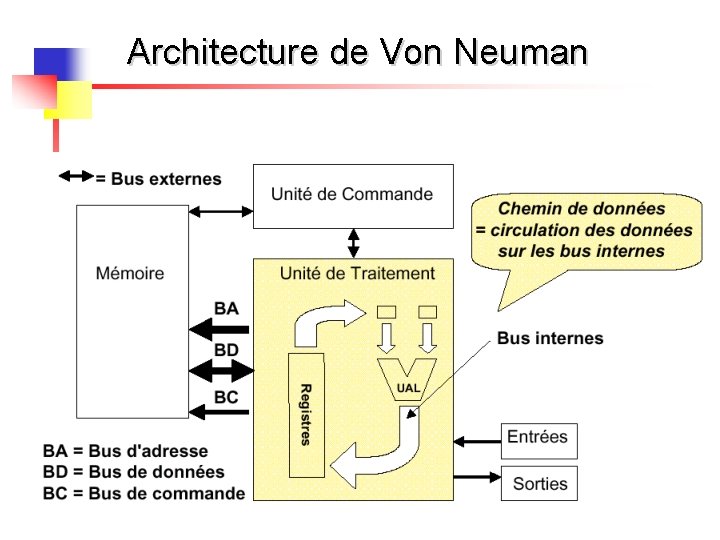

Architecture de Von Neuman

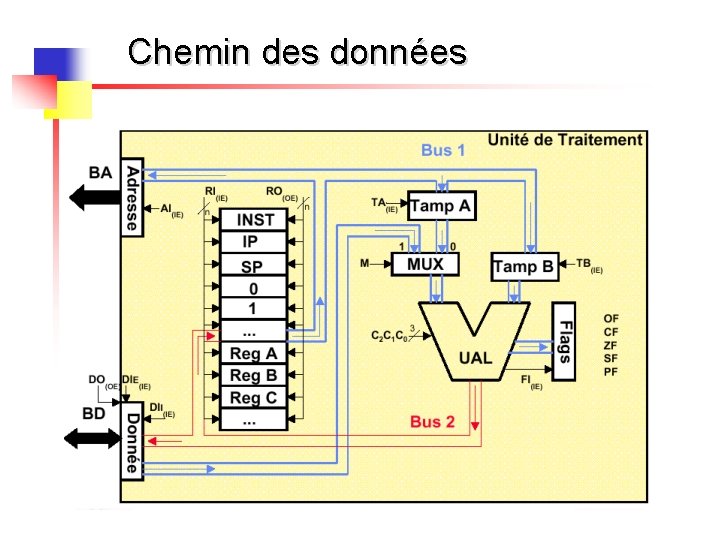

Chemin des données

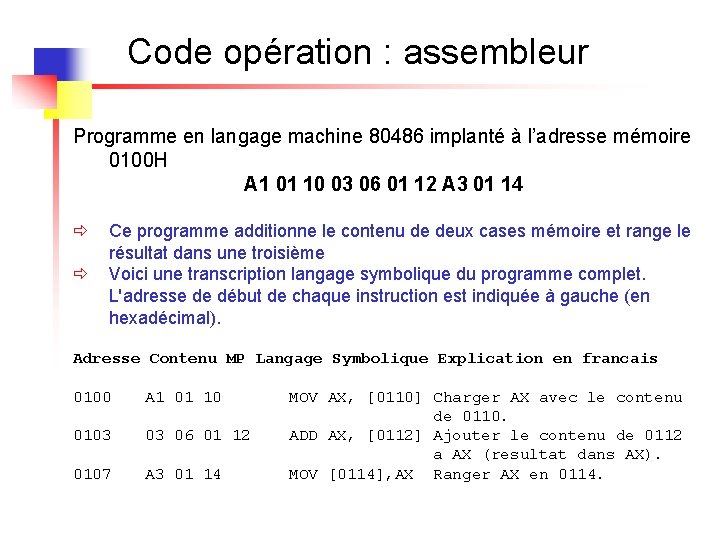

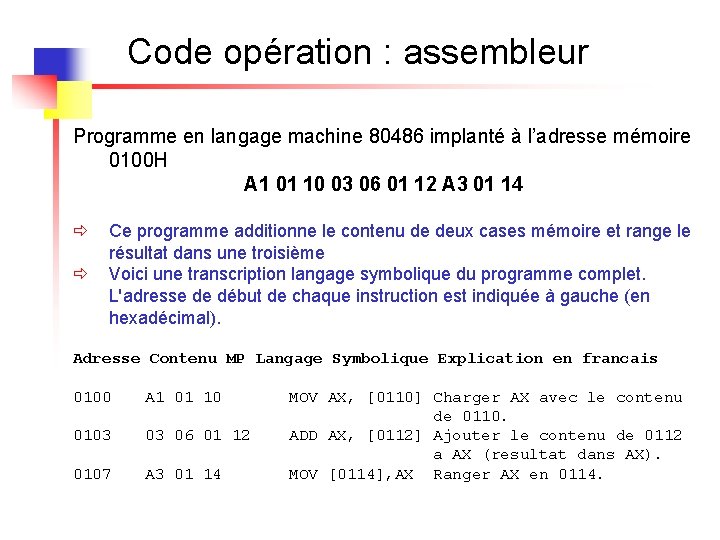

Code opération : assembleur Programme en langage machine 80486 implanté à l’adresse mémoire 0100 H A 1 01 10 03 06 01 12 A 3 01 14 ð ð Ce programme additionne le contenu de deux cases mémoire et range le résultat dans une troisième Voici une transcription langage symbolique du programme complet. L'adresse de début de chaque instruction est indiquée à gauche (en hexadécimal). Adresse Contenu MP Langage Symbolique Explication en francais 0100 A 1 01 10 0103 03 06 01 12 0107 A 3 01 14 MOV AX, [0110] Charger AX avec le contenu de 0110. ADD AX, [0112] Ajouter le contenu de 0112 a AX (resultat dans AX). MOV [0114], AX Ranger AX en 0114.

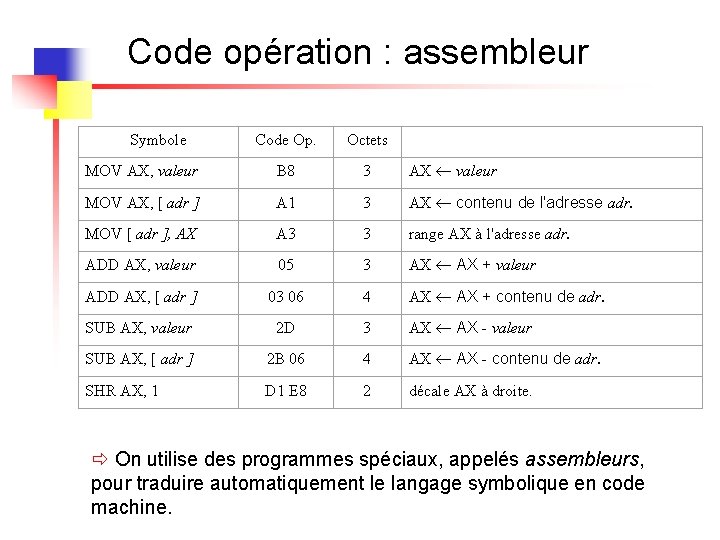

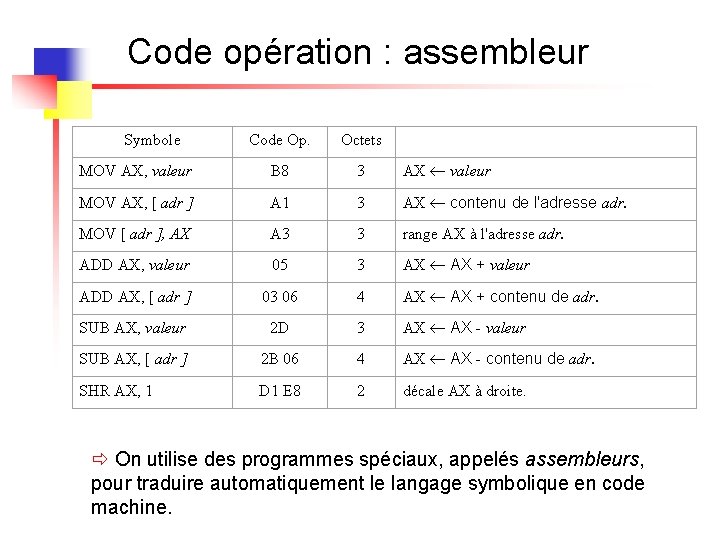

Code opération : assembleur Symbole Code Op. Octets MOV AX, valeur B 8 3 AX valeur MOV AX, [ adr ] A 1 3 AX contenu de l'adresse adr. MOV [ adr ], AX A 3 3 range AX à l'adresse adr. ADD AX, valeur 05 3 AX + valeur ADD AX, [ adr ] 03 06 4 AX + contenu de adr. SUB AX, valeur 2 D 3 AX - valeur SUB AX, [ adr ] 2 B 06 4 AX - contenu de adr. SHR AX, 1 D 1 E 8 2 décale AX à droite. ð On utilise des programmes spéciaux, appelés assembleurs, pour traduire automatiquement le langage symbolique en code machine.

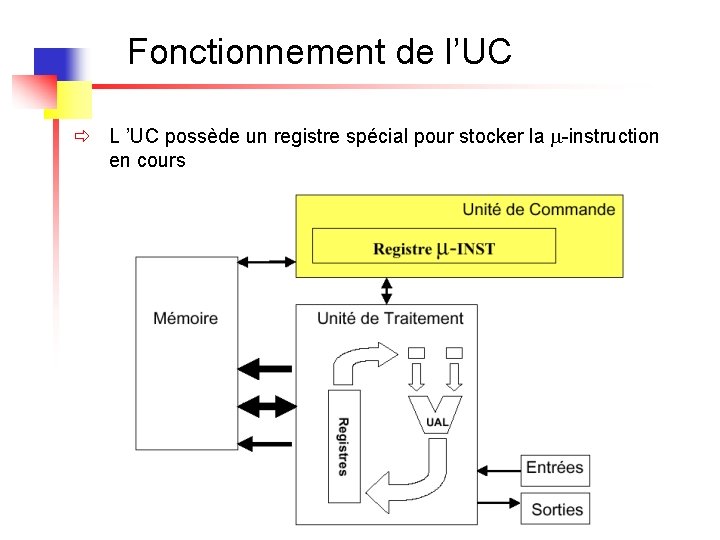

Fonctionnement de l’UC ð L ’UC possède un registre spécial pour stocker la -instruction en cours

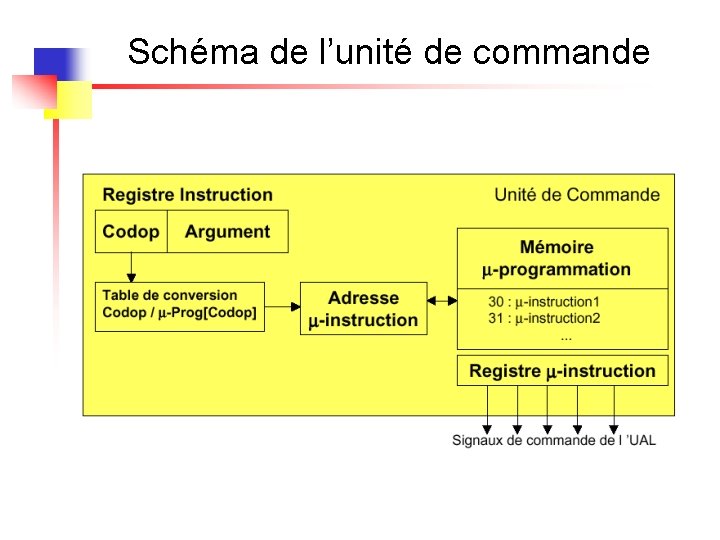

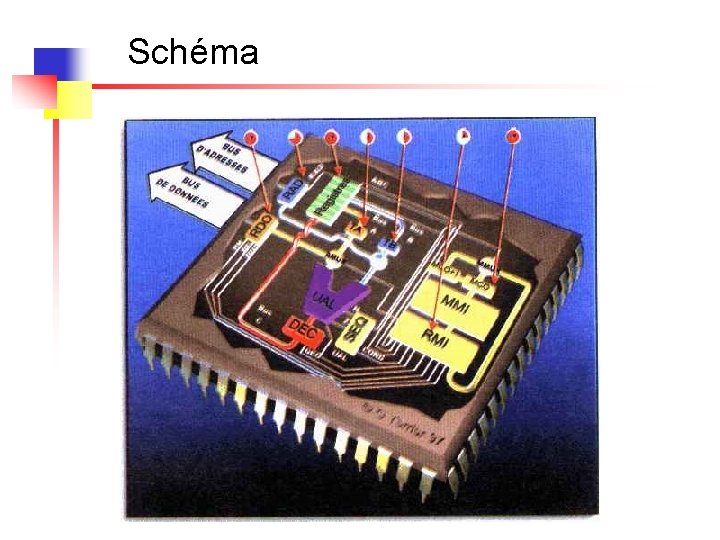

Schéma de l’unité de commande

Schéma

MMI, RMI et MCO ð MMI ou mémoire de micro-instructions = élément central de la logique de contrôle ð RMI (son registre associé) contient une micro instruction (tps t) ð La MMI, généralement une mémoire morte, contient toutes les micro-instructions qui sont nécessaires au processeur pour exécuter les instructions du langage machine. ð MCO, ou compteur ordinal du microprogramme : Il s'agit d'un registre qui contient l'adresse de la prochaine micro instruction à exécuter c'est-à-dire celle qui doit être placée dans le RMI, seul lieu où une micro instruction peut agir sur le circuit de données.

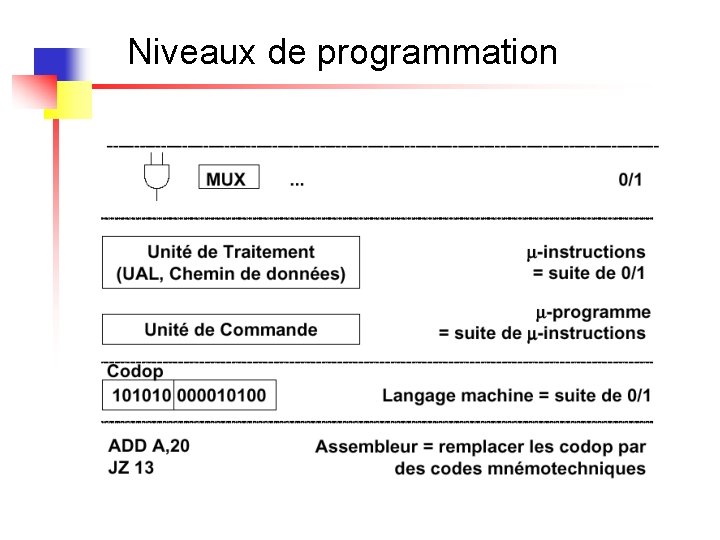

Niveaux de programmation

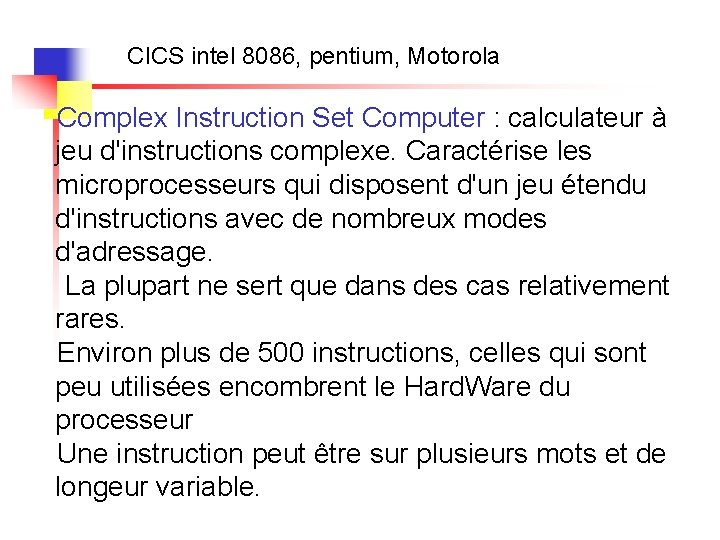

CICS intel 8086, pentium, Motorola Complex Instruction Set Computer : calculateur à jeu d'instructions complexe. Caractérise les microprocesseurs qui disposent d'un jeu étendu d'instructions avec de nombreux modes d'adressage. La plupart ne sert que dans des cas relativement rares. Environ plus de 500 instructions, celles qui sont peu utilisées encombrent le Hard. Ware du processeur Une instruction peut être sur plusieurs mots et de longeur variable.

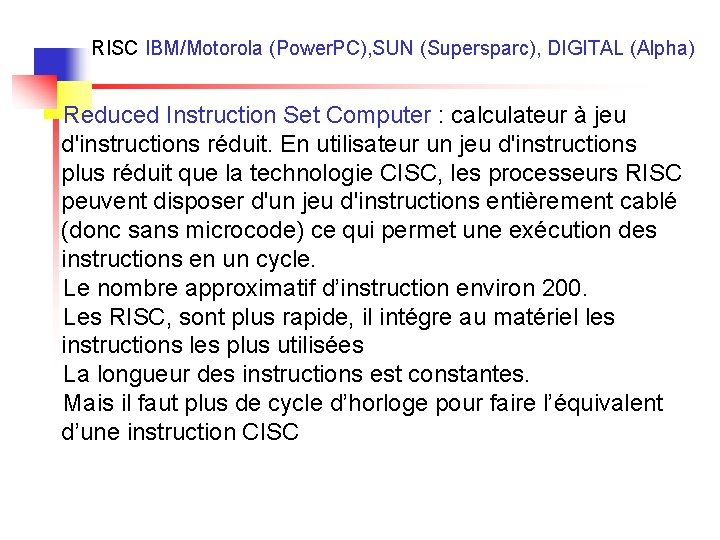

RISC IBM/Motorola (Power. PC), SUN (Supersparc), DIGITAL (Alpha) Reduced Instruction Set Computer : calculateur à jeu d'instructions réduit. En utilisateur un jeu d'instructions plus réduit que la technologie CISC, les processeurs RISC peuvent disposer d'un jeu d'instructions entièrement cablé (donc sans microcode) ce qui permet une exécution des instructions en un cycle. Le nombre approximatif d’instruction environ 200. Les RISC, sont plus rapide, il intégre au matériel les instructions les plus utilisées La longueur des instructions est constantes. Mais il faut plus de cycle d’horloge pour faire l’équivalent d’une instruction CISC

CICS / RISC Actuellement, les processeurs de type RISC sont plus performants que les CISC bien que ces derniers ne soient plus des CISC “purs”. On trouve plus souvent des hybrides incorporant différentes technologies: le pipeline (voir plus loin), le mariage du CISC et RISC comme dans le pentium pro (c'est un processeur RISC qui “traduit” les instructions CISC). On parle enfin d'architecture superscalaire (voir plus loin) quand un processeur RISC est capable d'exécuter plusieurs instructions simultanément en un seul cycle d'horloge.

La mémoire cache ð Depuis pas mal d'années, les circuits de mémoire ne sont plus assez rapides pour suivre la cadence des microprocesseurs ð ð ð on intercale entre le microprocesseur et la mémoire RAM, une autre mémoire allant à la même vitesse que le microprocesseur celle-ci est de taille assez réduite car elle coûte bien plus cher que la mémoire RAM standard souvent, il y a deux caches, un pour le programme et un pour les données ð Augmentation de la taille des bus d’adresses et de données ð ð Le micro-processeur est alimenté plus vite Bus d’adresse à 32 ou 64 bits = architecture à 32 ou 64 bits

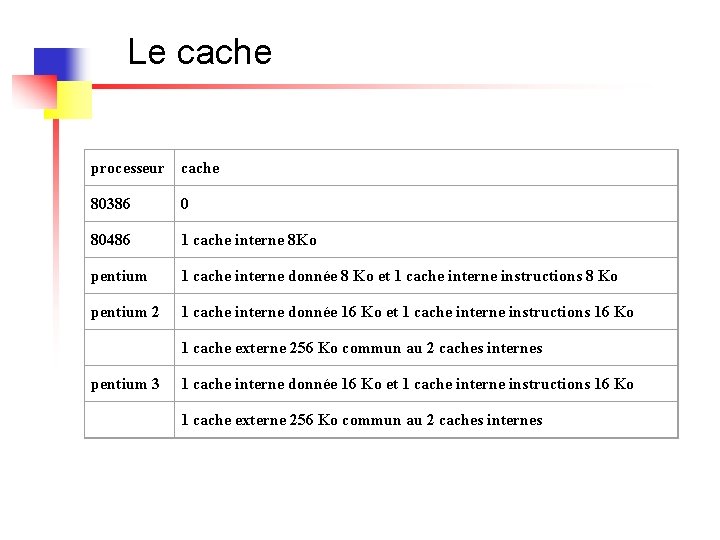

Le cache processeur cache 80386 0 80486 1 cache interne 8 Ko pentium 1 cache interne donnée 8 Ko et 1 cache interne instructions 8 Ko pentium 2 1 cache interne donnée 16 Ko et 1 cache interne instructions 16 Ko 1 cache externe 256 Ko commun au 2 caches internes pentium 3 1 cache interne donnée 16 Ko et 1 cache interne instructions 16 Ko 1 cache externe 256 Ko commun au 2 caches internes

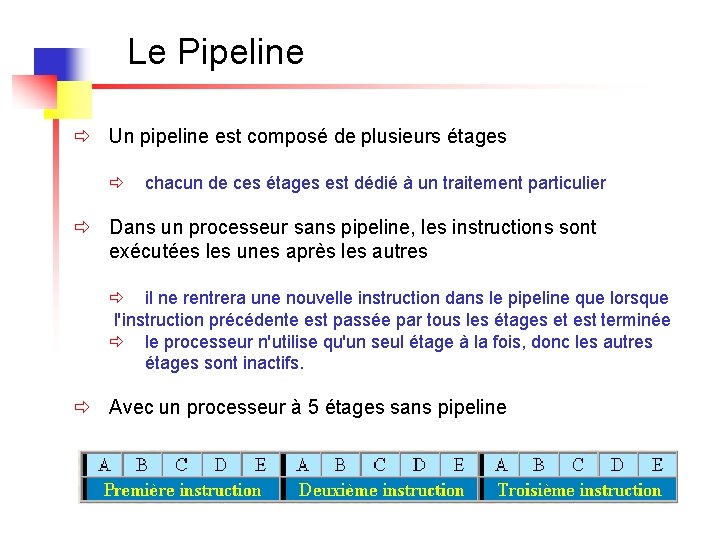

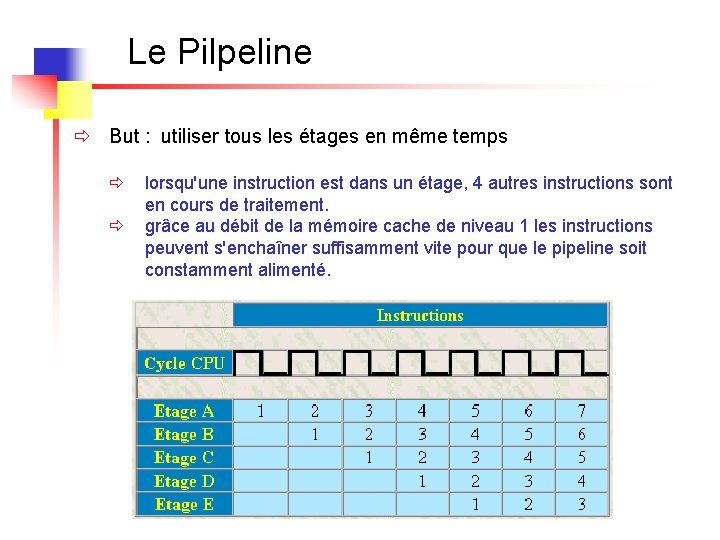

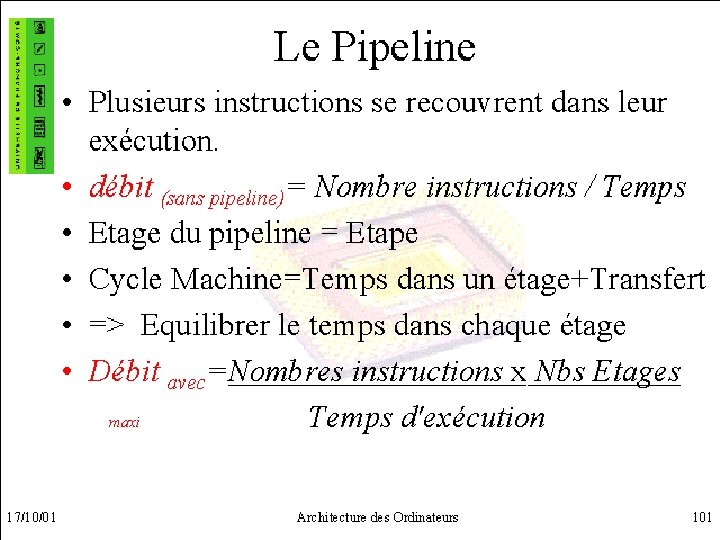

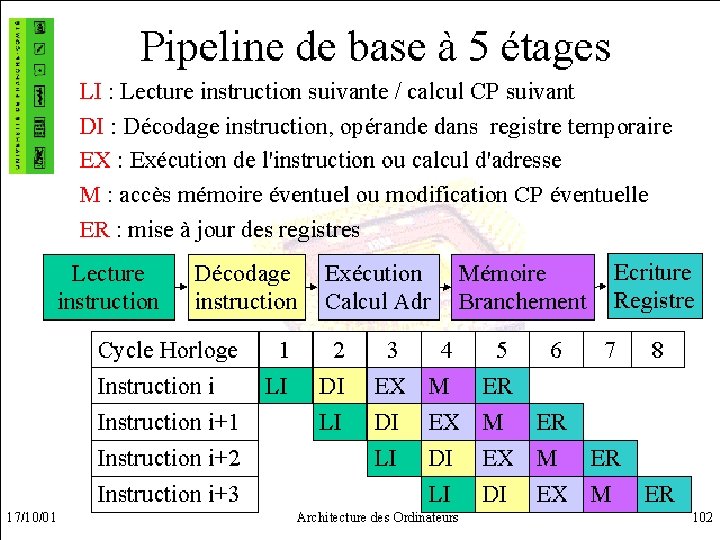

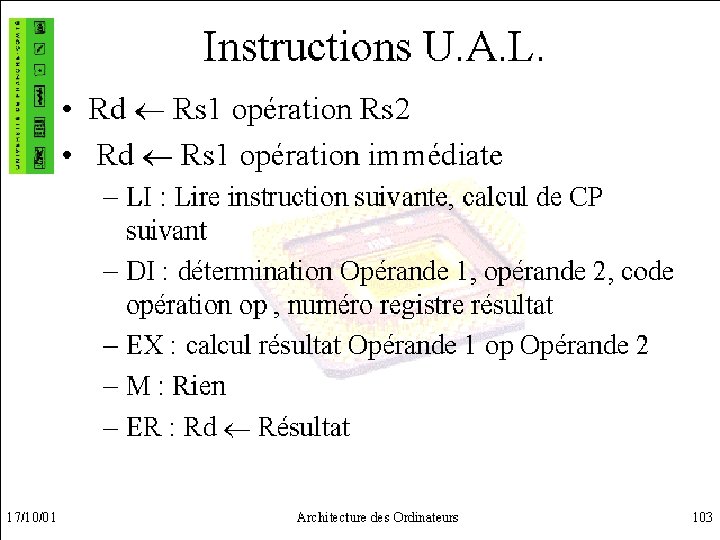

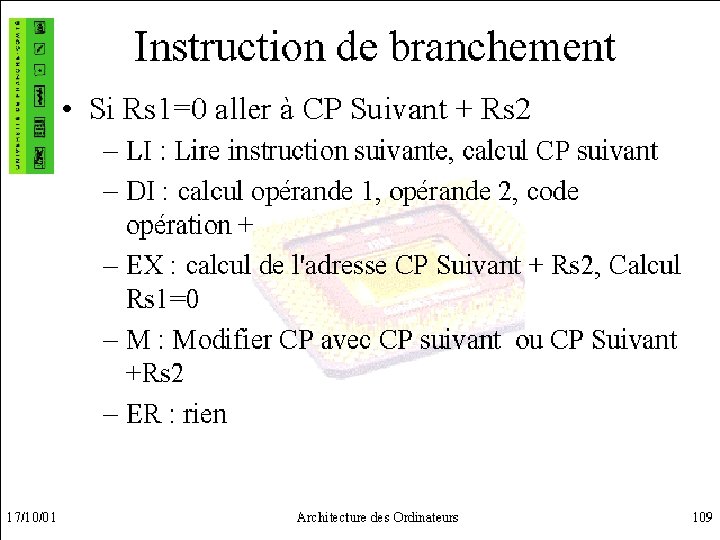

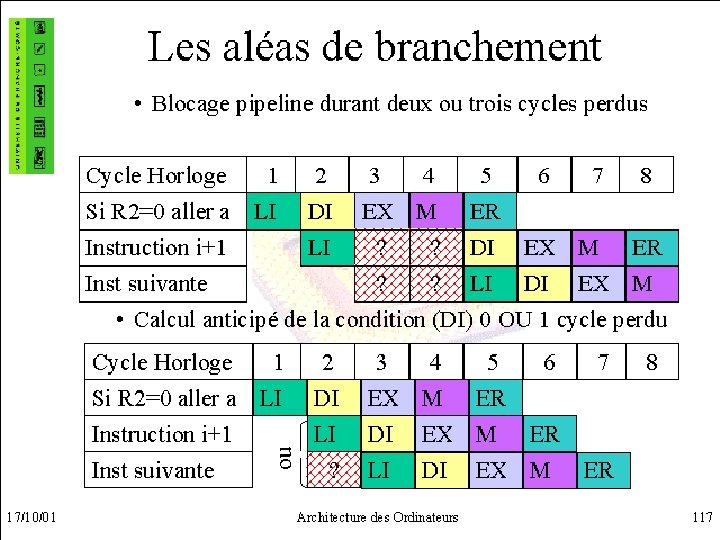

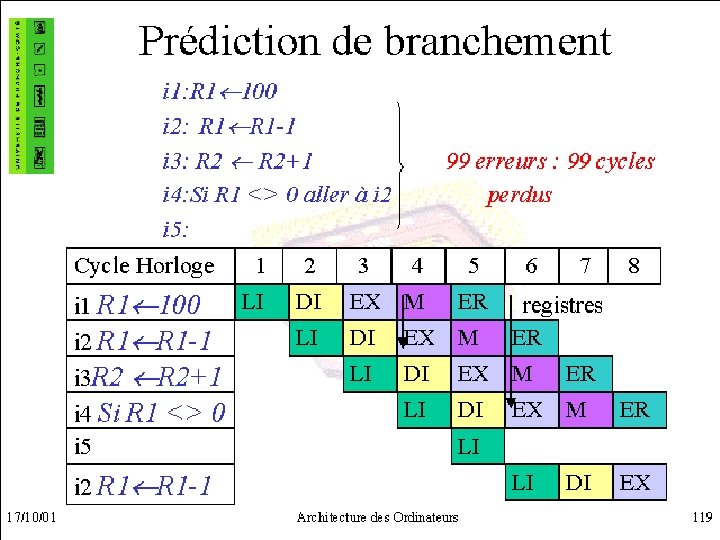

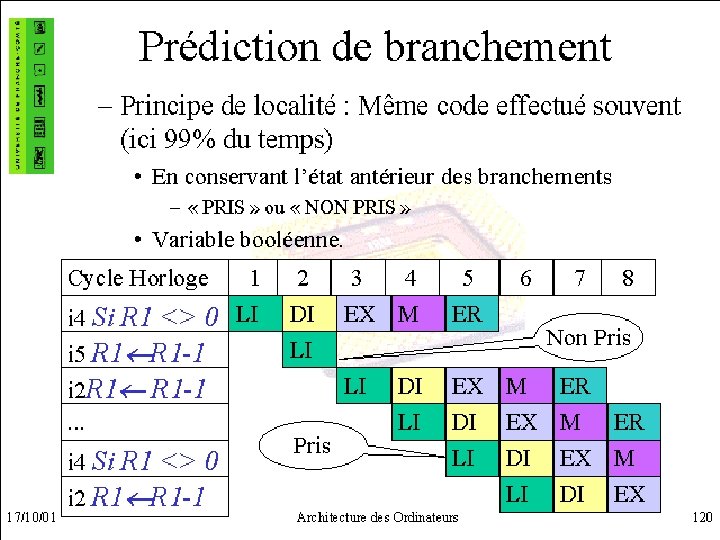

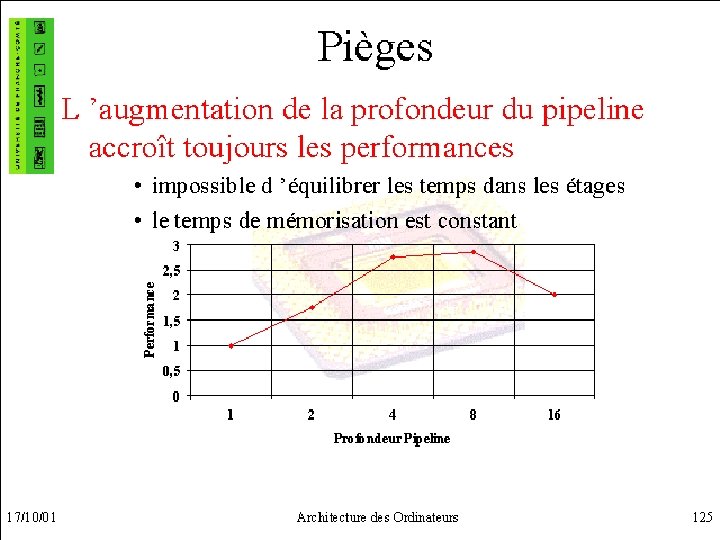

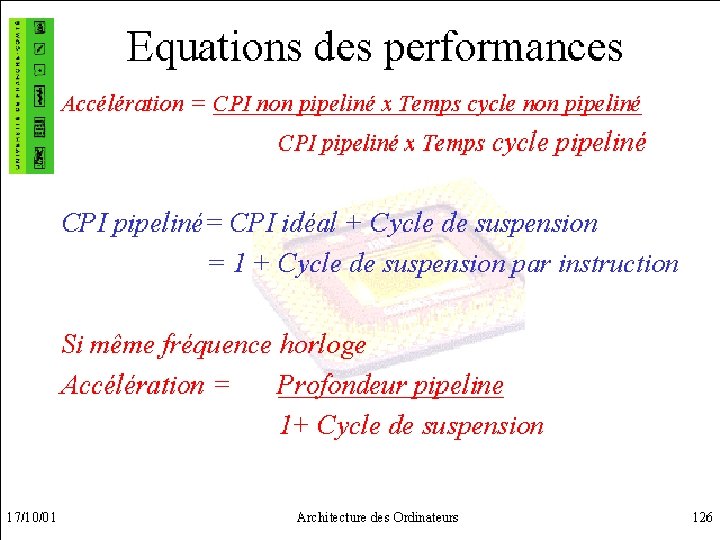

Le Pipeline ð Un pipeline est composé de plusieurs étages ð chacun de ces étages est dédié à un traitement particulier ð Dans un processeur sans pipeline, les instructions sont exécutées les unes après les autres ð il ne rentrera une nouvelle instruction dans le pipeline que lorsque l'instruction précédente est passée par tous les étages et est terminée ð le processeur n'utilise qu'un seul étage à la fois, donc les autres étages sont inactifs. ð Avec un processeur à 5 étages sans pipeline

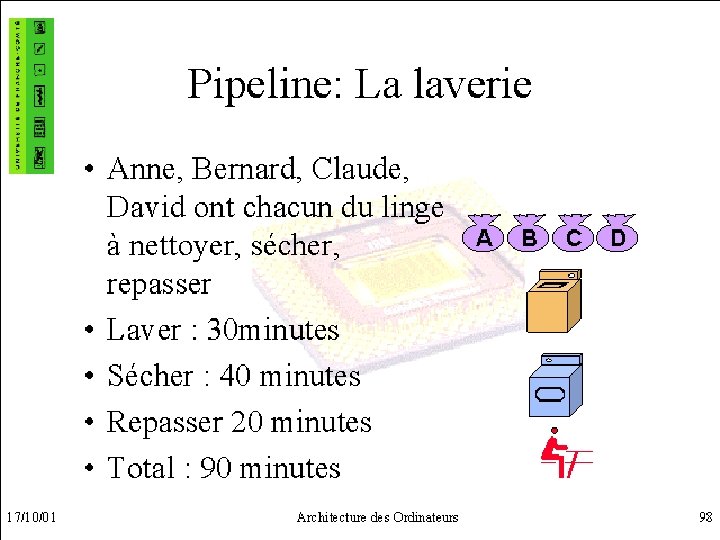

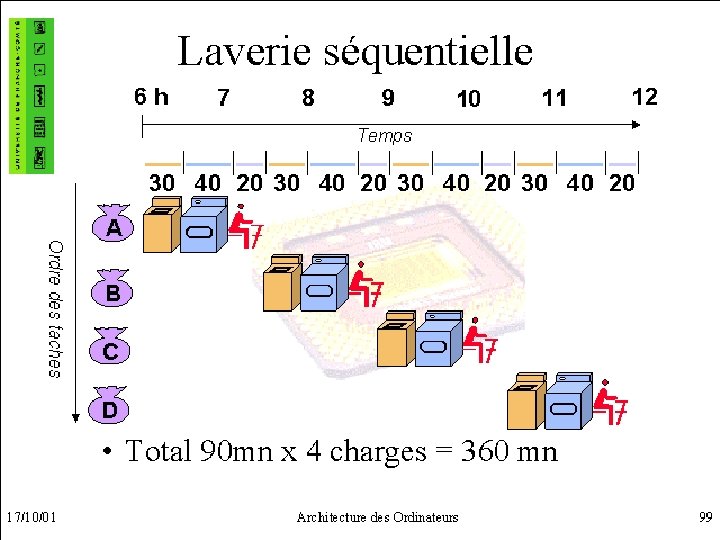

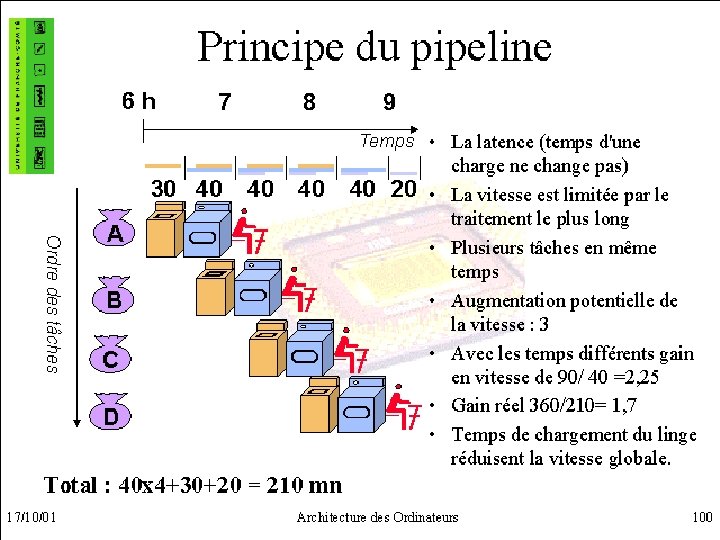

Le Pilpeline ð But : utiliser tous les étages en même temps ð ð lorsqu'une instruction est dans un étage, 4 autres instructions sont en cours de traitement. grâce au débit de la mémoire cache de niveau 1 les instructions peuvent s'enchaîner suffisamment vite pour que le pipeline soit constamment alimenté.

Processeurs superscalaires ð Un microprocesseur est de type superscalaire quand il intègre plus d'une unité entière (ALU) en con cœur. ð ð ð les deux unités sont indépendantes et fonctionnent en parallèle, chacune se charge d'exécuter une instruction sur deux. Il est ainsi possible d'exécuter deux instructions par cycle d'horloge.

Coprocesseurs mathématiques ð Jusqu'au 386, celui-ci était parfois assisté par un coprocesseur mathématique optionnel permettant d'accroître les capacités de calcul en virgule flottante (très ð utilisé par les tableurs et les logiciels de traitement graphique). ð Aujourd’hui, ce coprocesseur fait partie intégrante du CPU.

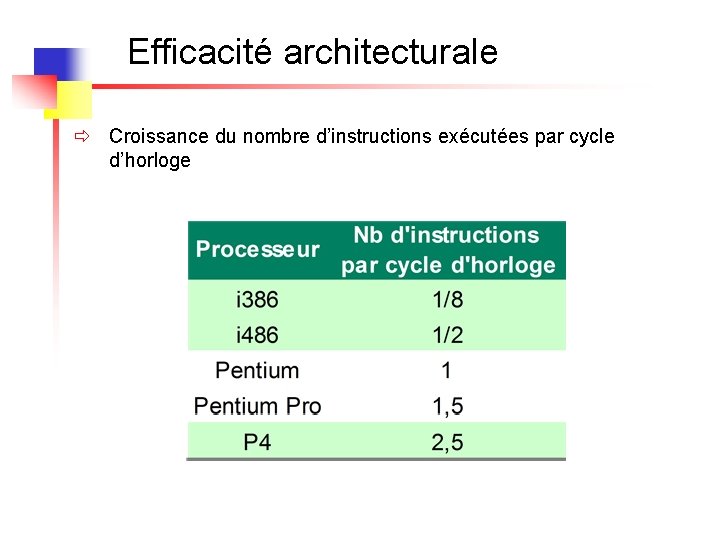

Efficacité architecturale ð Croissance du nombre d’instructions exécutées par cycle d’horloge

Plan Architecture d’un processeur Processeur 8086 Assembleur Pile et Procédures Systèmes d’exploitation et appels systèmes

Processeurs 80 x 86 ð Micro-processeurs 80 x 86 équipent les PC et compatibles ð ð Premiers PC (début 80) = 8086, micro-processeur 16 bits Puis 80286, 80386, 80486, Pentium… Augmentation de la fréquence d’horloge, de la largeur des bus d’adresses et de données Ajout de nouvelles instructions et de registres ð Compatibilité ascendante ð ð Un programme écrit dans le langage machine du 286 peut s’exécuter sur un 386 (l’inverse est faux) En TP on utilisera un assembleur 8086 et on exécutera le programme sur les Pentium de l’IUT

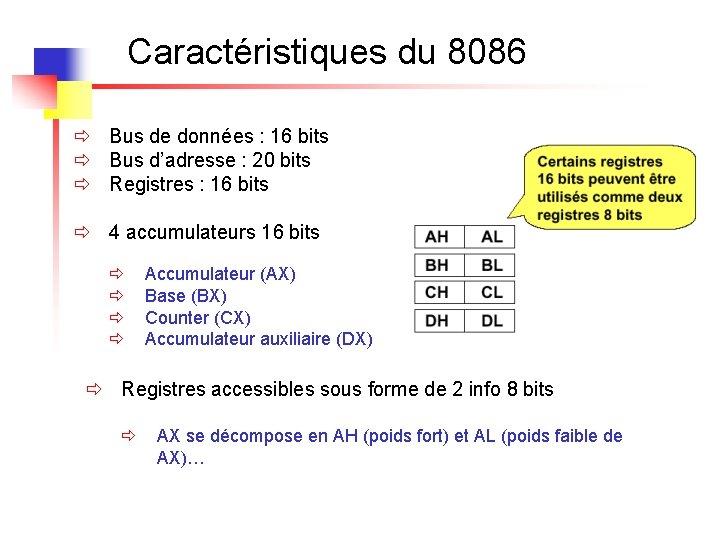

Caractéristiques du 8086 ð Bus de données : 16 bits ð Bus d’adresse : 20 bits ð Registres : 16 bits ð 4 accumulateurs 16 bits ð ð Accumulateur (AX) Base (BX) Counter (CX) Accumulateur auxiliaire (DX) ð Registres accessibles sous forme de 2 info 8 bits ð AX se décompose en AH (poids fort) et AL (poids faible de AX)…

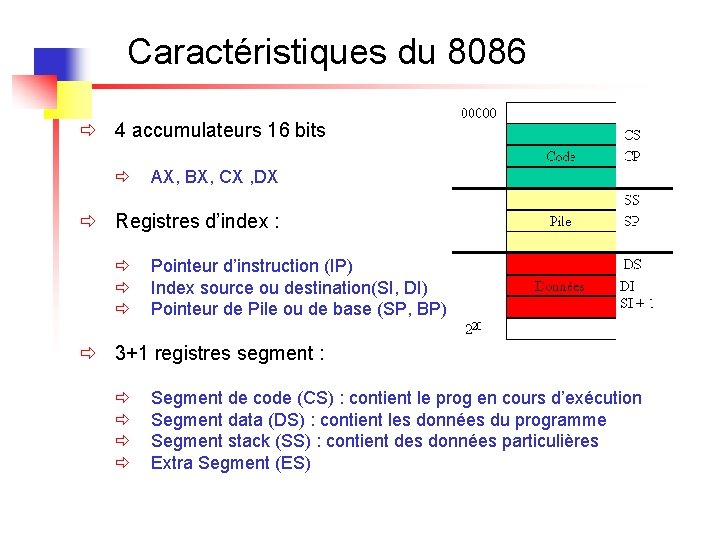

Caractéristiques du 8086 ð 4 accumulateurs 16 bits ð AX, BX, CX , DX ð Registres d’index : ð ð ð Pointeur d’instruction (IP) Index source ou destination(SI, DI) Pointeur de Pile ou de base (SP, BP) ð 3+1 registres segment : ð ð Segment de code (CS) : contient le prog en cours d’exécution Segment data (DS) : contient les données du programme Segment stack (SS) : contient des données particulières Extra Segment (ES)

Segmentation de la mémoire ð Largeur du bus d’adresse = 20 bits ð Possibilité d’adressage mémoire = 220 = 1 Mo ð Le pointeur d’instruction fait 16 bits ð Possibilité d’adresser 216 = 64 Ko (ce qui ne couvre pas la mémoire) ð On utilise deux registres pour indiquer une adresse au processeur ð ð Chaque segment débute à l'endroit spécifié par un registre spécial nommé registre segment. Le déplacement permet de trouver une information à l'intérieur du segment. CS: IP : lecture du code d’une instruction (CS registre segment et IP déplacement) DS : accès aux données (MOV AX, [1045] = lecture du mot mémoire d’adresse DS: 1045 H)

Segmentation de la mémoire ð Registres de déplacement = sélectionner une information dans un segment. ð Dans le segment de code CS : le compteur de programme IP joue ce rôle. CS: IP permet d'accéder à une information dans le segment de code. ð Dans les segments de DS : les deux index SI ou DI jouent ce rôle. Le déplacement peut être aussi une constante. DS: SI ou DS: DI permettent d'accéder à une information dans le segment de données. ð Dans le segment de pile SS le registre SP (stack pointer) et BP (base pointer) jouent ce rôle. SS: SP ou SS: BP permettent d'accéder à une information dans le segment de pile.

Jeu d’instruction (1) ð Instruction d’affectation (Transfert CPU Mémoire) : MOV ð Instructions arithmétiques : INC (incrémentation) (Opération Acc / Donnée) : DEC (décrementation) : ADD (addition) : SUB (soustraction) : CMP (soustraction sans sauvegarde) : NEG ð Instructions logiques : NOT, OR, XOR : AND, TEST (= AND sans sauvegarde) : SHL (SHR), SAL (SAR) : ROL (ROR), RCL (RCR)

Jeu d’instruction (2) ð Branchements conditionnels : JMP : JE/ JZ (JNE/ JNZ) : Jump if zero : JO (JNO) : Jump if overflow : JS (JNS) : Jump if sign ð Comparaison de valeurs CMP AX, BX suivi d ’un test : AX > BX ? AX < BX ? (entiers naturels) JA ( >= JAE) JB (JBE) (complément à 2) JG (JGE) JL (JLE)

Branchements ð Le processeur exécute une instruction en mémoire puis passe à celle qui suit en mémoire : séquentiel ð ð Besoin de faire répéter au processeur une suite d’instructions Besoin de déclencher une action qui dépend d’un test ð Utilisation d’une instruction de branchement ou saut ð On indique au processeur l’adresse de la prochaine instruction ð On distingue deux catégories de branchements ð ð le saut est toujours effectué (sauts inconditionnels) il est effectué seulement si une condition est vérifiée (sauts conditionnels).

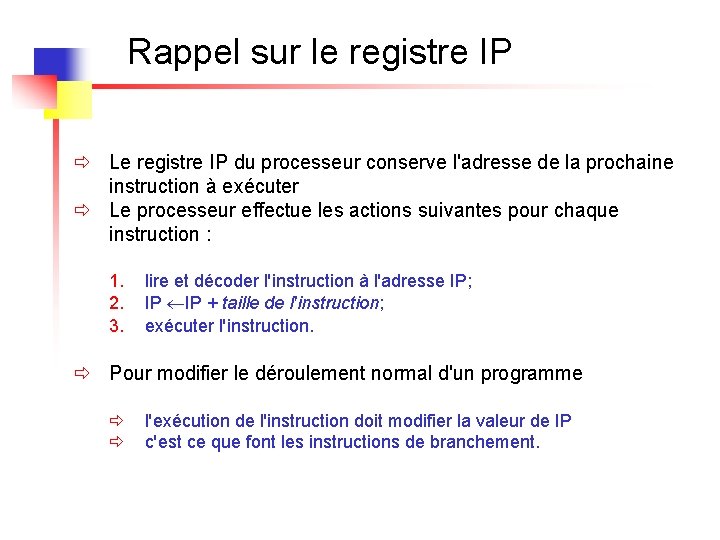

Rappel sur le registre IP ð Le registre IP du processeur conserve l'adresse de la prochaine instruction à exécuter ð Le processeur effectue les actions suivantes pour chaque instruction : 1. 2. 3. lire et décoder l'instruction à l'adresse IP; IP IP + taille de l'instruction; exécuter l'instruction. ð Pour modifier le déroulement normal d'un programme ð ð l'exécution de l'instruction doit modifier la valeur de IP c'est ce que font les instructions de branchement.

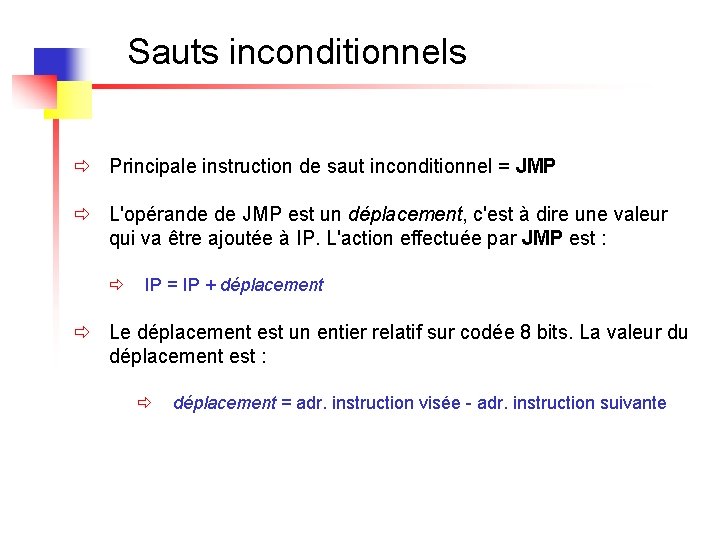

Sauts inconditionnels ð Principale instruction de saut inconditionnel = JMP ð L'opérande de JMP est un déplacement, c'est à dire une valeur qui va être ajoutée à IP. L'action effectuée par JMP est : ð IP = IP + déplacement ð Le déplacement est un entier relatif sur codée 8 bits. La valeur du déplacement est : ð déplacement = adr. instruction visée - adr. instruction suivante

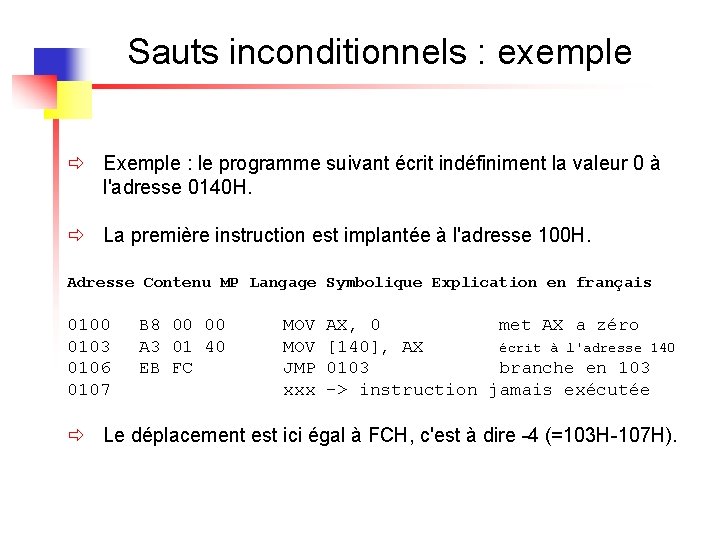

Sauts inconditionnels : exemple ð Exemple : le programme suivant écrit indéfiniment la valeur 0 à l'adresse 0140 H. ð La première instruction est implantée à l'adresse 100 H. Adresse Contenu MP Langage Symbolique Explication en français 0100 0103 0106 0107 B 8 00 00 A 3 01 40 EB FC MOV AX, 0 met AX a zéro MOV [140], AX écrit à l'adresse 140 JMP 0103 branche en 103 xxx -> instruction jamais exécutée ð Le déplacement est ici égal à FCH, c'est à dire -4 (=103 H-107 H).

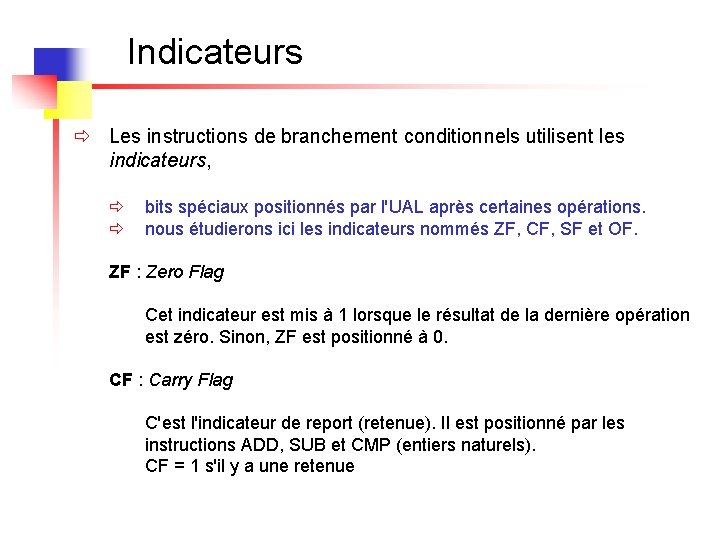

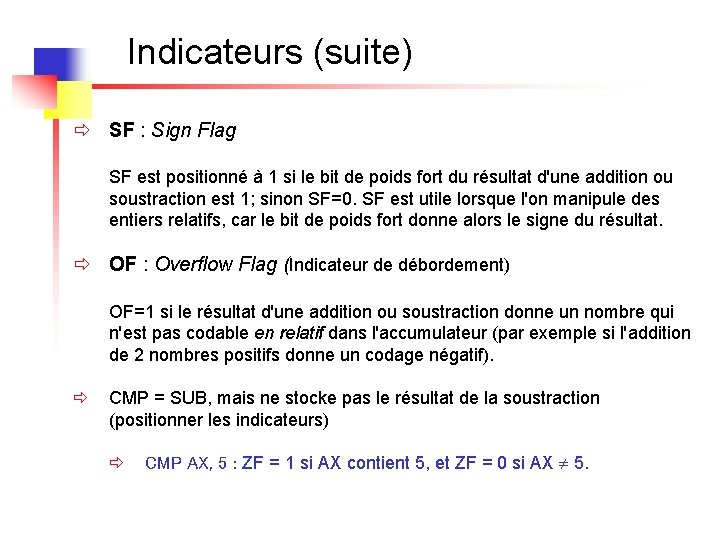

Indicateurs ð Les instructions de branchement conditionnels utilisent les indicateurs, ð ð bits spéciaux positionnés par l'UAL après certaines opérations. nous étudierons ici les indicateurs nommés ZF, CF, SF et OF. ZF : Zero Flag Cet indicateur est mis à 1 lorsque le résultat de la dernière opération est zéro. Sinon, ZF est positionné à 0. CF : Carry Flag C'est l'indicateur de report (retenue). Il est positionné par les instructions ADD, SUB et CMP (entiers naturels). CF = 1 s'il y a une retenue

Indicateurs (suite) ð SF : Sign Flag SF est positionné à 1 si le bit de poids fort du résultat d'une addition ou soustraction est 1; sinon SF=0. SF est utile lorsque l'on manipule des entiers relatifs, car le bit de poids fort donne alors le signe du résultat. ð OF : Overflow Flag (Indicateur de débordement) OF=1 si le résultat d'une addition ou soustraction donne un nombre qui n'est pas codable en relatif dans l'accumulateur (par exemple si l'addition de 2 nombres positifs donne un codage négatif). ð CMP = SUB, mais ne stocke pas le résultat de la soustraction (positionner les indicateurs) ð CMP AX, 5 : ZF = 1 si AX contient 5, et ZF = 0 si AX 5.

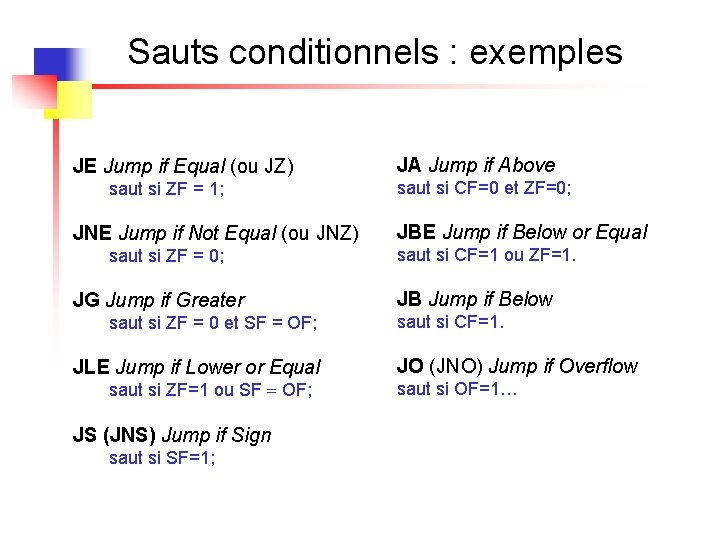

Sauts conditionnels : exemples JE Jump if Equal (ou JZ) saut si ZF = 1; JNE Jump if Not Equal (ou JNZ) saut si ZF = 0; JG Jump if Greater saut si ZF = 0 et SF = OF; JLE Jump if Lower or Equal saut si ZF=1 ou SF = OF; JS (JNS) Jump if Sign saut si SF=1; JA Jump if Above saut si CF=0 et ZF=0; JBE Jump if Below or Equal saut si CF=1 ou ZF=1. JB Jump if Below saut si CF=1. JO (JNO) Jump if Overflow saut si OF=1…

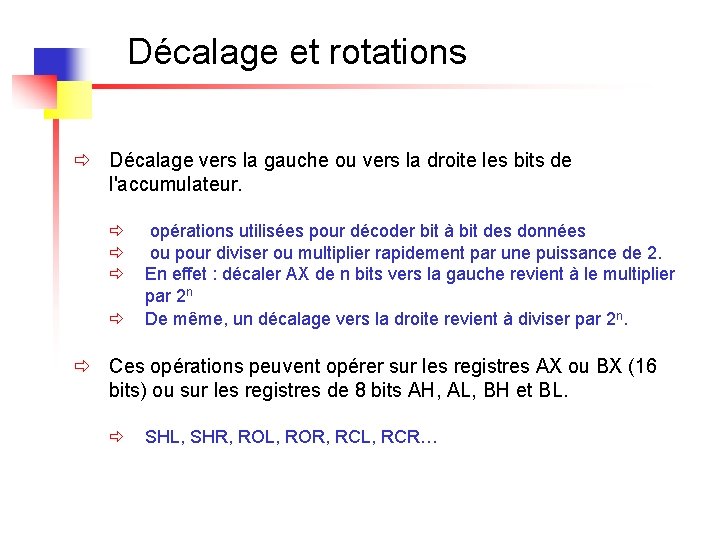

Décalage et rotations ð Décalage vers la gauche ou vers la droite les bits de l'accumulateur. ð ð opérations utilisées pour décoder bit à bit des données ou pour diviser ou multiplier rapidement par une puissance de 2. En effet : décaler AX de n bits vers la gauche revient à le multiplier par 2 n De même, un décalage vers la droite revient à diviser par 2 n. ð Ces opérations peuvent opérer sur les registres AX ou BX (16 bits) ou sur les registres de 8 bits AH, AL, BH et BL. ð SHL, SHR, ROL, ROR, RCL, RCR…

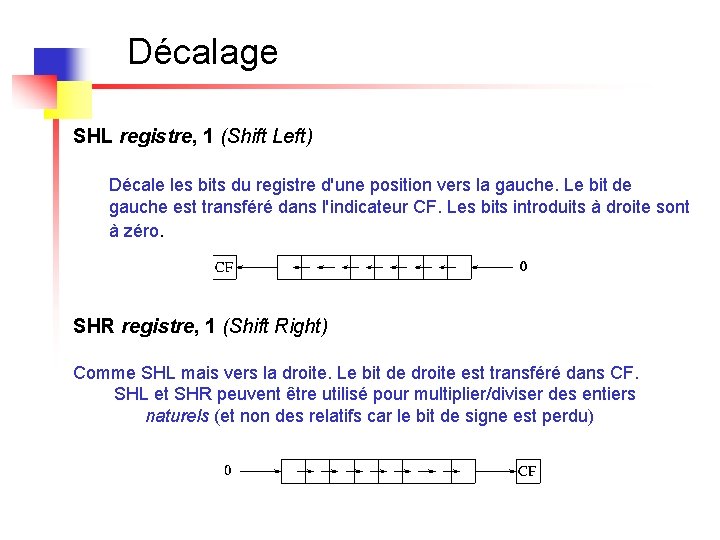

Décalage SHL registre, 1 (Shift Left) Décale les bits du registre d'une position vers la gauche. Le bit de gauche est transféré dans l'indicateur CF. Les bits introduits à droite sont à zéro. SHR registre, 1 (Shift Right) Comme SHL mais vers la droite. Le bit de droite est transféré dans CF. SHL et SHR peuvent être utilisé pour multiplier/diviser des entiers naturels (et non des relatifs car le bit de signe est perdu)

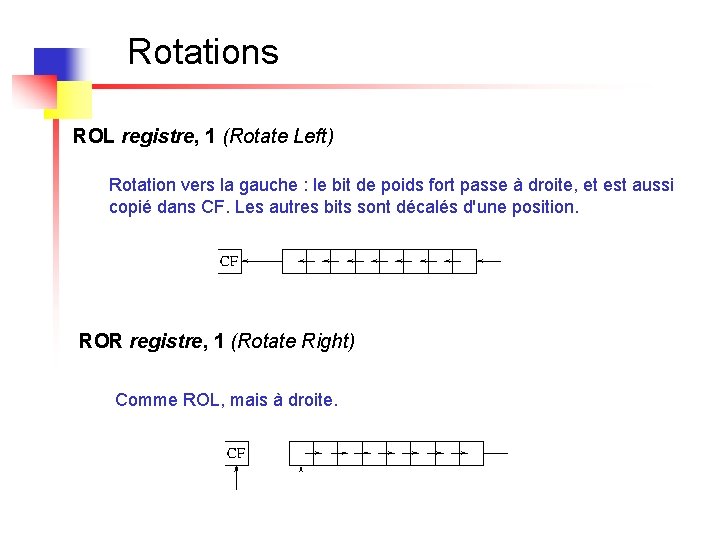

Rotations ROL registre, 1 (Rotate Left) Rotation vers la gauche : le bit de poids fort passe à droite, et est aussi copié dans CF. Les autres bits sont décalés d'une position. ROR registre, 1 (Rotate Right) Comme ROL, mais à droite.

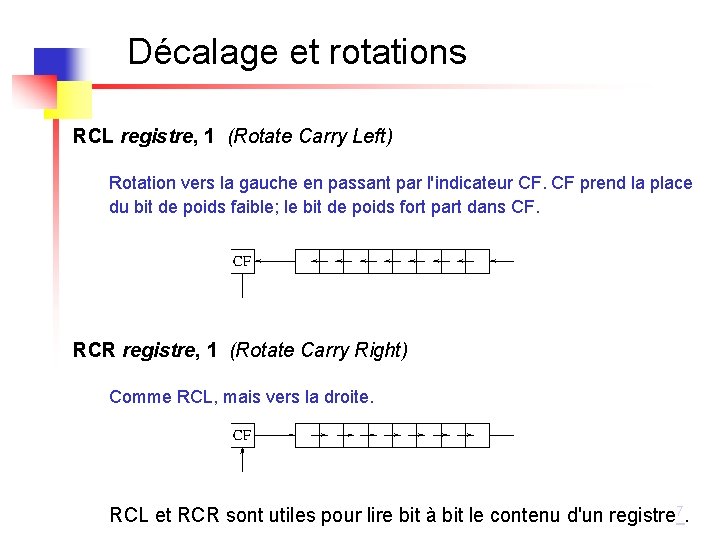

Décalage et rotations RCL registre, 1 (Rotate Carry Left) Rotation vers la gauche en passant par l'indicateur CF. CF prend la place du bit de poids faible; le bit de poids fort part dans CF. RCR registre, 1 (Rotate Carry Right) Comme RCL, mais vers la droite. RCL et RCR sont utiles pour lire bit à bit le contenu d'un registre 7.

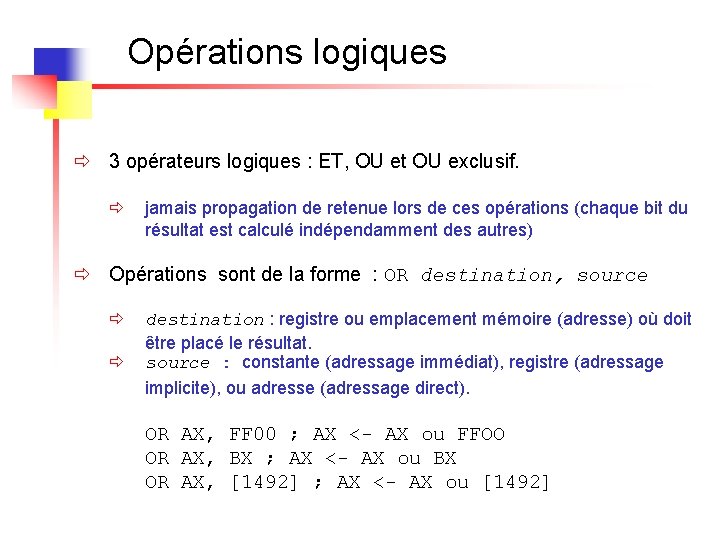

Opérations logiques ð 3 opérateurs logiques : ET, OU et OU exclusif. ð jamais propagation de retenue lors de ces opérations (chaque bit du résultat est calculé indépendamment des autres) ð Opérations sont de la forme : OR destination, source ð ð destination : registre ou emplacement mémoire (adresse) où doit être placé le résultat. source : constante (adressage immédiat), registre (adressage implicite), ou adresse (adressage direct). OR AX, FF 00 ; AX <- AX ou FFOO OR AX, BX ; AX <- AX ou BX OR AX, [1492] ; AX <- AX ou [1492]

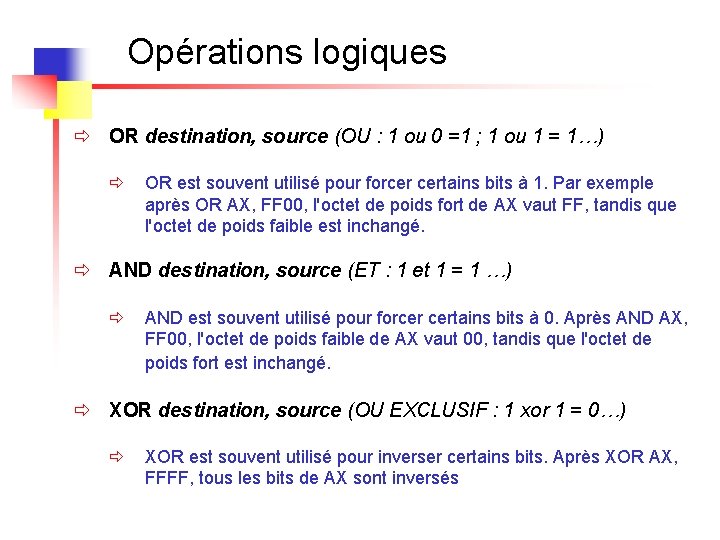

Opérations logiques ð OR destination, source (OU : 1 ou 0 =1 ; 1 ou 1 = 1…) ð OR est souvent utilisé pour forcer certains bits à 1. Par exemple après OR AX, FF 00, l'octet de poids fort de AX vaut FF, tandis que l'octet de poids faible est inchangé. ð AND destination, source (ET : 1 et 1 = 1 …) ð AND est souvent utilisé pour forcer certains bits à 0. Après AND AX, FF 00, l'octet de poids faible de AX vaut 00, tandis que l'octet de poids fort est inchangé. ð XOR destination, source (OU EXCLUSIF : 1 xor 1 = 0…) ð XOR est souvent utilisé pour inverser certains bits. Après XOR AX, FFFF, tous les bits de AX sont inversés

Codage ð Les instructions et leurs opérandes (paramètres) sont stockés en mémoire principale ð La taille totale d'une instruction (nombre de bits nécessaires pour la représenter en mémoire) dépend du type d'instruction et aussi du type d'opérande. ð Chaque instruction est toujours codée sur un nombre entier d'octets, afin de faciliter son décodage par le processeur. Une instruction est composée de deux champs : ð ð le code opération, qui indique au processeur quelle instruction réaliser; le champ opérande qui contient la donnée, ou la référence à une donnée en mémoire (son adresse).

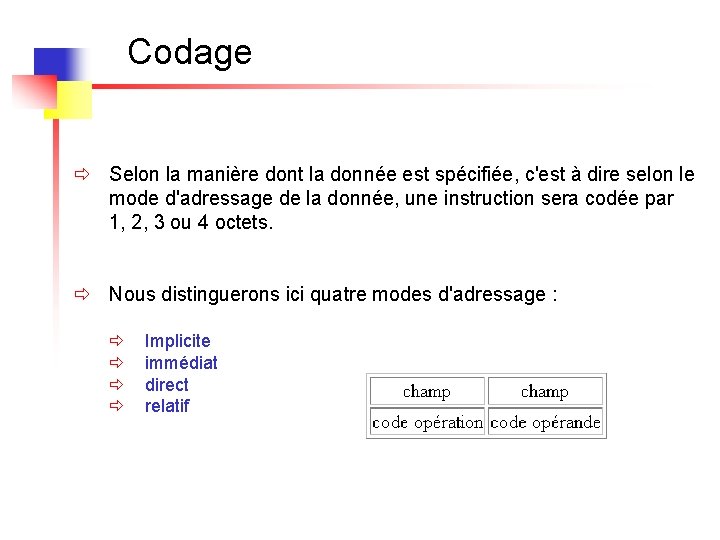

Codage ð Selon la manière dont la donnée est spécifiée, c'est à dire selon le mode d'adressage de la donnée, une instruction sera codée par 1, 2, 3 ou 4 octets. ð Nous distinguerons ici quatre modes d'adressage : ð ð Implicite immédiat direct relatif

Types d’adressage ð Adressage implicite ou par registre ADD AX, BX INC AX Pas d’accès mémoire pour les opérandes L'instruction contient seulement le code opération, sur 1 ou 2 octets. L'instruction porte sur des registres ou spécifie une opération sans opérande

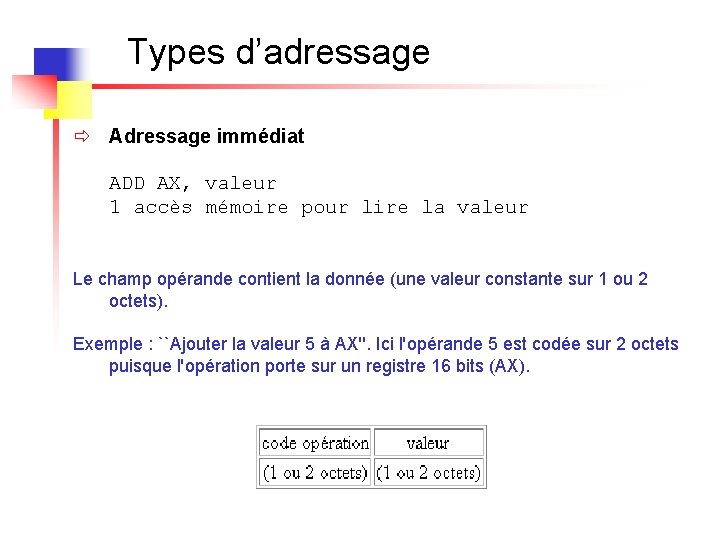

Types d’adressage ð Adressage immédiat ADD AX, valeur 1 accès mémoire pour lire la valeur Le champ opérande contient la donnée (une valeur constante sur 1 ou 2 octets). Exemple : ``Ajouter la valeur 5 à AX''. Ici l'opérande 5 est codée sur 2 octets puisque l'opération porte sur un registre 16 bits (AX).

![Types d’adressage ð Adressage direct ADD AX, [adresse] 2 accès mémoire : adresse puis Types d’adressage ð Adressage direct ADD AX, [adresse] 2 accès mémoire : adresse puis](http://slidetodoc.com/presentation_image_h/1a70718a682f21e59b5e3c5fbded7e90/image-60.jpg)

Types d’adressage ð Adressage direct ADD AX, [adresse] 2 accès mémoire : adresse puis valeur Le champ opérande contient l'adresse de la donnée en mémoire principale sur 2 octets. Attention : dans le 80 x 86, les adresses sont toujours manipulées sur 16 bits, quelle que soit la taille réelle du bus. Exemple : ``Placer dans AX la valeur contenue à l'adresse 130 H''.

![Types d’adressage ð Adressage relatif ou indexé ADD AX, [adresse+index] MOV AX, [SI+1] ð Types d’adressage ð Adressage relatif ou indexé ADD AX, [adresse+index] MOV AX, [SI+1] ð](http://slidetodoc.com/presentation_image_h/1a70718a682f21e59b5e3c5fbded7e90/image-61.jpg)

Types d’adressage ð Adressage relatif ou indexé ADD AX, [adresse+index] MOV AX, [SI+1] ð 2 accès mémoire Ce mode d'adressage est utilisé pour certaines instructions de branchement. Le champ opérande contient un entier relatif codé sur 1 octet, nommé déplacement, qui sera ajouté à la valeur courante de IP.

Plan Architecture d’un processeur Processeur 8086 Assembleur Pile et Procédures Systèmes d’exploitation et appels systèmes

Code opération : assembleur Programme en langage machine 80486 implanté à l’adresse mémoire 0100 H A 1 01 10 03 06 01 12 A 3 01 14 ð ð Ce programme additionne le contenu de deux cases mémoire et range le résultat dans une troisième Voici une transcription langage symbolique du programme complet. L'adresse de début de chaque instruction est indiquée à gauche (en hexadécimal). Adresse Contenu MP Langage Symbolique Explication en francais 0100 A 1 01 10 0103 03 06 01 12 0107 A 3 01 14 MOV AX, [0110] Charger AX avec le contenu de 0110. ADD AX, [0112] Ajouter le contenu de 0112 a AX (resultat dans AX). MOV [0114], AX Ranger AX en 0114.

Code opération : assembleur Symbole Code Op. Octets MOV AX, valeur B 8 3 AX valeur MOV AX, [ adr ] A 1 3 AX contenu de l'adresse adr. MOV [ adr ], AX A 3 3 range AX à l'adresse adr. ADD AX, valeur 05 3 AX + valeur ADD AX, [ adr ] 03 06 4 AX + contenu de adr. SUB AX, valeur 2 D 3 AX - valeur SUB AX, [ adr ] 2 B 06 4 AX - contenu de adr. SHR AX, 1 D 1 E 8 2 décale AX à droite. ð On utilise des programmes spéciaux, appelés assembleurs, pour traduire automatiquement le langage symbolique en code machine.

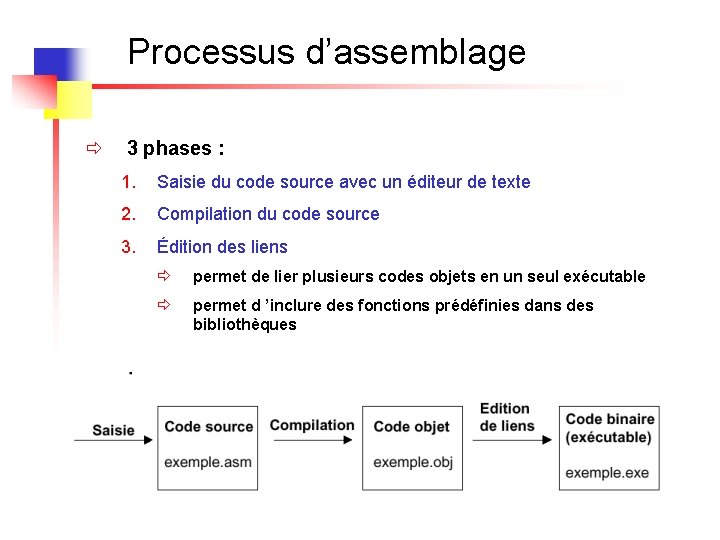

Processus d’assemblage ð 3 phases : 1. Saisie du code source avec un éditeur de texte 2. Compilation du code source 3. Édition des liens ð permet de lier plusieurs codes objets en un seul exécutable ð permet d ’inclure des fonctions prédéfinies dans des bibliothèques

![Assembleur : NASM [BITS 16] [ORG 0 x 0100] [SEGMENT. text] BEGIN: jmp START Assembleur : NASM [BITS 16] [ORG 0 x 0100] [SEGMENT. text] BEGIN: jmp START](http://slidetodoc.com/presentation_image_h/1a70718a682f21e59b5e3c5fbded7e90/image-66.jpg)

Assembleur : NASM [BITS 16] [ORG 0 x 0100] [SEGMENT. text] BEGIN: jmp START FIN: mov ax, 0 x 4 C 00 int 0 x 21 START: mov [Var 1], 3 jmp FIN Val equ 12 Var 1 db 69 Var 2 dw 0 FFFFh Tab resb 100

![En-tête ð [BITS 16] : indique au compilateur qu’on travaille en mode 16 bits En-tête ð [BITS 16] : indique au compilateur qu’on travaille en mode 16 bits](http://slidetodoc.com/presentation_image_h/1a70718a682f21e59b5e3c5fbded7e90/image-67.jpg)

En-tête ð [BITS 16] : indique au compilateur qu’on travaille en mode 16 bits (programme DOS) ð [ORG 0 x 100] : le programme est chargé en mémoire à partir de l’adresse 0 x 100 h (programme. com) ð [SEGMENT. text] : déclaration du segment dans lequel on travaille, dans un programme. com : 1 seul segment pour le code et les données ð [int 0 x 20] : Interruption = appel système pour rendre la main au dos

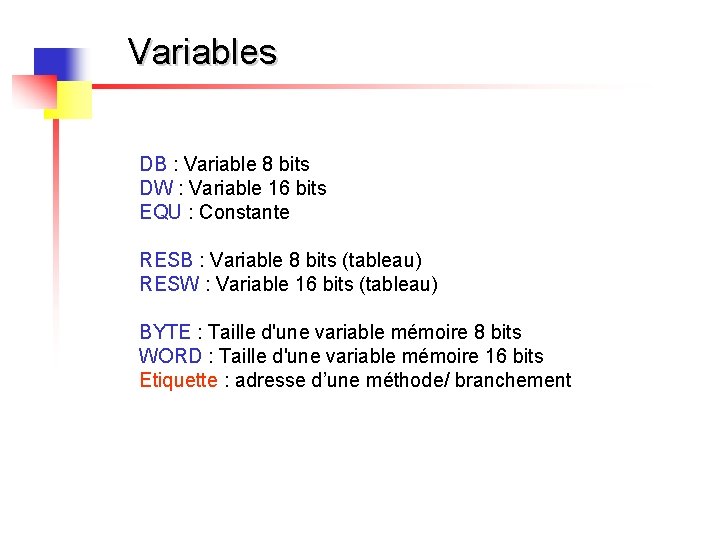

Variables DB : Variable 8 bits DW : Variable 16 bits EQU : Constante RESB : Variable 8 bits (tableau) RESW : Variable 16 bits (tableau) BYTE : Taille d'une variable mémoire 8 bits WORD : Taille d'une variable mémoire 16 bits Etiquette : adresse d’une méthode/ branchement

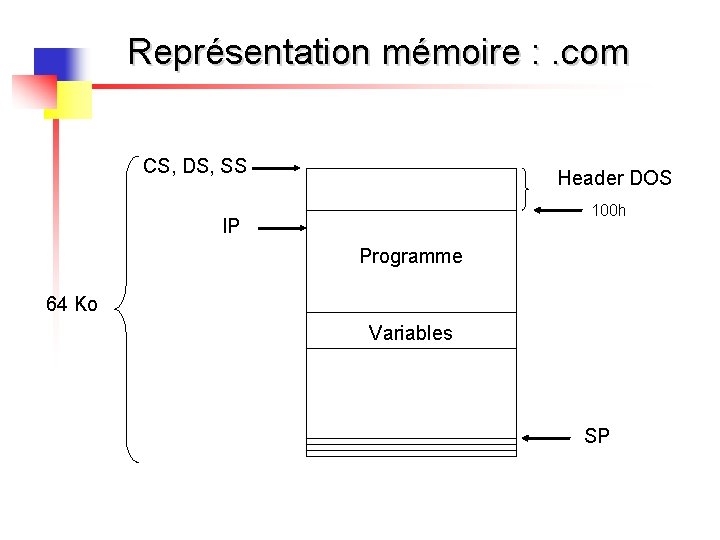

Représentation mémoire : . com CS, DS, SS Header DOS 100 h IP Programme 64 Ko Variables SP

Fichier. com ð Un seul segment de 64 Ko pour les données le programme et la pile ð. exe : on peut avoir un segment pour chaque ð Au début du programme ð IP pointe sur l’adresse 100 h du segment (header DOS) ð CS, DS, SS pointent au début ð SP pointe à la fin (tête de pile) : attention que votre pile n’écrase pas votre programme ou vos données

![Exemple de programme NASM [BITS 16] [ORG 0 x 100] [SEGMENT. text] mov AX, Exemple de programme NASM [BITS 16] [ORG 0 x 100] [SEGMENT. text] mov AX,](http://slidetodoc.com/presentation_image_h/1a70718a682f21e59b5e3c5fbded7e90/image-71.jpg)

Exemple de programme NASM [BITS 16] [ORG 0 x 100] [SEGMENT. text] mov AX, 0 x 13 int 0 x 10 mov AX, 0 x. A 000 mov ES, AX mov DI, 6720 boucle: mov byte [ES: DI], 5 add DI, 321 cmp DI, 12000 jb boucle int 0 x 20

Plan Architecture d’un processeur Processeur 8086 Assembleur Pile et Procédures Systèmes d’exploitation et appels systèmes

Pile ð Structure de « rangement » de données ð définie dans un segment de mémoire particulier (. exe) ou dans le même que le code et les données (. com) ð fonctionnement LIFO (Last In, First Out) ð Comment y accéder : ð adresse du dernier élément posé : SS: SP ð empiler : PUSH Reg 16 (registre 16 bits) ð dépiler : POP Reg 16 (registre 16 bits) ð La pile augmente vers les adresses faibles ð PUSH : SP SP- 2, POP : SP SP+ 2

Pile : exemple d’utilisation (1) ð PUSH registre ð empile le contenu du registre sur la pile. ð POP registre ð retire la valeur en haut de la pile et la place dans le registres spécifié. ð Exemple : transfert de AX vers BX en passant par la pile. PUSH AX ; Pile <- AX POP BX ; BX <- Pile Note : cet exemple n'est pas très utile, il vaut mieux employer MOV AX, BX. )

Pile : exemple d’utilisation (2) ð La pile est souvent utilisée pour sauvegarder temporairement le contenu des registres : ; AX et BX contiennent des données a conserver PUSH AX PUSH BX MOV BX, truc ; on utilise AX ADD AX, BX ; et BX POP BX ; récupère l'ancien BX POP AX ; et l'ancien AX ð On voit que la pile peut conserver plusieurs valeurs. ð La valeur dépilée par POP est la dernière valeur empilée; c'est pourquoi on parle ici de pile LIFO (Last In First Out, Premier Entré Dernier Sorti).

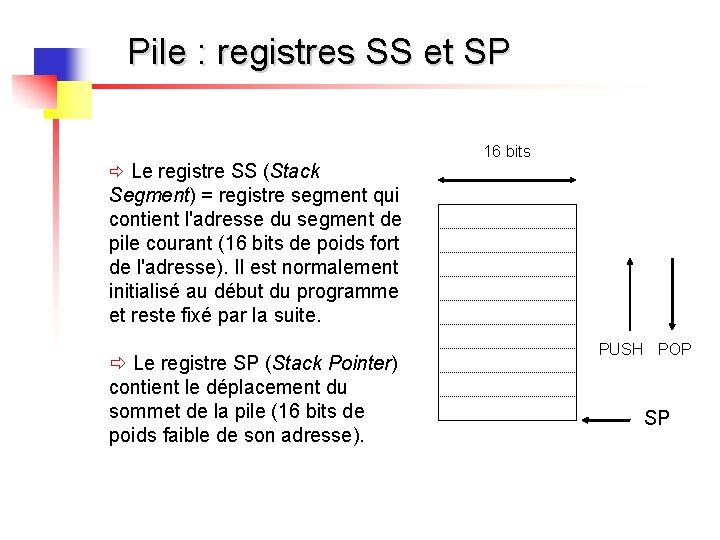

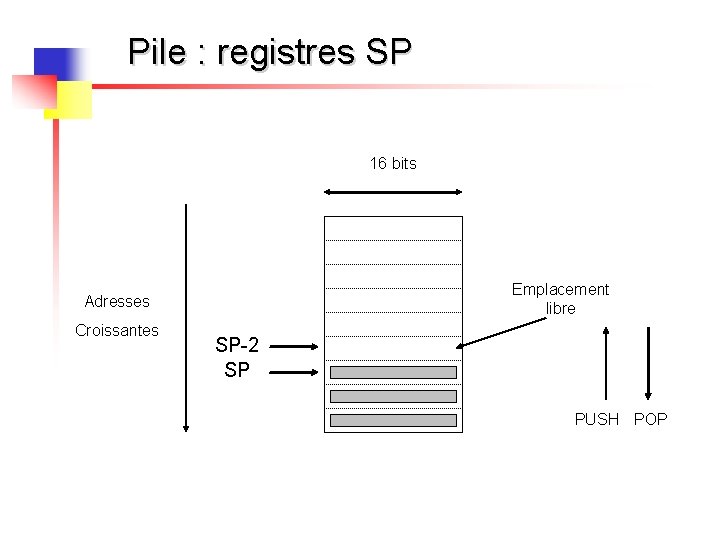

Pile : registres SS et SP ð Le registre SS (Stack 16 bits Segment) = registre segment qui contient l'adresse du segment de pile courant (16 bits de poids fort de l'adresse). Il est normalement initialisé au début du programme et reste fixé par la suite. ð Le registre SP (Stack Pointer) contient le déplacement du sommet de la pile (16 bits de poids faible de son adresse). PUSH POP SP

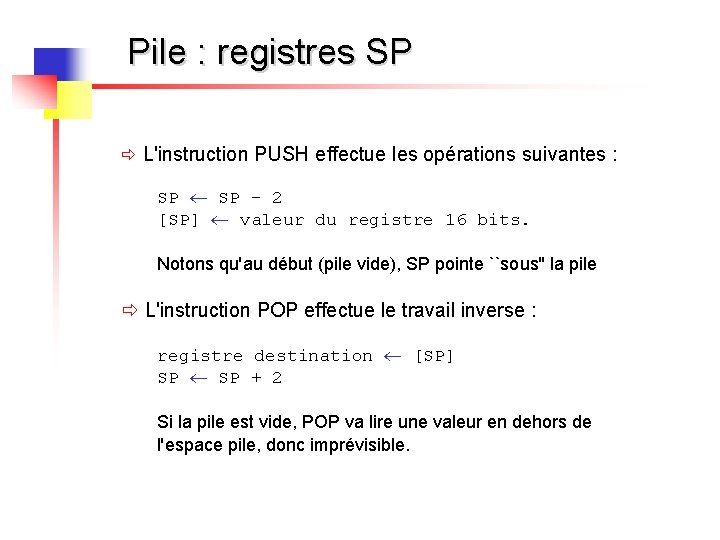

Pile : registres SP ð L'instruction PUSH effectue les opérations suivantes : SP - 2 [SP] valeur du registre 16 bits. Notons qu'au début (pile vide), SP pointe ``sous'' la pile ð L'instruction POP effectue le travail inverse : registre destination [SP] SP + 2 Si la pile est vide, POP va lire une valeur en dehors de l'espace pile, donc imprévisible.

Pile : registres SP 16 bits Emplacement libre Adresses Croissantes SP-2 SP PUSH POP

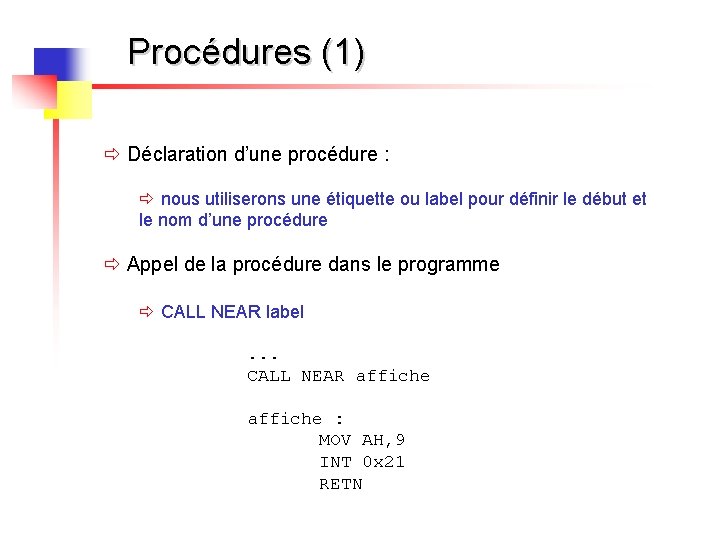

Procédures (1) ð Déclaration d’une procédure : ð nous utiliserons une étiquette ou label pour définir le début et le nom d’une procédure ð Appel de la procédure dans le programme ð CALL NEAR label. . . CALL NEAR affiche : MOV AH, 9 INT 0 x 21 RETN

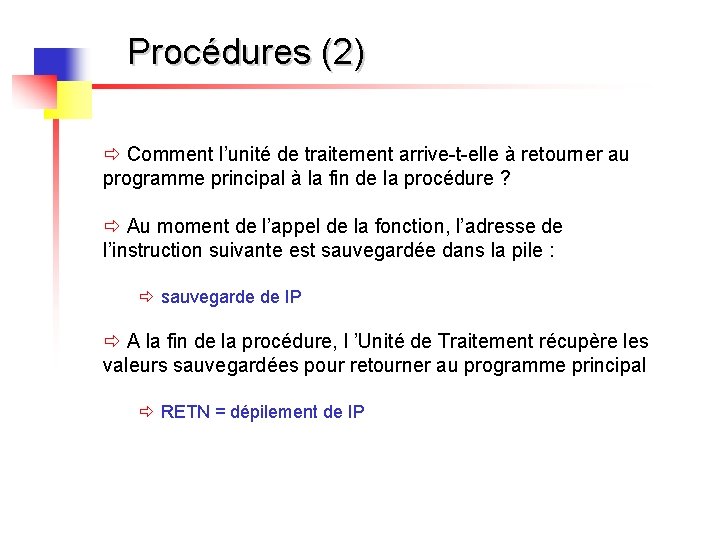

Procédures (2) ð Comment l’unité de traitement arrive-t-elle à retourner au programme principal à la fin de la procédure ? ð Au moment de l’appel de la fonction, l’adresse de l’instruction suivante est sauvegardée dans la pile : ð sauvegarde de IP ð A la fin de la procédure, l ’Unité de Traitement récupère les valeurs sauvegardées pour retourner au programme principal ð RETN = dépilement de IP

Passage de paramètres ð 2 méthodes de passage de paramètres : ð par registre ð par la pile ð Passage de paramètres par registre : ð les paramètres d’entrée de la procédure sont mis dans des registres avant l’appel de la procédure ð les paramètres de sortie sont aussi rangés dans des registres ð avantage = rapidité ð inconvénients = peu de registres

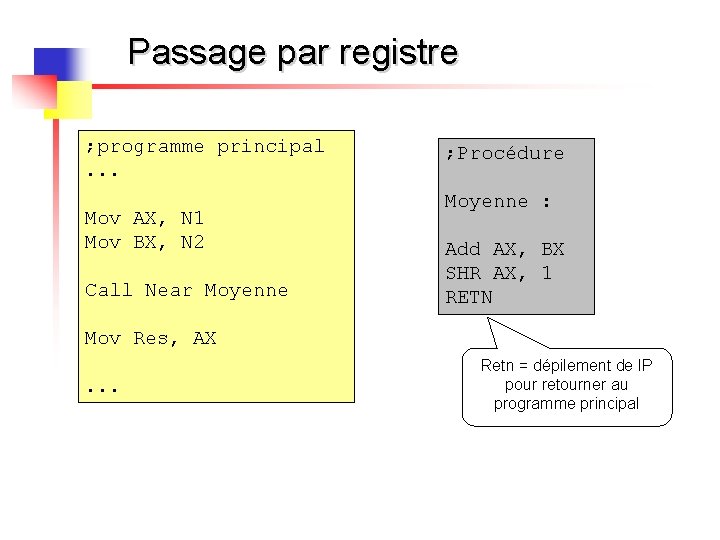

Passage par registre ; programme principal. . . Mov AX, N 1 Mov BX, N 2 Call Near Moyenne ; Procédure Moyenne : Add AX, BX SHR AX, 1 RETN Mov Res, AX. . . Retn = dépilement de IP pour retourner au programme principal

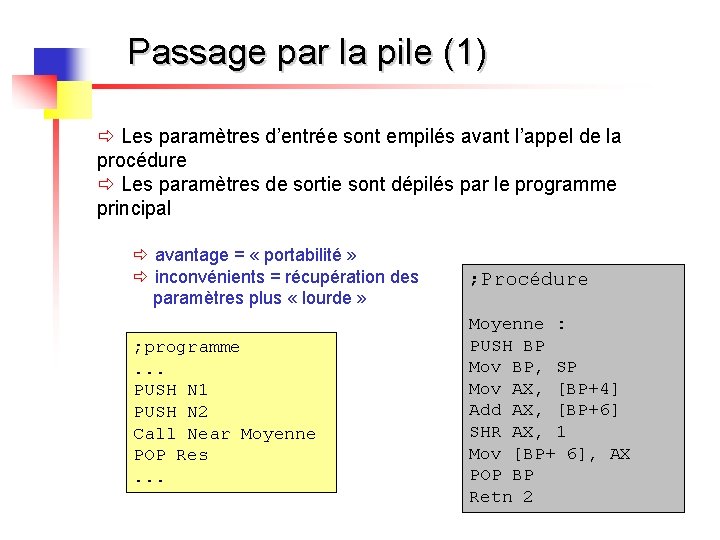

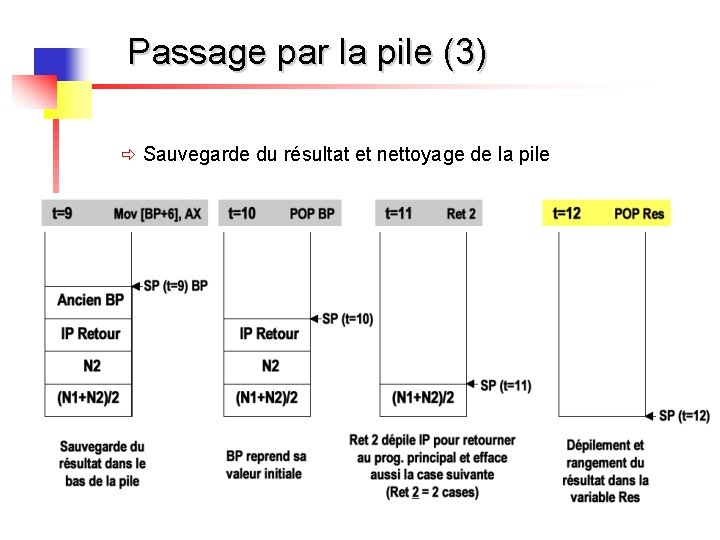

Passage par la pile (1) ð Les paramètres d’entrée sont empilés avant l’appel de la procédure ð Les paramètres de sortie sont dépilés par le programme principal ð avantage = « portabilité » ð inconvénients = récupération des paramètres plus « lourde » ; Procédure ; programme. . . PUSH N 1 PUSH N 2 Call Near Moyenne POP Res. . . Moyenne : PUSH BP Mov BP, SP Mov AX, [BP+4] Add AX, [BP+6] SHR AX, 1 Mov [BP+ 6], AX POP BP Retn 2

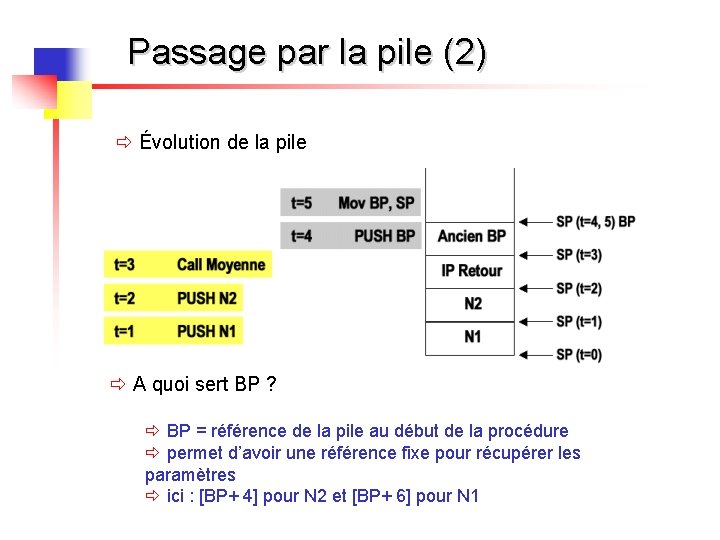

Passage par la pile (2) ð Évolution de la pile ð A quoi sert BP ? ð BP = référence de la pile au début de la procédure ð permet d’avoir une référence fixe pour récupérer les paramètres ð ici : [BP+ 4] pour N 2 et [BP+ 6] pour N 1

Passage par la pile (3) ð Sauvegarde du résultat et nettoyage de la pile

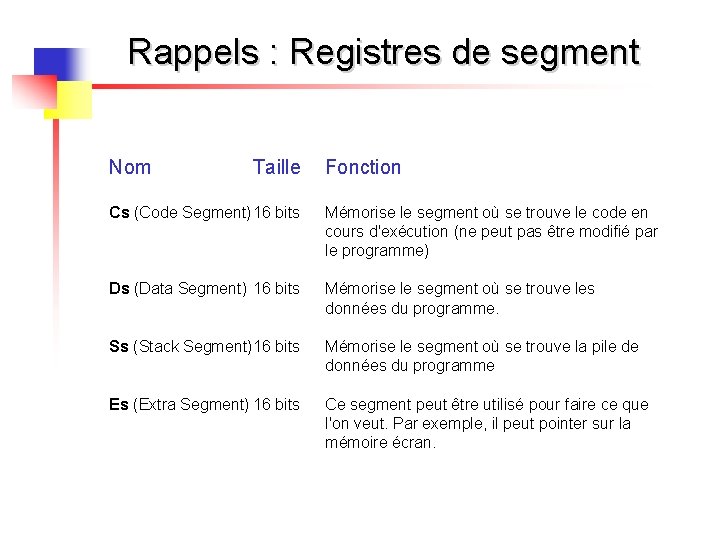

Rappels : Registres de segment Nom Taille Fonction Cs (Code Segment) 16 bits Mémorise le segment où se trouve le code en cours d'exécution (ne peut pas être modifié par le programme) Ds (Data Segment) 16 bits Mémorise le segment où se trouve les données du programme. Ss (Stack Segment)16 bits Es (Extra Segment) 16 bits Mémorise le segment où se trouve la pile de données du programme Ce segment peut être utilisé pour faire ce que l'on veut. Par exemple, il peut pointer sur la mémoire écran.

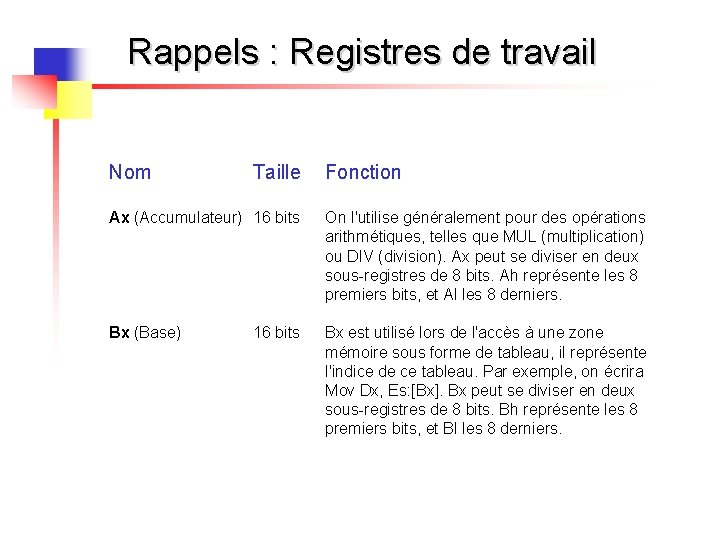

Rappels : Registres de travail Nom Taille Fonction Ax (Accumulateur) 16 bits On l'utilise généralement pour des opérations arithmétiques, telles que MUL (multiplication) ou DIV (division). Ax peut se diviser en deux sous-registres de 8 bits. Ah représente les 8 premiers bits, et Al les 8 derniers. Bx (Base) Bx est utilisé lors de l'accès à une zone mémoire sous forme de tableau, il représente l'indice de ce tableau. Par exemple, on écrira Mov Dx, Es: [Bx]. Bx peut se diviser en deux sous-registres de 8 bits. Bh représente les 8 premiers bits, et Bl les 8 derniers. 16 bits

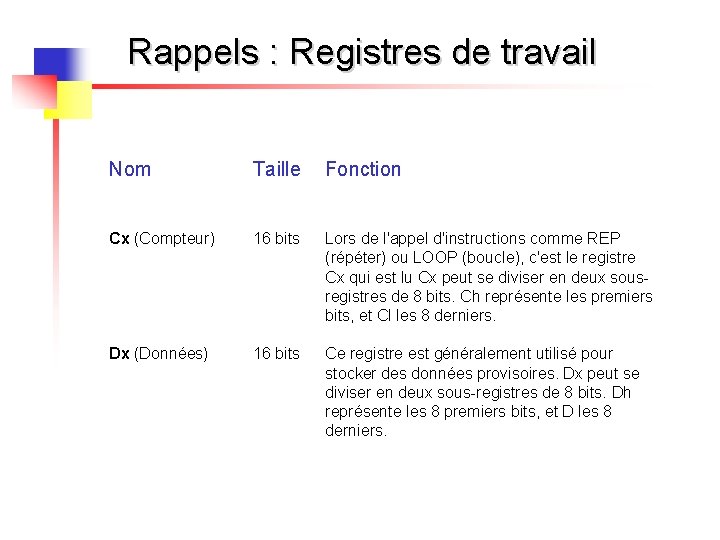

Rappels : Registres de travail Nom Taille Fonction Cx (Compteur) 16 bits Lors de l'appel d'instructions comme REP (répéter) ou LOOP (boucle), c'est le registre Cx qui est lu Cx peut se diviser en deux sousregistres de 8 bits. Ch représente les premiers bits, et Cl les 8 derniers. Dx (Données) 16 bits Ce registre est généralement utilisé pour stocker des données provisoires. Dx peut se diviser en deux sous-registres de 8 bits. Dh représente les 8 premiers bits, et D les 8 derniers.

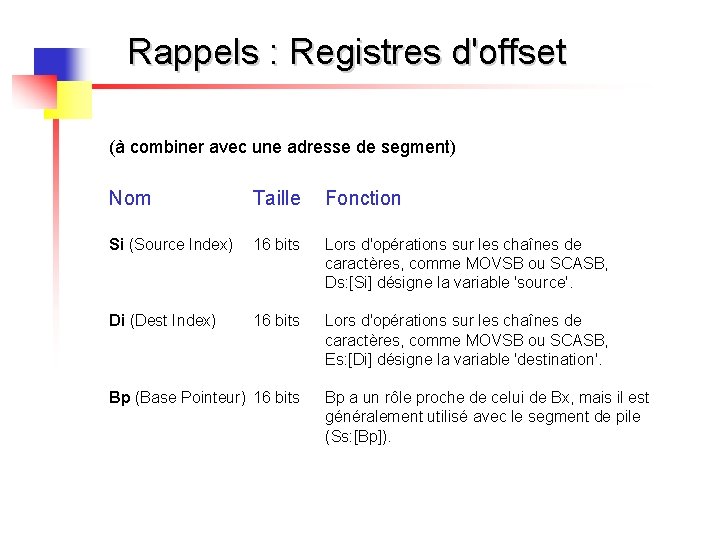

Rappels : Registres d'offset (à combiner avec une adresse de segment) Nom Taille Fonction Si (Source Index) 16 bits Lors d'opérations sur les chaînes de caractères, comme MOVSB ou SCASB, Ds: [Si] désigne la variable 'source'. Di (Dest Index) 16 bits Lors d'opérations sur les chaînes de caractères, comme MOVSB ou SCASB, Es: [Di] désigne la variable 'destination'. Bp (Base Pointeur) 16 bits Bp a un rôle proche de celui de Bx, mais il est généralement utilisé avec le segment de pile (Ss: [Bp]).

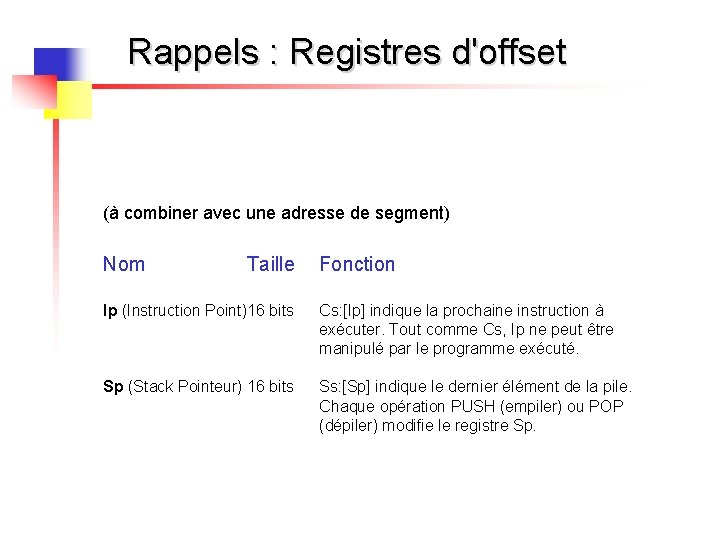

Rappels : Registres d'offset (à combiner avec une adresse de segment) Nom Taille Fonction Ip (Instruction Point)16 bits Sp (Stack Pointeur) 16 bits Cs: [Ip] indique la prochaine instruction à exécuter. Tout comme Cs, Ip ne peut être manipulé par le programme exécuté. Ss: [Sp] indique le dernier élément de la pile. Chaque opération PUSH (empiler) ou POP (dépiler) modifie le registre Sp.

![Exemple de programme NASM [BITS 16] [ORG 0 x 100] [SEGMENT. text] PILE PROC Exemple de programme NASM [BITS 16] [ORG 0 x 100] [SEGMENT. text] PILE PROC](http://slidetodoc.com/presentation_image_h/1a70718a682f21e59b5e3c5fbded7e90/image-91.jpg)

Exemple de programme NASM [BITS 16] [ORG 0 x 100] [SEGMENT. text] PILE PROC

Plan Architecture d’un processeur Processeur 8086 Assembleur Pile et Procédures Systèmes d’exploitation et appels systèmes

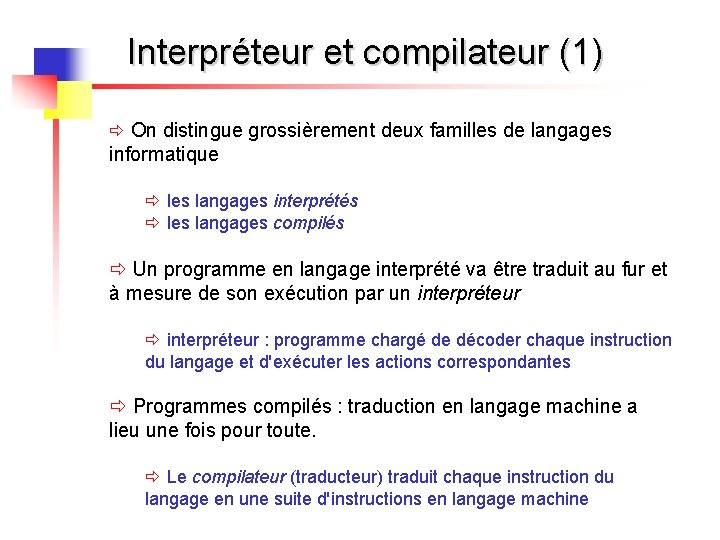

Interpréteur et compilateur (1) ð On distingue grossièrement deux familles de langages informatique ð les langages interprétés ð les langages compilés ð Un programme en langage interprété va être traduit au fur et à mesure de son exécution par un interpréteur ð interpréteur : programme chargé de décoder chaque instruction du langage et d'exécuter les actions correspondantes ð Programmes compilés : traduction en langage machine a lieu une fois pour toute. ð Le compilateur (traducteur) traduit chaque instruction du langage en une suite d'instructions en langage machine

Interpréteur et compilateur (2) ð Les programmes compilés s'exécutent ainsi plus rapidement que les programmes interprétés ð La traduction est déjà faite ð Mais on perd en souplesse de programmation, car les types de données doivent être connus au moment de la compilation ð Compilateur = traduit un programme source écrit dans un langage de haut niveau (C) en un autre programme dans un langage de bas niveau (par exemple l'assembleur) ð Opération de traduction complexe ð Compilateurs = programmes sophistiqués

Principaux langages ð Les principaux langages compilés sont : ð C/C++ ð ADA ð Cobol ð Fortran ð Pascal : programmation système et scientifique : logiciels embarqués : gestion : calcul scientifique : enseignement ð Quelques langages interprétés : ð BASIC ð LISP, Prolog ð Python ð Java ð MATLAB : bricolage : Intelligence Artificielle : programmation système, Internet : applets internet : calcul scientifique ð LISP, Java ou Python : une première phase de compilation vers un langage intermédiaire (bytecode), qui sera lui même interprété.

Compilation du C ð Traduction en assembleur des programmes en langage C ð Le détail de cette traduction (ou compilation) dépend ð Compilateur utilisé ð Système d'exploitation (DOS, Windows, UNIX, . . . ). ð Taille des types : exemple int (16 ou 32 bits) ð Modèle de mémoire utilisé (pointeurs sur 16 ou 32 bits, données et code dans des segments différents ou non, etc. ) ð Exemple : compilateur Turbo C++ version 3 sous DOS (entiers de 16 bits et le modèle de mémoire « small » ) ð Génère directement du code objet (fichier. OBJ) à partir d'un fichier source en langage C ð Il est cependant possible de demander l'arrêt de la compilation pour obtenir du langage assembleur (fichier. ASM)

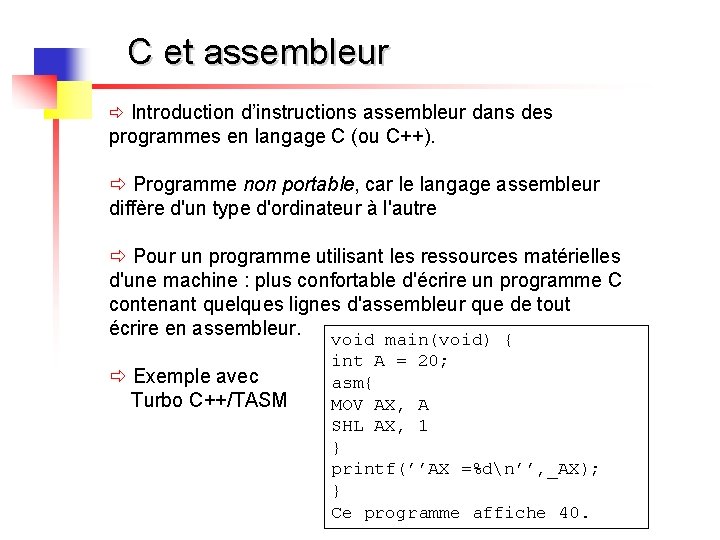

C et assembleur ð Introduction d’instructions assembleur dans des programmes en langage C (ou C++). ð Programme non portable, car le langage assembleur diffère d'un type d'ordinateur à l'autre ð Pour un programme utilisant les ressources matérielles d'une machine : plus confortable d'écrire un programme C contenant quelques lignes d'assembleur que de tout écrire en assembleur. void main(void) { ð Exemple avec Turbo C++/TASM int A = 20; asm{ MOV AX, A SHL AX, 1 } printf(’’AX =%dn’’, _AX); } Ce programme affiche 40.

Système d’exploitation ð OS : Operating System : le programme permettant d'utiliser les circuits qui ont été câblés. ð Soit entièrement en ROM ð Soit un code de boot en ROM se chargeant de placer en RAM le reste de l'OS à partir de la disquette ou du DD ð Souvent, une ROM de boot contient néanmoins la partie de l'OS la plus primitive: le BIOS. ð But de l'OS = décharger le programme des tâches répétitives et de bas niveau. ð Gain de temps lors du développement programmes ð Pas à se soucier du fonctionnement de la circuiterie électronique

Système d’exploitation ð Le système d’exploitation doit s’occuper de : ð l ’exécution des commandes d’entrée/ sortie ð la gestion de la mémoire ð la gestion des fichiers ð la multi- programmation ( « multi- tâche » ) ð Comment exécuter plusieurs programmes à la fois ? ð Et si ces programmes veulent tous accéder à l ’imprimante en même temps ? ð Et s’ils doivent échanger des informations ? … ð Comment exécuter un seul programme avec plusieurs processeurs ? ð la sécurité (gestion des accès, …) ð Le SE doit aussi fournir : ð un langage de commande ð divers utilitaires (compilateurs, éditeurs, outils, …) ð une interface graphique pour l’utilisateur

Système d’exploitation ð Windows 95/ 98, Windows NT (Microsoft) : ð processeurs 80 x 86 ð OS/ 2 (IBM) ð Mac. OS (Apple) : ð processeurs 68000 puis Power. PC ð UNIX = famille de SE : ð Versions payantes généralement spécialisées à un type de machine : ð Sun. OS/ Solaris (Sun) ð AIX (IBM) ð HP/ UX (HP) ð Versions libres : ðLINUX : 80 x 86, 68000, Power. PC, Sparc …

Présentation du BIOS ð BIOS (Basic Input Output System) : partie de l'OS du plus bas niveau ð opérations très primitives: lecture du clavier, affichage écran en mode texte, accès simplifié au lecteur de disquette et au disque dur, accès au ports série et parallèle. ð Le programme du BIOS se trouve en mémoire morte (ROM) ð une mémoire gardant son contenu lorsque l'on interrompt son alimentation électrique ð Chaque modèle de PC est vendu avec une version du BIOS adapté à sa configuration matérielle.

Fonctions du BIOS ð BIOS librairie de fonctions ð Chaque fonction effectue une tâche bien précise (par exemple afficher un caractère donné sur l'écran) ð L'appel de l'une de ces fonctions = appel système ð Fonctions du BIOS procédures appelées avec l'instruction CALL ð il a été prévu de pouvoir modifier le comportement du BIOS en cours d'utilisation (par exemple pour gérer un nouveau périphérique) ð Code du BIOS en ROM = non modifiable ð Le BIOS étant différent d'un ordinateur à l'autre, les adresses des fonctions changent. . .

Vecteurs d’interruption (1) ð Problème résolu par l'utilisation d'une table d'indirection = la table des vecteurs d'interruptions ð table est placée en RAM : contient les adresses (en ROM ou en RAM) des fonctions du BIOS ð implantée à partir de l'adresse 0000 H (première case mémoire) ð elle est initialisée par le BIOS lui même au moment du démarrage du PC (boot). Adresse 0000 0004 . . . contenu adresse de la première fonction du BIOS adresse de la deuxième fonction du BIOS

Vecteurs d’interruption ð Chaque élément de la table occupe 4 octets (adresse 32 bits). ð table à 256 éléments (1 Ko). ð exemple : si l'on sait que la fonction du BIOS qui affiche un caractère est la 33 ième, on va l'appeler en lisant la 33 ième ligne de la table, puis en allant exécuter les instructions à l'adresse trouvée : Adresse . . . 0084 H . . . contenu F 1234560 H (car 4 x 33 = 84 H). ð La table des vecteurs d'interruptions contient des valeurs différentes pour chaque version de BIOS ð peut être modifiée pour pointer sur du code en mémoire principale, modifiant alors le BIOS existant.

Interruptions ð Unité de Traitement exécute séquentiellement les instructions ou effectue des sauts programmés (JMP, CALL) ð Il existe des situations où l ’U. T. est « déroutée » de sa tâche : ð Reset : signal envoyé au processeur pour un (re-) démarrage ð Exceptions (interruptions internes) : débordement de pile, dépassement de capacité, div /0, … ð Appels systèmes (int. logicielles) : appels du programme lui- même « int 21 h » … ð Interruptions physiques (int. externes) : appels d’autres périphériques

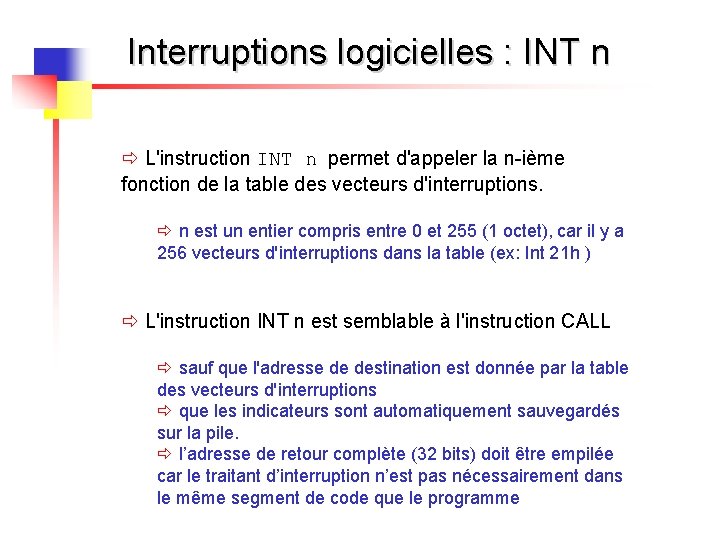

Interruptions logicielles : INT n ð L'instruction INT n permet d'appeler la n-ième fonction de la table des vecteurs d'interruptions. ð n est un entier compris entre 0 et 255 (1 octet), car il y a 256 vecteurs d'interruptions dans la table (ex: Int 21 h ) ð L'instruction INT n est semblable à l'instruction CALL ð sauf que l'adresse de destination est donnée par la table des vecteurs d'interruptions ð que les indicateurs sont automatiquement sauvegardés sur la pile. ð l’adresse de retour complète (32 bits) doit être empilée car le traitant d’interruption n’est pas nécessairement dans le même segment de code que le programme

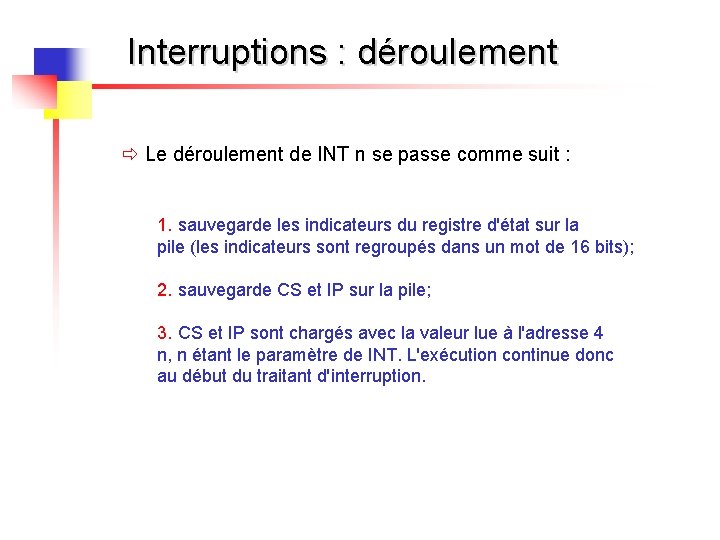

Interruptions : déroulement ð Le déroulement de INT n se passe comme suit : 1. sauvegarde les indicateurs du registre d'état sur la pile (les indicateurs sont regroupés dans un mot de 16 bits); 2. sauvegarde CS et IP sur la pile; 3. CS et IP sont chargés avec la valeur lue à l'adresse 4 n, n étant le paramètre de INT. L'exécution continue donc au début du traitant d'interruption.

Interruptions : fonctionnement ð Lorsque l’interruption est déclenchée, l ’U. T. doit exécuter un bout de programme précis : le traitant de l’interruption. l ’U. T. doit savoir où se trouve l ’adresse (CS: IP) du traitant numéro n Cette information est stockée en mémoire (0000: 0000 à 0000: 03 FFh)

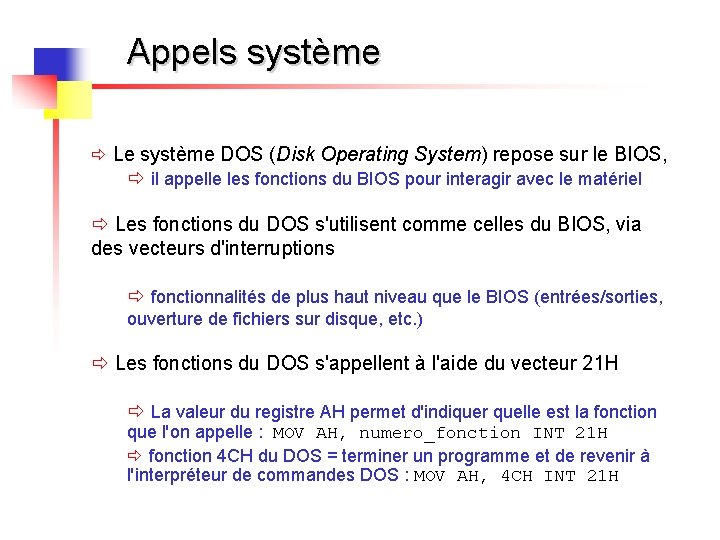

Appels système ð Le système DOS (Disk Operating System) repose sur le BIOS, ð il appelle les fonctions du BIOS pour interagir avec le matériel ð Les fonctions du DOS s'utilisent comme celles du BIOS, via des vecteurs d'interruptions ð fonctionnalités de plus haut niveau que le BIOS (entrées/sorties, ouverture de fichiers sur disque, etc. ) ð Les fonctions du DOS s'appellent à l'aide du vecteur 21 H ð La valeur du registre AH permet d'indiquer quelle est la fonction que l'on appelle : MOV AH, numero_fonction INT 21 H ð fonction 4 CH du DOS = terminer un programme et de revenir à l'interpréteur de commandes DOS : MOV AH, 4 CH INT 21 H

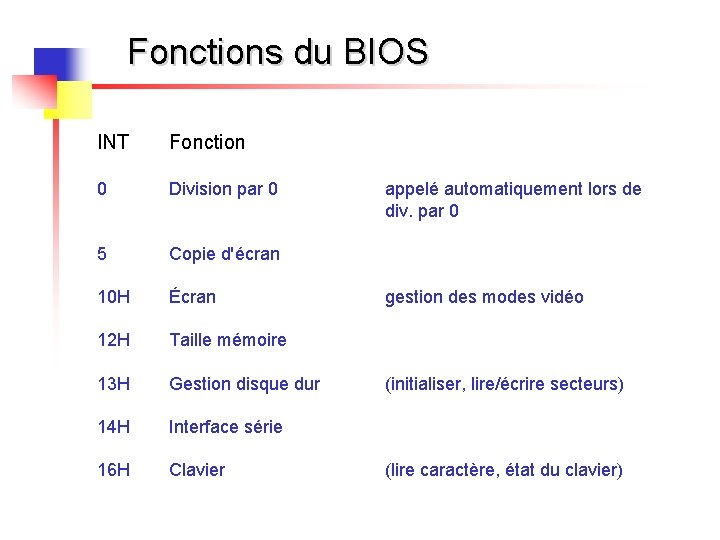

Fonctions du BIOS INT Fonction 0 Division par 0 5 Copie d'écran 10 H Écran 12 H Taille mémoire 13 H Gestion disque dur 14 H Interface série 16 H Clavier appelé automatiquement lors de div. par 0 gestion des modes vidéo (initialiser, lire/écrire secteurs) (lire caractère, état du clavier)

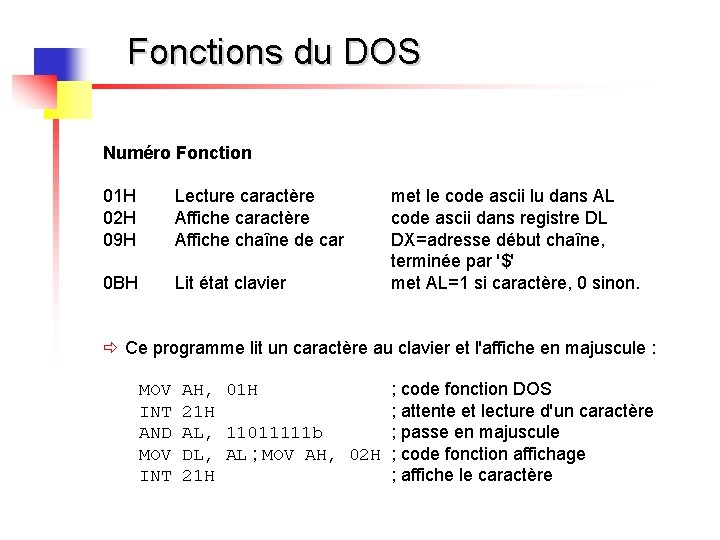

Fonctions du DOS Numéro Fonction 01 H 02 H 09 H Lecture caractère Affiche caractère Affiche chaîne de car 0 BH Lit état clavier met le code ascii lu dans AL code ascii dans registre DL DX=adresse début chaîne, terminée par '$' met AL=1 si caractère, 0 sinon. ð Ce programme lit un caractère au clavier et l'affiche en majuscule : MOV AH, 01 H ; code fonction DOS INT 21 H ; attente et lecture d'un caractère AND AL, 11011111 b ; passe en majuscule MOV DL, AL ; MOV AH, 02 H ; code fonction affichage INT 21 H ; affiche le caractère

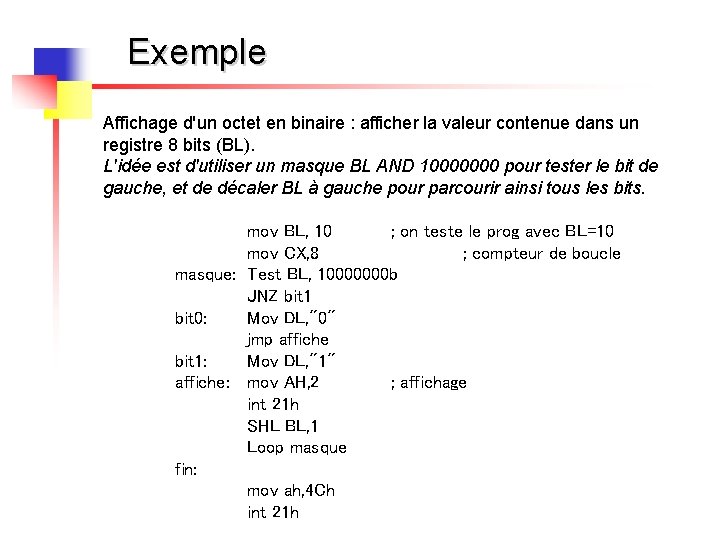

Exemple Affichage d'un octet en binaire : afficher la valeur contenue dans un registre 8 bits (BL). L'idée est d'utiliser un masque BL AND 10000000 pour tester le bit de gauche, et de décaler BL à gauche pour parcourir ainsi tous les bits. mov BL, 10 ; on teste le prog avec BL=10 mov CX, 8 ; compteur de boucle masque: Test BL, 10000000 b JNZ bit 1 bit 0: Mov DL, "0" jmp affiche bit 1: Mov DL, "1" affiche: mov AH, 2 ; affichage int 21 h SHL BL, 1 Loop masque fin: mov ah, 4 Ch int 21 h

- Slides: 112