Architecture matrielle des machines parallles SGI Origin Cray

- Slides: 32

Architecture matérielle des machines parallèles: SGI Origin & Cray T 3 E Professeur: Nilo Stolte Chargé de Cours: Mohammed ELKANOUNI Département de génie logiciel et des TI

SGI Origin

Introduction n SMP (symetric multiprocessor): Les processeurs et leur façon d’interconnecter aux voisins sont semblables DSM (distributed shared memory): chaque processeur a sa mémoire locale accessible par les autres processeurs cc. NUMA (cache coherent non-uniform memory access): les caches sont gardés cohérent avec la mémoire par le “hardware” Architecture matérielle des machines parallèles 3

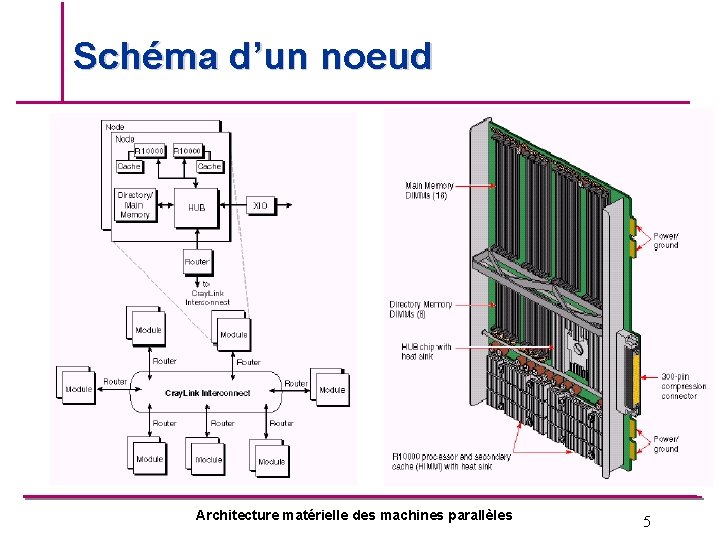

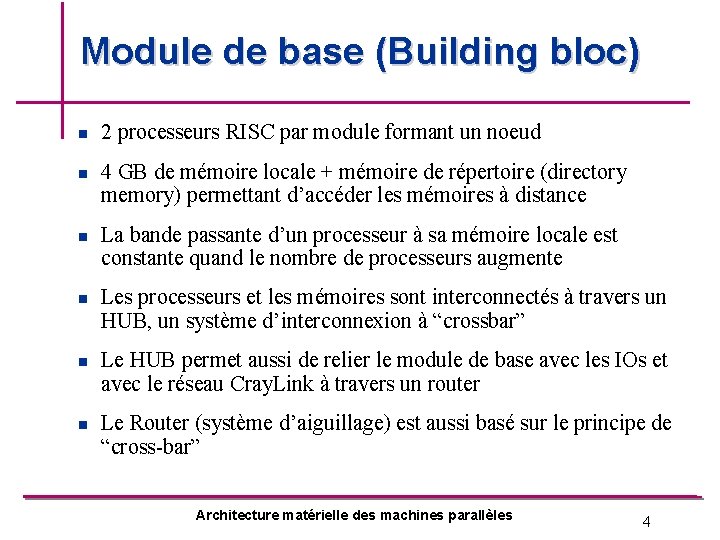

Module de base (Building bloc) n n n 2 processeurs RISC par module formant un noeud 4 GB de mémoire locale + mémoire de répertoire (directory memory) permettant d’accéder les mémoires à distance La bande passante d’un processeur à sa mémoire locale est constante quand le nombre de processeurs augmente Les processeurs et les mémoires sont interconnectés à travers un HUB, un système d’interconnexion à “crossbar” Le HUB permet aussi de relier le module de base avec les IOs et avec le réseau Cray. Link à travers un router Le Router (système d’aiguillage) est aussi basé sur le principe de “cross-bar” Architecture matérielle des machines parallèles 4

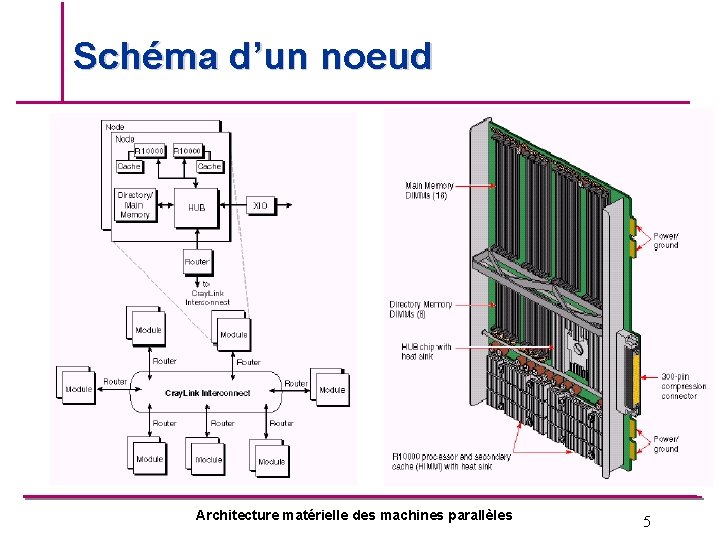

Schéma d’un noeud Architecture matérielle des machines parallèles 5

Hiérarchie de la mémoire n Registre: temps d’accès le plus vite n Cache primaire dans la puce de CPU n n Chaque processeur a un espace de mémoire virtuelle qui est “mappée” à la mémoire physique composé de mémoire locale et mémoire à distance Les informations nécessaires pour “mapping” sont dans la mémoire de répertoire (director memory) Architecture matérielle des machines parallèles 6

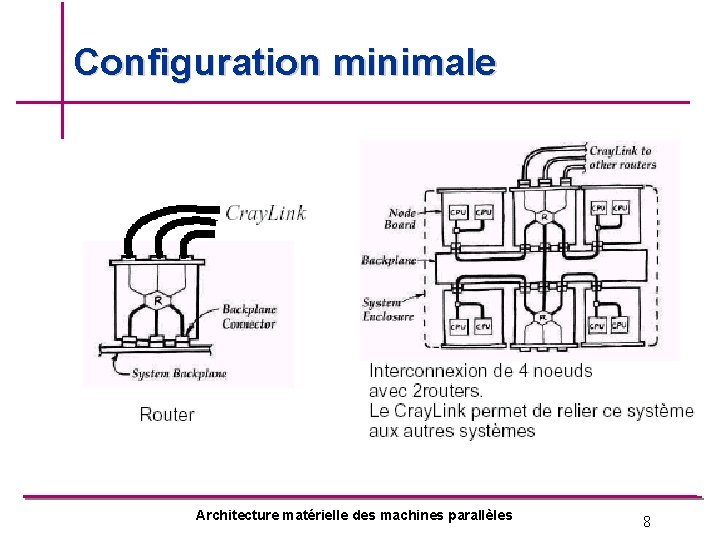

Configuration minimale n n Le système minimal, Origin 2000, contient une carte mère, 4 noeuds (8 processeurs) se reliant avec 2 routeurs, les IOs. Les routeurs sont basés sur le principe de cross-bar avec 6 liens d’interconnexion et a une bande passante de 1. 6 GB. 3 liens du router vont sur la “backplane” pour relier les 4 noeuds, 3 autres liens vont sur le Cray. Link permettant de relier aux autres systèmes. Les noeuds font accès aux IOs via les XBOW, un autre système d’interconnexion basé sur “cross-bar”, aussi avec une bande passante de 1. 6 GB Architecture matérielle des machines parallèles 7

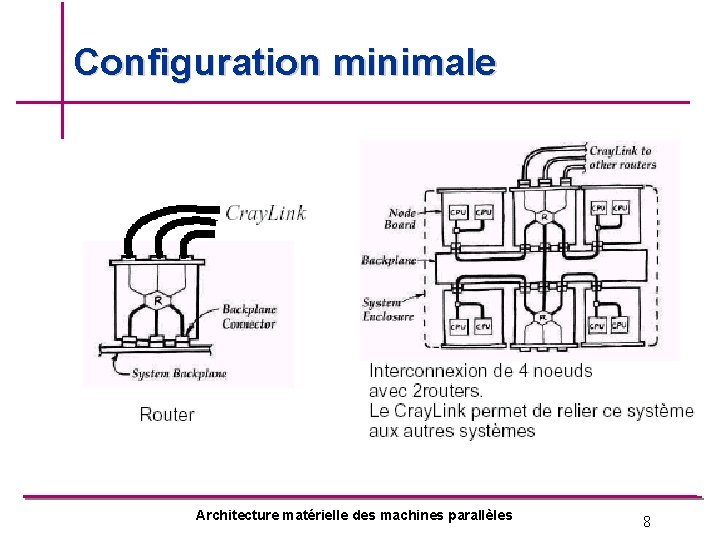

Configuration minimale Architecture matérielle des machines parallèles 8

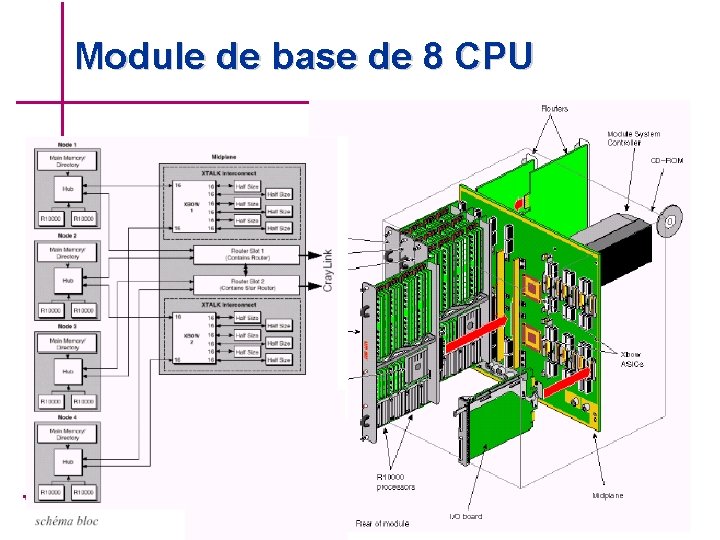

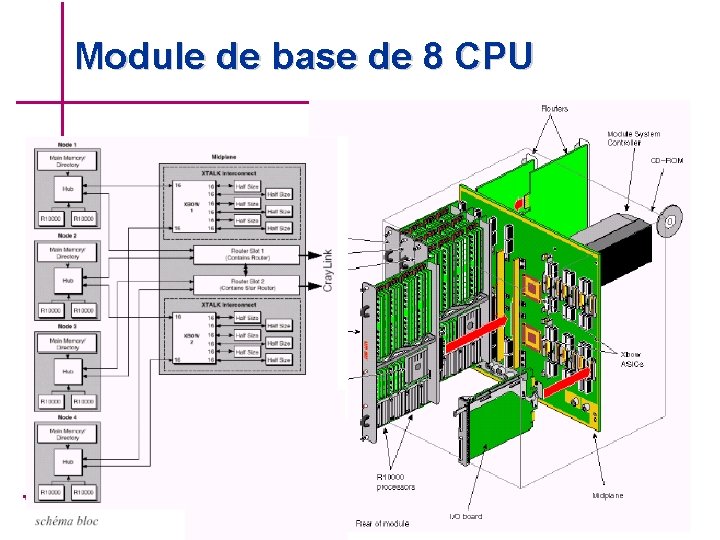

Module de base de 8 CPU Architecture matérielle des machines parallèles 9

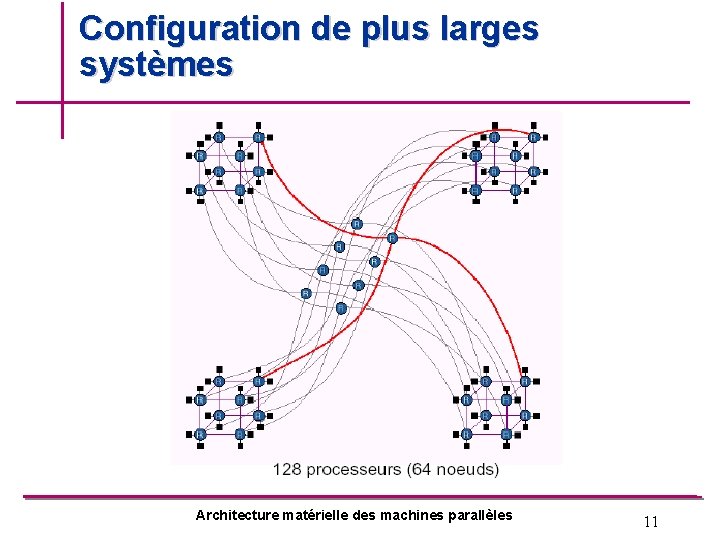

Configuration de plus larges systèmes Architecture matérielle des machines parallèles 10

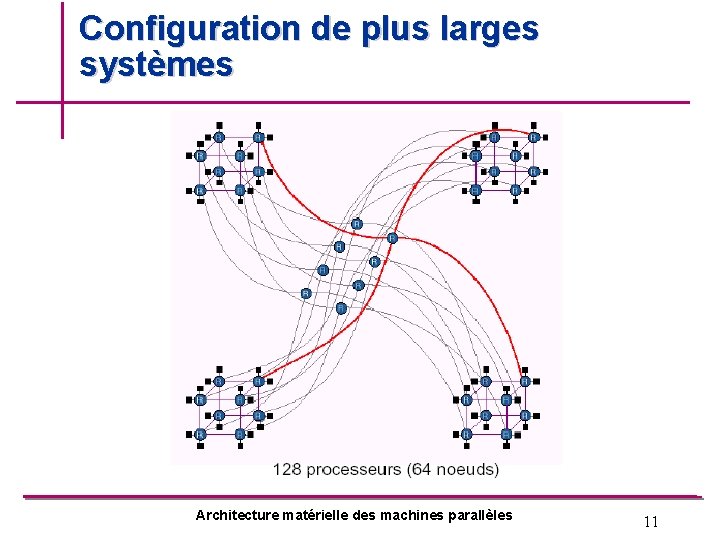

Configuration de plus larges systèmes Architecture matérielle des machines parallèles 11

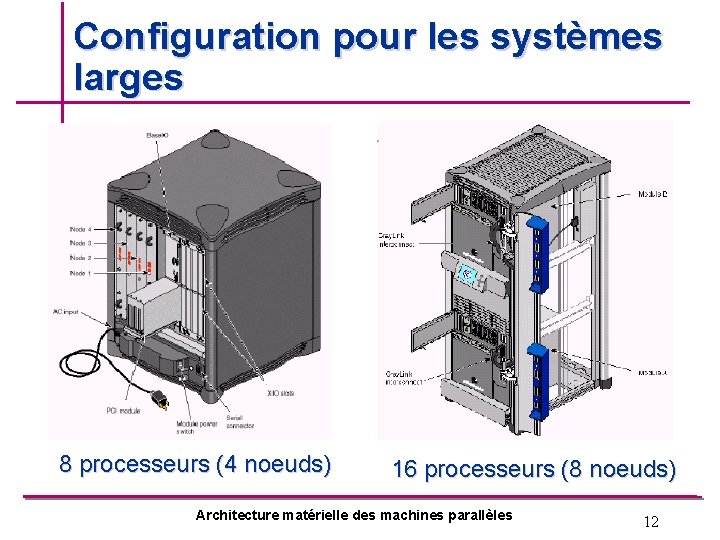

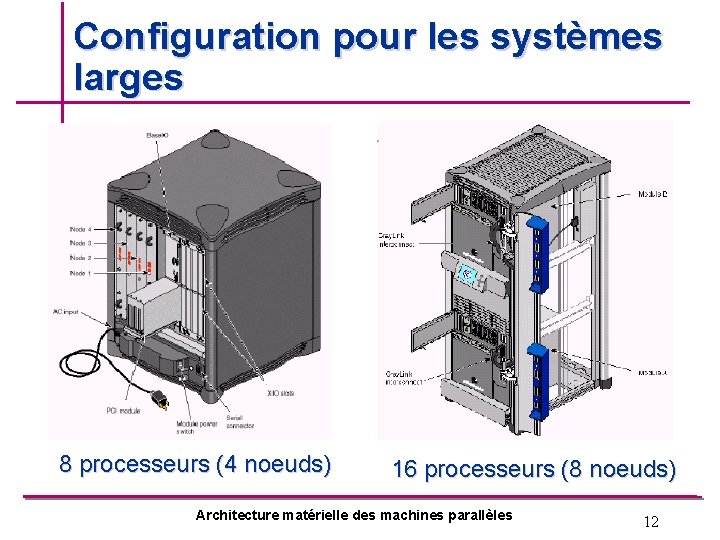

Configuration pour les systèmes larges 8 processeurs (4 noeuds) 16 processeurs (8 noeuds) Architecture matérielle des machines parallèles 12

Configuration pour les systèmes larges n n n Les systèmes peuvent s’agrandir facilement en interconnectant des systèmes minimaux en utilisant des routers et des liens Cray. Link => architecture dimensionable (scalable) Jusqu’à 512 noeuds peuvent être reliés en parallèle (1024 processeurs) Chaque processeur peut adresser la mémoire de tous les autres processeurs (mémoire distribuée partagée) Chaque processeur peut aussi adresser tous les IOs Le transfert de mémoire aux IOs peut se faire en mode DMA (direct memory access) Architecture matérielle des machines parallèles 13

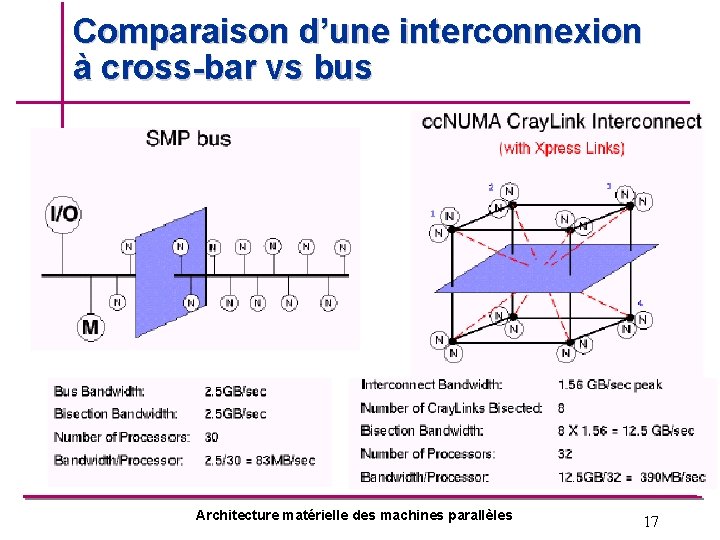

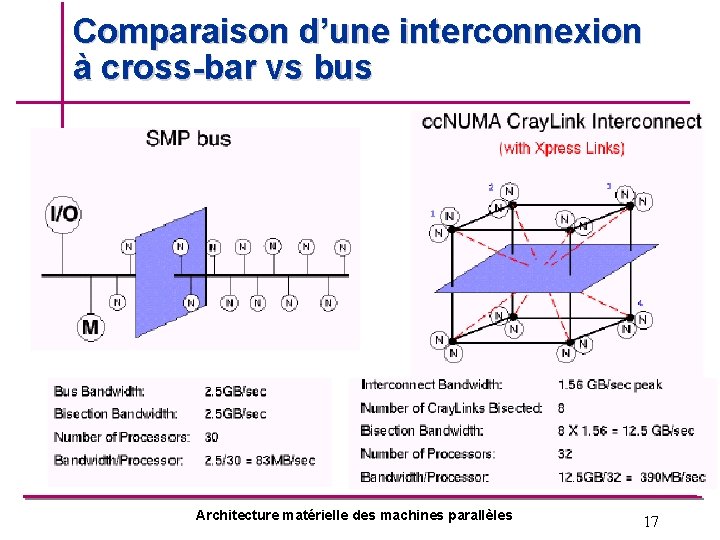

Comparaison d’une interconnexion à cross-bar vs bus Bus n Même bus partagé par plusieurs processeurs et IOs n Une seule bande passante partagée par tout le système n Un arbitrage est nécessaire pour partager le bus n Le taux de transfert diminue rapidement lorsque le nombre de processeurs et IO augmente n La dimensionabilité est limitée (le système ne peut pas augmenter à un grand nombre de processeurs & IOs). n Convenable pour 4 processeurs et moins. n Moins dispendieux pour un système à petit nombre de processeurs/IOs Architecture matérielle des machines parallèles 14

Comparaison d’une interconnexion à cross-bar vs bus Interconnexion par cross-bar n Cross-bar est une maille de contacteurs dynamiquement reconfigurable. n Multiplicité de chemins d’accès d’un processeur/IO à un autre n Le nombre de processeurs/IOs qui demande le même chemin est beaucoup plus faible que avec le bus n Moins de processeurs/IOs partageant une bande passante =>vitesse de communication plus vite. n Meilleur dimensionnabilité (peu de dégradation de performance quand le nombre de processeurs/IOs augmente) Architecture matérielle des machines parallèles 15

Comparaison d’une interconnexion à cross-bar vs bus Calcul de la bande passante allouée à chaque processeur n Tracer un plan qui subdivise le système en deux moitiés n Compter le nombre de liens disponibles pour relier les deux moitiés n La bande passante disponible est la totalité des bandes passantes des liens disponibles. n Diviser la bande passante disponible par le nombre de processeurs. Architecture matérielle des machines parallèles 16

Comparaison d’une interconnexion à cross-bar vs bus Architecture matérielle des machines parallèles 17

Architecture de la machine CRAY-T 3 E

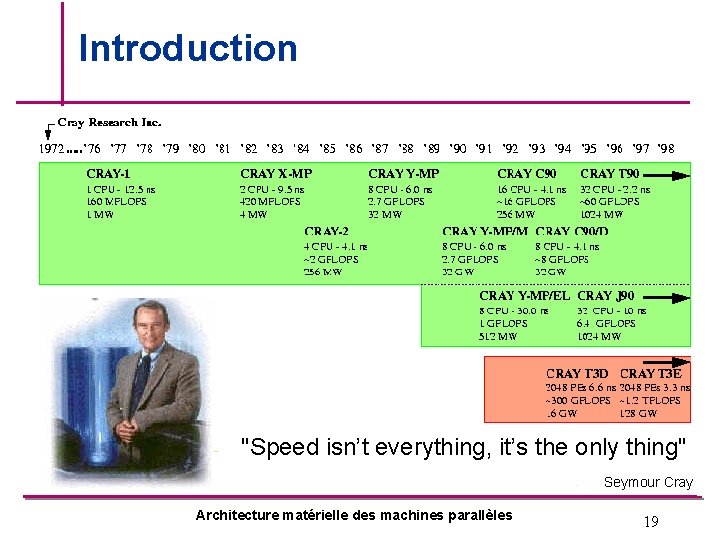

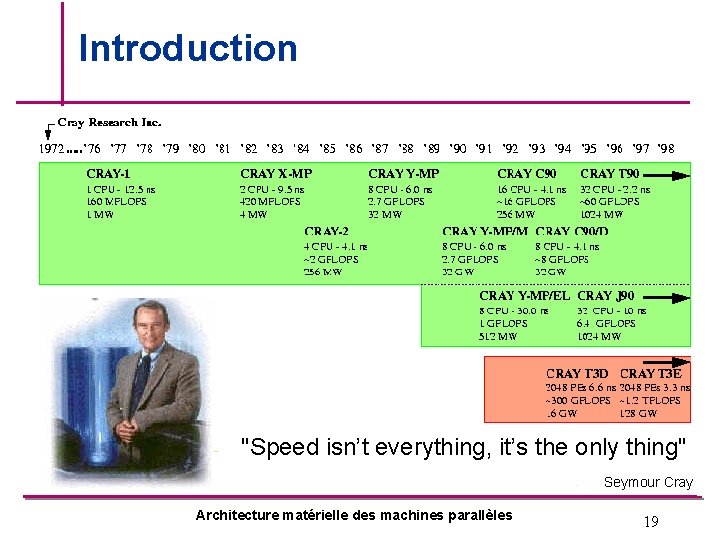

Introduction - "Speed isn’t everything, it’s the only thing" - Architecture matérielle des machines parallèles Seymour Cray 19

Cray T 3 E n CRAY T 3 E est un multiprocesseur à mémoire distribuée basé sur le microprocesseur Alpha 21164 de DEC: • Modèle à refroidissement par liquide • Modèle à refroidissement par air Architecture matérielle des machines parallèles 20

Architecture matérielle du Cray T 3 E n Capacité en nœud du Cray T 3 E • peut être étendu jusqu ’à 8 cabines • Chaque cabine peut héberger jusqu ’à 34 modules • Chaque module contient 8 nœud-processeurs • Capacité de 272 nœud-processeurs/cabine • Capacité maximale de 2176 nœud-processeurs Architecture matérielle des machines parallèles 21

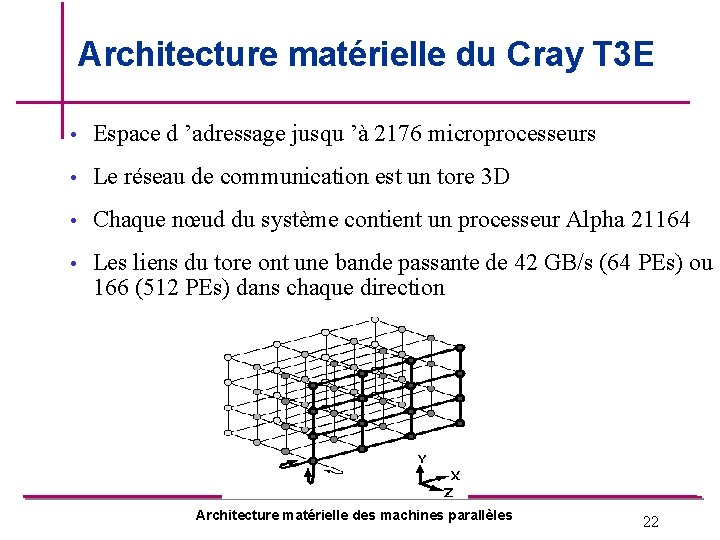

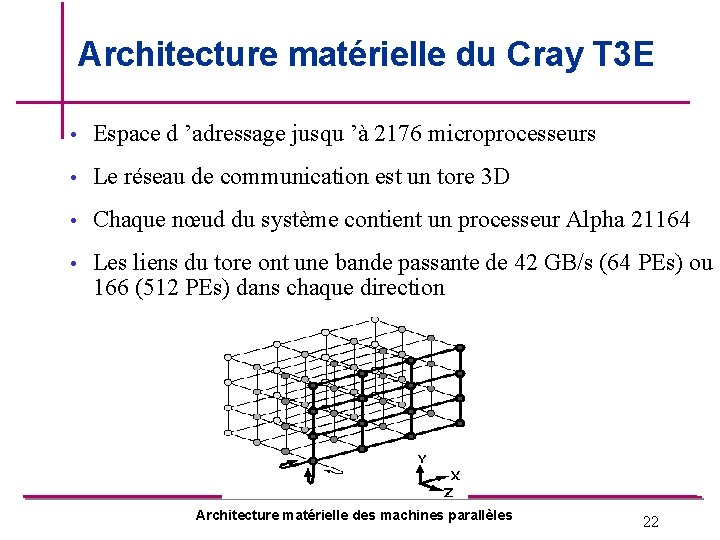

Architecture matérielle du Cray T 3 E • Espace d ’adressage jusqu ’à 2176 microprocesseurs • Le réseau de communication est un tore 3 D • Chaque nœud du système contient un processeur Alpha 21164 • Les liens du tore ont une bande passante de 42 GB/s (64 PEs) ou 166 (512 PEs) dans chaque direction Architecture matérielle des machines parallèles 22

Architecture matérielle du Cray T 3 E • Liaison ajoutée entre les éléments latéraux • Communication full duplex • Nombre total de tore: l×m+m×n+l×n • Nombre de bus: 6×l×m×n • Pour une architecture de 128 éléments on a 80 Tores et 768 Bus Architecture matérielle des machines parallèles 23

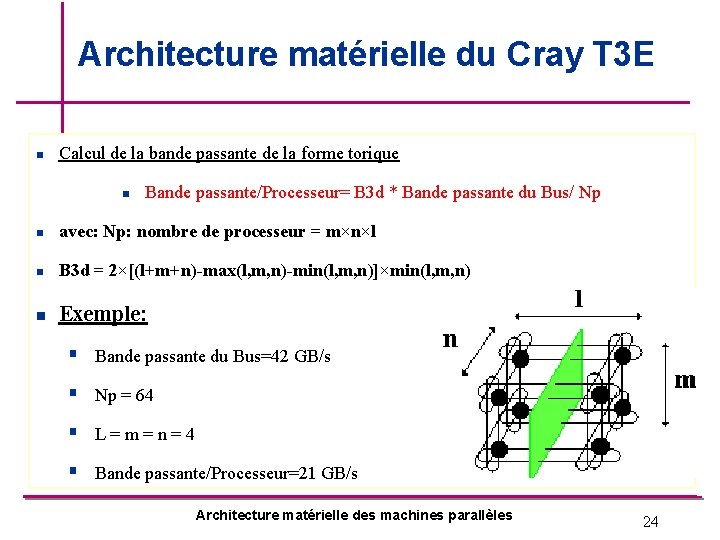

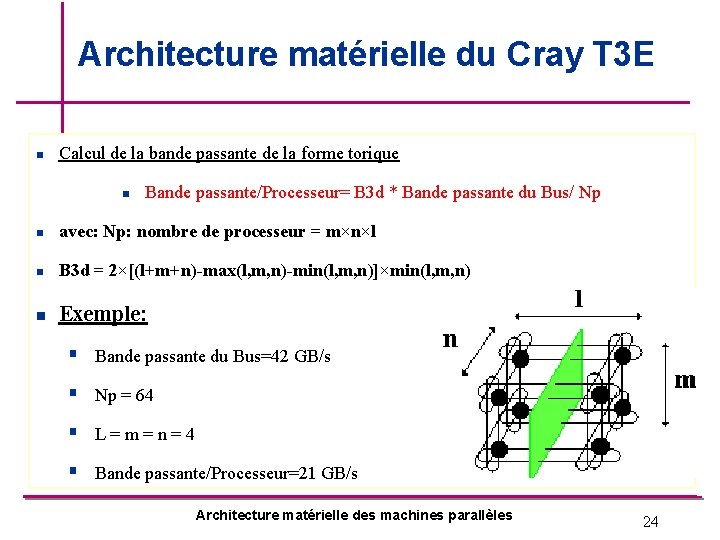

Architecture matérielle du Cray T 3 E n Calcul de la bande passante de la forme torique n Bande passante/Processeur= B 3 d * Bande passante du Bus/ Np n avec: Np: nombre de processeur = m×n×l n B 3 d = 2×[(l+m+n)-max(l, m, n)-min(l, m, n)]×min(l, m, n) n Exemple: § Bande passante du Bus=42 GB/s § Np = 64 § L = m = n = 4 § Bande passante/Processeur=21 GB/s Architecture matérielle des machines parallèles 24

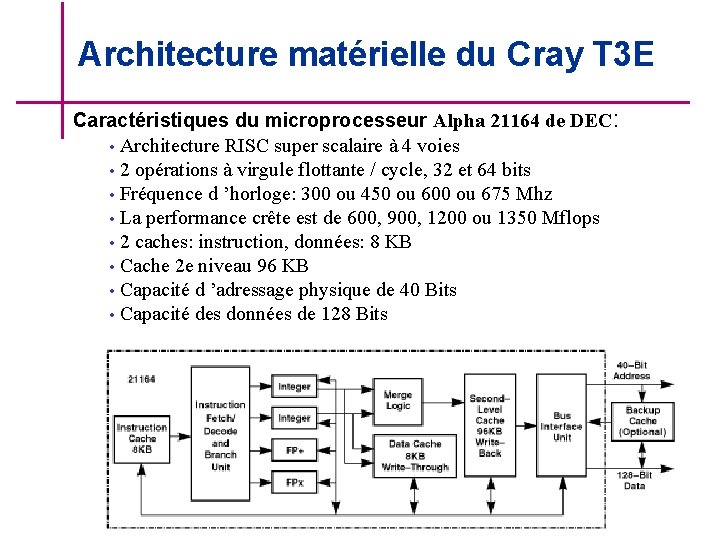

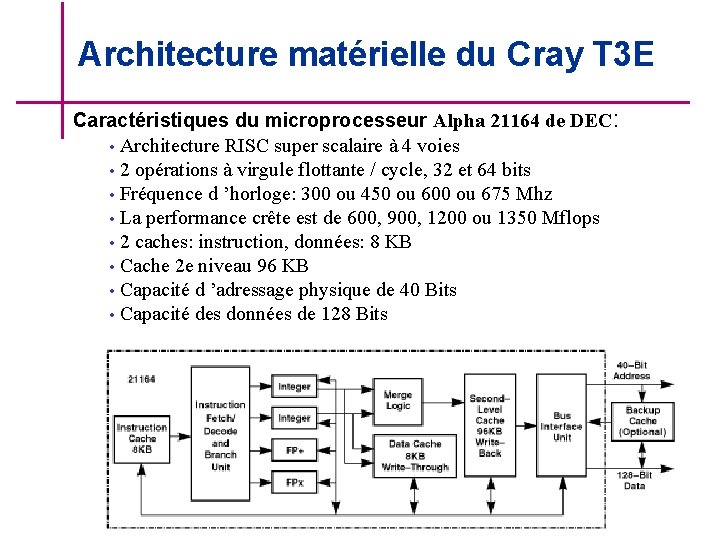

Architecture matérielle du Cray T 3 E Caractéristiques du microprocesseur Alpha 21164 de DEC: • Architecture RISC super scalaire à 4 voies • 2 opérations à virgule flottante / cycle, 32 et 64 bits • Fréquence d ’horloge: 300 ou 450 ou 600 ou 675 Mhz • La performance crête est de 600, 900, 1200 ou 1350 Mflops • 2 caches: instruction, données: 8 KB • Cache 2 e niveau 96 KB • Capacité d ’adressage physique de 40 Bits • Capacité des données de 128 Bits Architecture matérielle des machines parallèles 25

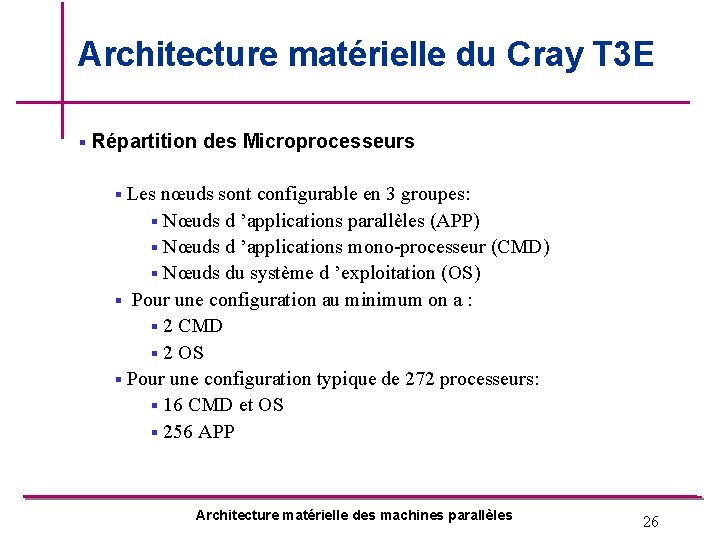

Architecture matérielle du Cray T 3 E § Répartition des Microprocesseurs § Les nœuds sont configurable en 3 groupes: § Nœuds d ’applications parallèles (APP) § Nœuds d ’applications mono-processeur (CMD) § Nœuds du système d ’exploitation (OS) § Pour une configuration au minimum on a : § 2 CMD § 2 OS § Pour une configuration typique de 272 processeurs: § 16 CMD et OS § 256 APP Architecture matérielle des machines parallèles 26

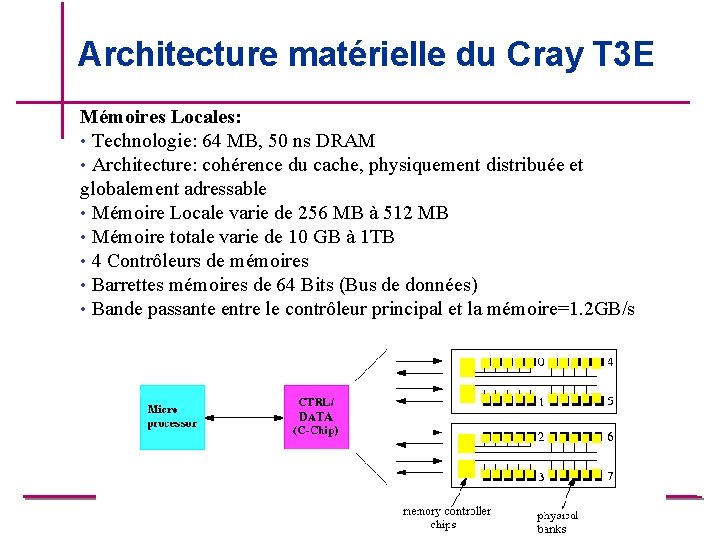

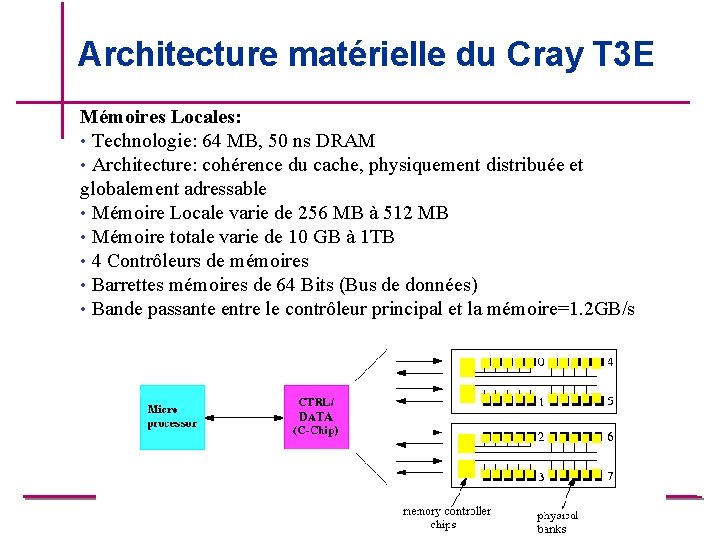

Architecture matérielle du Cray T 3 E Mémoires Locales: • Technologie: 64 MB, 50 ns DRAM • Architecture: cohérence du cache, physiquement distribuée et globalement adressable • Mémoire Locale varie de 256 MB à 512 MB • Mémoire totale varie de 10 GB à 1 TB • 4 Contrôleurs de mémoires • Barrettes mémoires de 64 Bits (Bus de données) • Bande passante entre le contrôleur principal et la mémoire=1. 2 GB/s Architecture matérielle des machines parallèles 27

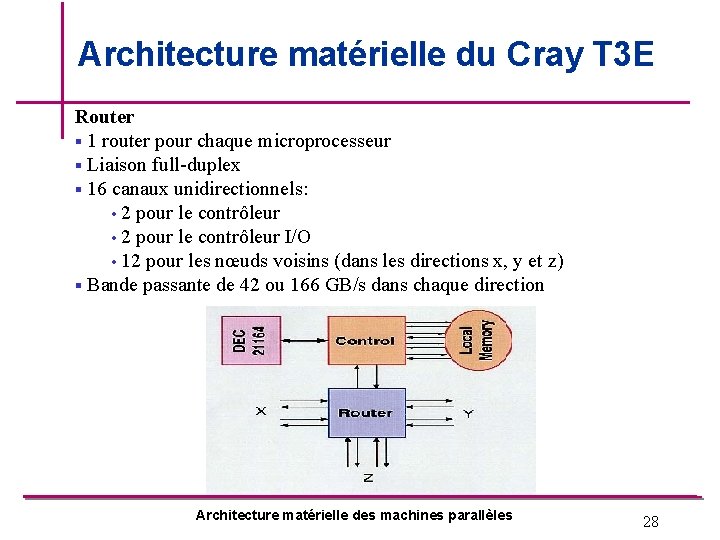

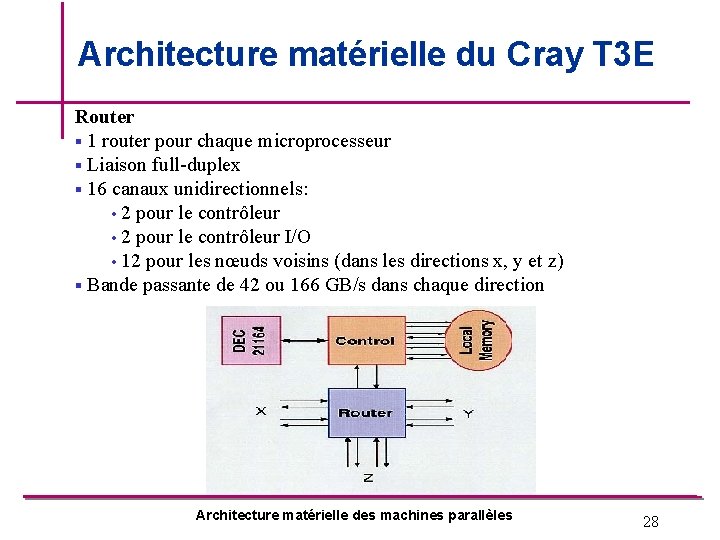

Architecture matérielle du Cray T 3 E Router § 1 router pour chaque microprocesseur § Liaison full-duplex § 16 canaux unidirectionnels: • 2 pour le contrôleur I/O • 12 pour les nœuds voisins (dans les directions x, y et z) § Bande passante de 42 ou 166 GB/s dans chaque direction Architecture matérielle des machines parallèles 28

Configuration standard § Le système est commercialisé avec des configurations de 40 à 2176 processeurs en deux versions: refroidies à l'air et à l'eau § Performance crête de 54 GFlops à 3 TFlops Architecture matérielle des machines parallèles 29

Logiciels fonctionnant sur Cray • OS: UNICOS • C++ compiler • C++ Tools and Math. Pack • ANSI C compiler • Fortran compiler • Libsma Libm Libsci Libcomm (BLACS) • Libfi Total View Apprentice which helps users tune application performance • MPT (Message Passing Toolkit), PVM (Parallel Virtual Machine), MPI (Message Passing Interface) Xbrowse Architecture matérielle des machines parallèles 30

Applications, utilisateurs et utilisations Types d'utilisations · · · Recherches nécessitant la puissance d’un super-calculateur Centres informatiques offrant une grande variété d’environnement de développement Fournisseur d’accès distant pour les informations multimédia Aide à la prise de décisions critiques Programme à applications parallèles Résolution des problèmes scientifiques et techniques dans des domaines tels que: · · · l’aérospatiale, l’automobile, la finance, la modélisation, la prévision météorologique, la prospection des gisements de pétrole et de gaz … Architecture matérielle des machines parallèles 31

Applications, utilisateurs et utilisations (suite) Utilisateurs Alfred Wegener Institut (AWI) Scientifique (CNRS/IDRIS) Bear Stearns Japan Advanced Institute of Science and Technology (JAIST) California Institute of Technology/Jet Propulsion Laboratory KIST/System Engineering Research Institute (ETRI) Center for Scientific Computing (CSC) CIEMAT (Centro de Investigaciones Energéticas Mediambientales y Tecnológicas) CINECA Los Alamos National Laboratory Max-Planck-Gesellschaft Network Computing Services (Minnesota Supercomputer Center) NASA Goddard Space Flight Center CSAR at the University of Manchester Commissariat à l'énergie atomique (CEA) Deutscher Wetterdienst National Energy Research Scientific Computing Center (NERSC) National Institute for Water and Atmospheric Research Defense Evaluation and Research Agency (DERA) Ecole Polytechnique Federale de Lausanne EXXON National Supercomputer Center (NSC) Naval Oceanographic Office (NAVOCEANO) NOAA/Geophysical Fluid Dynamic Laboratory Forschungzentrum Juelich (FZJ) Insitute du Developpement et des Ressources en Informatique Norwegian University of Science and Technology …. . Architecture matérielle des machines parallèles 32