Architecture CH 006 Figure 6 1 ARM byteaddressable

Architecture CH 006

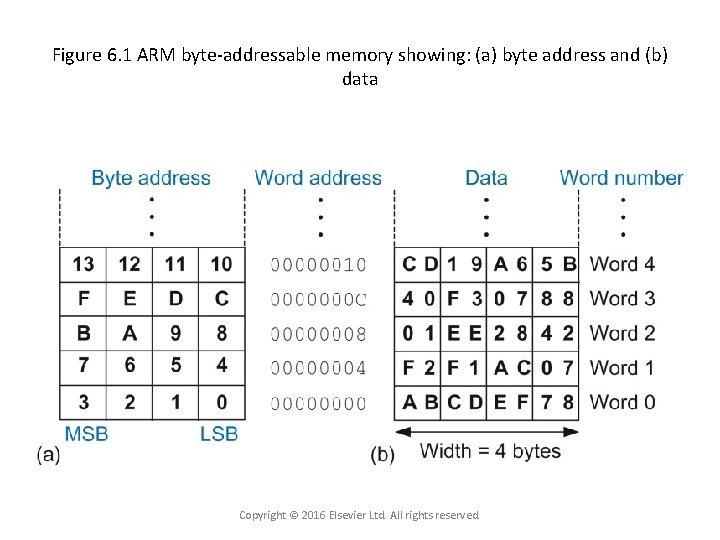

Figure 6. 1 ARM byte-addressable memory showing: (a) byte address and (b) data Copyright © 2016 Elsevier Ltd. All rights reserved.

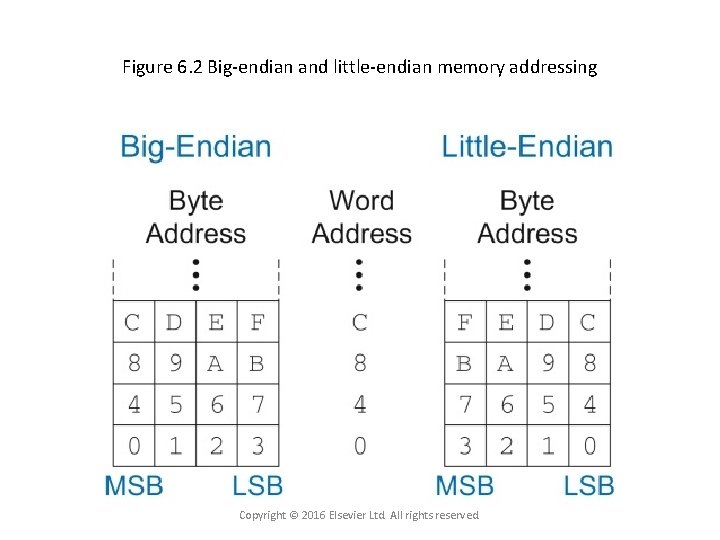

Figure 6. 2 Big-endian and little-endian memory addressing Copyright © 2016 Elsevier Ltd. All rights reserved.

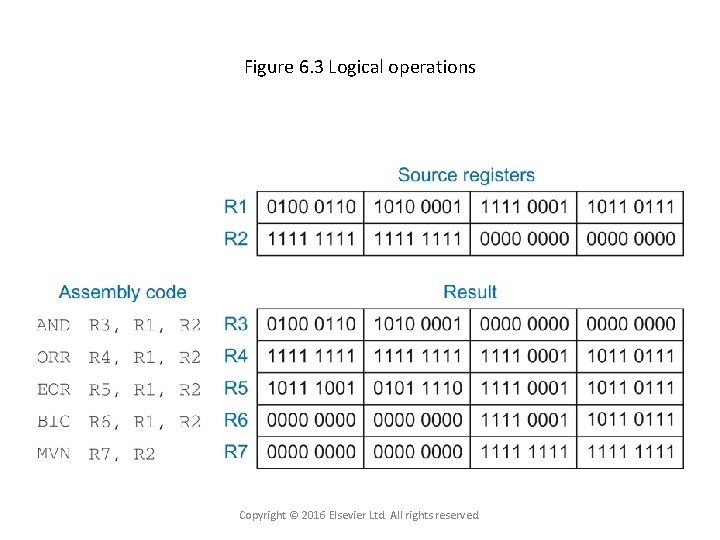

Figure 6. 3 Logical operations Copyright © 2016 Elsevier Ltd. All rights reserved.

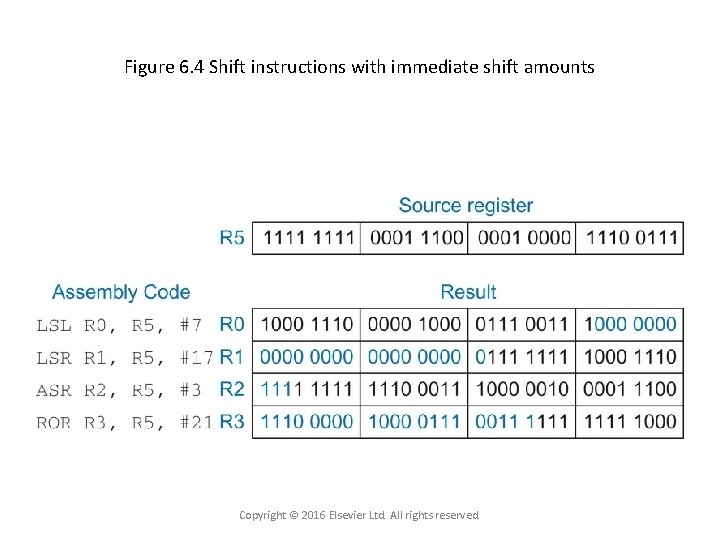

Figure 6. 4 Shift instructions with immediate shift amounts Copyright © 2016 Elsevier Ltd. All rights reserved.

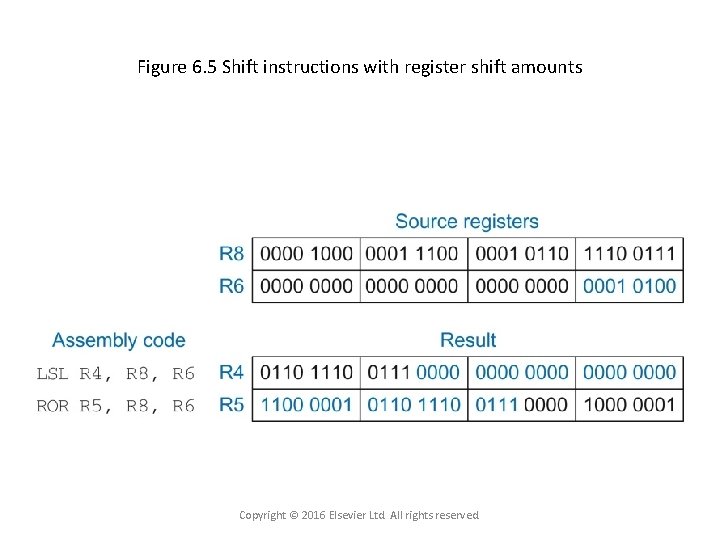

Figure 6. 5 Shift instructions with register shift amounts Copyright © 2016 Elsevier Ltd. All rights reserved.

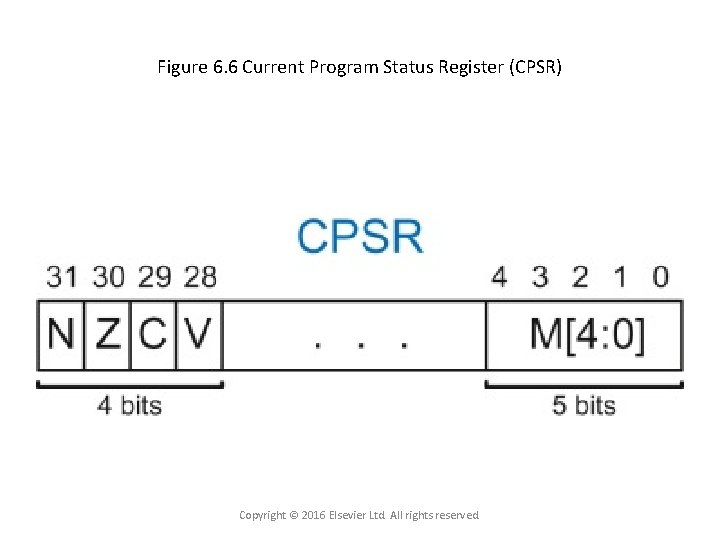

Figure 6. 6 Current Program Status Register (CPSR) Copyright © 2016 Elsevier Ltd. All rights reserved.

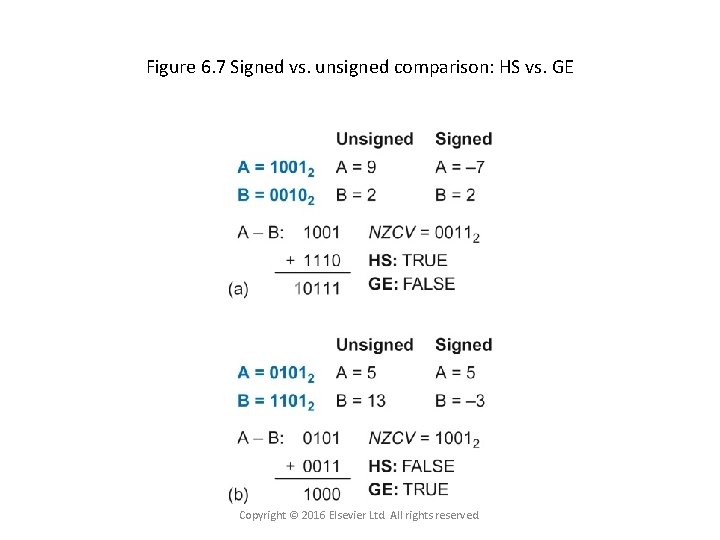

Figure 6. 7 Signed vs. unsigned comparison: HS vs. GE Copyright © 2016 Elsevier Ltd. All rights reserved.

![Figure 6. 8 Memory holding scores[200] starting at base address 0 x 14000000 Copyright Figure 6. 8 Memory holding scores[200] starting at base address 0 x 14000000 Copyright](http://slidetodoc.com/presentation_image_h2/37b4c03eaa85114a3f67a9f34bf60131/image-9.jpg)

Figure 6. 8 Memory holding scores[200] starting at base address 0 x 14000000 Copyright © 2016 Elsevier Ltd. All rights reserved.

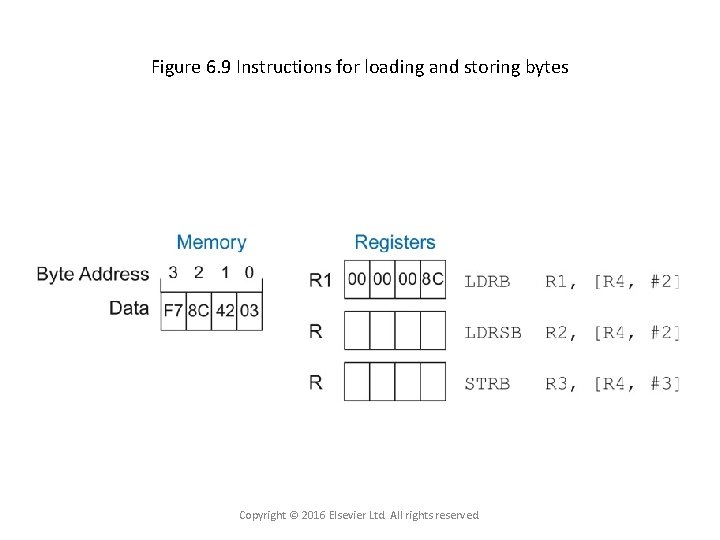

Figure 6. 9 Instructions for loading and storing bytes Copyright © 2016 Elsevier Ltd. All rights reserved.

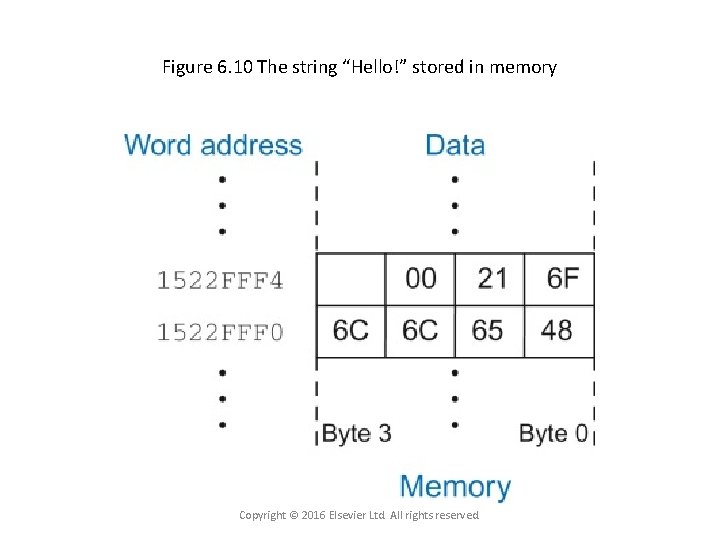

Figure 6. 10 The string “Hello!” stored in memory Copyright © 2016 Elsevier Ltd. All rights reserved.

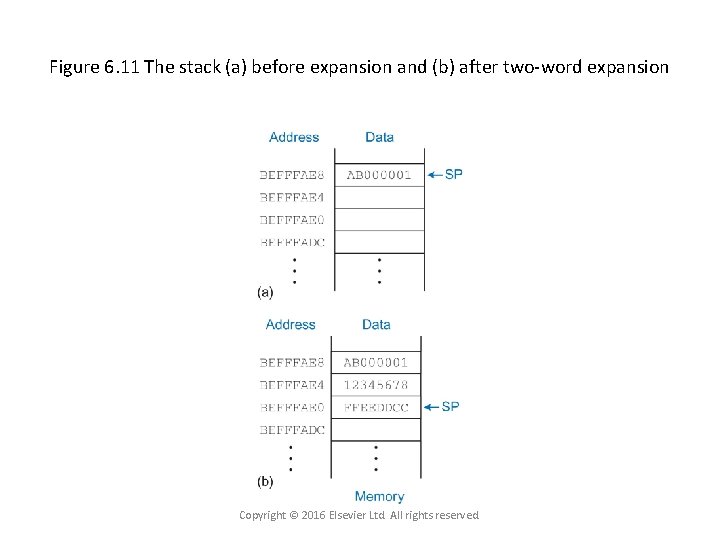

Figure 6. 11 The stack (a) before expansion and (b) after two-word expansion Copyright © 2016 Elsevier Ltd. All rights reserved.

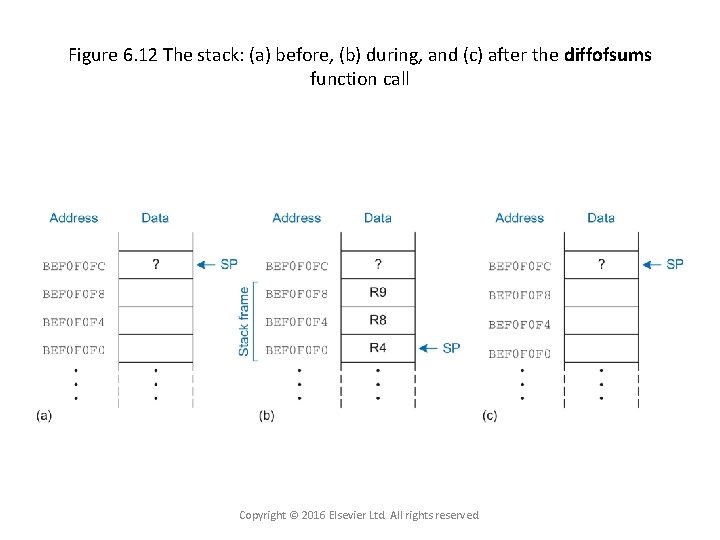

Figure 6. 12 The stack: (a) before, (b) during, and (c) after the diffofsums function call Copyright © 2016 Elsevier Ltd. All rights reserved.

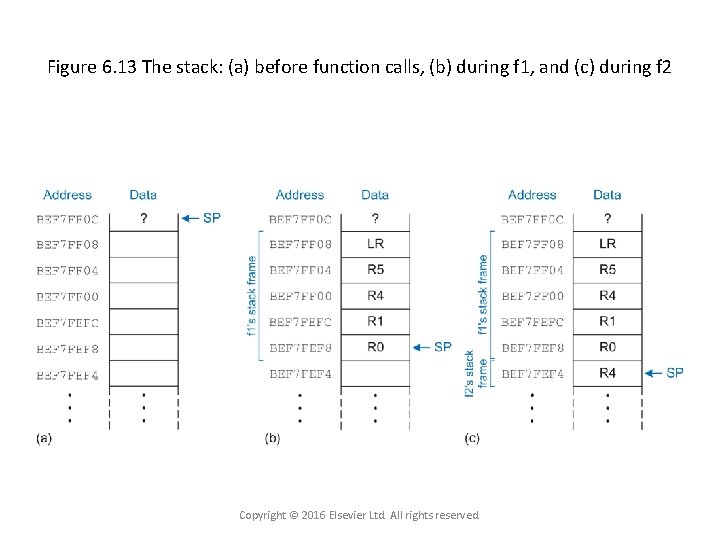

Figure 6. 13 The stack: (a) before function calls, (b) during f 1, and (c) during f 2 Copyright © 2016 Elsevier Ltd. All rights reserved.

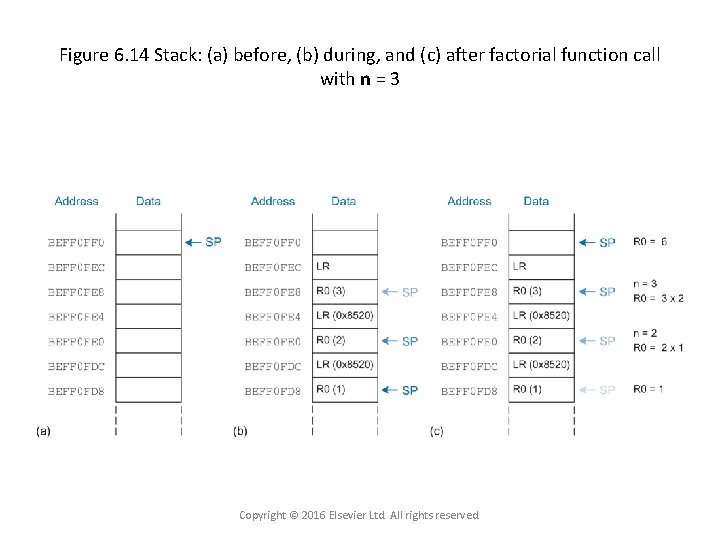

Figure 6. 14 Stack: (a) before, (b) during, and (c) after factorial function call with n = 3 Copyright © 2016 Elsevier Ltd. All rights reserved.

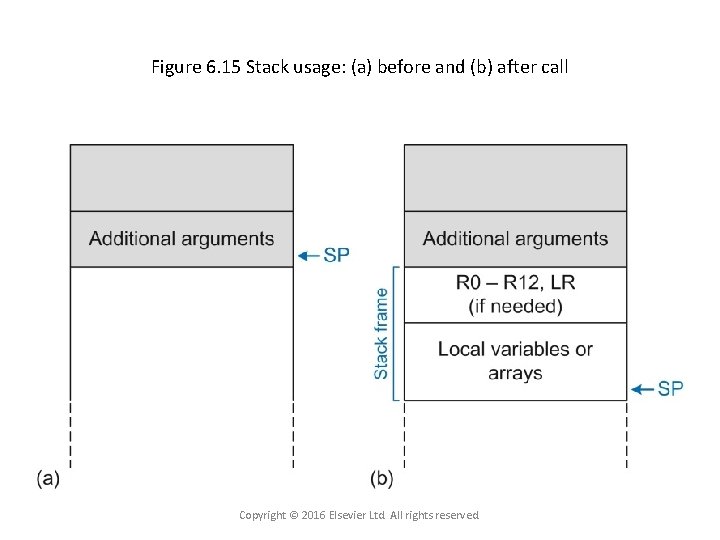

Figure 6. 15 Stack usage: (a) before and (b) after call Copyright © 2016 Elsevier Ltd. All rights reserved.

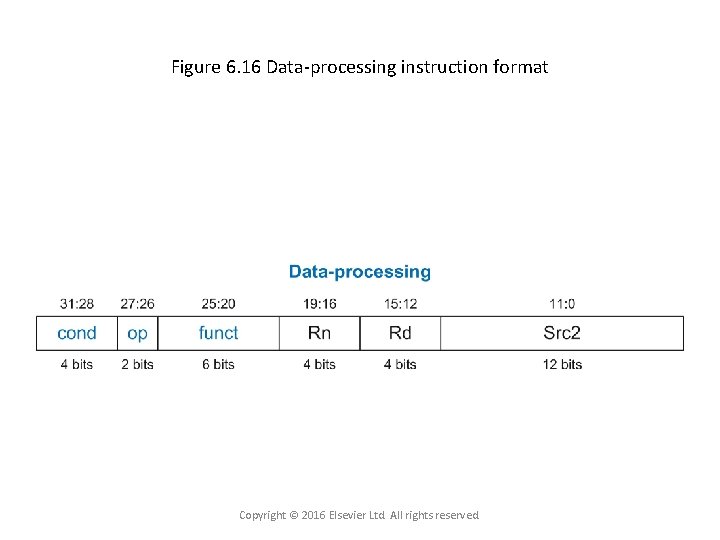

Figure 6. 16 Data-processing instruction format Copyright © 2016 Elsevier Ltd. All rights reserved.

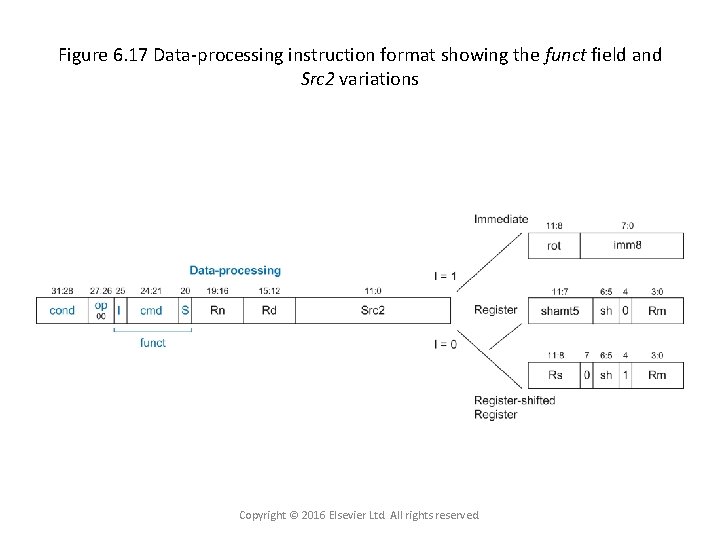

Figure 6. 17 Data-processing instruction format showing the funct field and Src 2 variations Copyright © 2016 Elsevier Ltd. All rights reserved.

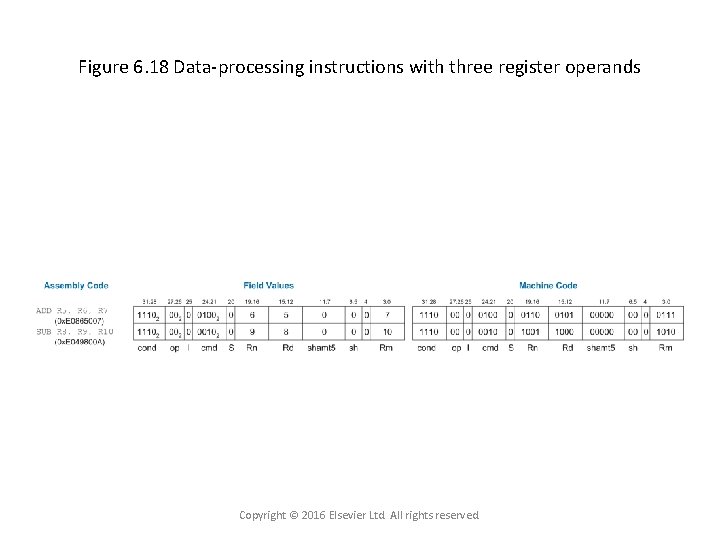

Figure 6. 18 Data-processing instructions with three register operands Copyright © 2016 Elsevier Ltd. All rights reserved.

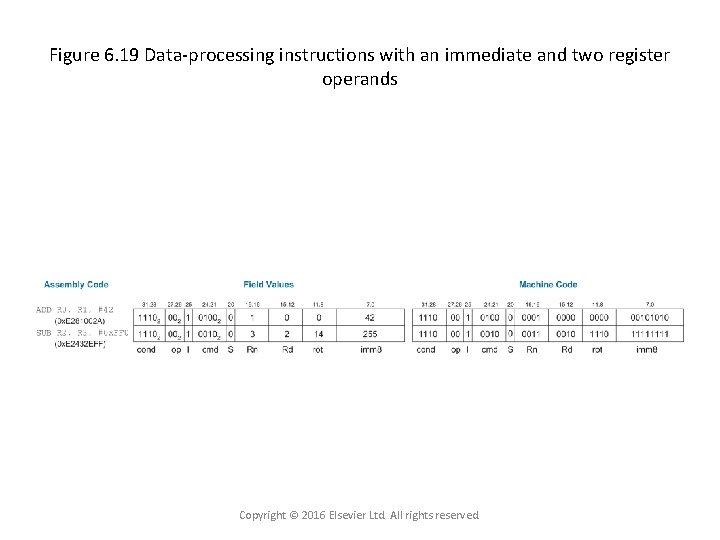

Figure 6. 19 Data-processing instructions with an immediate and two register operands Copyright © 2016 Elsevier Ltd. All rights reserved.

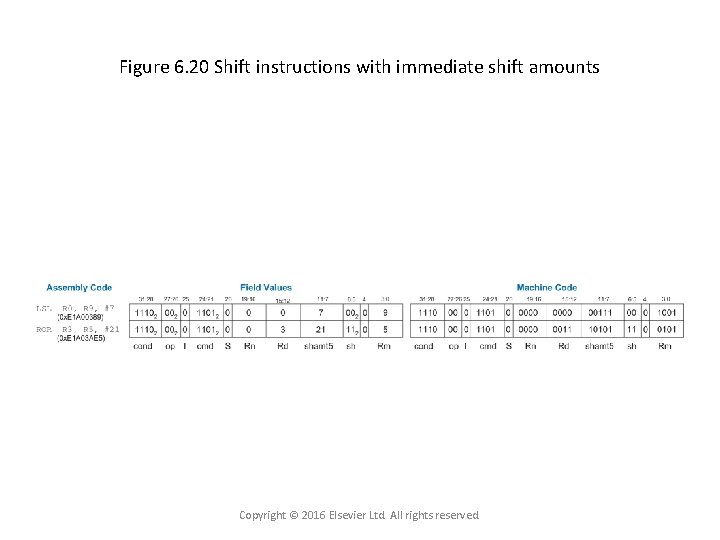

Figure 6. 20 Shift instructions with immediate shift amounts Copyright © 2016 Elsevier Ltd. All rights reserved.

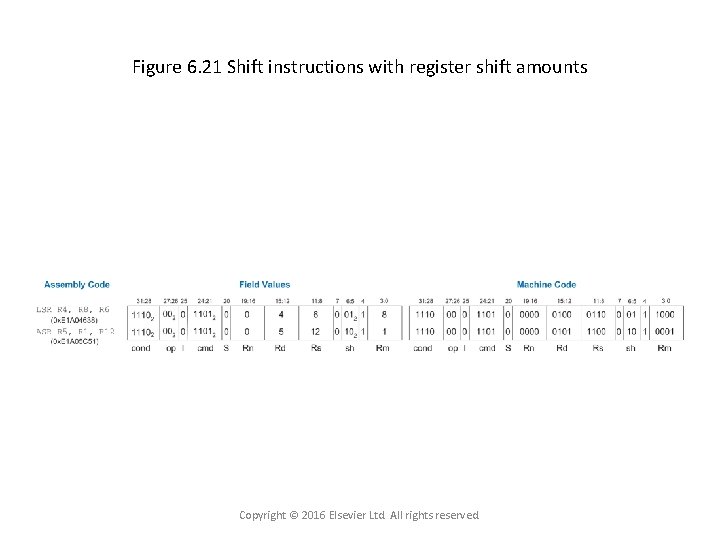

Figure 6. 21 Shift instructions with register shift amounts Copyright © 2016 Elsevier Ltd. All rights reserved.

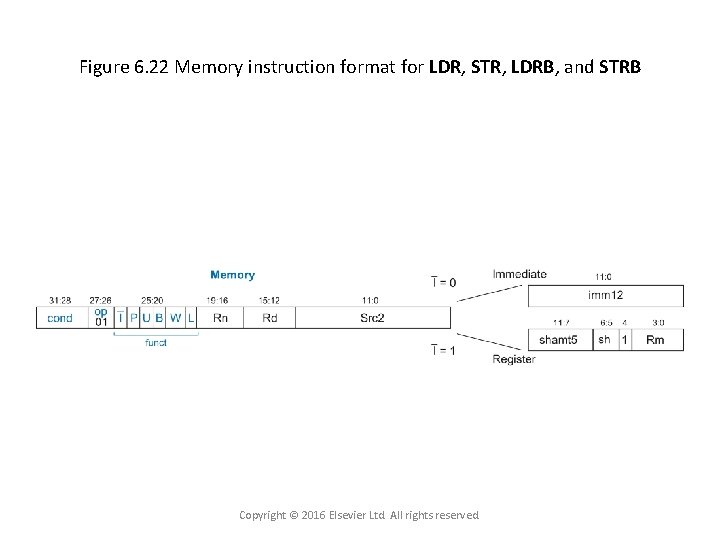

Figure 6. 22 Memory instruction format for LDR, STR, LDRB, and STRB Copyright © 2016 Elsevier Ltd. All rights reserved.

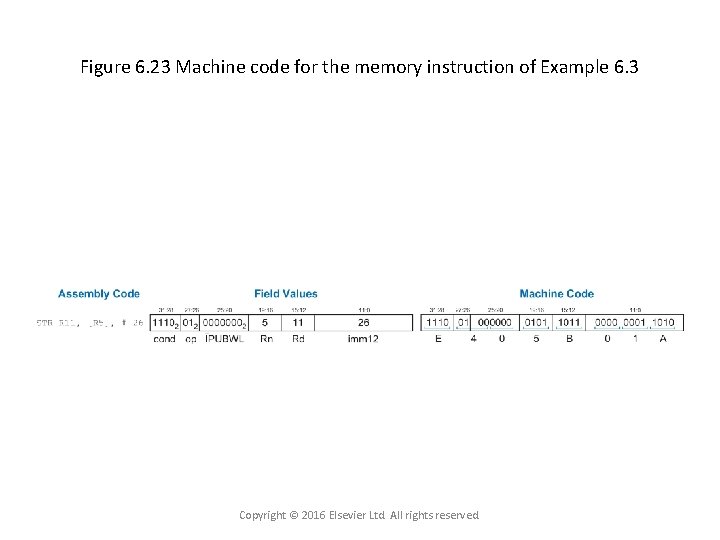

Figure 6. 23 Machine code for the memory instruction of Example 6. 3 Copyright © 2016 Elsevier Ltd. All rights reserved.

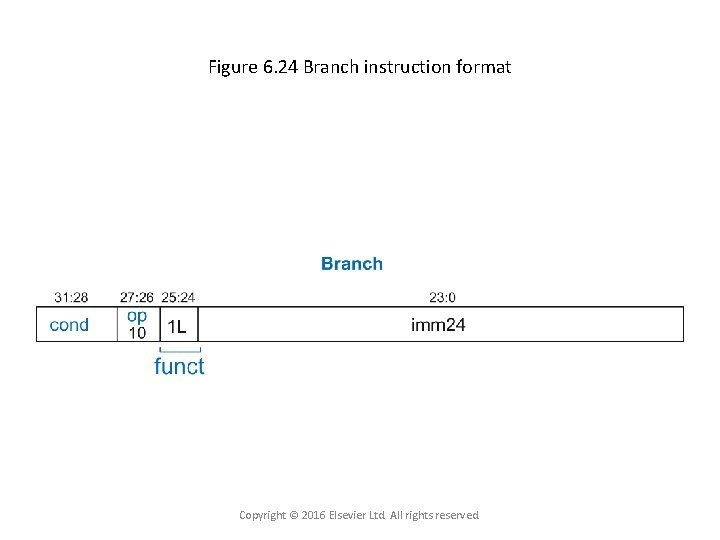

Figure 6. 24 Branch instruction format Copyright © 2016 Elsevier Ltd. All rights reserved.

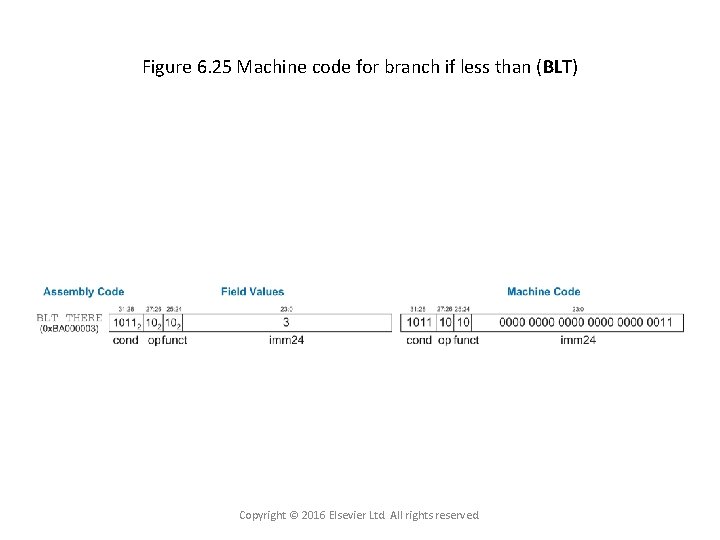

Figure 6. 25 Machine code for branch if less than (BLT) Copyright © 2016 Elsevier Ltd. All rights reserved.

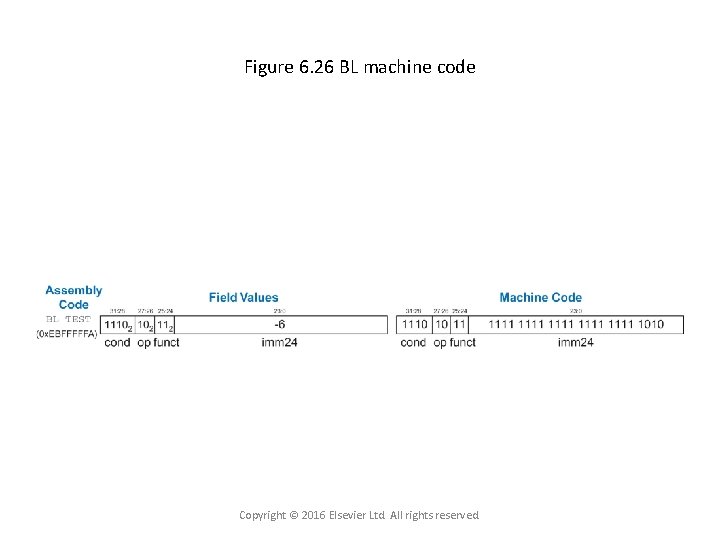

Figure 6. 26 BL machine code Copyright © 2016 Elsevier Ltd. All rights reserved.

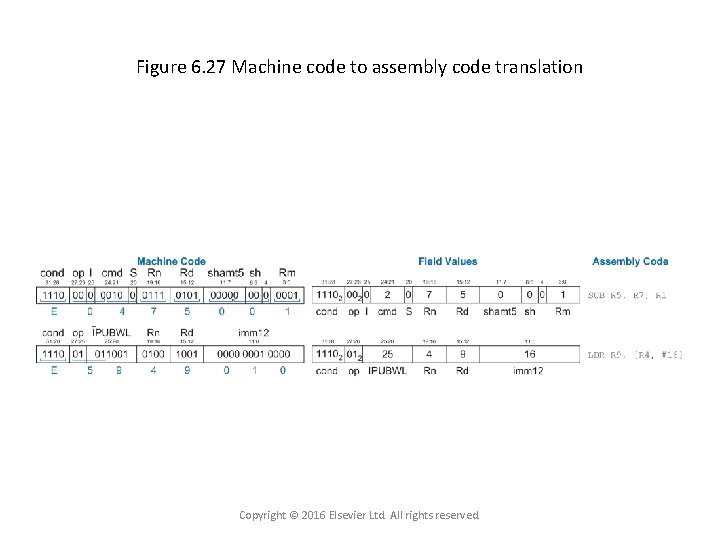

Figure 6. 27 Machine code to assembly code translation Copyright © 2016 Elsevier Ltd. All rights reserved.

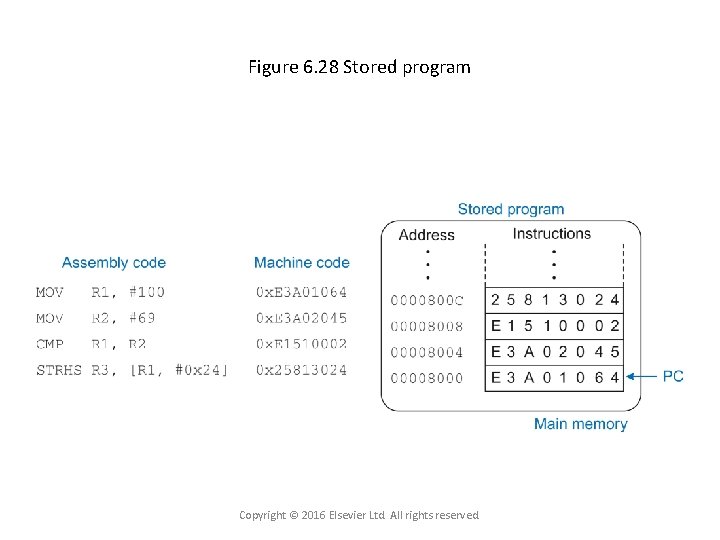

Figure 6. 28 Stored program Copyright © 2016 Elsevier Ltd. All rights reserved.

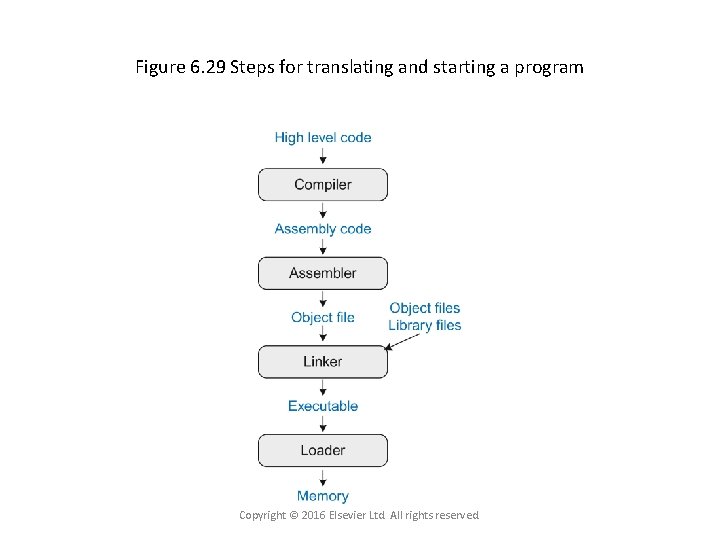

Figure 6. 29 Steps for translating and starting a program Copyright © 2016 Elsevier Ltd. All rights reserved.

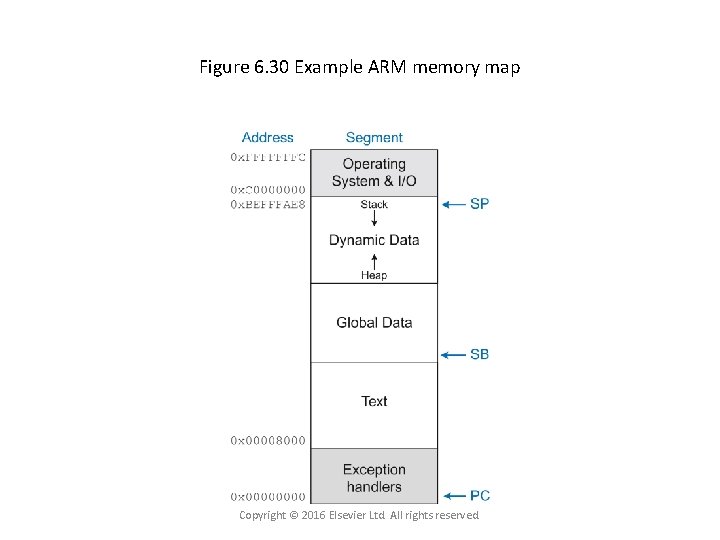

Figure 6. 30 Example ARM memory map Copyright © 2016 Elsevier Ltd. All rights reserved.

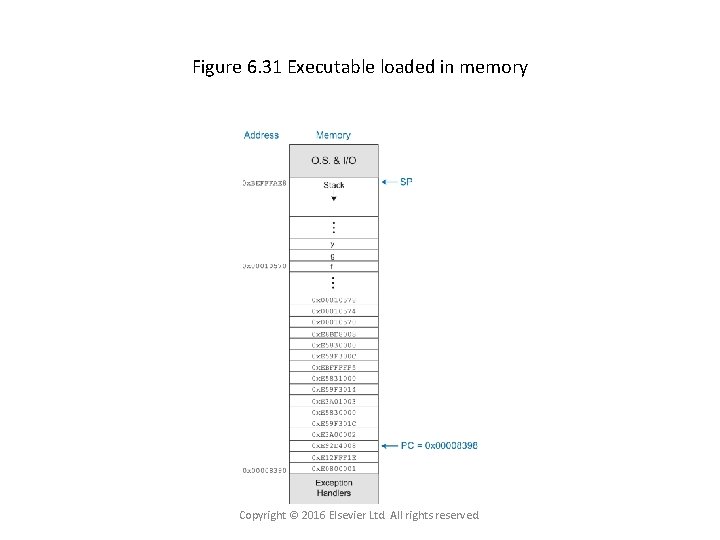

Figure 6. 31 Executable loaded in memory Copyright © 2016 Elsevier Ltd. All rights reserved.

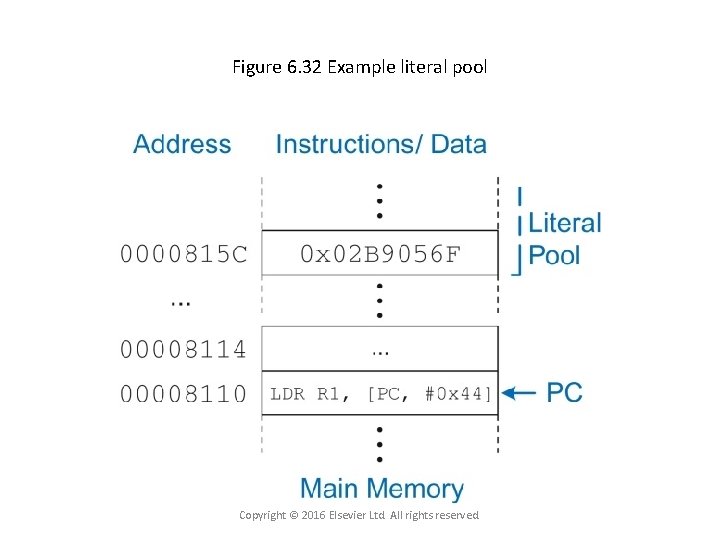

Figure 6. 32 Example literal pool Copyright © 2016 Elsevier Ltd. All rights reserved.

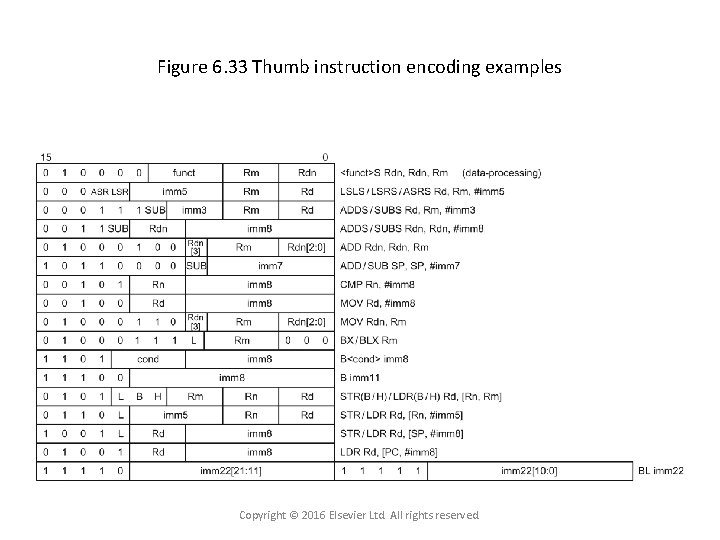

Figure 6. 33 Thumb instruction encoding examples Copyright © 2016 Elsevier Ltd. All rights reserved.

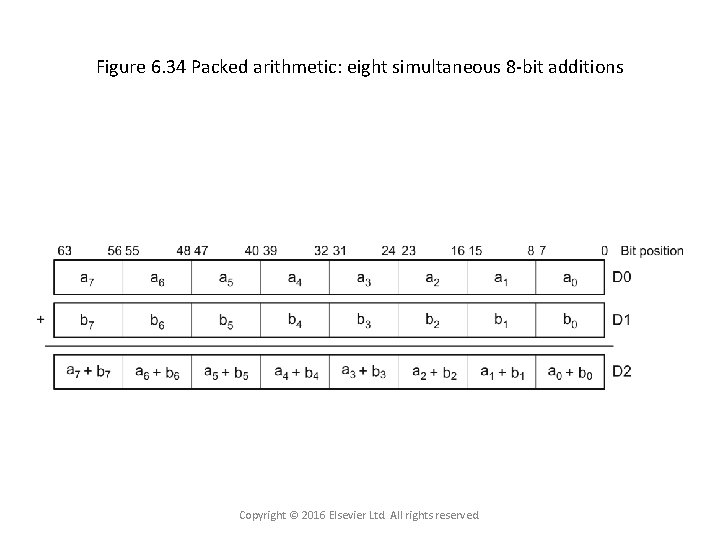

Figure 6. 34 Packed arithmetic: eight simultaneous 8 -bit additions Copyright © 2016 Elsevier Ltd. All rights reserved.

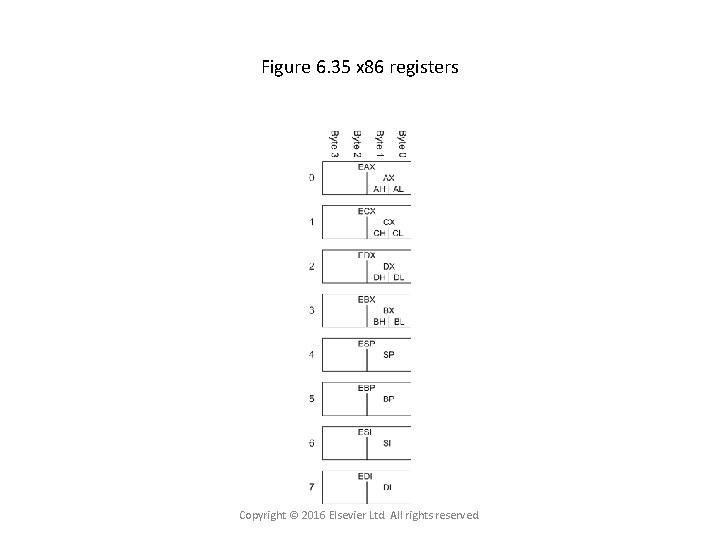

Figure 6. 35 x 86 registers Copyright © 2016 Elsevier Ltd. All rights reserved.

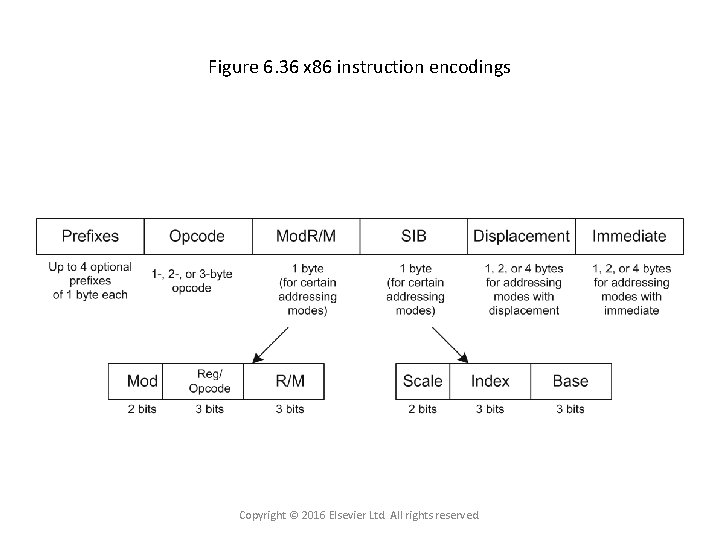

Figure 6. 36 x 86 instruction encodings Copyright © 2016 Elsevier Ltd. All rights reserved.

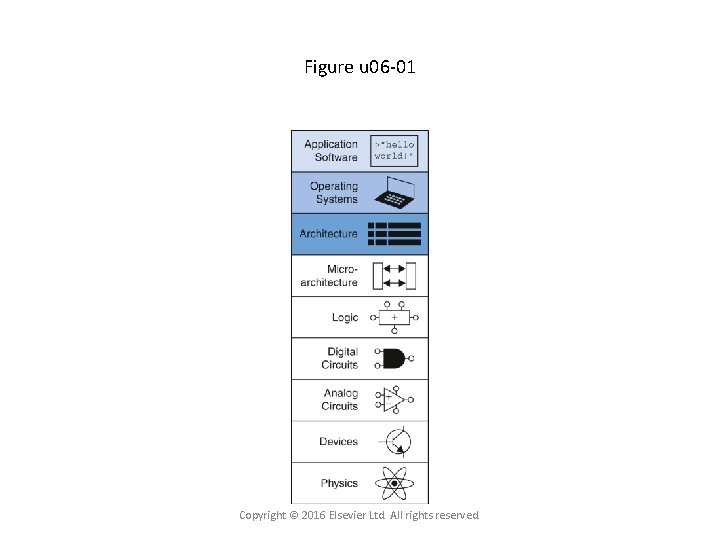

Figure u 06 -01 Copyright © 2016 Elsevier Ltd. All rights reserved.

Copyright © 2016 Elsevier Ltd. All rights reserved.

Copyright © 2016 Elsevier Ltd. All rights reserved.

Copyright © 2016 Elsevier Ltd. All rights reserved.

Copyright © 2016 Elsevier Ltd. All rights reserved.

- Slides: 42