Applicazioni di Calcolo Reconfigurable per Sistemi Embedded ad

Applicazioni di Calcolo Reconfigurable per Sistemi Embedded ad Alte Prestazioni Fabio Campi Corso di Elettronica dei Sistemi Digitali Aa 2003 -2004 23 Ottobre 2002 Sviluppo di una metodologia di progetto per un sistema on-chip basato su architettura riconfigurabile

Data Flow Graph Res=(a+b)2 – 3*(c+d) +e

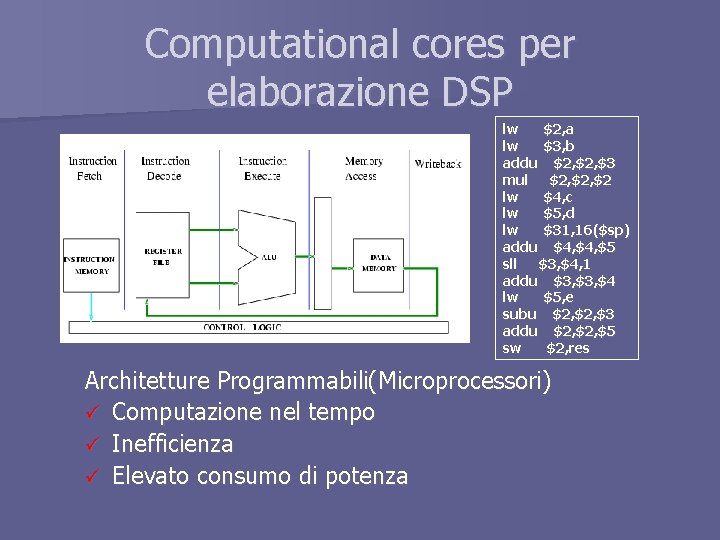

Computational cores per elaborazione DSP lw $2, a lw $3, b addu $2, $3 mul $2, $2 lw $4, c lw $5, d lw $31, 16($sp) addu $4, $5 sll $3, $4, 1 addu $3, $4 lw $5, e subu $2, $3 addu $2, $5 sw $2, res Architetture Programmabili(Microprocessori) ü Computazione nel tempo ü Inefficienza ü Elevato consumo di potenza

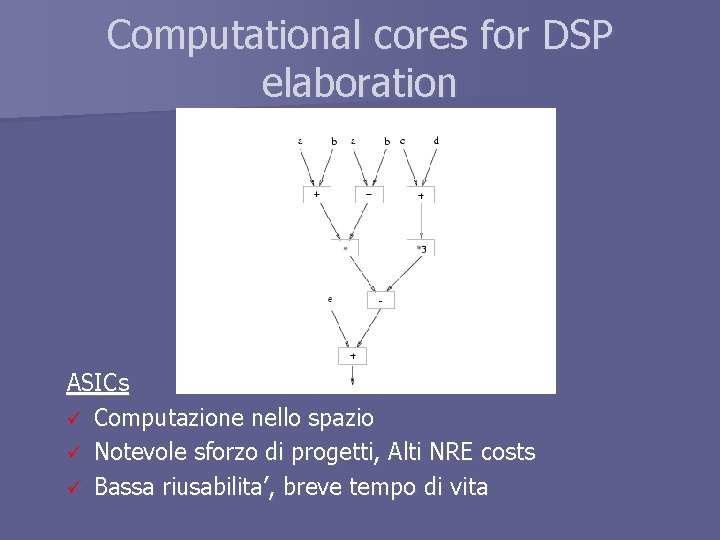

Computational cores for DSP elaboration ASICs ü Computazione nello spazio ü Notevole sforzo di progetti, Alti NRE costs ü Bassa riusabilita’, breve tempo di vita

Computational cores per elaborazione DSP Fu #1 Fu #2 Processori DSP Unita’ funzionali application-specific applicate ad un ambiente software-programmable ü Difficolta’ con i compilatori -> largo uso di assembly ü

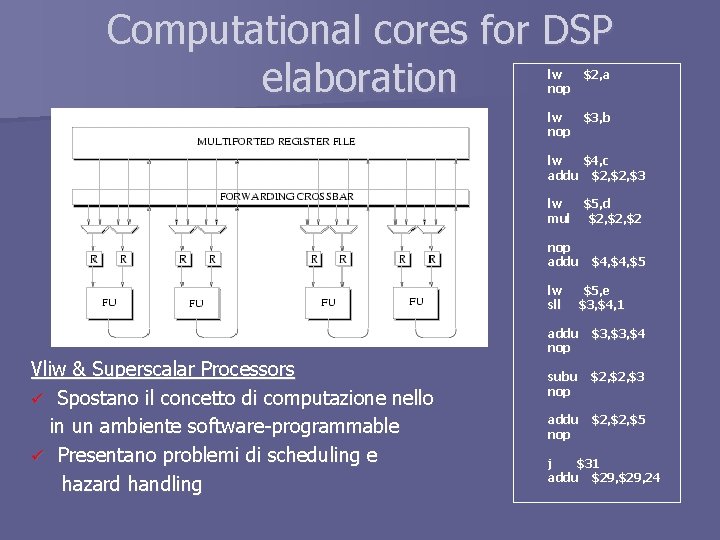

Computational cores for DSP elaboration lw nop $2, a lw nop $3, b lw $4, c addu $2, $3 lw mul nop addu lw sll Vliw & Superscalar Processors ü Spostano il concetto di computazione nello in un ambiente software-programmable ü Presentano problemi di scheduling e hazard handling $5, d $2, $2 $4, $5 $5, e $3, $4, 1 addu nop $3, $4 subu nop $2, $3 addu nop $2, $5 j $31 addu $29, 24

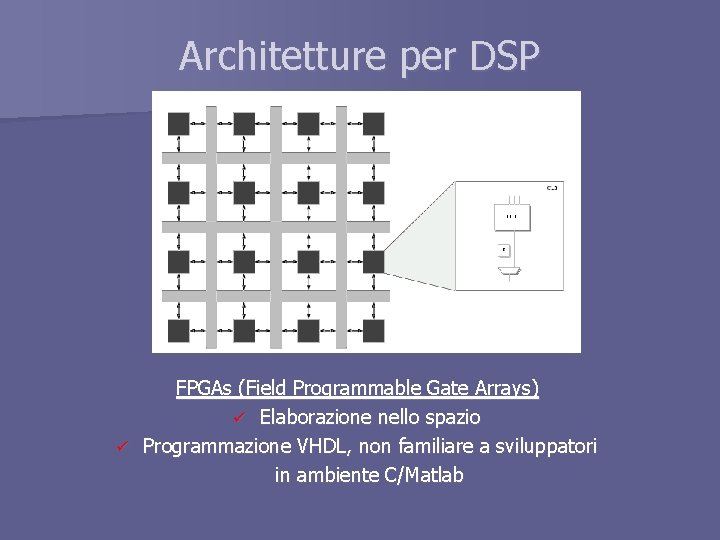

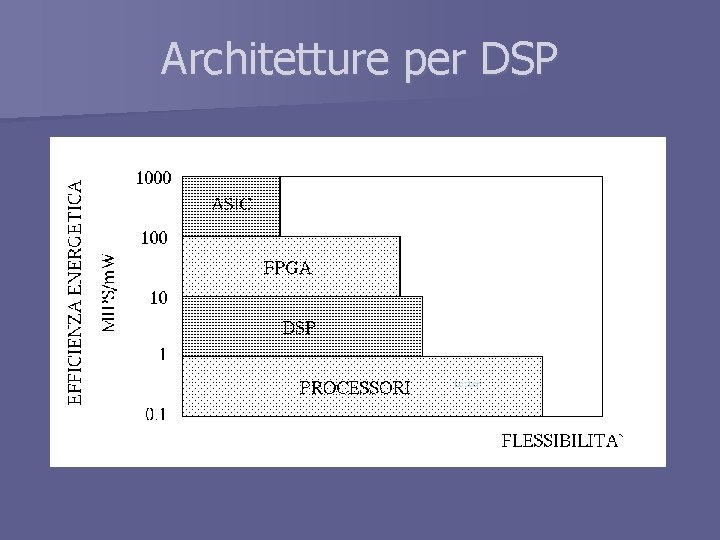

Architetture per DSP FPGAs (Field Programmable Gate Arrays) ü Elaborazione nello spazio ü Programmazione VHDL, non familiare a sviluppatori in ambiente C/Matlab

Architetture per DSP

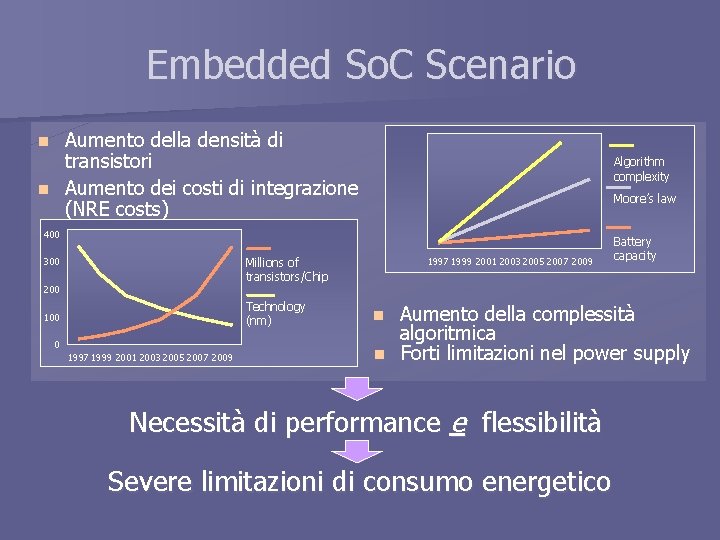

Embedded So. C Scenario Aumento della densità di transistori n Aumento dei costi di integrazione (NRE costs) n Algorithm complexity Moore’s law 400 Millions of transistors/Chip 300 200 Technology (nm) 100 0 1997 1999 2001 2003 2005 2007 2009 Battery capacity Aumento della complessità algoritmica n Forti limitazioni nel power supply n Necessità di performance e flessibilità Severe limitazioni di consumo energetico

Analisi Algoritmica per applicazioni DSP n 90% della complessità computazionale è concentrata sul 10% del codice ü Si può utilizzare application-specific hardware n Molti algoritmi hanno un instruction-level parallelism ü Utilizzo di multiple parallel data paths n p. La granularità degli operandi è spesso diversa da 32 -bit ü Le ALU tradizionali sono power-inefficient Miglioramenti significativi si possono ottenere utilizzando processori estesi da unità funzionali Application Specific

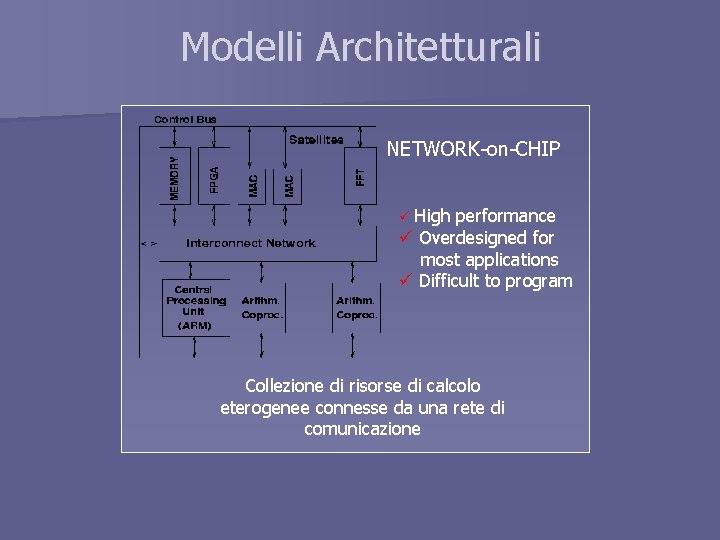

Modelli Architetturali NETWORK-on-CHIP ü High performance ü Overdesigned for most applications ü Difficult to program Collezione di risorse di calcolo eterogenee connesse da una rete di comunicazione

Modelli Architetturali XTENSA ü Good performance ü Easy to program ü Configured at mask-level Processore Risc con unità funzionali applicationspecific function units opzionalmente inserite nella pipeline

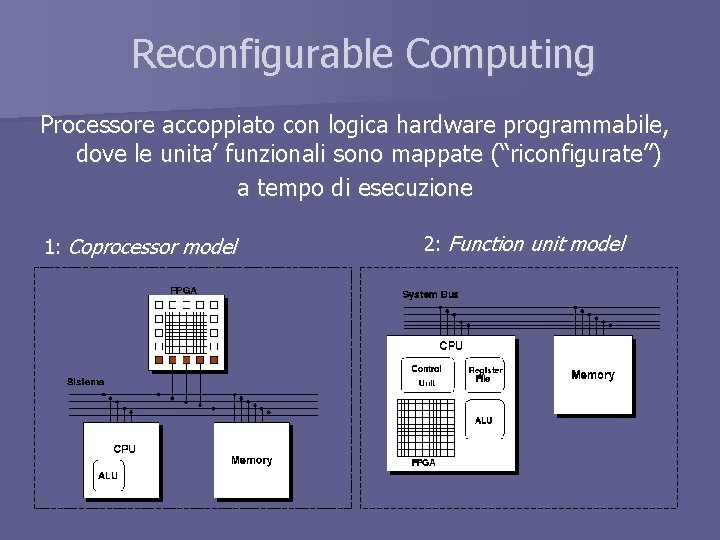

Reconfigurable Computing Processore accoppiato con logica hardware programmabile, dove le unita’ funzionali sono mappate (“riconfigurate”) a tempo di esecuzione 1: Coprocessor model 2: Function unit model

Function unit model: Prisc n Array fit in the risc pipeline ü No communication overhead ü Some degree of parallelism between function units n Gate array performs combinatorial instructions ONLY (very fine grain) ü Low speedup figures (2 x/3 x) Harvard, 1994

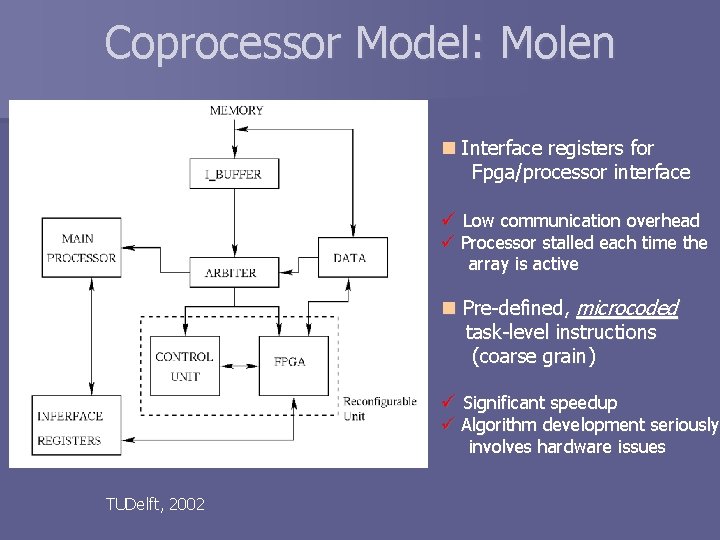

Coprocessor Model: Molen n Interface registers for Fpga/processor interface ü Low communication overhead ü Processor stalled each time the array is active n Pre-defined, microcoded task-level instructions (coarse grain) ü Significant speedup ü Algorithm development seriously involves hardware issues TUDelft, 2002

Architettura

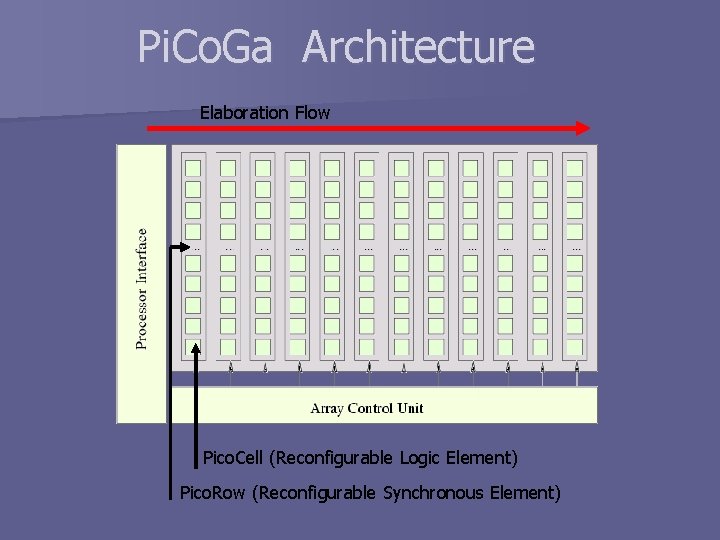

Pi. Co. Ga Architecture Elaboration Flow Pico. Cell (Reconfigurable Logic Element) Pico. Row (Reconfigurable Synchronous Element)

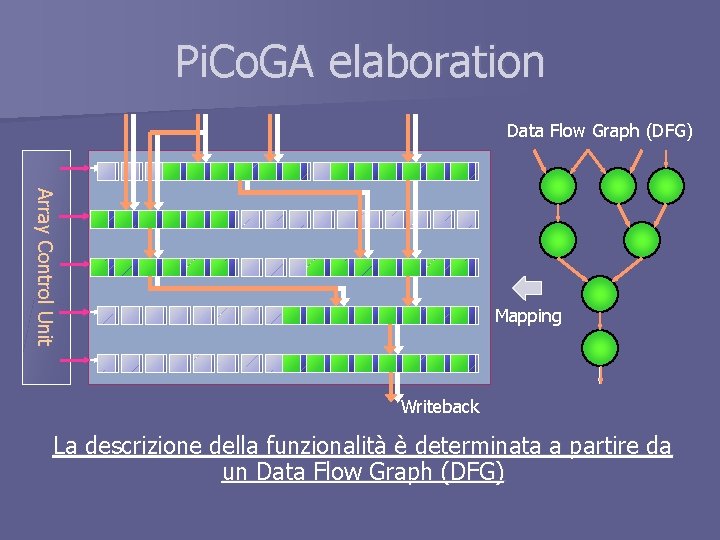

Pi. Co. GA elaboration Data Flow Graph (DFG) A rra y C o n t ro l U n i t Mapping Writeback La descrizione della funzionalità è determinata a partire da un Data Flow Graph (DFG)

Dynamic Instruction set extension

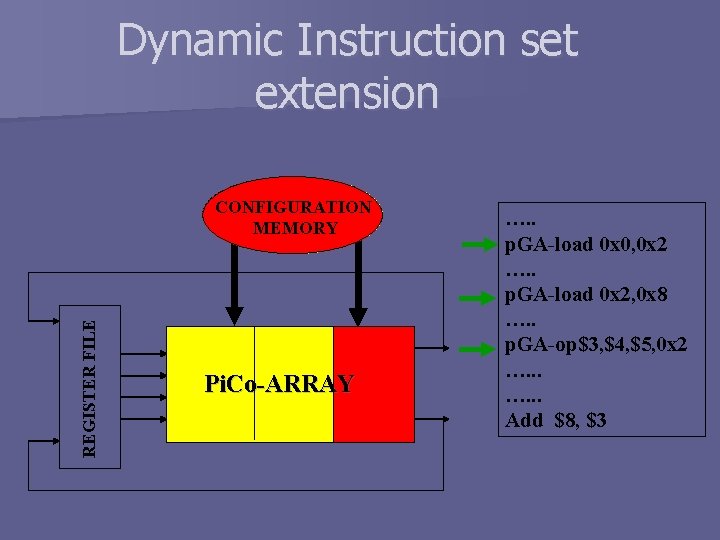

Dynamic Instruction set extension REGISTER FILE CONFIGURATION MEMORY Pi. Co-ARRAY …. . p. GA-load 0 x 0, 0 x 2 …. . p. GA-load 0 x 2, 0 x 8 …. . p. GA-op$3, $4, $5, 0 x 2 …. . . Add $8, $3

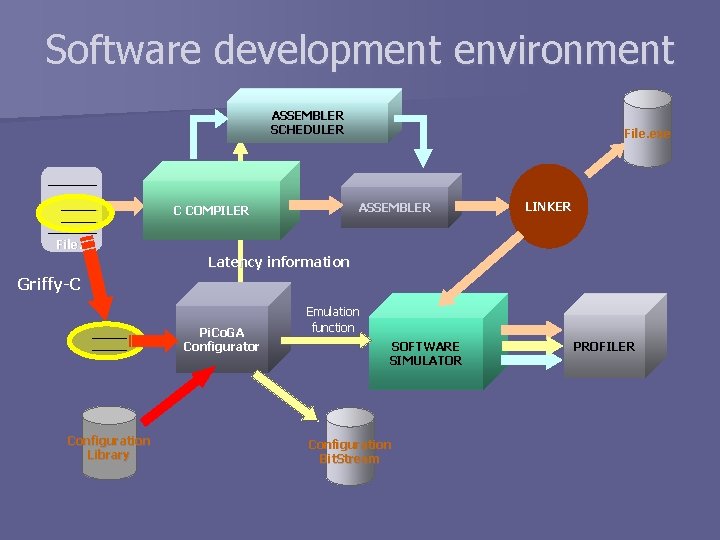

Software development environment ASSEMBLER SCHEDULER File. exe ASSEMBLER C COMPILER LINKER File. c Latency information Griffy-C Pi. Co. GA Configurator Configuration Library Emulation function SOFTWARE SIMULATOR Configuration Bit. Stream PROFILER

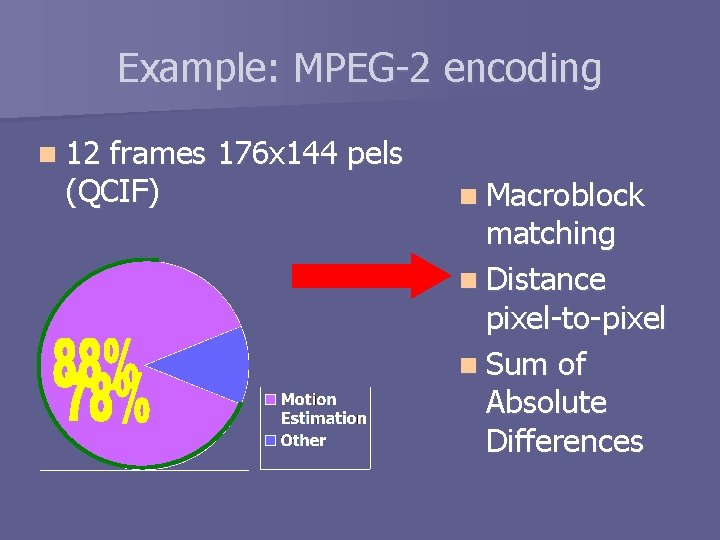

Example: MPEG-2 encoding n 12 frames 176 x 144 pels (QCIF) n Macroblock matching n Distance pixel-to-pixel n Sum of Absolute Differences

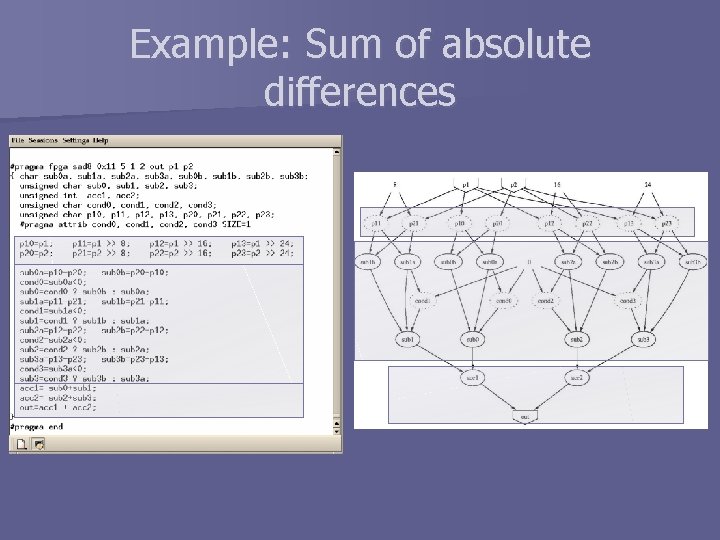

Example: Sum of absolute differences

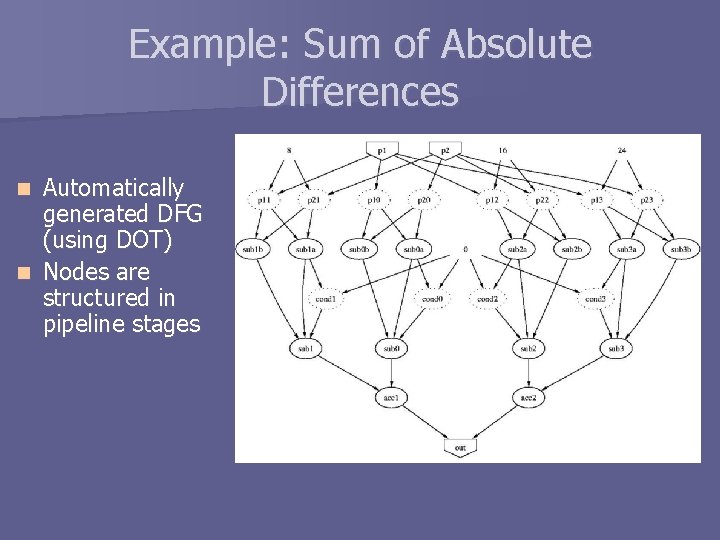

Example: Sum of Absolute Differences Automatically generated DFG (using DOT) n Nodes are structured in pipeline stages n

Example: Sum of Absolute Differences From Register File AD 1 AD 2 AD 3 SAD (AD - Absolute Difference) (SAD – Sum of AD)) Writeback to Register File AD 4

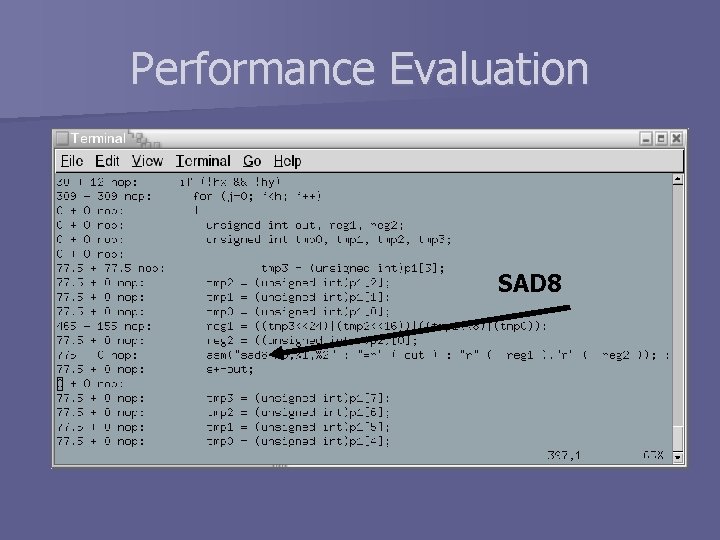

Performance Evaluation SAD 8

- Slides: 26