Application Brief Ga N Switching Loss Simulation using

Application Brief Ga. N Switching Loss Simulation using LTSpice May 22, 2018 Ga. N Systems 1

Overview § Ga. N Systems provides Pspice/LTSpice simulation models for Ga. N Enhancement mode HEMT. § In this presentation, a half bridge double pulse test circuit in LTSpice will be introduced and used as the test bench to evaluate switching performance under different electrical parameters. § Switching losses were simulated and compared with Lab measurement Ga. N Systems 2

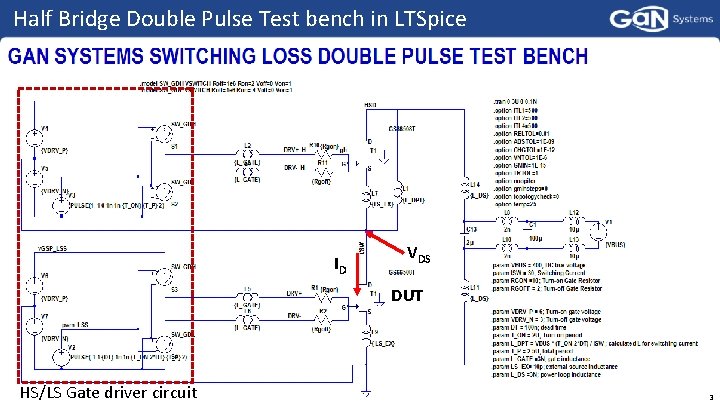

Half Bridge Double Pulse Test bench in LTSpice ID VDS DUT HS/LS Gate driver circuit Ga. N Systems 3

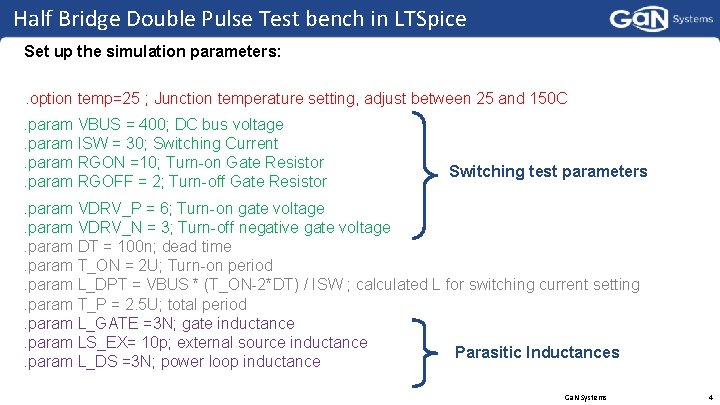

Half Bridge Double Pulse Test bench in LTSpice Set up the simulation parameters: . option temp=25 ; Junction temperature setting, adjust between 25 and 150 C. param VBUS = 400; DC bus voltage. param ISW = 30; Switching Current. param RGON =10; Turn-on Gate Resistor. param RGOFF = 2; Turn-off Gate Resistor Switching test parameters . param VDRV_P = 6; Turn-on gate voltage. param VDRV_N = 3; Turn-off negative gate voltage. param DT = 100 n; dead time. param T_ON = 2 U; Turn-on period. param L_DPT = VBUS * (T_ON-2*DT) / ISW ; calculated L for switching current setting. param T_P = 2. 5 U; total period. param L_GATE =3 N; gate inductance. param LS_EX= 10 p; external source inductance Parasitic Inductances. param L_DS =3 N; power loop inductance Ga. N Systems 4

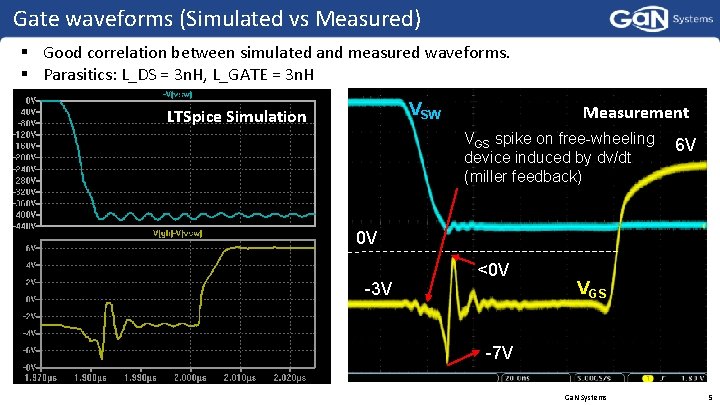

Gate waveforms (Simulated vs Measured) § Good correlation between simulated and measured waveforms. § Parasitics: L_DS = 3 n. H, L_GATE = 3 n. H VSW LTSpice Simulation Measurement VGS spike on free-wheeling device induced by dv/dt (miller feedback) 6 V 0 V -3 V <0 V VGS -7 V Ga. N Systems 5

Half Bridge Double Pulse Test bench in LTSpice Double Pulse Simulation Results (400 V/30 A) 400 V/30 A Hard switch-off VDS 30 A Turn-off ID 30 A Turn-on 400 V/30 A Hard switch-on Ga. N Systems 6

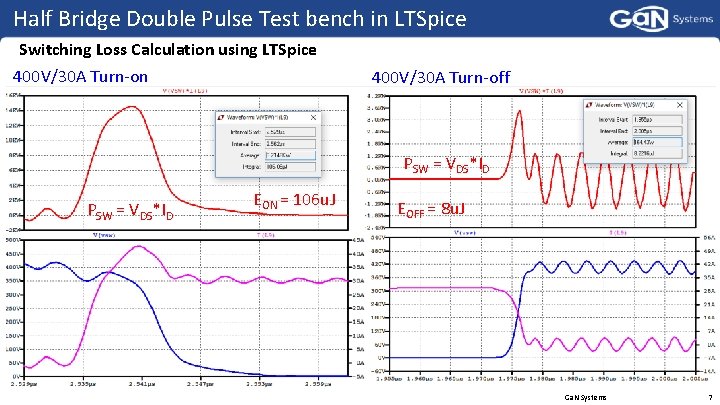

Half Bridge Double Pulse Test bench in LTSpice Switching Loss Calculation using LTSpice 400 V/30 A Turn-on 400 V/30 A Turn-off PSW = VDS*ID EON = 106 u. J EOFF = 8 u. J Ga. N Systems 7

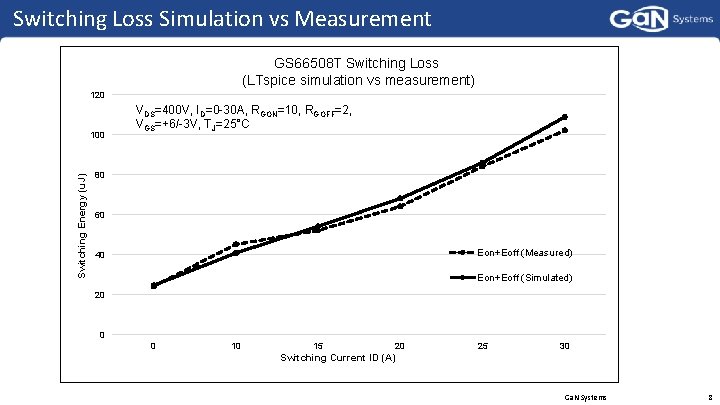

Switching Loss Simulation vs Measurement GS 66508 T Switching Loss (LTspice simulation vs measurement) 120 Switching Energy (u. J) 100 VDS=400 V, ID=0 -30 A, RGON=10, RGOFF=2, VGS=+6/-3 V, TJ=25°C 80 60 Eon+Eoff (Measured) 40 Eon+Eoff (Simulated) 20 0 0 10 15 20 25 30 Switching Current ID (A) Ga. N Systems 8

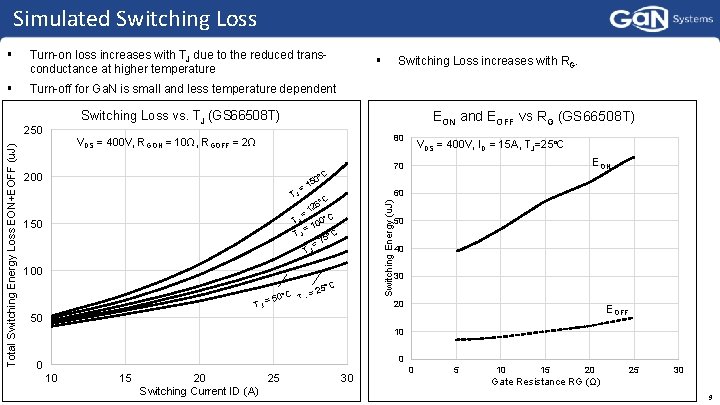

Simulated Switching Loss § Turn-on loss increases with TJ due to the reduced transconductance at higher temperature § Turn-off for Ga. N is small and less temperature dependent Switching Loss increases with RG. Switching Loss vs. TJ (GS 66508 T) 250 EON and EOFF vs RG (GS 66508 T) 80 VDS = 400 V, RGON = 10Ω, RGOFF = 2Ω 200 VDS = 400 V, ID = 15 A, TJ=25°C EON 70 C 0° 5 TJ =1 60 °C 25 1 = T J 100°C = C TJ 5° =7 TJ 150 Switching Energy (u. J) Total Switching Energy Loss EON+EOFF (u. J) § 100 TJ = 50°C T J 5°C =2 50 40 30 20 EOFF 50 10 0 0 10 15 20 25 Switching Current ID (A) 30 0 5 10 15 20 25 30 Gate Resistance RG (Ω) Ga. N Systems 9

Summary § Ga. N E-HEMT switching losses were simulated by using a half bridge double pulse test circuit in LTSpice § The simulation results were verified by the lab measurement. Although the real world measurement can be affected by many other factors, we have achieved reasonably good agreement between the simulation model and measurement. § This LTSpice test circuit can be a convenient tool for end users to get started with simulation and be familiar with Ga. N switching characteristics to assist their design. § This simulation test bench can also be used to easily evaluate Ga. N switching performance under different electrical parameters Click to download LTSpice simulation file Ga. N Systems 10

Tomorrow’s power today TM www. gansystems. com • North America • Europe • Asia Ga. N Systems 11

- Slides: 11