Another use of the JTAG Interface on FPGA

- Slides: 14

Another use of the JTAG Interface on FPGA Presented by Karin Shusterman JTAG Interface as a Communication Port

Introduction • JTAG is usually used for testing the board • The JTAG interface can be also used to configure FPGAs and program flash devices • Can we do more? • How about design testing? JTAG Interface as a Communication Port

Design testing using JTAG • The BS technology on FPGA is providing us test and debug capability to our design • We use custom Instructions JTAG controller and to debug the logic of the design • The JTAG controller is already built into the FPGA, minimizing user design JTAG Interface as a Communication Port

Existing solutions • Adding debug outputs and asserts into our design • Using switches and LEDs on board • Using FPGA as a black box • The problem – We can’t know where exactly the problem is – We need many test vectors for many different states • We wish we could have a spy inside our design JTAG Interface as a Communication Port

GNAT • General-purpose Native JTAG Tester • Configured into the FPGA in addition to our design • Uses JTAG controller and resources for debug issues • Allows us to enable communication with our design JTAG Interface as a Communication Port

The uses for GNAT • Replacement for external components (such as LEDs and switches) • Enabling test/diagnostic modes • Reading status/debug registers from design • Controlling a multiplexer to select signals that route to external pins for monitoring • Programming/uploading external memories that interface to the FPGA, such as SDRAM JTAG Interface as a Communication Port

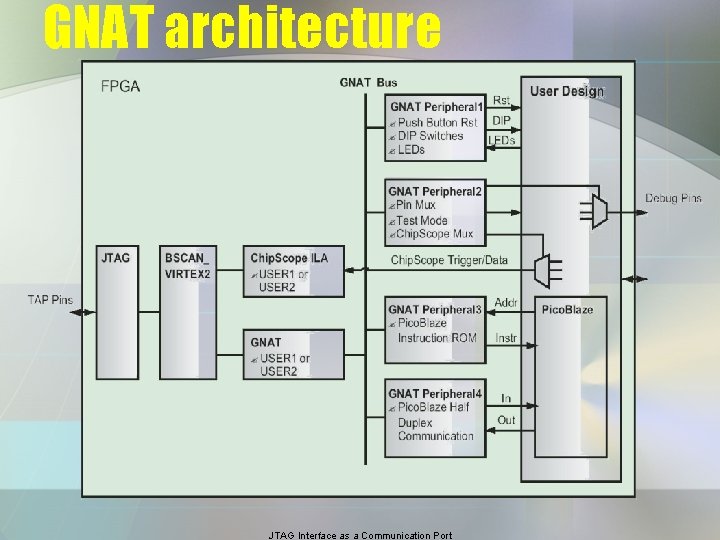

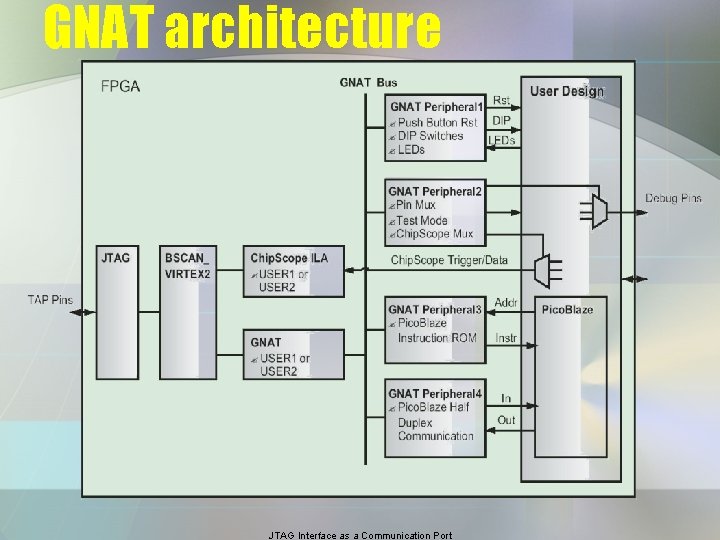

GNAT architecture JTAG Interface as a Communication Port

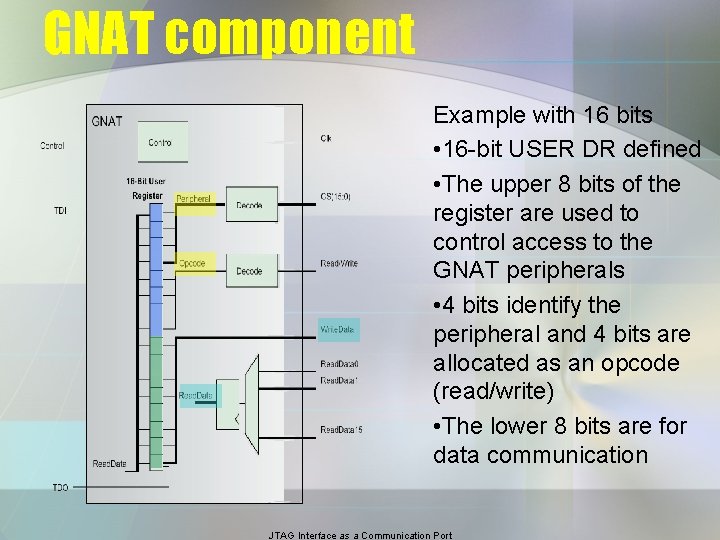

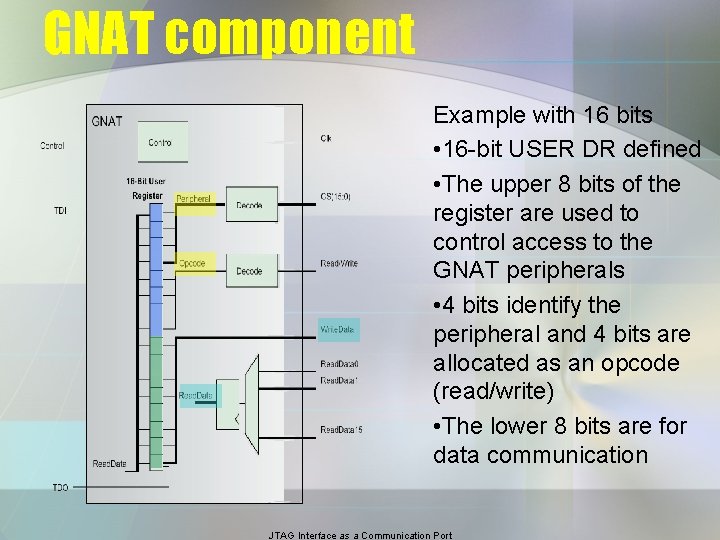

GNAT component Example with 16 bits • 16 -bit USER DR defined • The upper 8 bits of the register are used to control access to the GNAT peripherals • 4 bits identify the peripheral and 4 bits are allocated as an opcode (read/write) • The lower 8 bits are for data communication JTAG Interface as a Communication Port

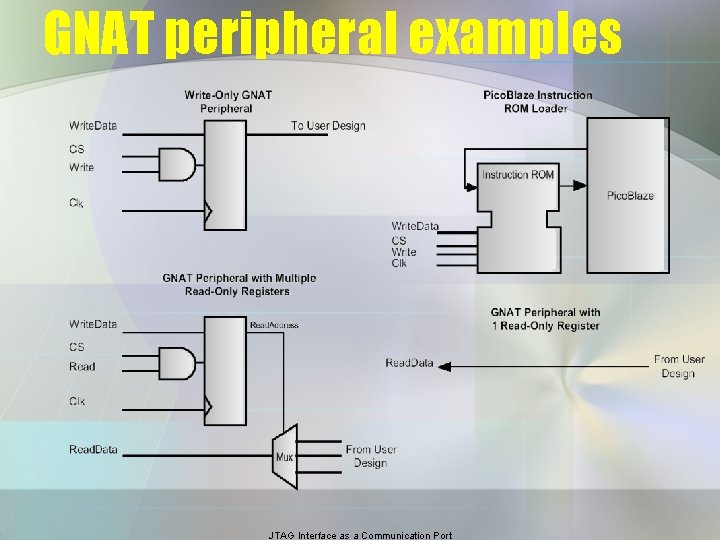

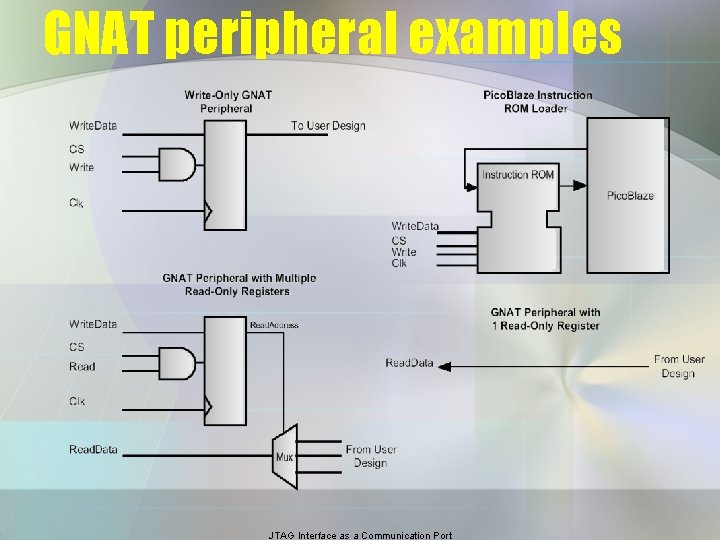

GNAT peripheral examples JTAG Interface as a Communication Port

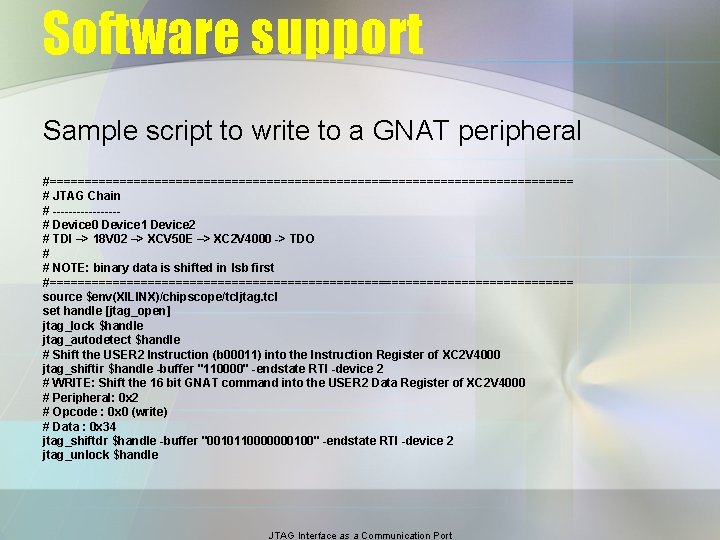

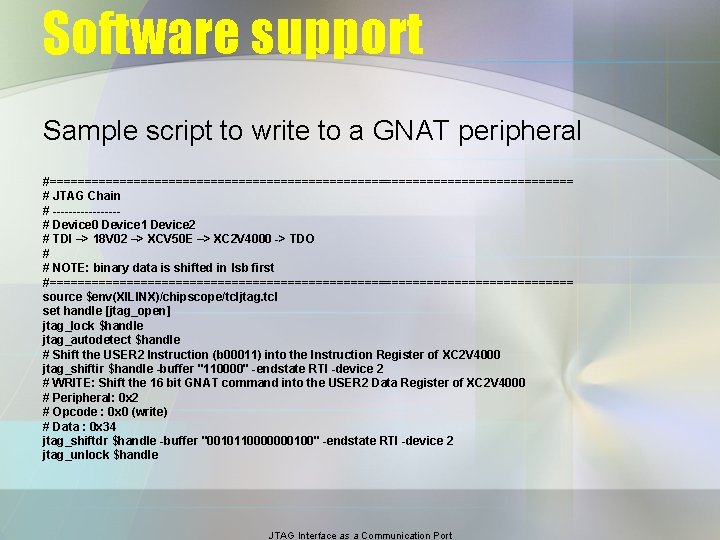

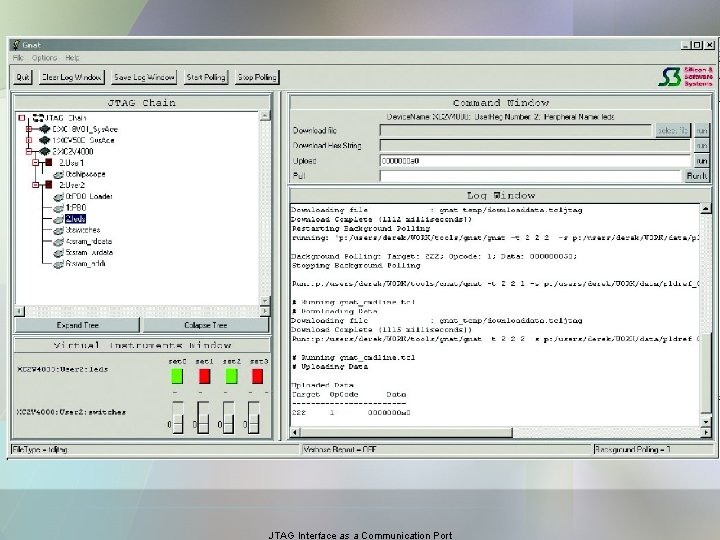

Software support Sample script to write to a GNAT peripheral #====================================== # JTAG Chain # --------# Device 0 Device 1 Device 2 # TDI –> 18 V 02 –> XCV 50 E –> XC 2 V 4000 -> TDO # # NOTE: binary data is shifted in lsb first #====================================== source $env(XILINX)/chipscope/tcljtag. tcl set handle [jtag_open] jtag_lock $handle jtag_autodetect $handle # Shift the USER 2 Instruction (b 00011) into the Instruction Register of XC 2 V 4000 jtag_shiftir $handle -buffer "110000" -endstate RTI -device 2 # WRITE: Shift the 16 bit GNAT command into the USER 2 Data Register of XC 2 V 4000 # Peripheral: 0 x 2 # Opcode : 0 x 0 (write) # Data : 0 x 34 jtag_shiftdr $handle -buffer "0010110000000100" -endstate RTI -device 2 jtag_unlock $handle JTAG Interface as a Communication Port

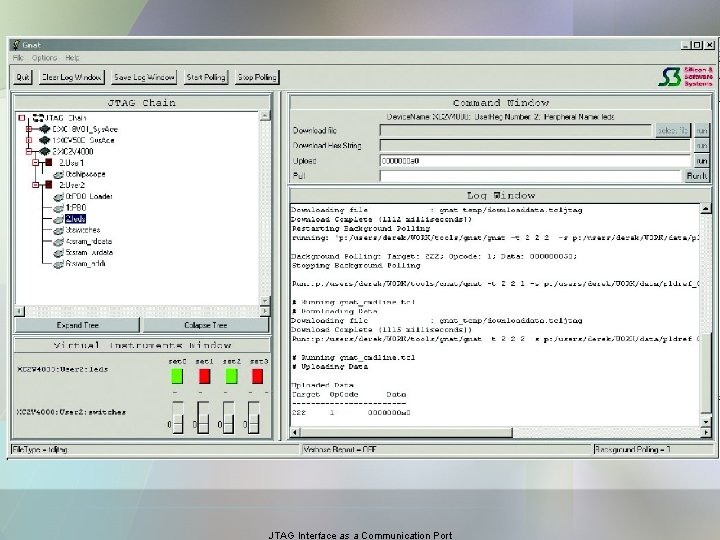

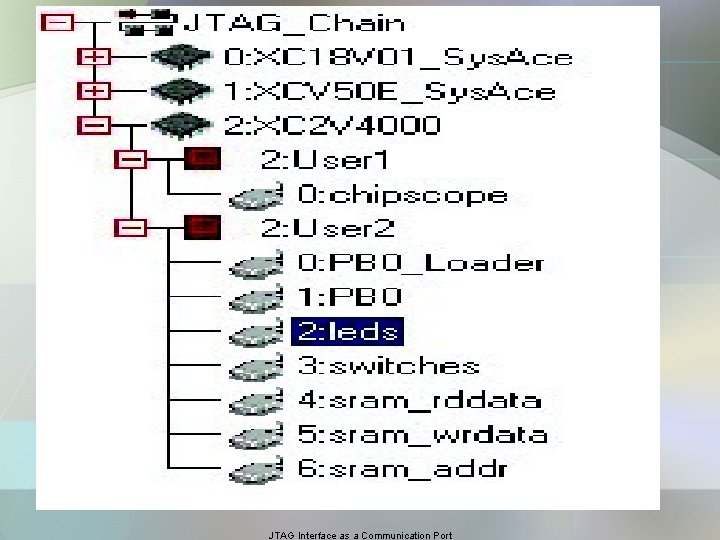

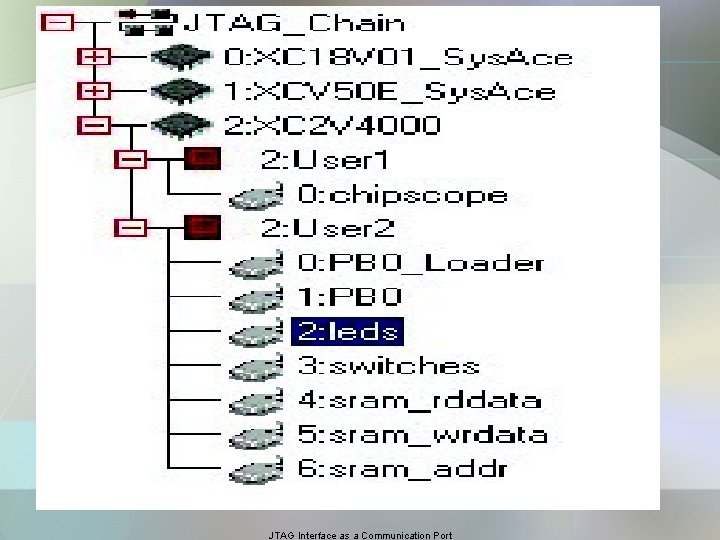

JTAG Interface as a Communication Port

JTAG Interface as a Communication Port

Conclusions • We found a way to look into the design using JTAG technology • We are using existing JTAG resources • GNAT – Shows how you can quickly and easily add JTAG debug capability to your design – Has minimal FPGA resource overhead – A simple lightweight and flexible architecture JTAG Interface as a Communication Port

Questions ? JTAG Interface as a Communication Port