Analog to Digital Converters NyquistRate ADCs q Flash

- Slides: 42

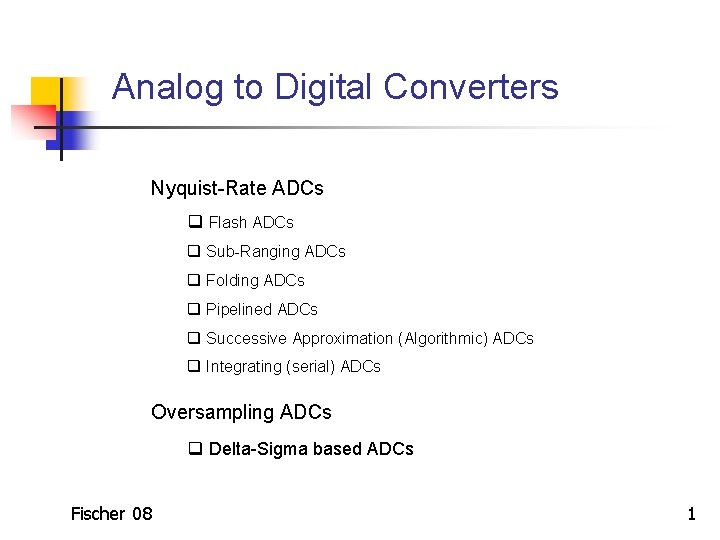

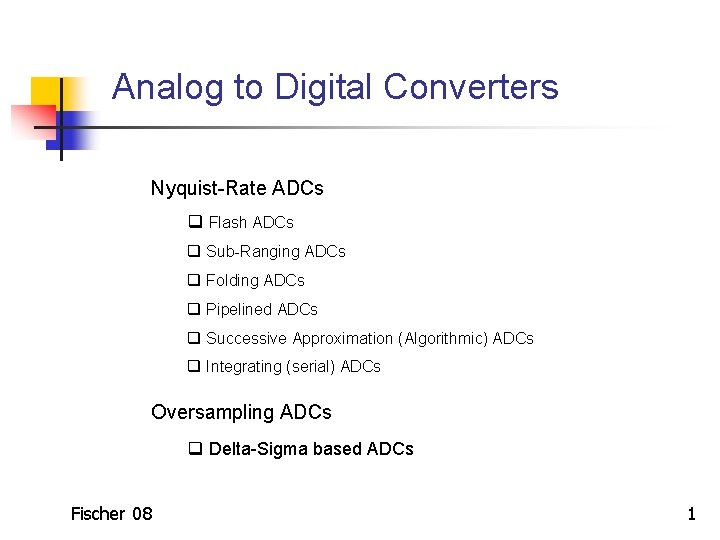

Analog to Digital Converters Nyquist-Rate ADCs q Flash ADCs q Sub-Ranging ADCs q Folding ADCs q Pipelined ADCs q Successive Approximation (Algorithmic) ADCs q Integrating (serial) ADCs Oversampling ADCs q Delta-Sigma based ADCs Fischer 08 1

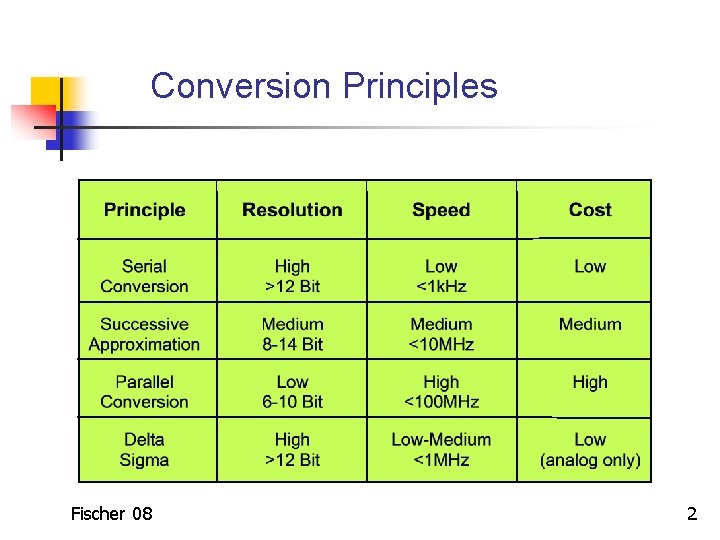

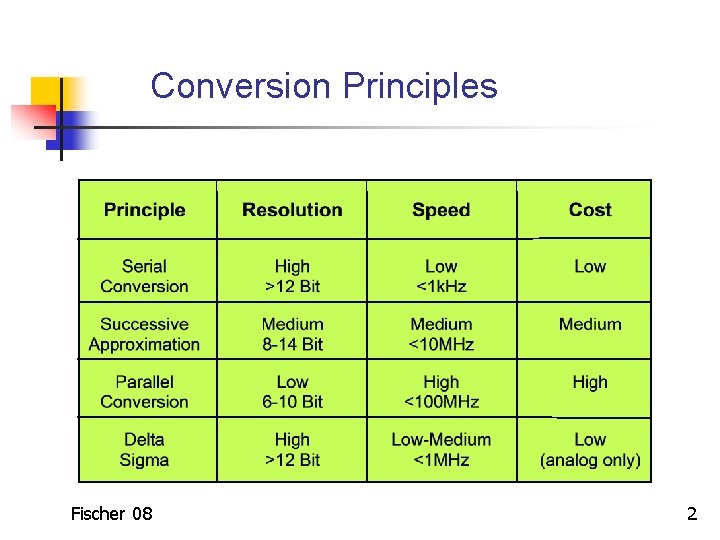

Conversion Principles Fischer 08 2

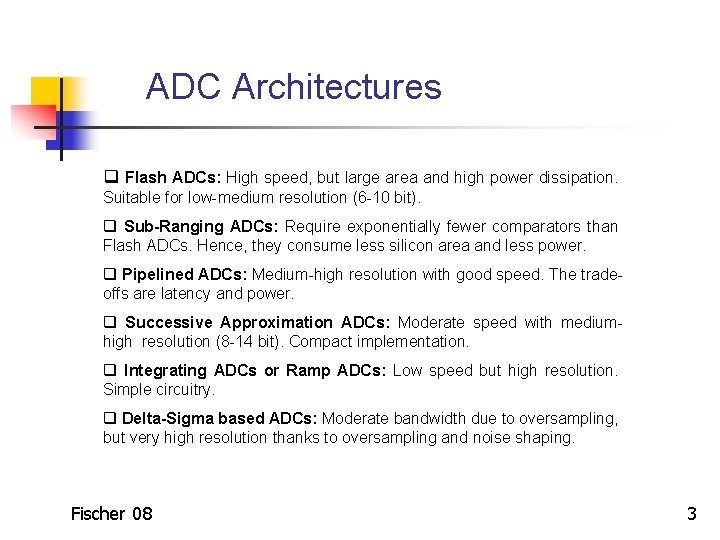

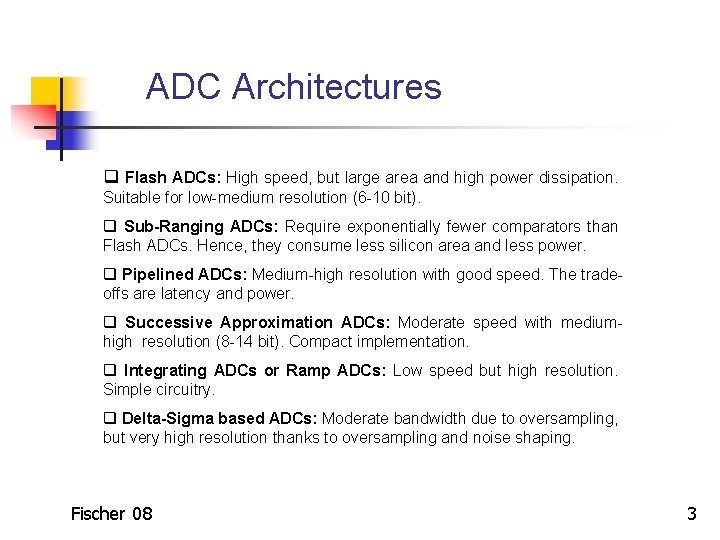

ADC Architectures q Flash ADCs: High speed, but large area and high power dissipation. Suitable for low-medium resolution (6 -10 bit). q Sub-Ranging ADCs: Require exponentially fewer comparators than Flash ADCs. Hence, they consume less silicon area and less power. q Pipelined ADCs: Medium-high resolution with good speed. The tradeoffs are latency and power. q Successive Approximation ADCs: Moderate speed with mediumhigh resolution (8 -14 bit). Compact implementation. q Integrating ADCs or Ramp ADCs: Low speed but high resolution. Simple circuitry. q Delta-Sigma based ADCs: Moderate bandwidth due to oversampling, but very high resolution thanks to oversampling and noise shaping. Fischer 08 3

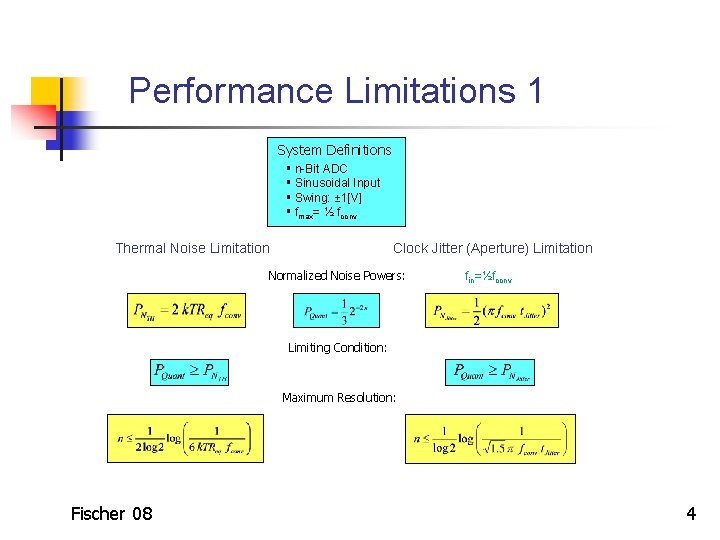

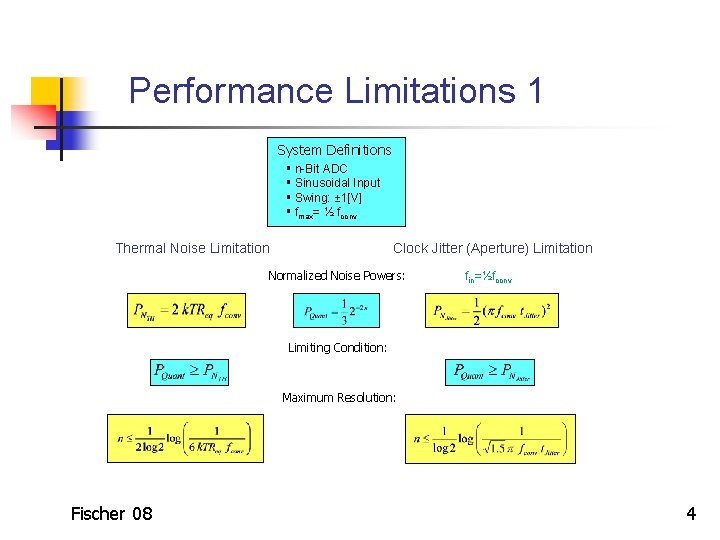

Performance Limitations 1 System Definitions § n-Bit ADC § Sinusoidal Input § Swing: ± 1[V] § fmax= ½ fconv Thermal Noise Limitation Clock Jitter (Aperture) Limitation Normalized Noise Powers: fin=½fconv Limiting Condition: Maximum Resolution: Fischer 08 4

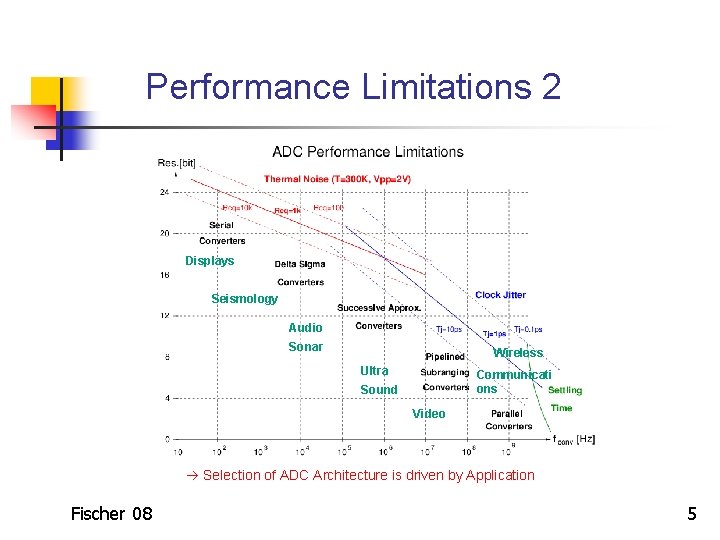

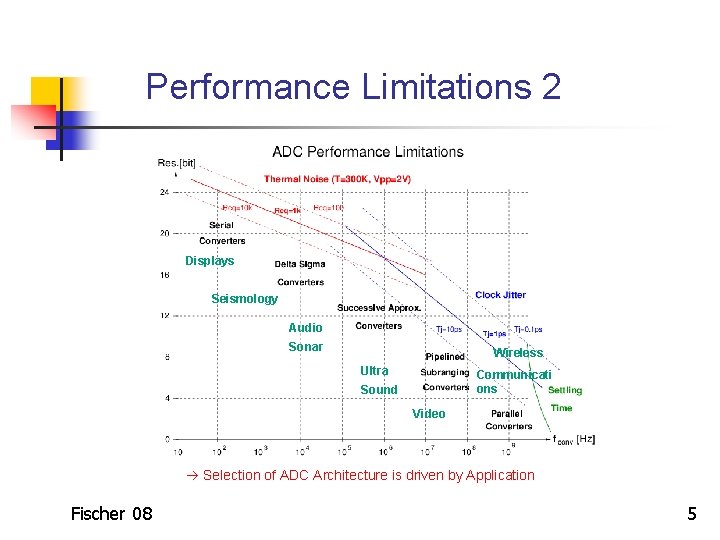

Performance Limitations 2 Displays Seismology Audio Sonar Wireless Ultra Communicati ons Sound Video Selection of ADC Architecture is driven by Application Fischer 08 5

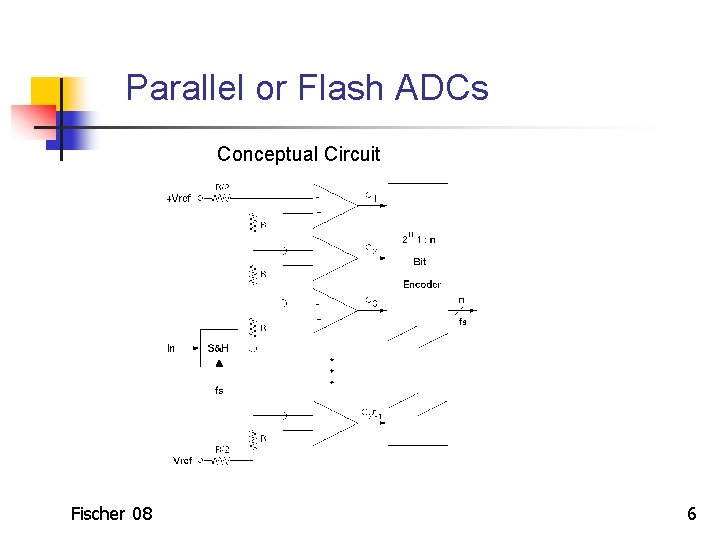

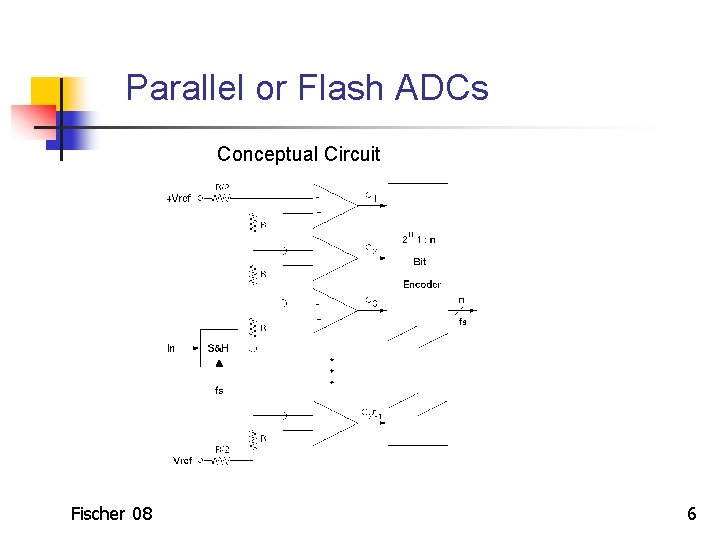

Parallel or Flash ADCs Conceptual Circuit Fischer 08 6

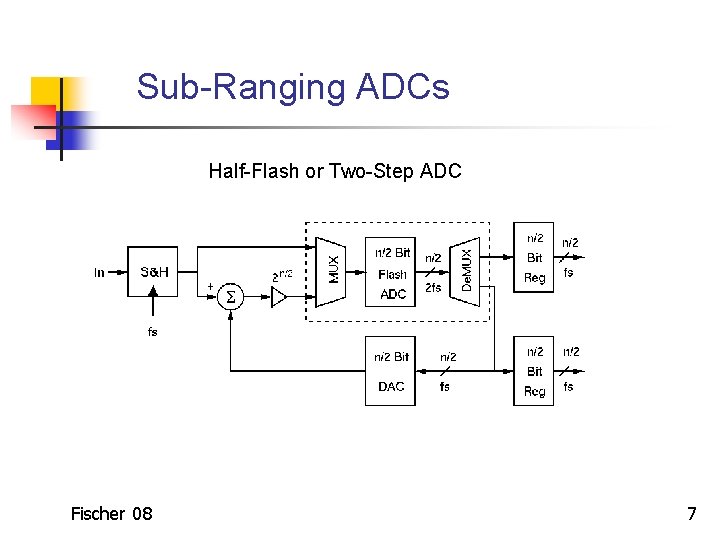

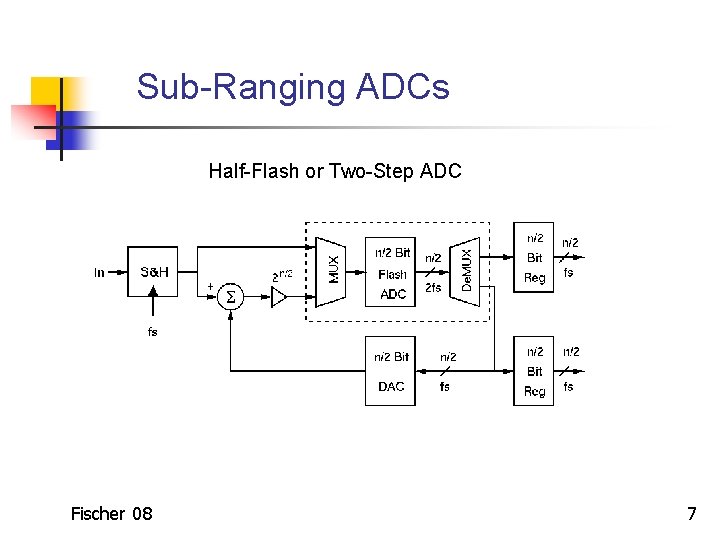

Sub-Ranging ADCs Half-Flash or Two-Step ADC Fischer 08 7

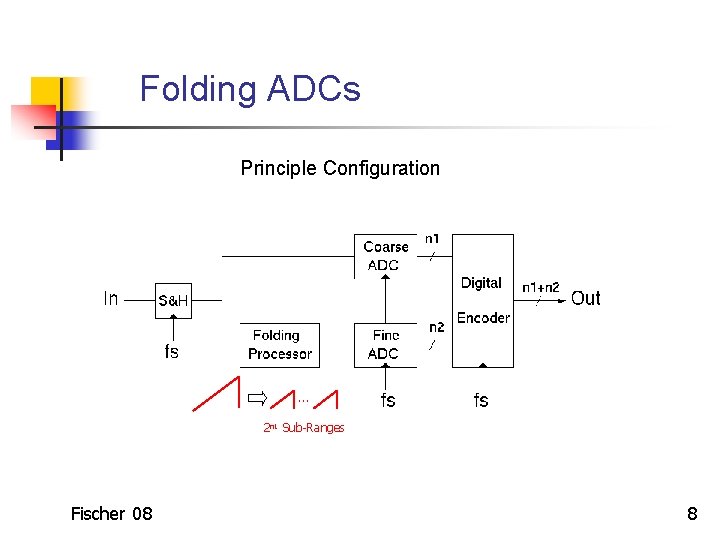

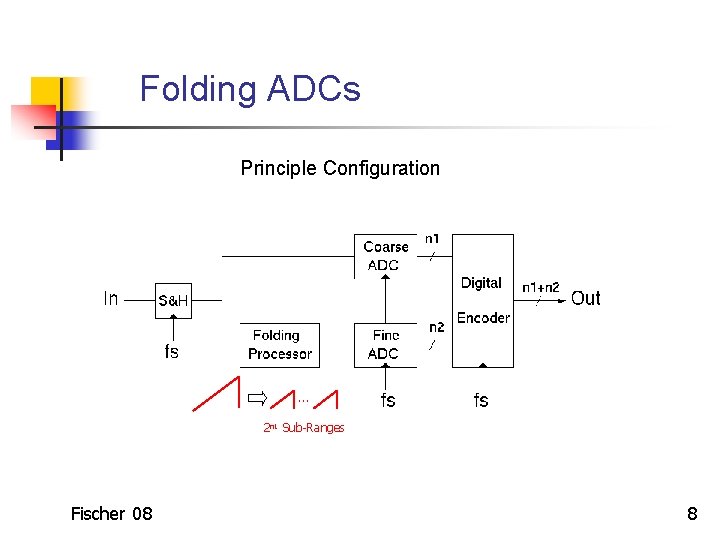

Folding ADCs Principle Configuration … 2 n 1 Sub-Ranges Fischer 08 8

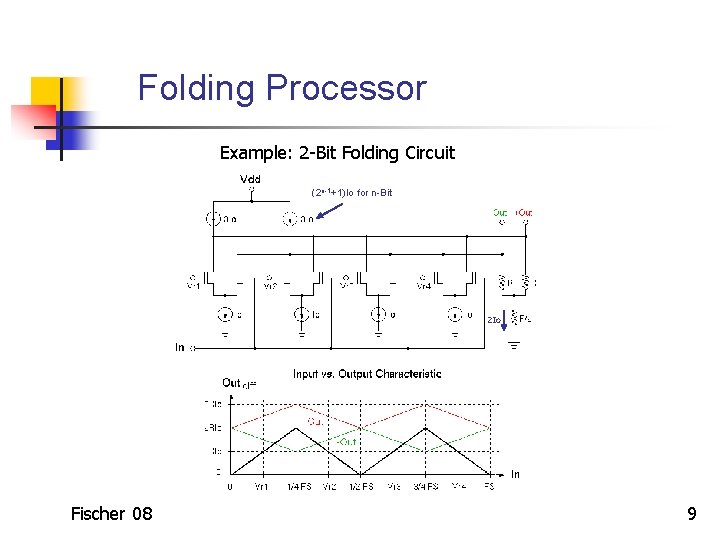

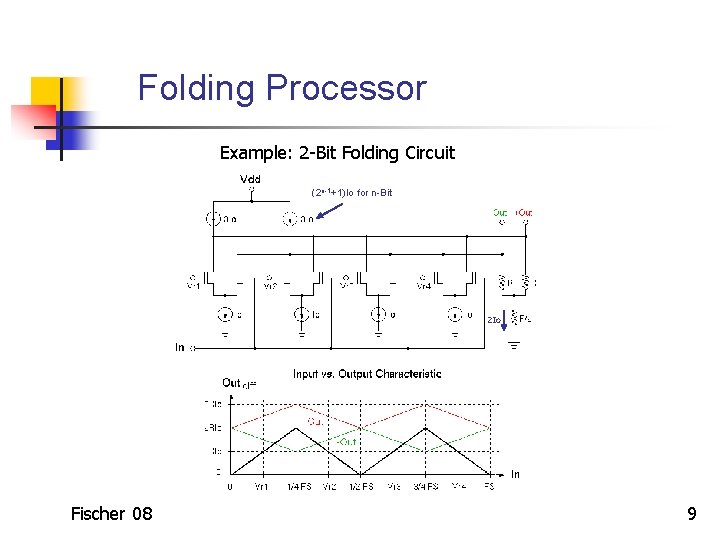

Folding Processor Example: 2 -Bit Folding Circuit (2 n-1+1)Io for n-Bit 2 Io Fischer 08 9

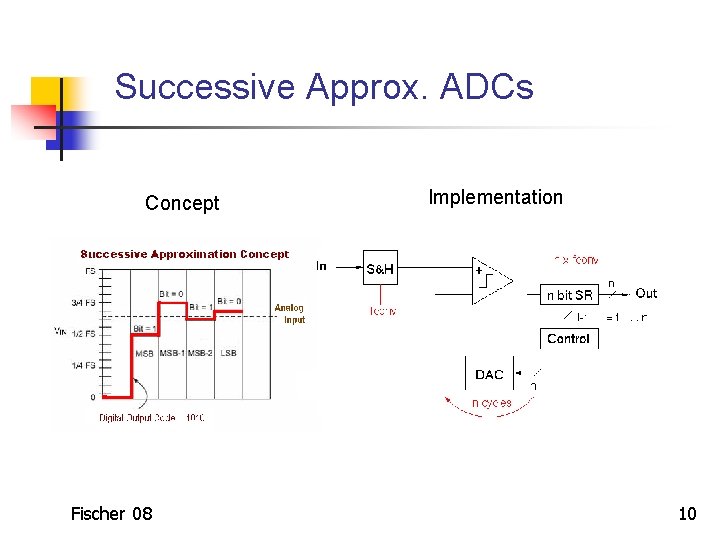

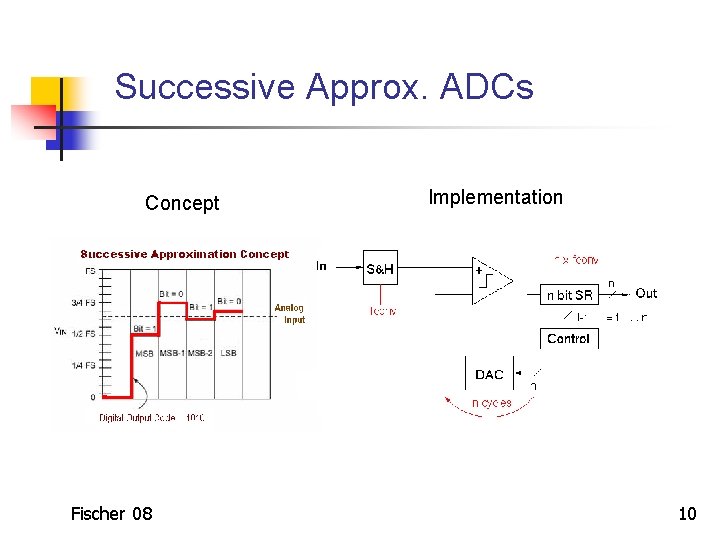

Successive Approx. ADCs Concept Fischer 08 Implementation 10

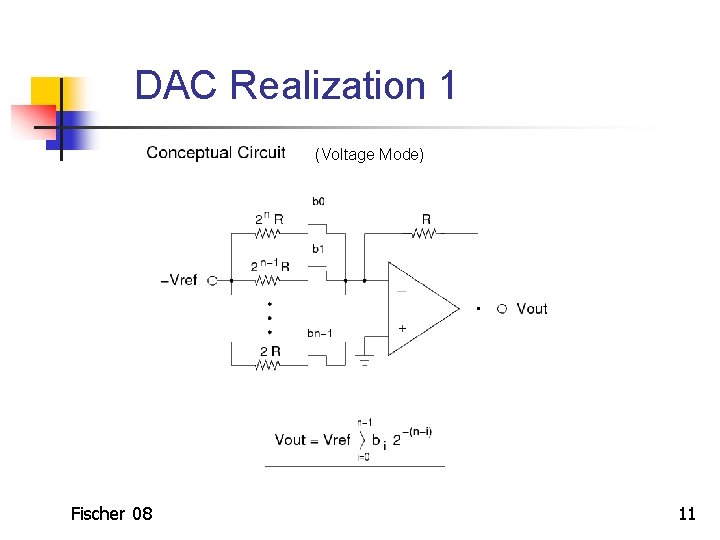

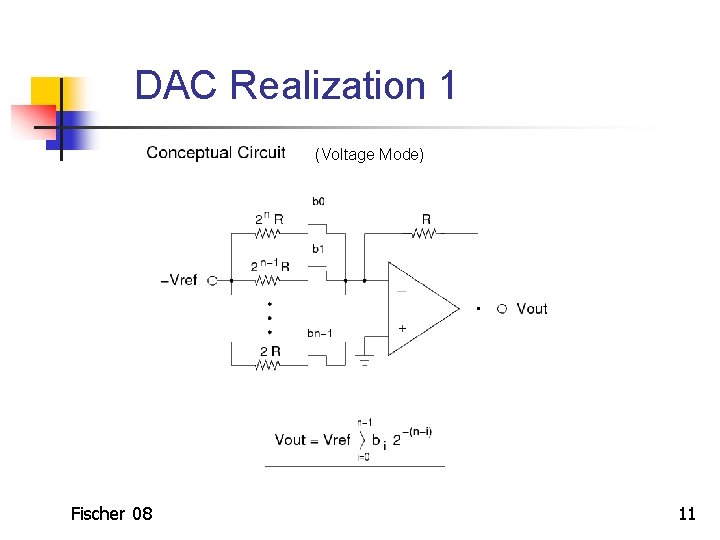

DAC Realization 1 (Voltage Mode) Fischer 08 11

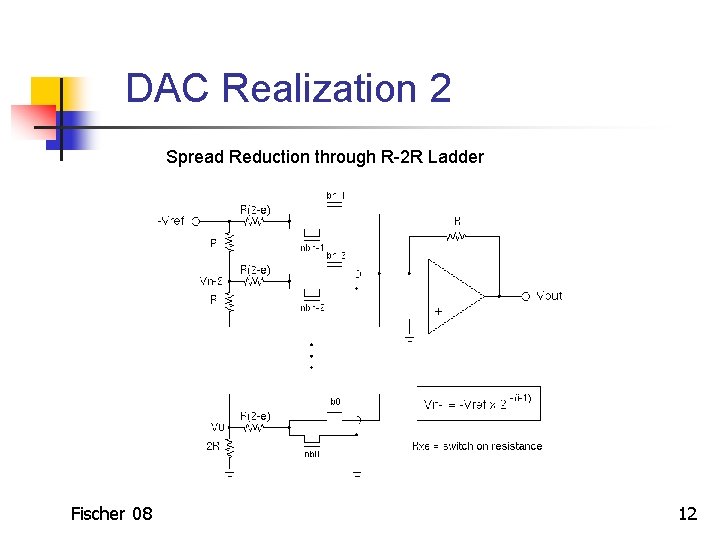

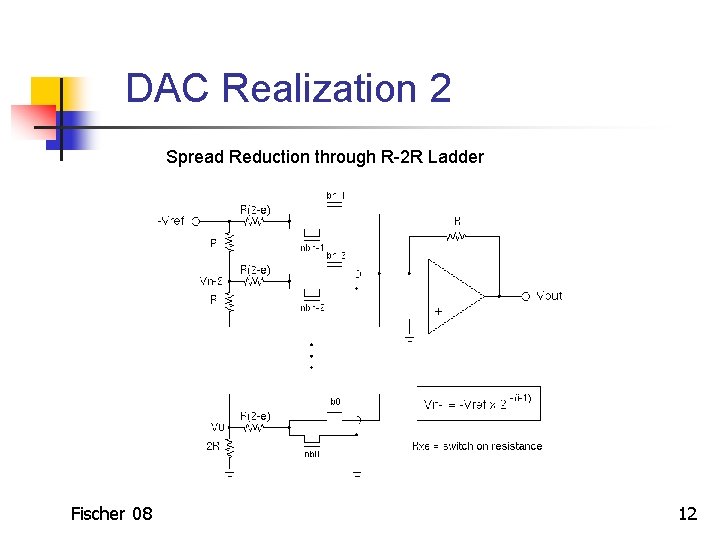

DAC Realization 2 Spread Reduction through R-2 R Ladder Fischer 08 12

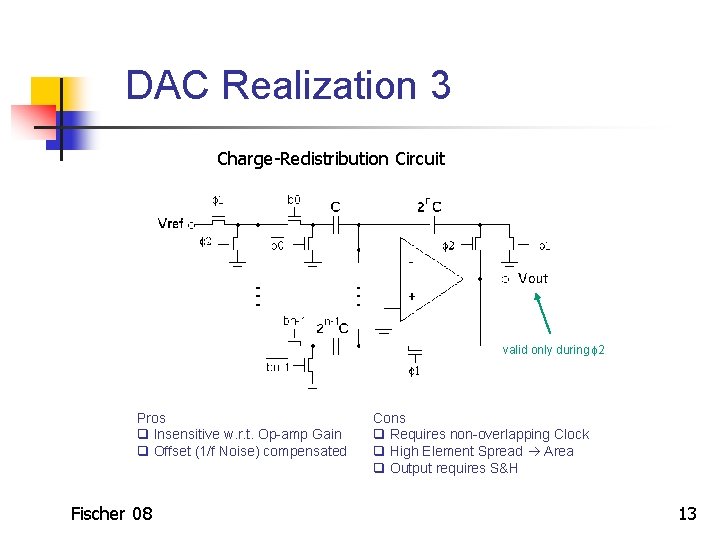

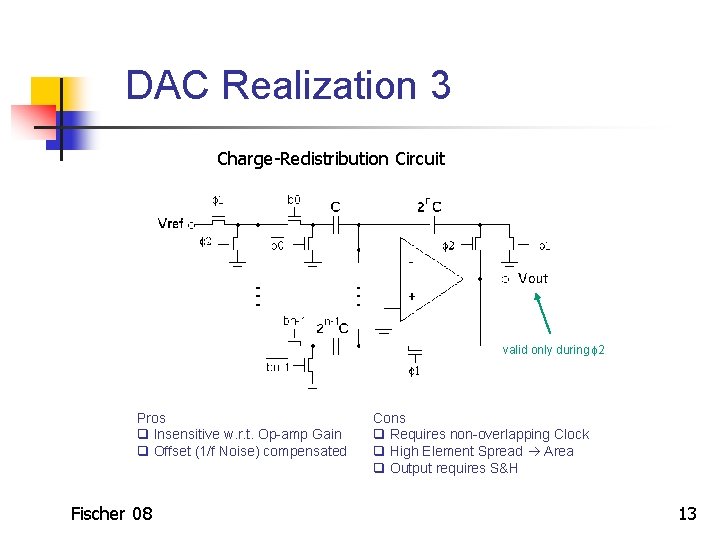

DAC Realization 3 Charge-Redistribution Circuit valid only during f 2 Pros q Insensitive w. r. t. Op-amp Gain q Offset (1/f Noise) compensated Fischer 08 Cons q Requires non-overlapping Clock q High Element Spread Area q Output requires S&H 13

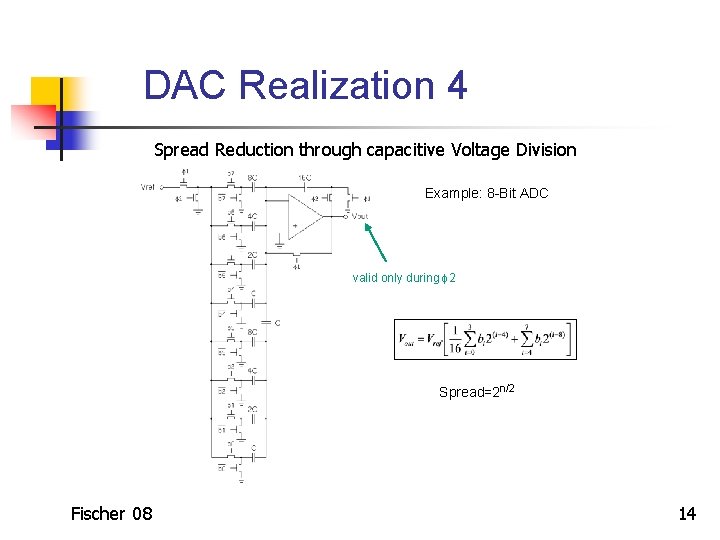

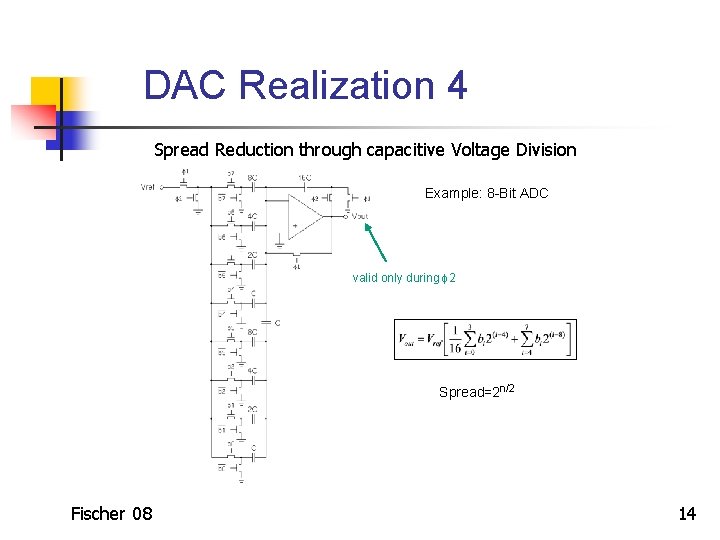

DAC Realization 4 Spread Reduction through capacitive Voltage Division Example: 8 -Bit ADC valid only during f 2 Spread=2 n/2 Fischer 08 14

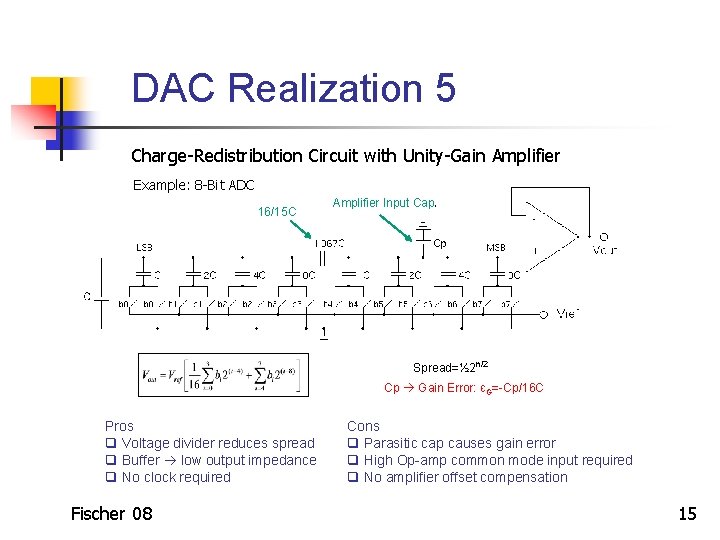

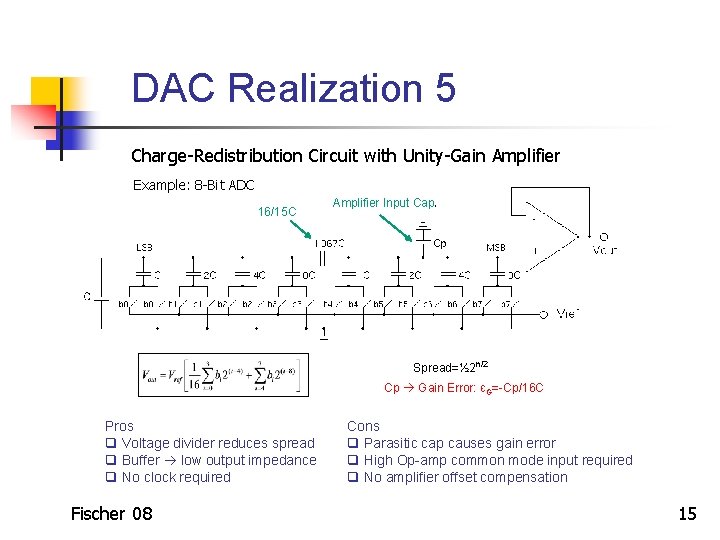

DAC Realization 5 Charge-Redistribution Circuit with Unity-Gain Amplifier Example: 8 -Bit ADC 16/15 C Amplifier Input Cap. Spread=½ 2 n/2 Cp Gain Error: єG=-Cp/16 C Pros q Voltage divider reduces spread q Buffer low output impedance q No clock required Fischer 08 Cons q Parasitic cap causes gain error q High Op-amp common mode input required q No amplifier offset compensation 15

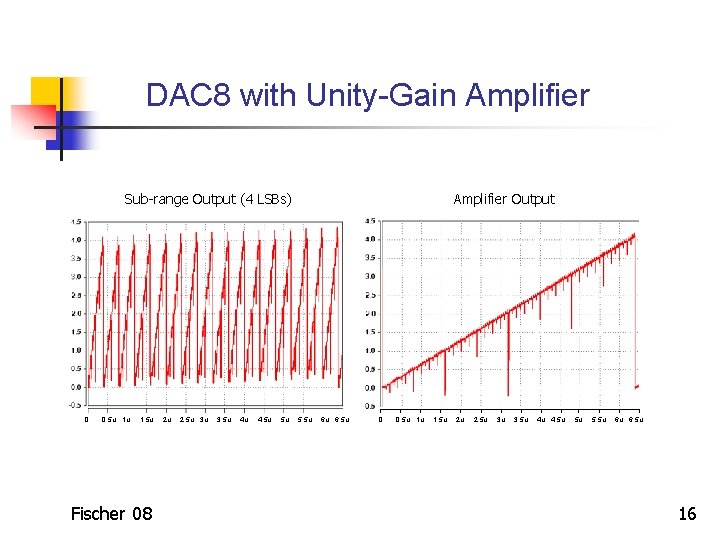

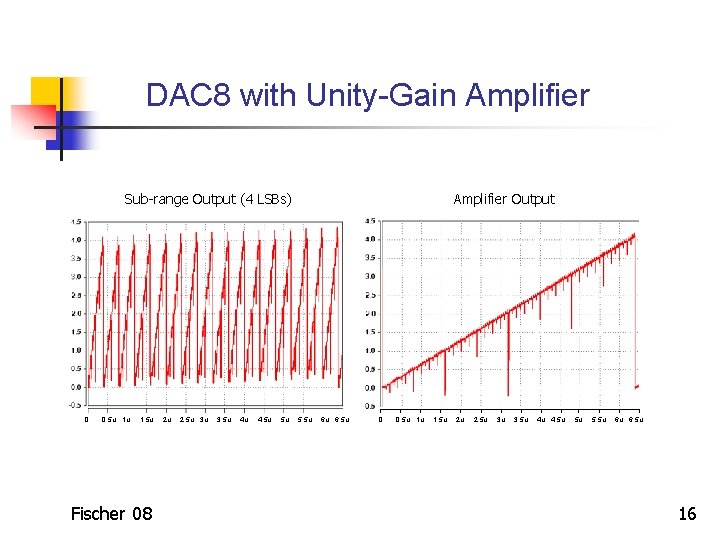

DAC 8 with Unity-Gain Amplifier Sub-range Output (4 LSBs) 0 0. 5 u 1 u 1. 5 u Fischer 08 2 u 2. 5 u 3 u 3. 5 u 4 u 4. 5 u 5 u Amplifier Output 5. 5 u 6 u 6. 5 u 0 0. 5 u 1 u 1. 5 u 2 u 2. 5 u 3 u 3. 5 u 4 u 4. 5 u 5 u 5. 5 u 6 u 6. 5 u 16

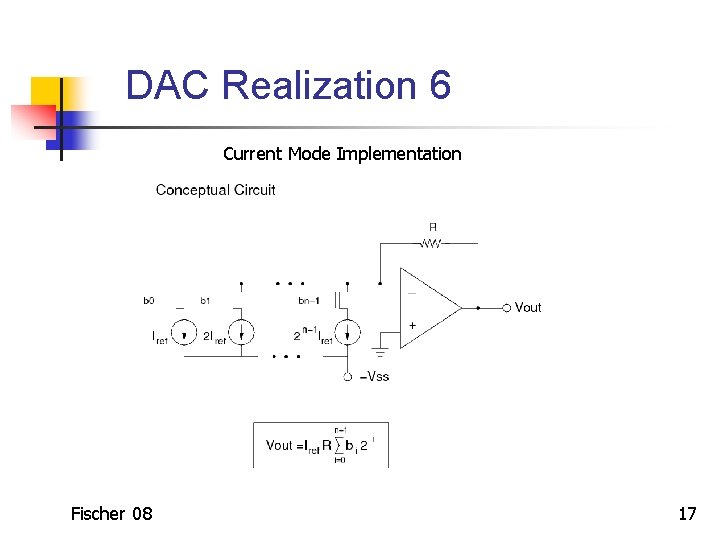

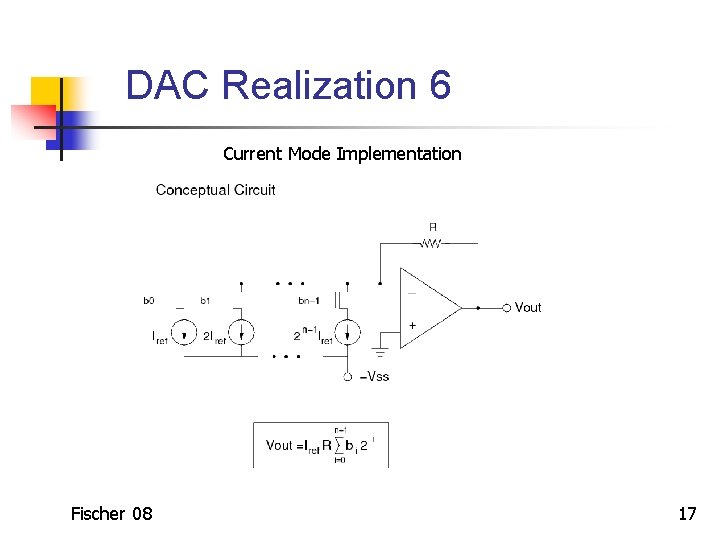

DAC Realization 6 Current Mode Implementation Fischer 08 17

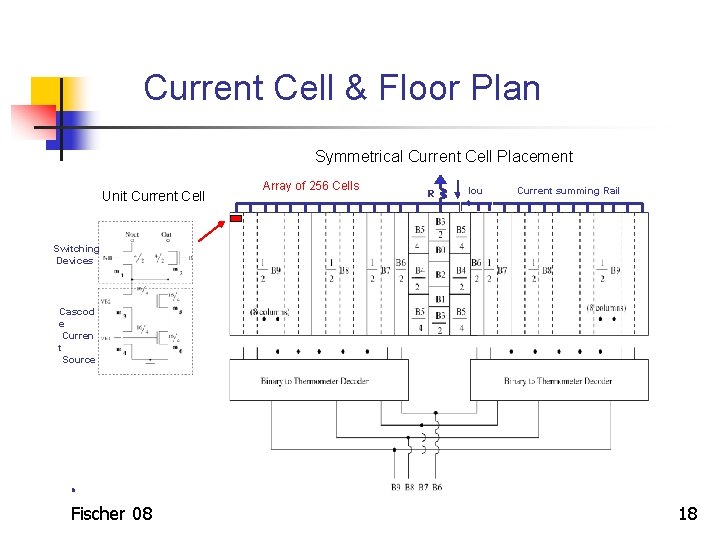

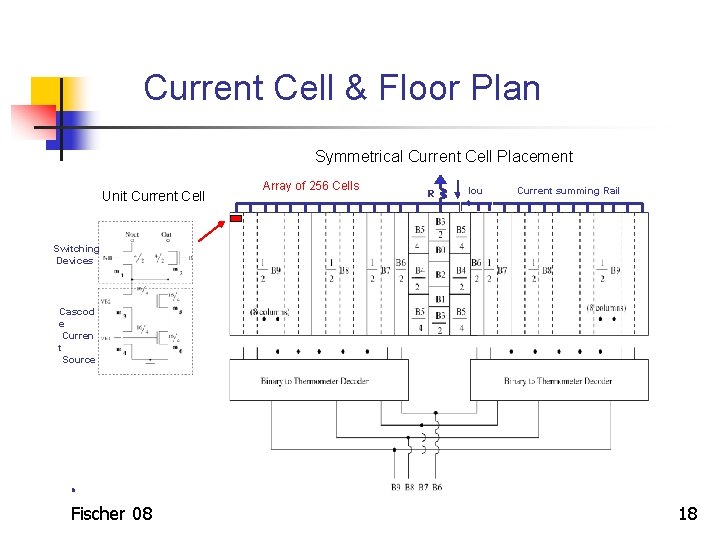

Current Cell & Floor Plan Symmetrical Current Cell Placement Unit Current Cell Array of 256 Cells R Iou t Current summing Rail Switching Devices Cascod e Curren t Source Fischer 08 18

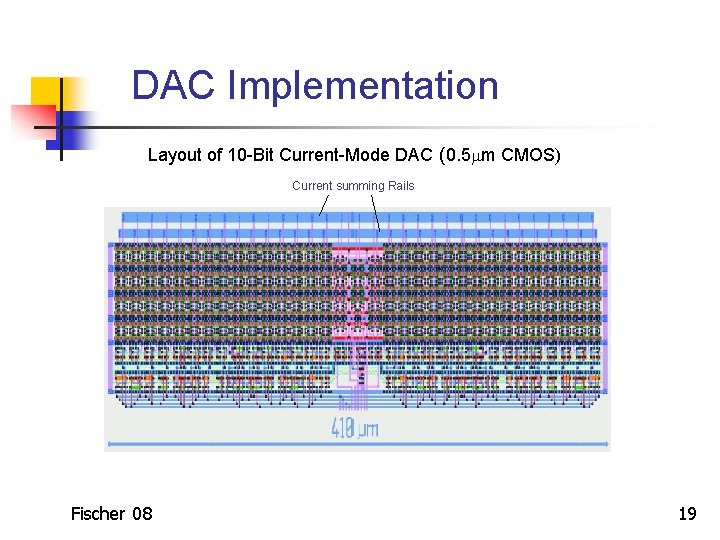

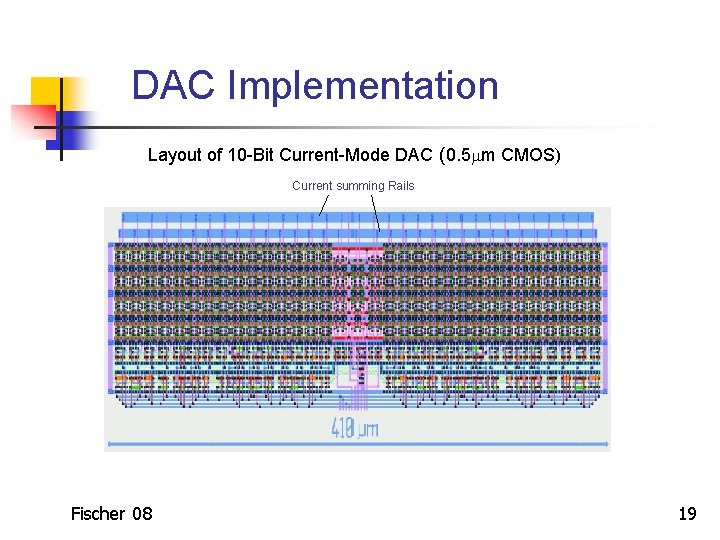

DAC Implementation Layout of 10 -Bit Current-Mode DAC (0. 5 mm CMOS) Current summing Rails Fischer 08 19

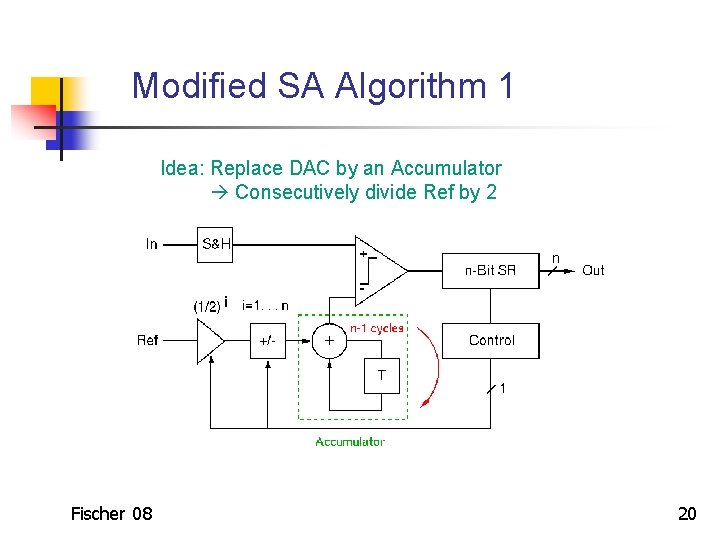

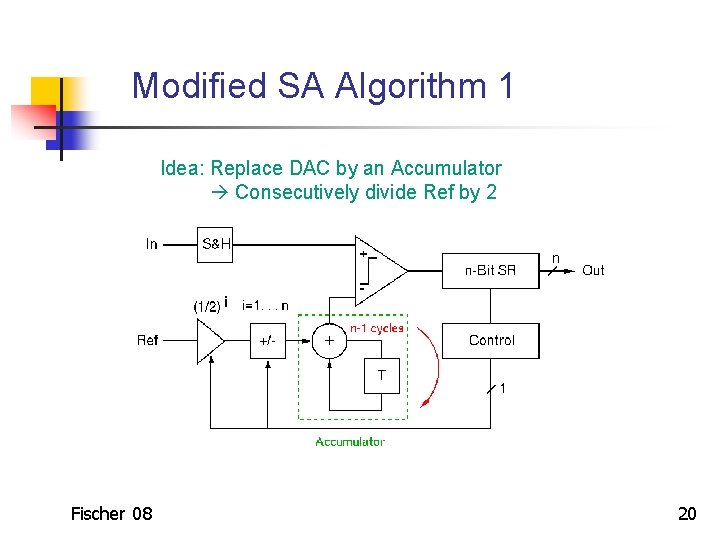

Modified SA Algorithm 1 Idea: Replace DAC by an Accumulator Consecutively divide Ref by 2 Fischer 08 20

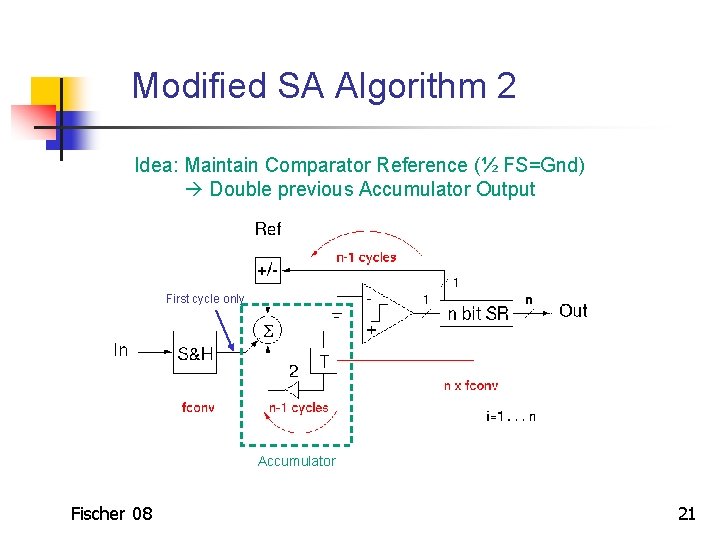

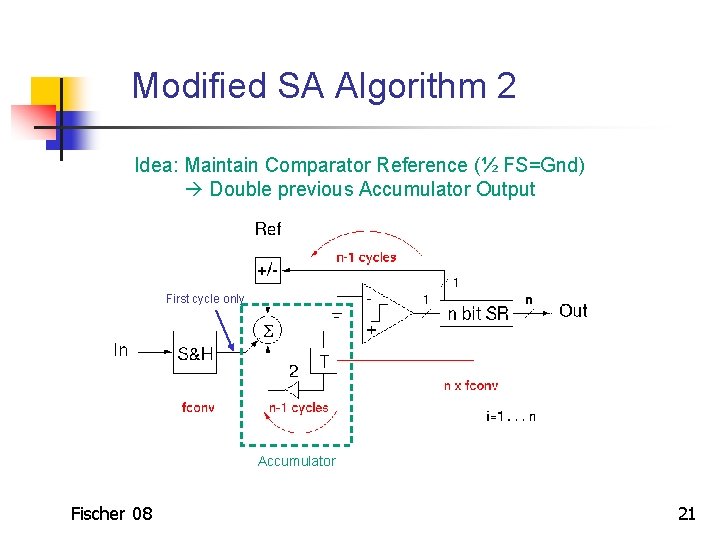

Modified SA Algorithm 2 Idea: Maintain Comparator Reference (½ FS=Gnd) Double previous Accumulator Output First cycle only Accumulator Fischer 08 21

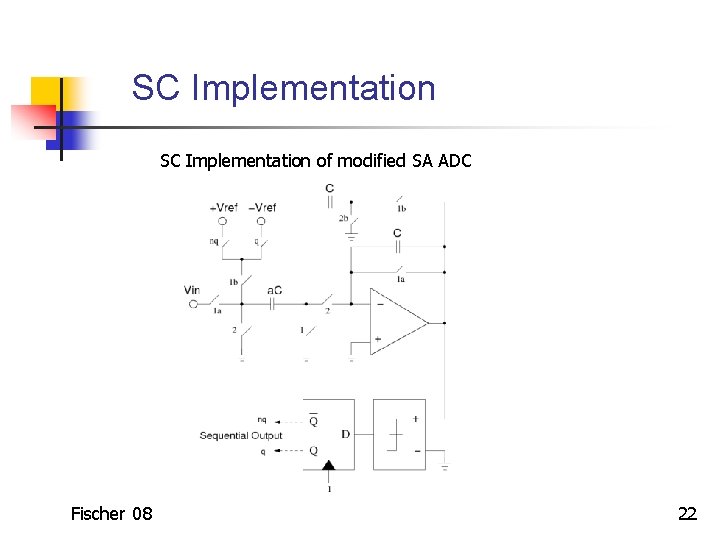

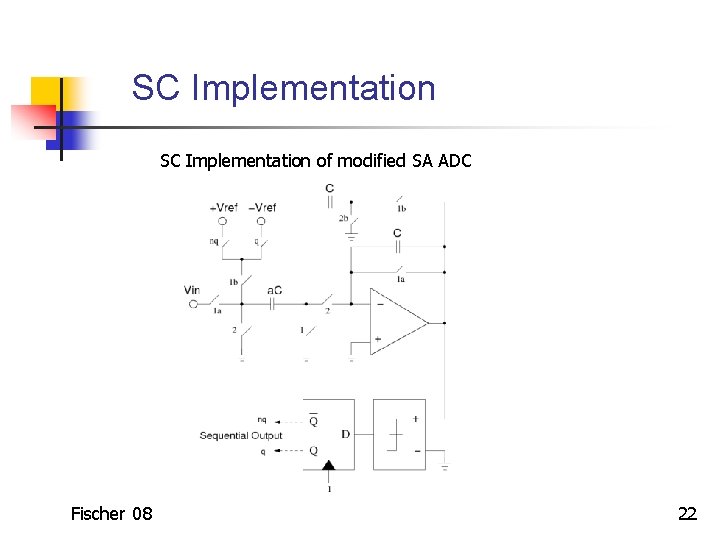

SC Implementation of modified SA ADC Fischer 08 22

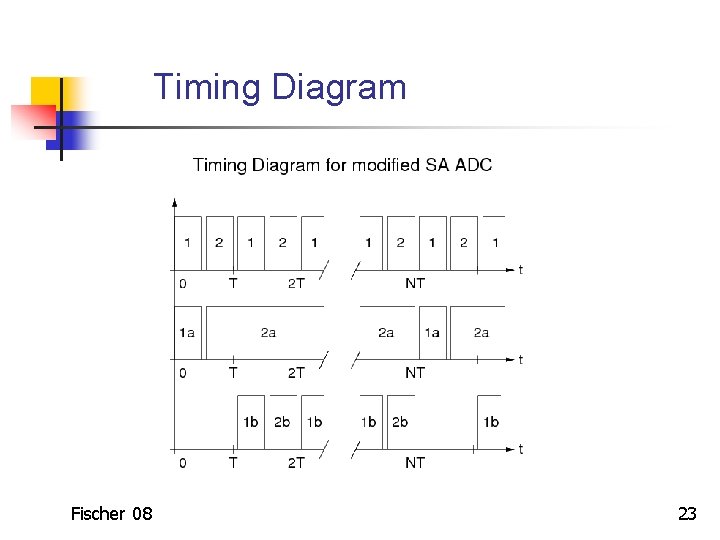

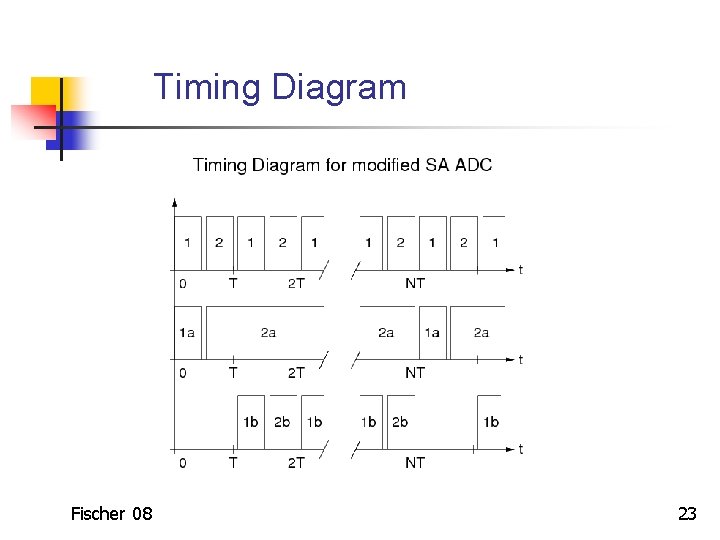

Timing Diagram Fischer 08 23

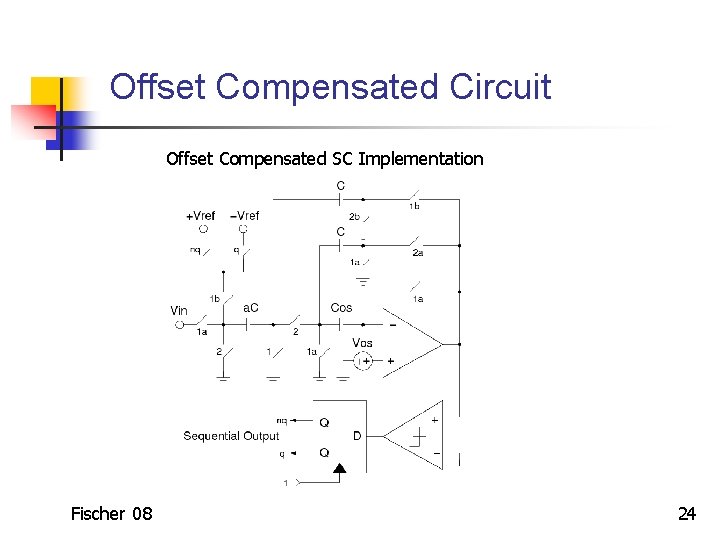

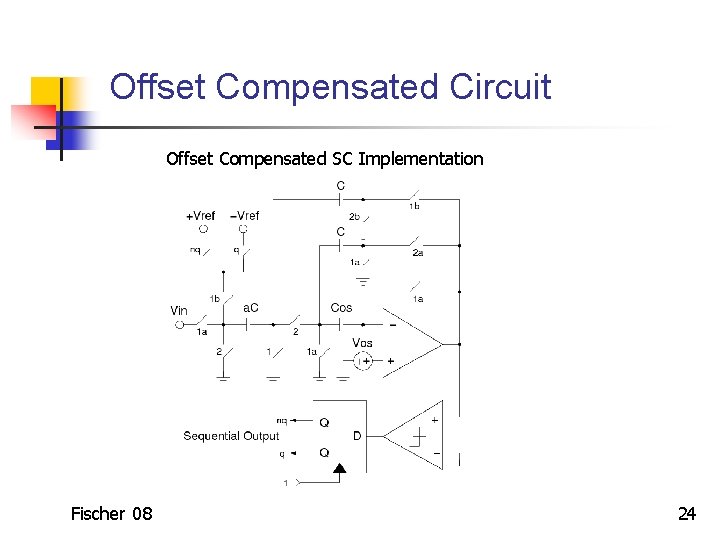

Offset Compensated Circuit Offset Compensated SC Implementation Fischer 08 24

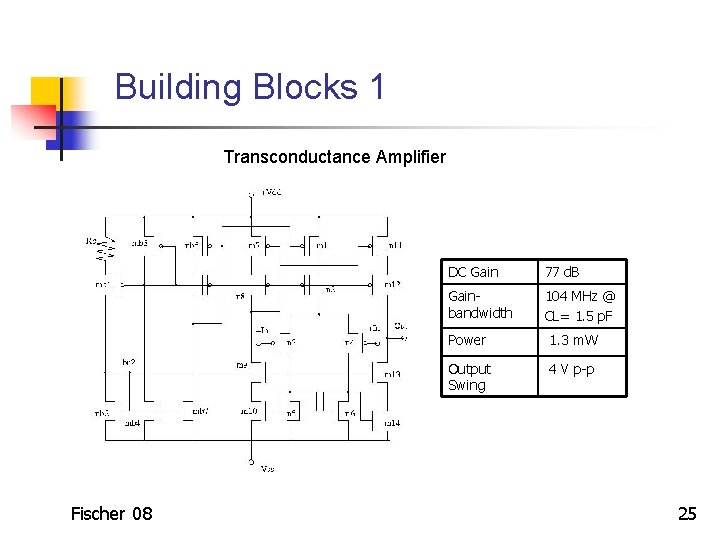

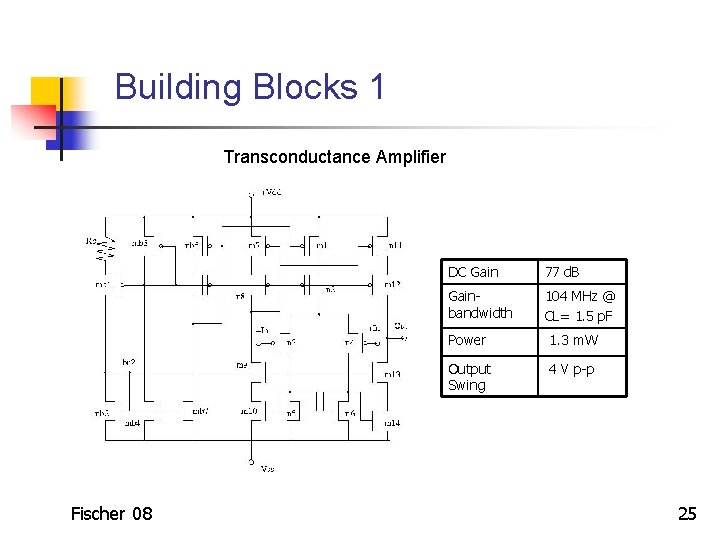

Building Blocks 1 Transconductance Amplifier Fischer 08 DC Gain 77 d. B Gainbandwidth 104 MHz @ CL= 1. 5 p. F Power 1. 3 m. W Output Swing 4 V p-p 25

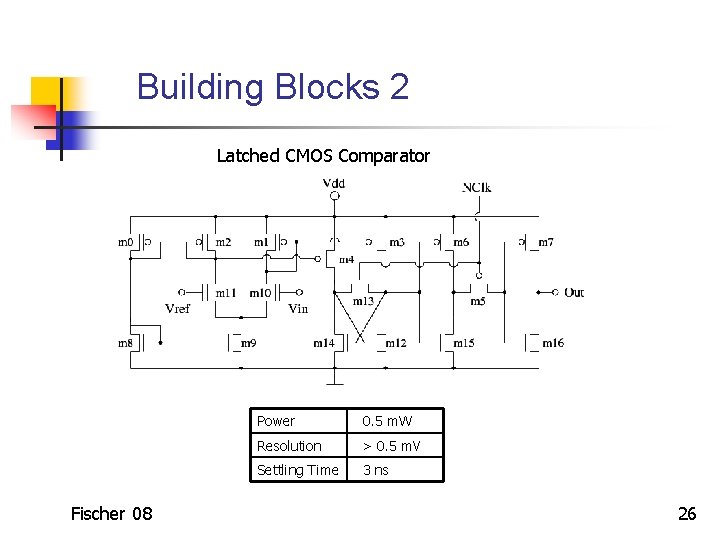

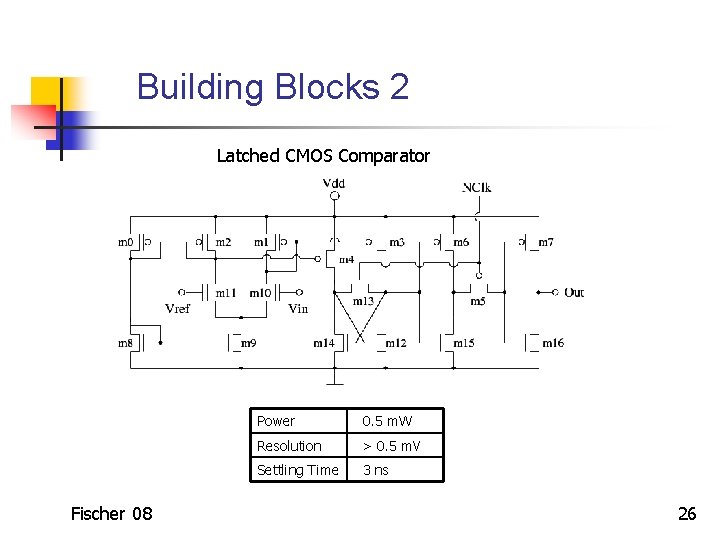

Building Blocks 2 Latched CMOS Comparator Fischer 08 Power 0. 5 m. W Resolution > 0. 5 m. V Settling Time 3 ns 26

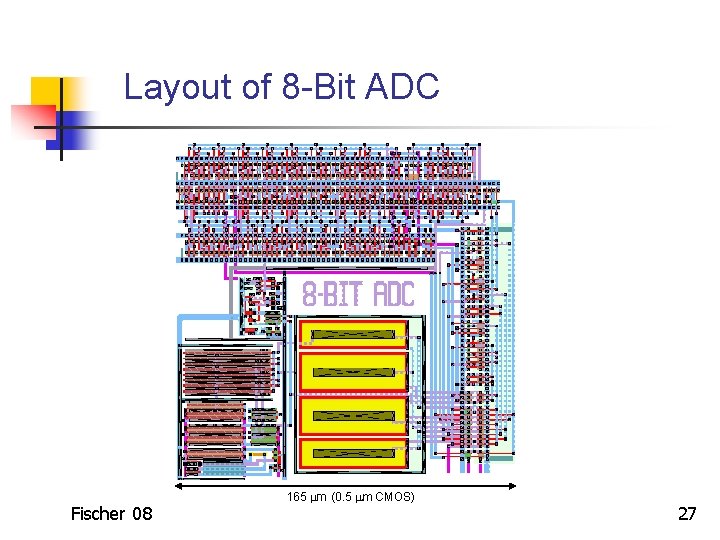

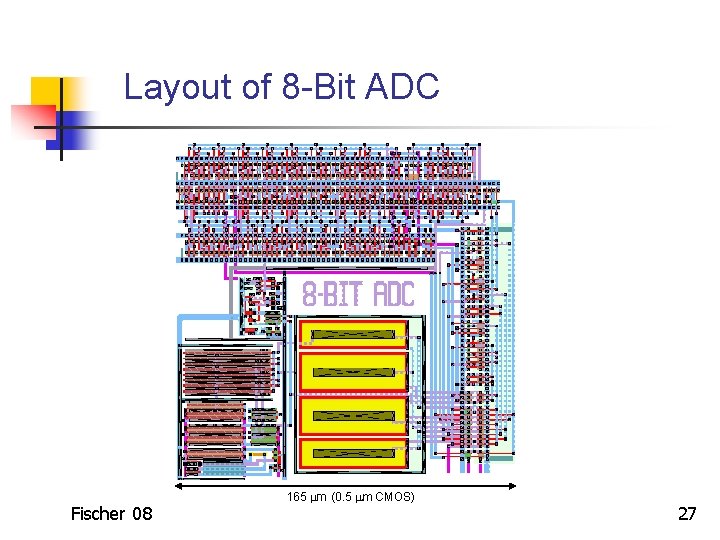

Layout of 8 -Bit ADC Fischer 08 165 mm (0. 5 mm CMOS) 27

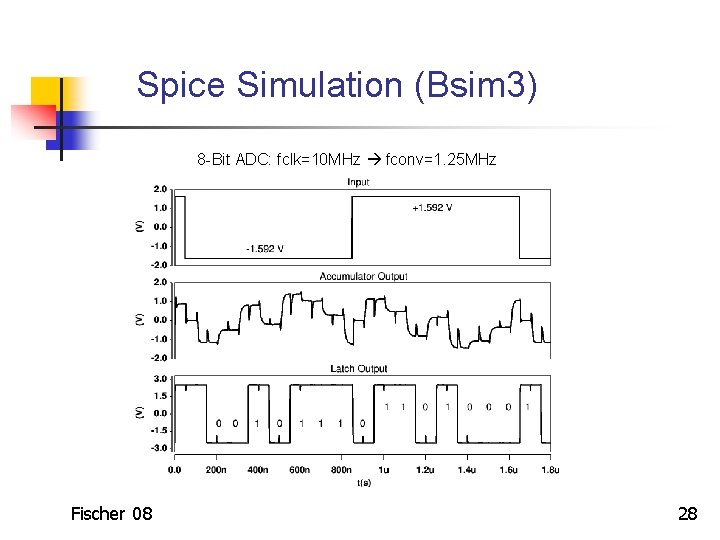

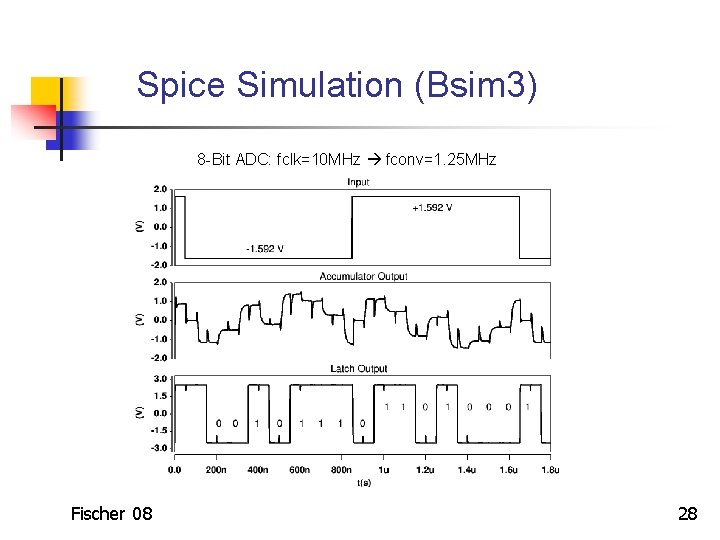

Spice Simulation (Bsim 3) 8 -Bit ADC: fclk=10 MHz fconv=1. 25 MHz Fischer 08 28

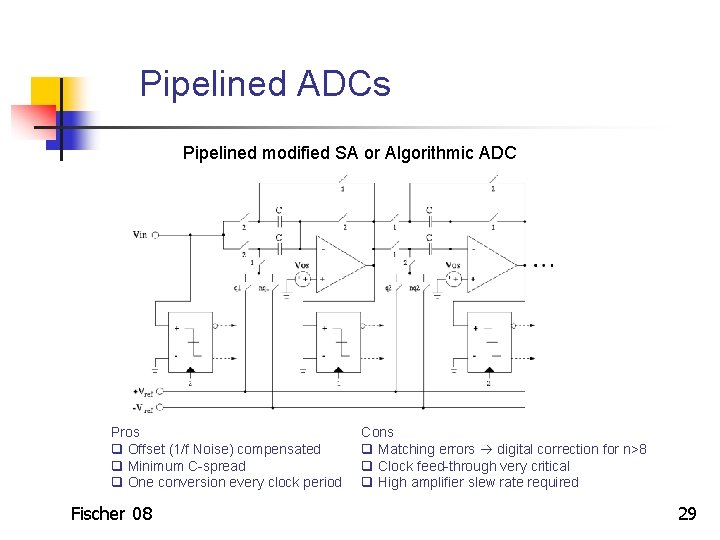

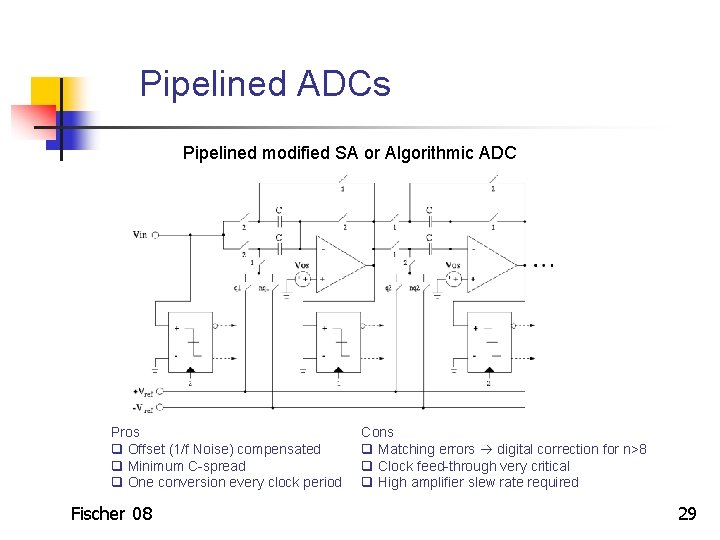

Pipelined ADCs Pipelined modified SA or Algorithmic ADC Pros q Offset (1/f Noise) compensated q Minimum C-spread q One conversion every clock period Fischer 08 Cons q Matching errors digital correction for n>8 q Clock feed-through very critical q High amplifier slew rate required 29

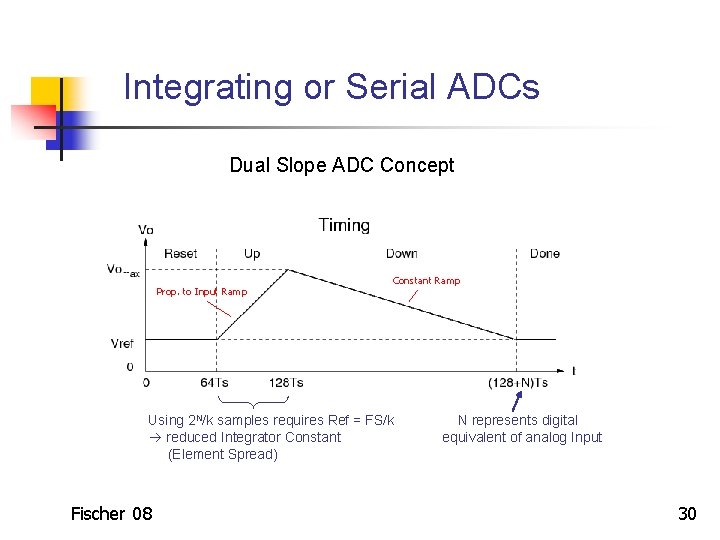

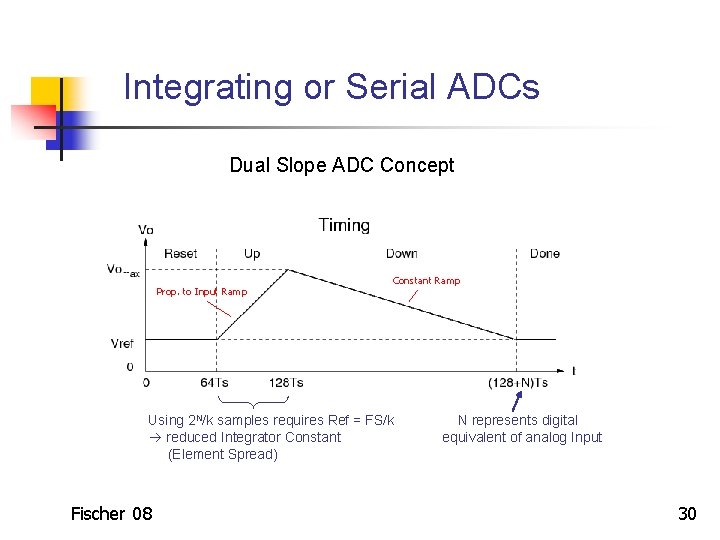

Integrating or Serial ADCs Dual Slope ADC Concept Prop. to Input Ramp Constant Ramp Using 2 N/k samples requires Ref = FS/k reduced Integrator Constant (Element Spread) Fischer 08 N represents digital equivalent of analog Input 30

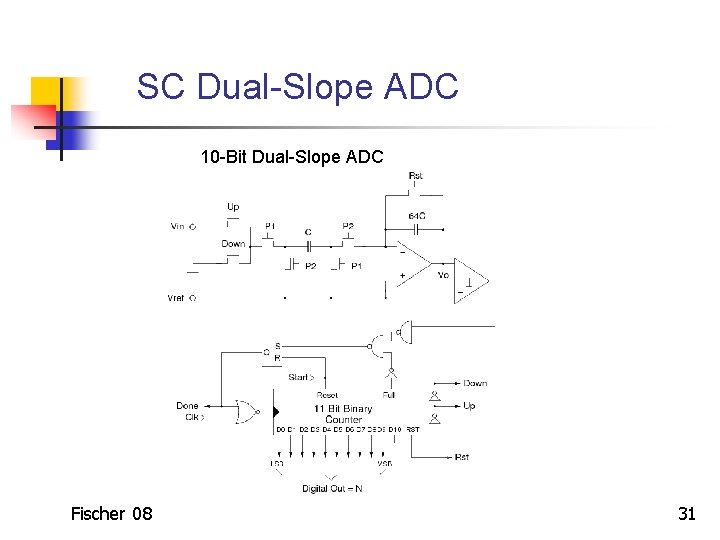

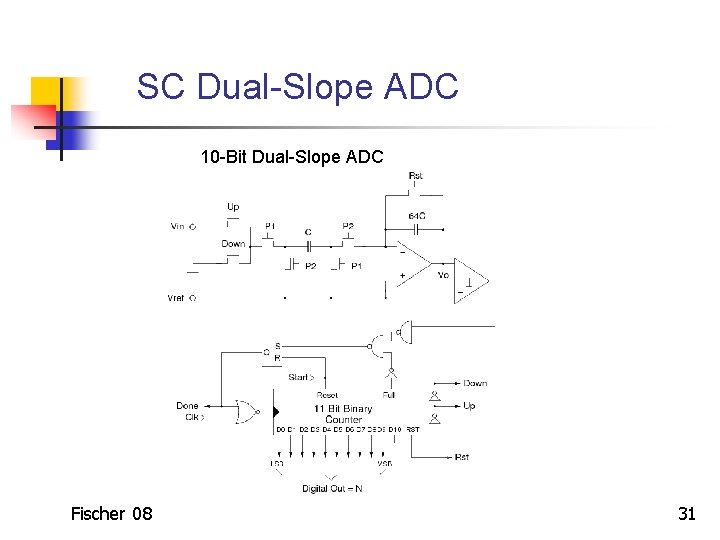

SC Dual-Slope ADC 10 -Bit Dual-Slope ADC Fischer 08 31

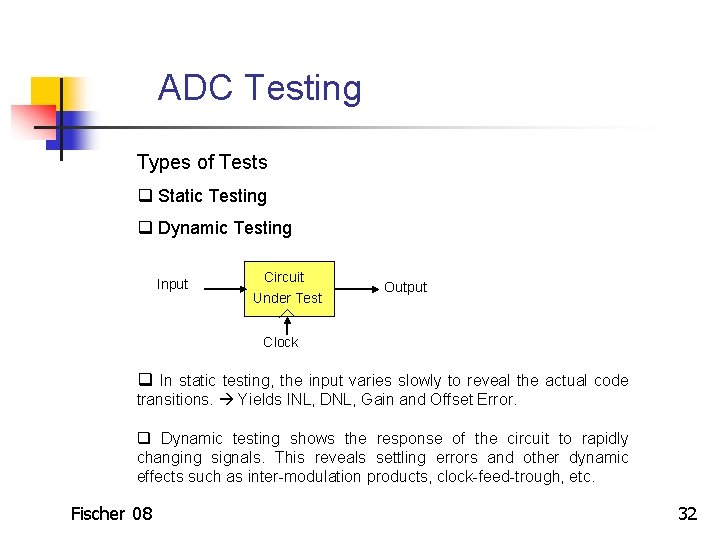

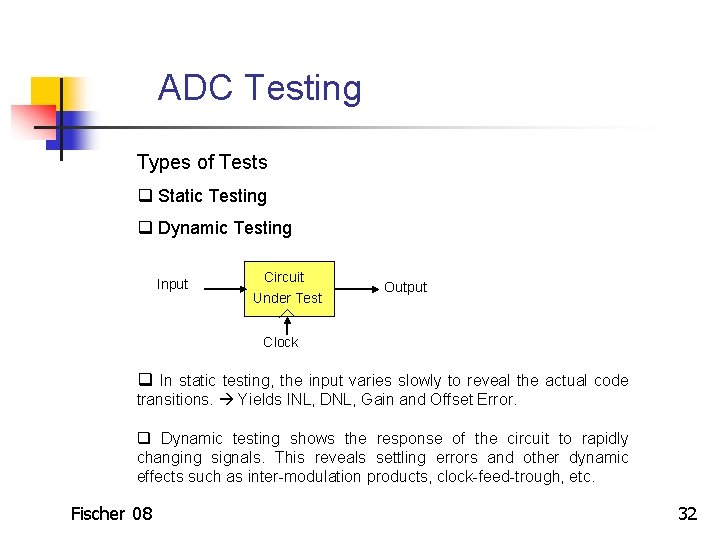

ADC Testing Types of Tests q Static Testing q Dynamic Testing Input Circuit Under Test Output Clock q In static testing, the input varies slowly to reveal the actual code transitions. Yields INL, DNL, Gain and Offset Error. q Dynamic testing shows the response of the circuit to rapidly changing signals. This reveals settling errors and other dynamic effects such as inter-modulation products, clock-feed-trough, etc. Fischer 08 32

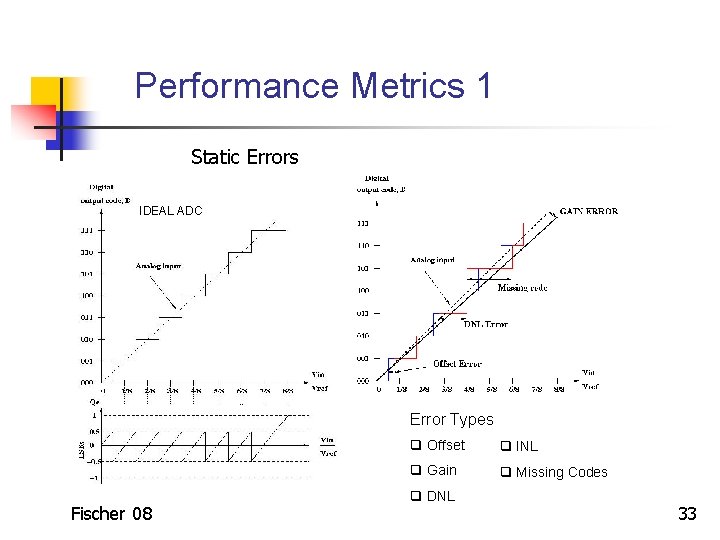

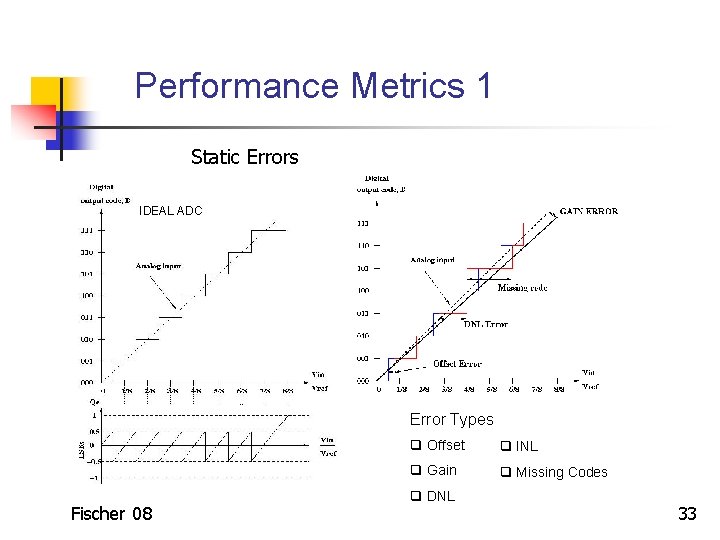

Performance Metrics 1 Static Errors IDEAL ADC Error Types Fischer 08 q Offset q INL q Gain q Missing Codes q DNL 33

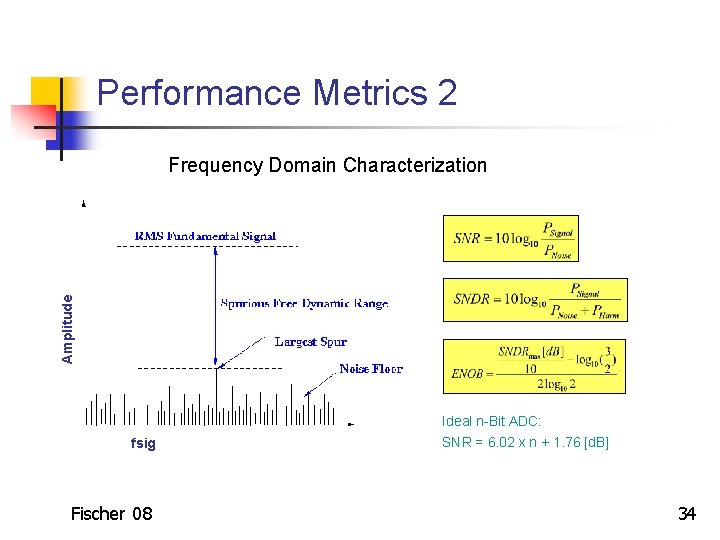

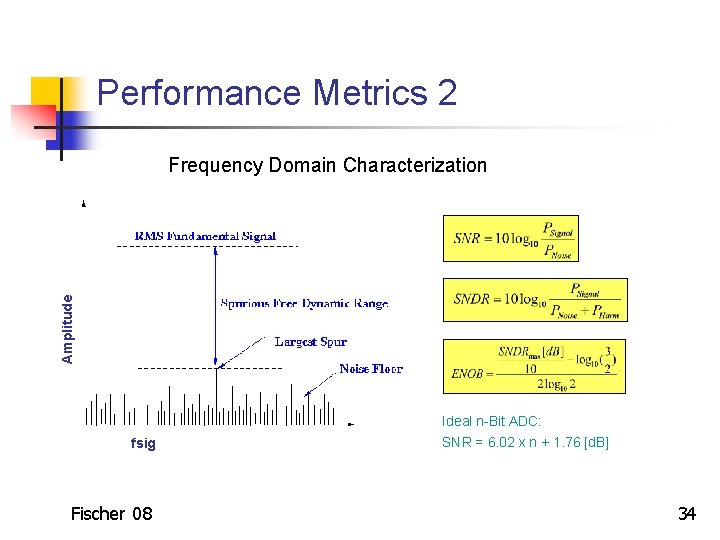

Performance Metrics 2 Amplitude Frequency Domain Characterization Ideal n-Bit ADC: fsig Fischer 08 SNR = 6. 02 x n + 1. 76 [d. B] 34

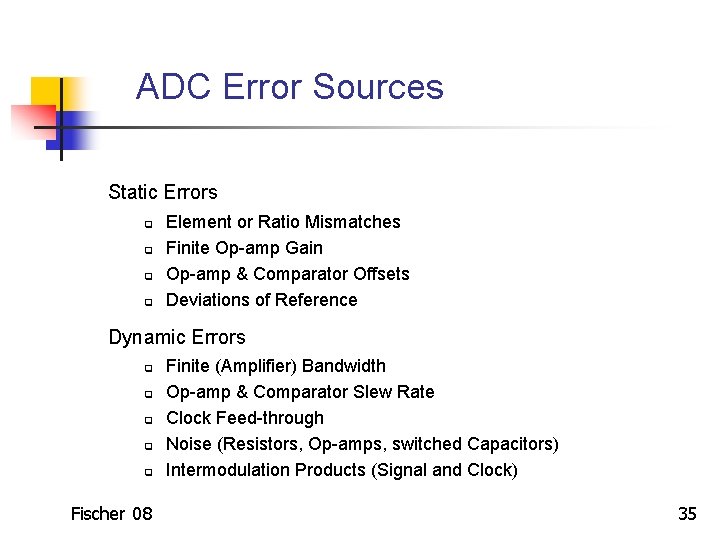

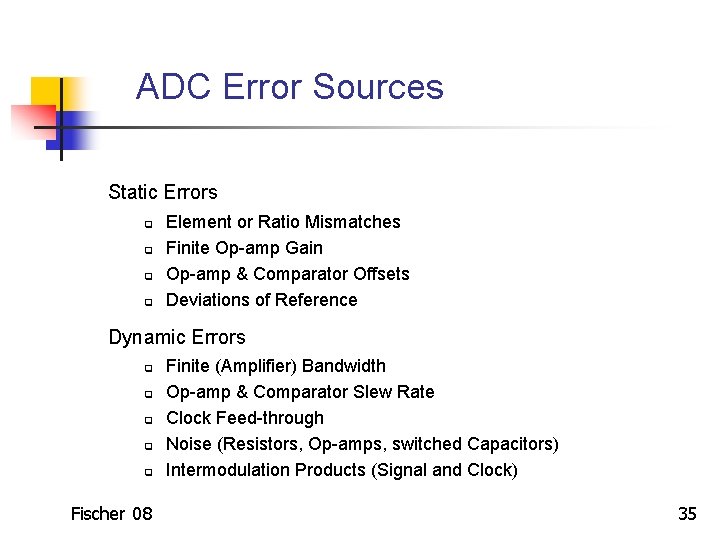

ADC Error Sources Static Errors q q Element or Ratio Mismatches Finite Op-amp Gain Op-amp & Comparator Offsets Deviations of Reference Dynamic Errors q q q Fischer 08 Finite (Amplifier) Bandwidth Op-amp & Comparator Slew Rate Clock Feed-through Noise (Resistors, Op-amps, switched Capacitors) Intermodulation Products (Signal and Clock) 35

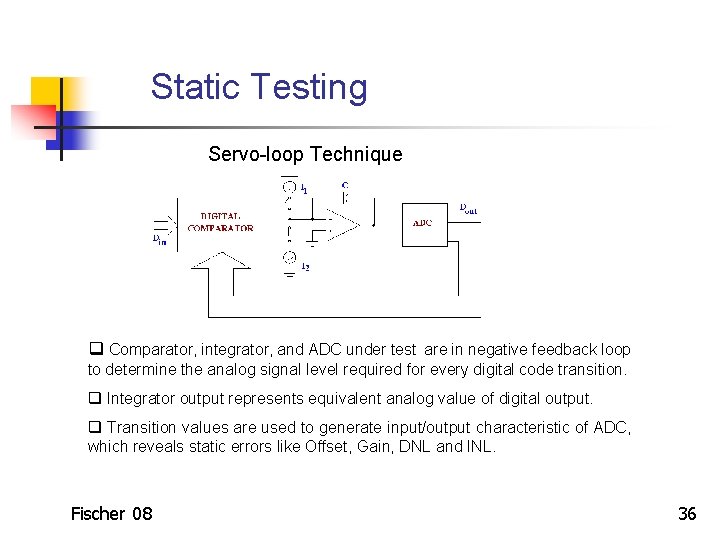

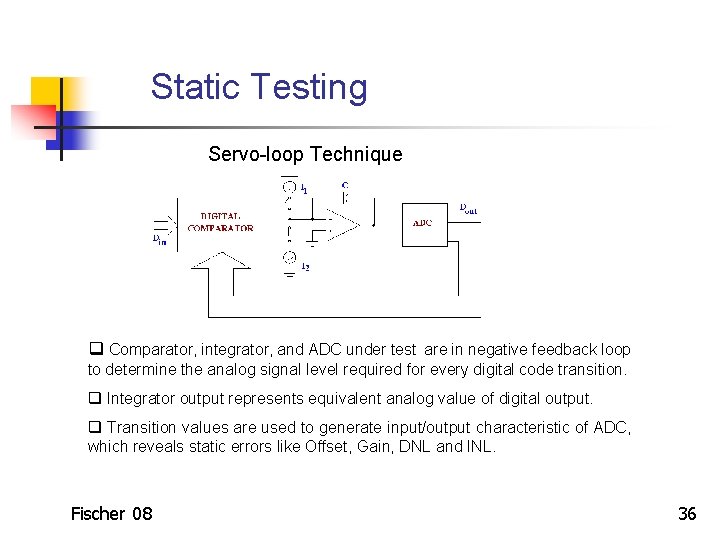

Static Testing Servo-loop Technique q Comparator, integrator, and ADC under test are in negative feedback loop to determine the analog signal level required for every digital code transition. q Integrator output represents equivalent analog value of digital output. q Transition values are used to generate input/output characteristic of ADC, which reveals static errors like Offset, Gain, DNL and INL. Fischer 08 36

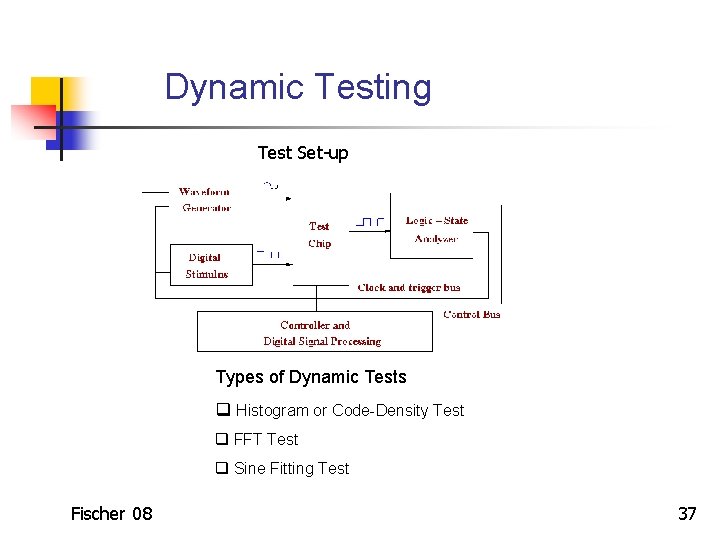

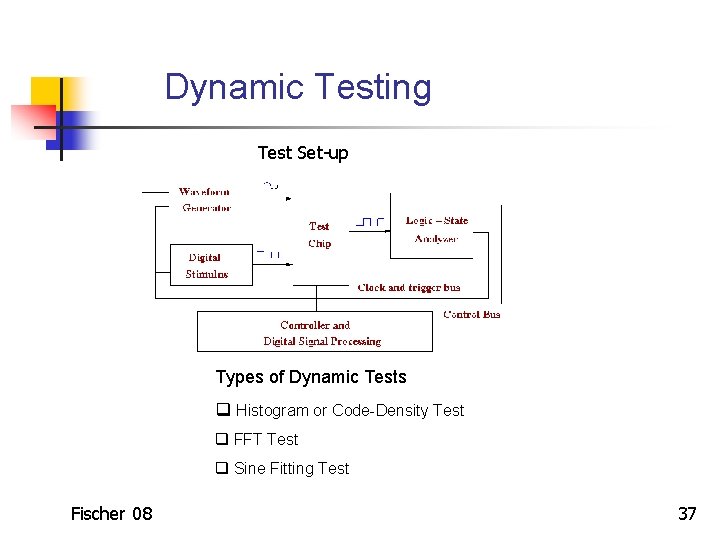

Dynamic Testing Test Set-up Types of Dynamic Tests q Histogram or Code-Density Test q FFT Test q Sine Fitting Test Fischer 08 37

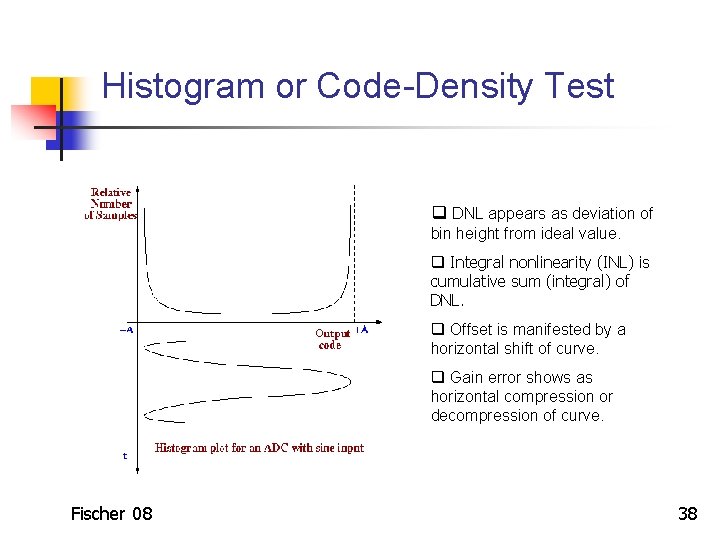

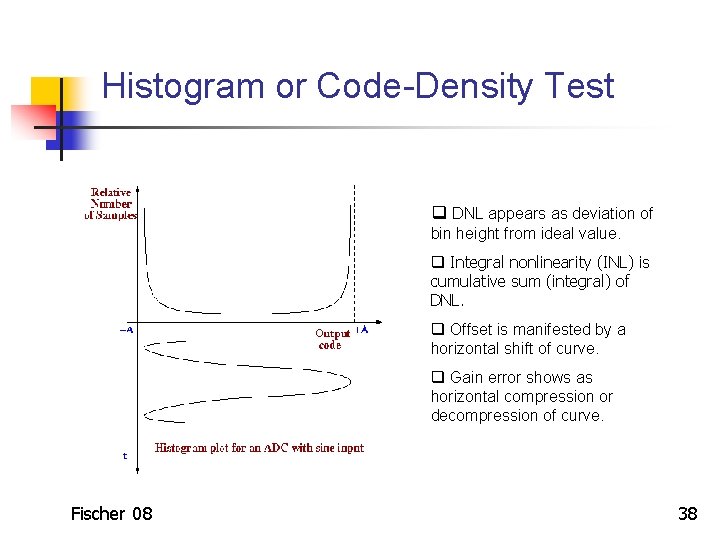

Histogram or Code-Density Test q DNL appears as deviation of bin height from ideal value. q Integral nonlinearity (INL) is cumulative sum (integral) of DNL. q Offset is manifested by a horizontal shift of curve. q Gain error shows as horizontal compression or decompression of curve. Fischer 08 38

Histogram Test Pros and Cons of Histogram Test q Histogram test provides information on each code transition. q DNL errors may be concealed due to random noise in circuit. q Input frequency must be selected carefully to avoid missing codes (fclk/fin must be non-integer ratio). q Input Swing is critical (cover full range) q Requires a large number of conversions (o 2 n x 1, 000). Fischer 08 39

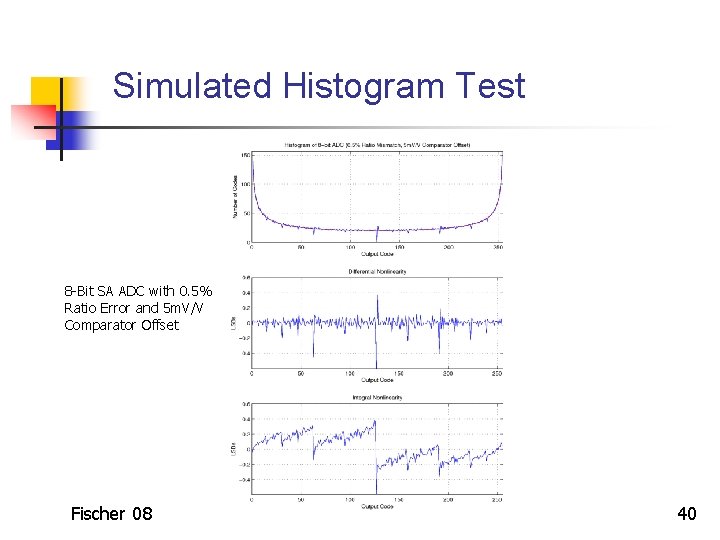

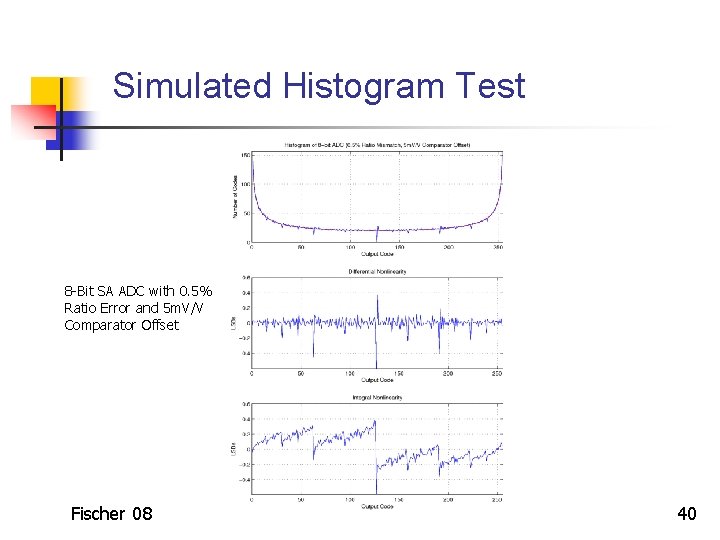

Simulated Histogram Test 8 -Bit SA ADC with 0. 5% Ratio Error and 5 m. V/V Comparator Offset Fischer 08 40

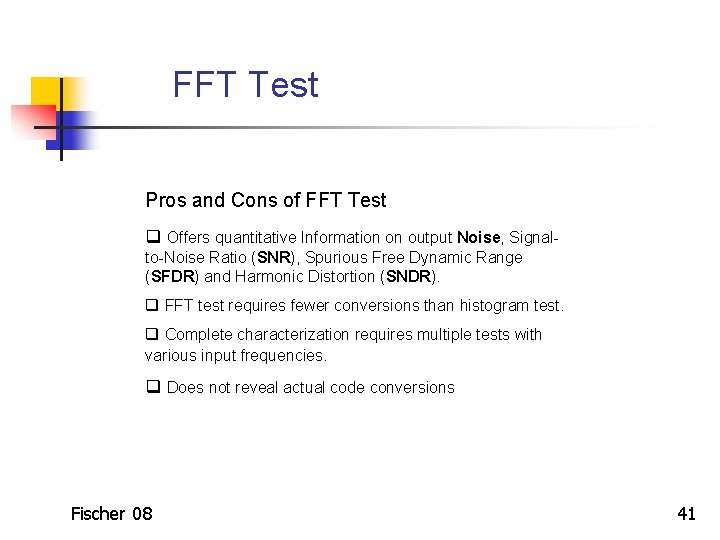

FFT Test Pros and Cons of FFT Test q Offers quantitative Information on output Noise, Signalto-Noise Ratio (SNR), Spurious Free Dynamic Range (SFDR) and Harmonic Distortion (SNDR). q FFT test requires fewer conversions than histogram test. q Complete characterization requires multiple tests with various input frequencies. q Does not reveal actual code conversions Fischer 08 41

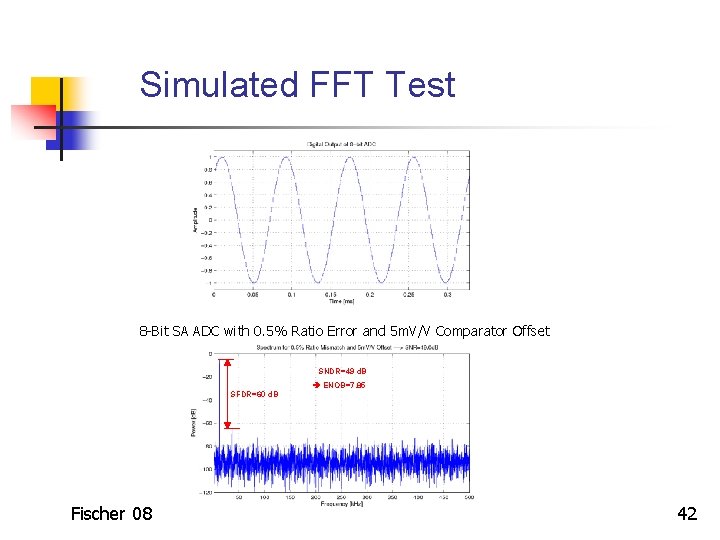

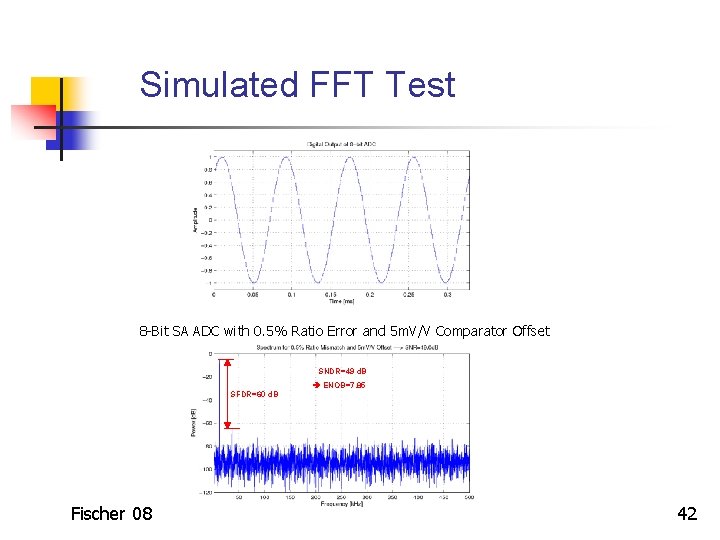

Simulated FFT Test 8 -Bit SA ADC with 0. 5% Ratio Error and 5 m. V/V Comparator Offset SNDR=49 d. B SFDR=60 d. B Fischer 08 ENOB=7. 85 42