Analog Integrated Circuits Lecture 1 Introduction and MOS

- Slides: 66

Analog Integrated Circuits Lecture 1: Introduction and MOS Physics ELC 601 – Fall 2013 Dr. Ahmed Nader Dr. Mohamed M. Aboudina anader@ieee. org maboudina@gmail. com Department of Electronics and Communications Engineering Faculty of Engineering – Cairo University

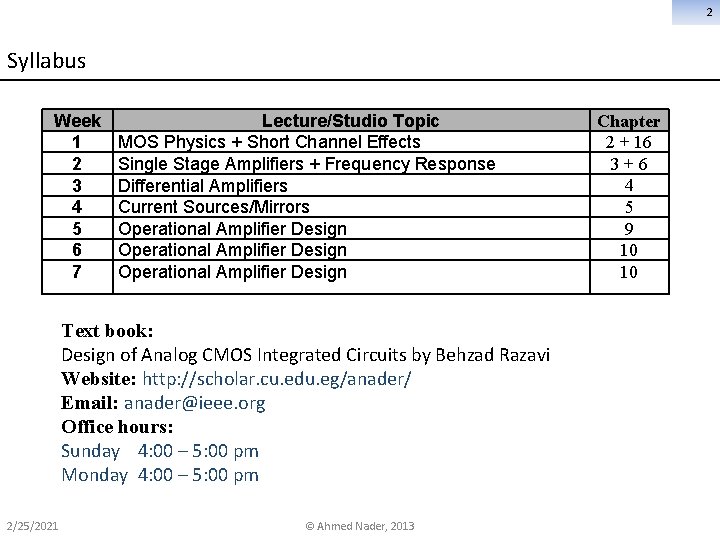

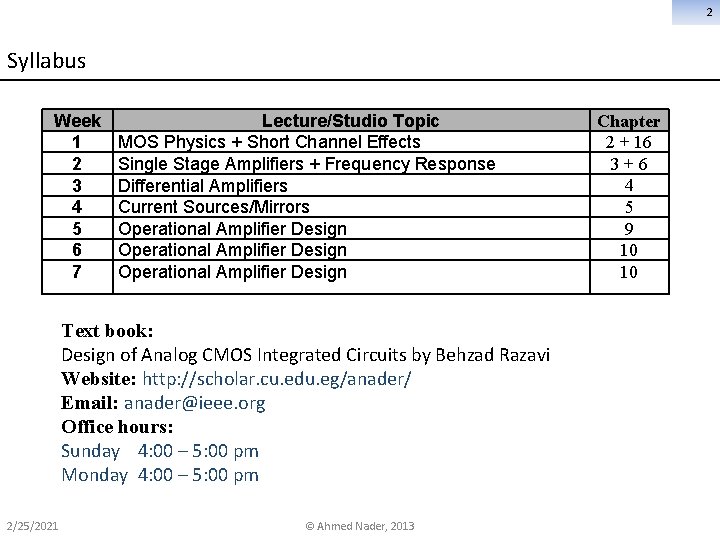

2 Syllabus Week 1 2 3 4 5 6 7 Lecture/Studio Topic MOS Physics + Short Channel Effects Single Stage Amplifiers + Frequency Response Differential Amplifiers Current Sources/Mirrors Operational Amplifier Design Text book: Design of Analog CMOS Integrated Circuits by Behzad Razavi Website: http: //scholar. cu. edu. eg/anader/ Email: anader@ieee. org Office hours: Sunday 4: 00 – 5: 00 pm Monday 4: 00 – 5: 00 pm 2/25/2021 © Ahmed Nader, 2013 Chapter 2 + 16 3+6 4 5 9 10 10

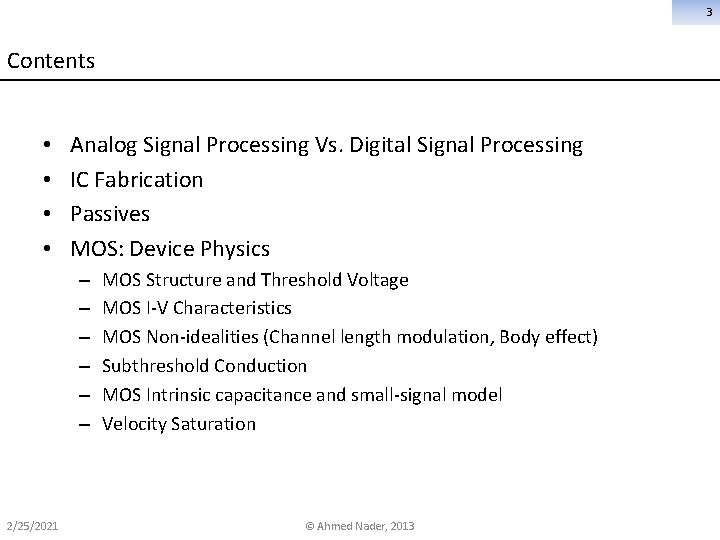

3 Contents • • Analog Signal Processing Vs. Digital Signal Processing IC Fabrication Passives MOS: Device Physics – – – 2/25/2021 MOS Structure and Threshold Voltage MOS I-V Characteristics MOS Non-idealities (Channel length modulation, Body effect) Subthreshold Conduction MOS Intrinsic capacitance and small-signal model Velocity Saturation © Ahmed Nader, 2013

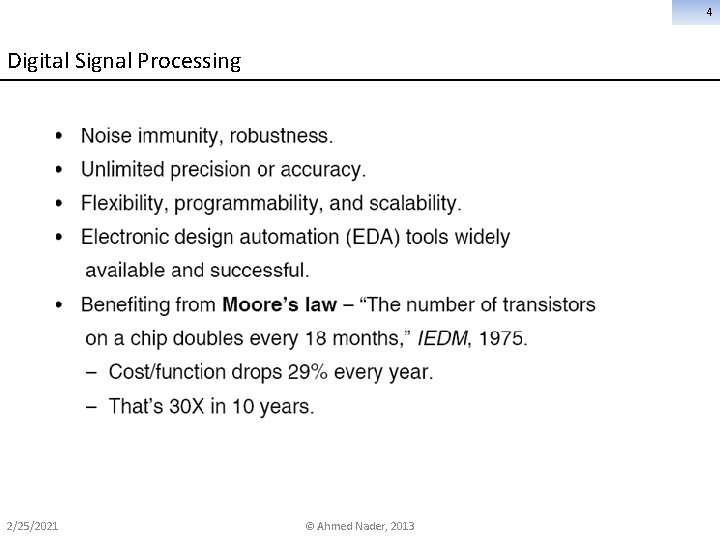

4 Digital Signal Processing 2/25/2021 © Ahmed Nader, 2013

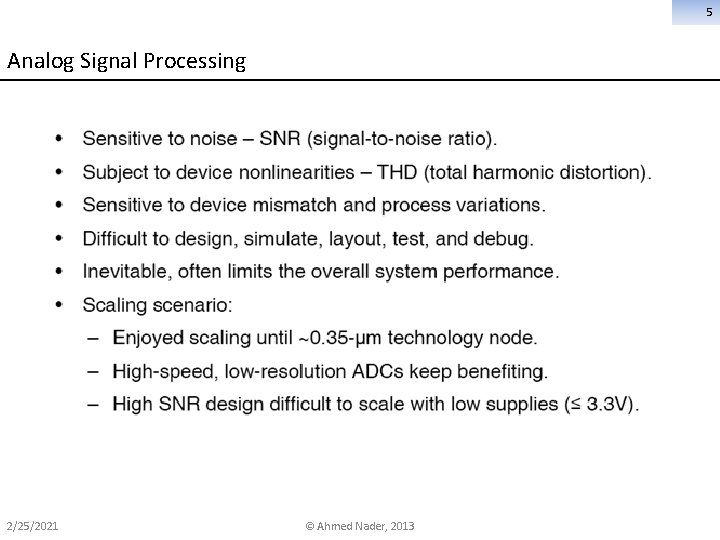

5 Analog Signal Processing 2/25/2021 © Ahmed Nader, 2013

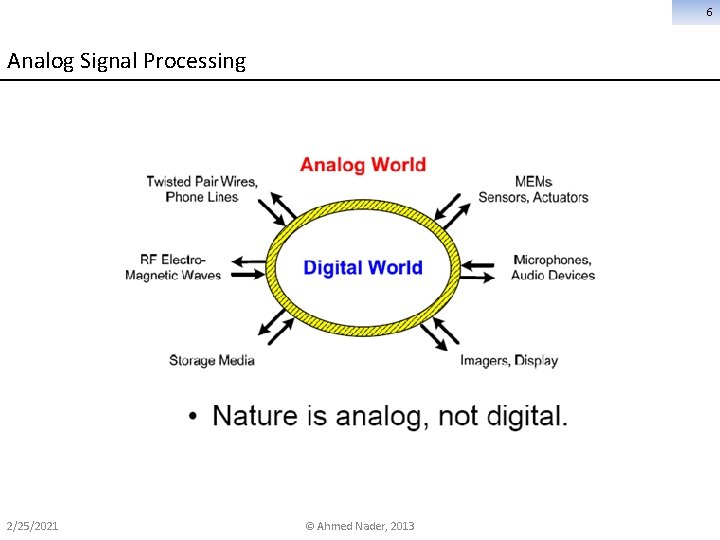

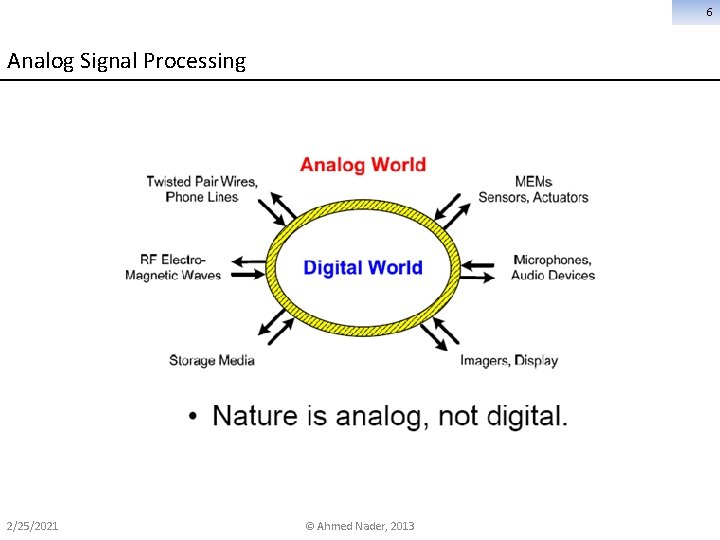

6 Analog Signal Processing 2/25/2021 © Ahmed Nader, 2013

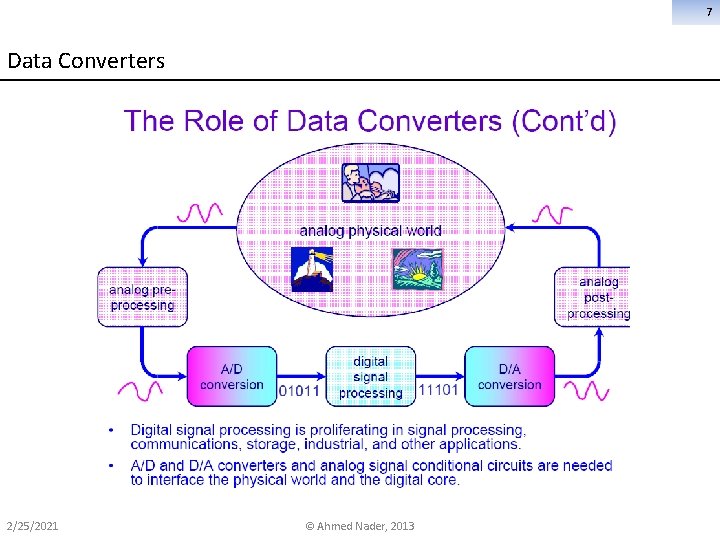

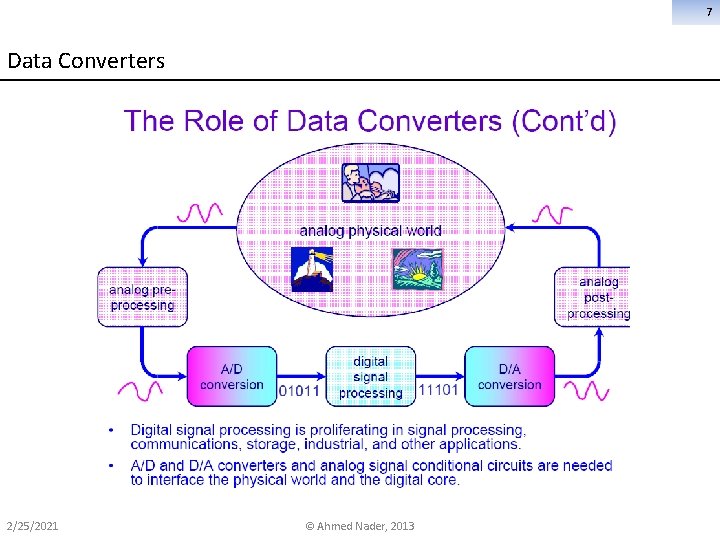

7 Data Converters 2/25/2021 © Ahmed Nader, 2013

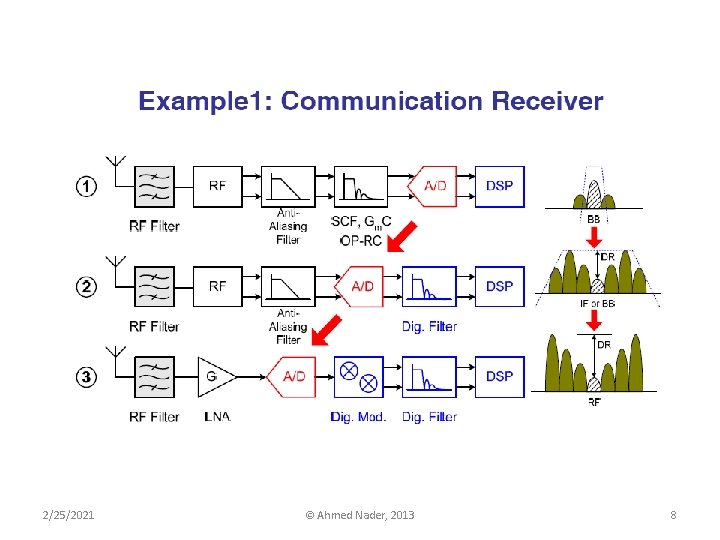

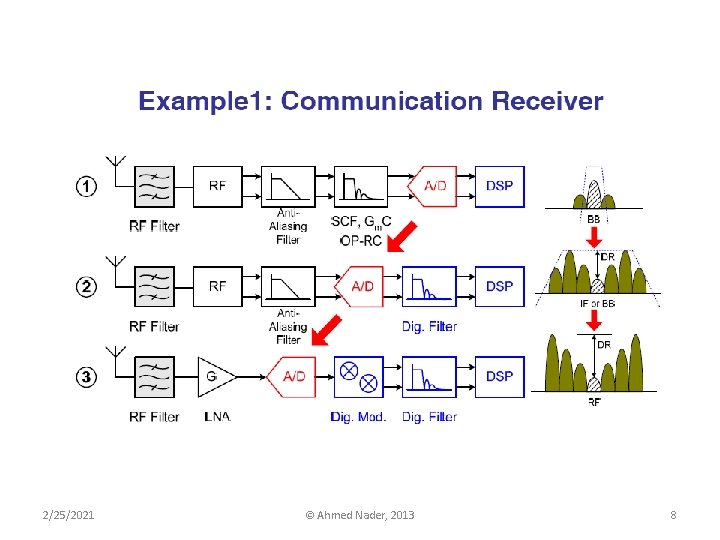

2/25/2021 © Ahmed Nader, 2013 8

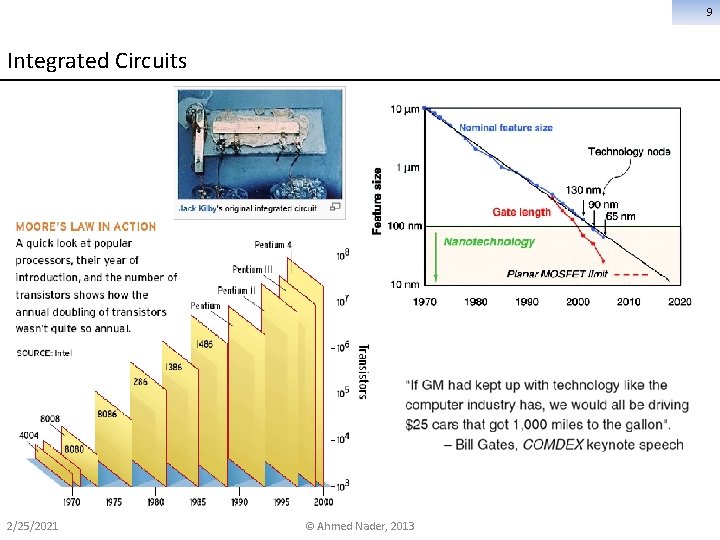

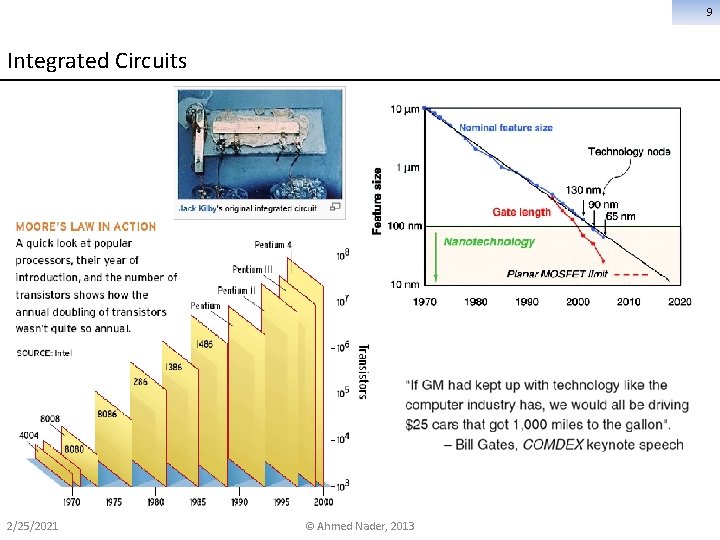

9 Integrated Circuits 2/25/2021 © Ahmed Nader, 2013

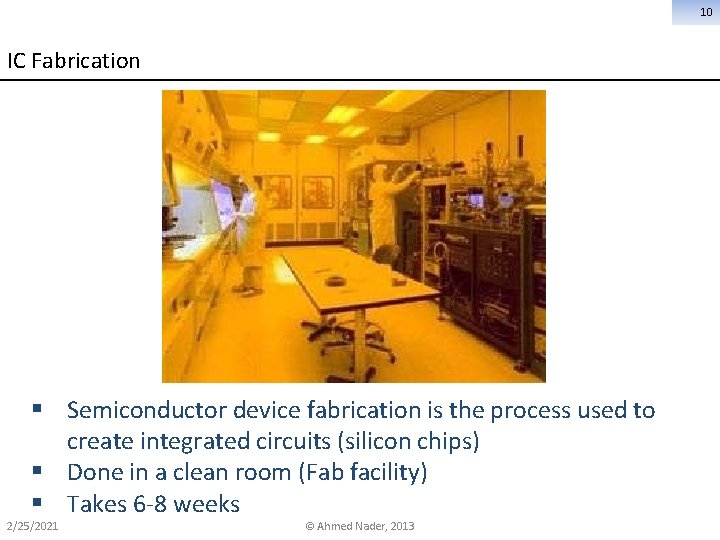

10 IC Fabrication § Semiconductor device fabrication is the process used to create integrated circuits (silicon chips) § Done in a clean room (Fab facility) § Takes 6 -8 weeks 2/25/2021 © Ahmed Nader, 2013

11 Video 2/25/2021 © Ahmed Nader, 2013

12 Semiconductor Industry § § § 2/25/2021 Semiconductor IC industry had revenues that reached $295 billion last year (2012). Microcontrollers (MC), Digital Signal Processors (DSP) and Microprocessors (MP) have been the center of the IC revolution since the beginning. The Personal Computer (PC) boom of the last century has become the Smartphone, Entertainment Console, Notebook and Tablet explosion in the new millennium. Largest companies in that industry are: Intel with $50 billion revenue in 2012. Samsung Electronics ranked second. Qualcomm, Texas instruments, Toshiba rounding out the top 5. Largest manufacturers (Fab facilities): Intel, TSMC, STMicroelectronics, IBM © Ahmed Nader, 2013

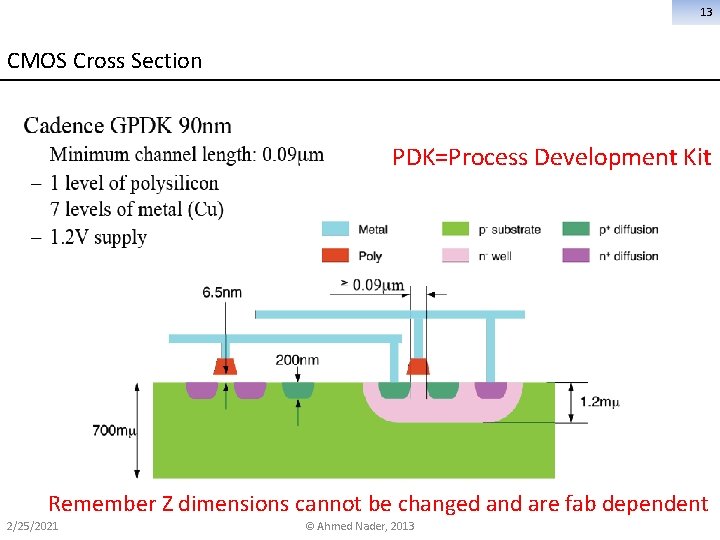

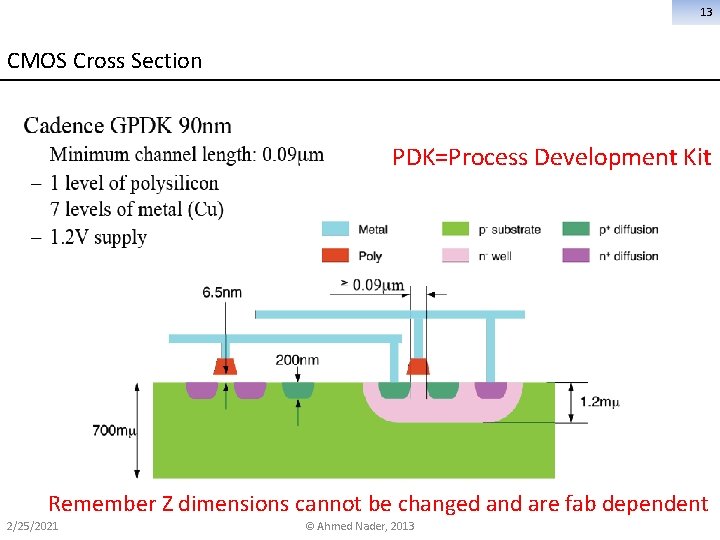

13 CMOS Cross Section PDK=Process Development Kit Remember Z dimensions cannot be changed and are fab dependent 2/25/2021 © Ahmed Nader, 2013

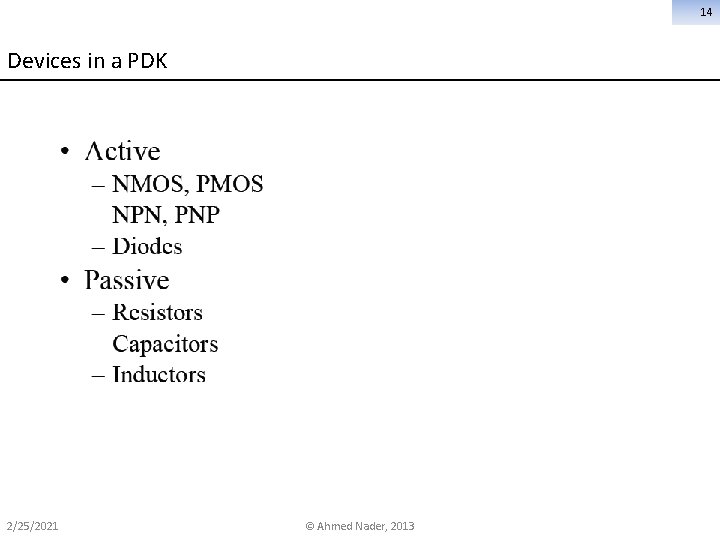

14 Devices in a PDK 2/25/2021 © Ahmed Nader, 2013

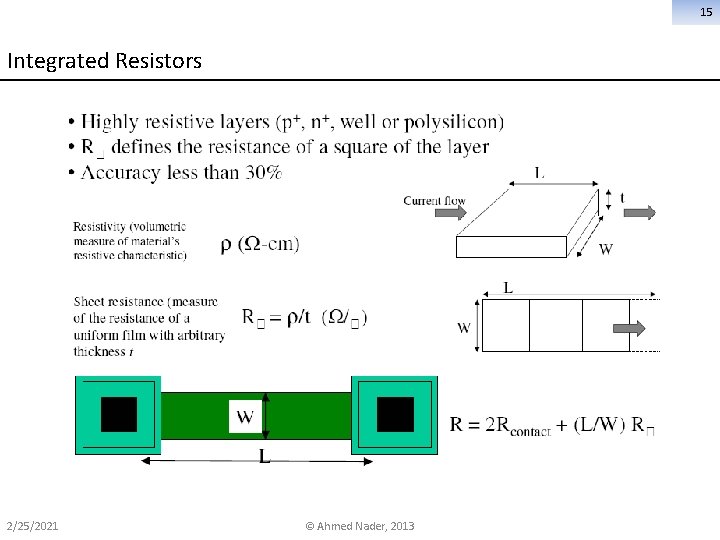

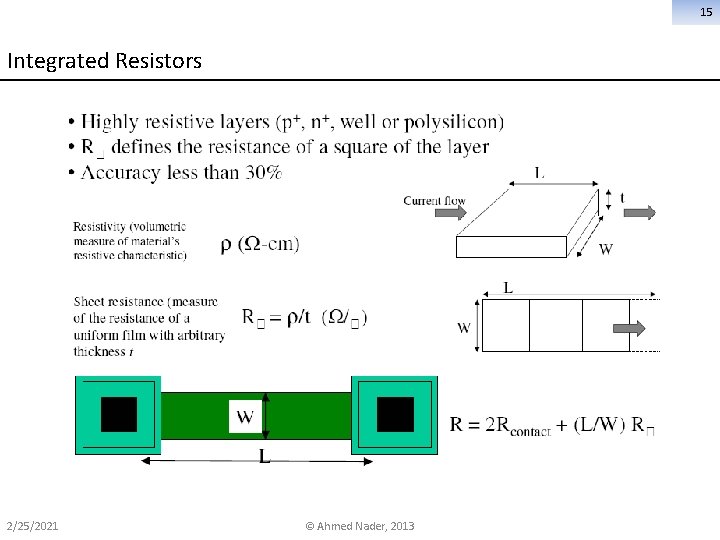

15 Integrated Resistors 2/25/2021 © Ahmed Nader, 2013

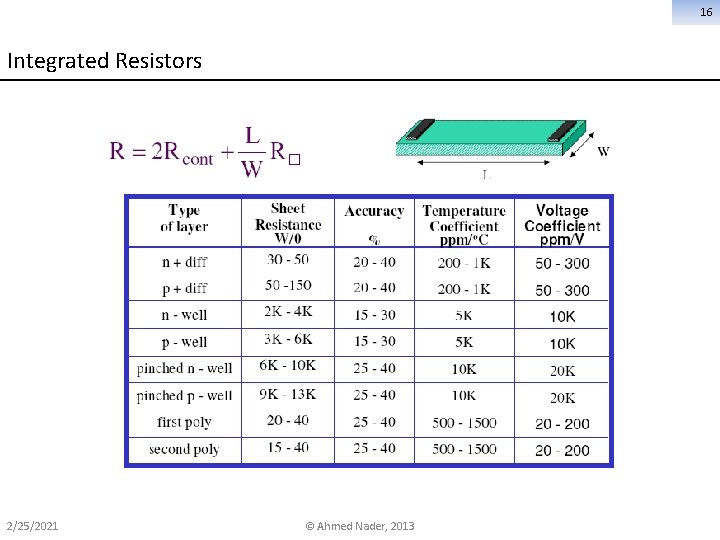

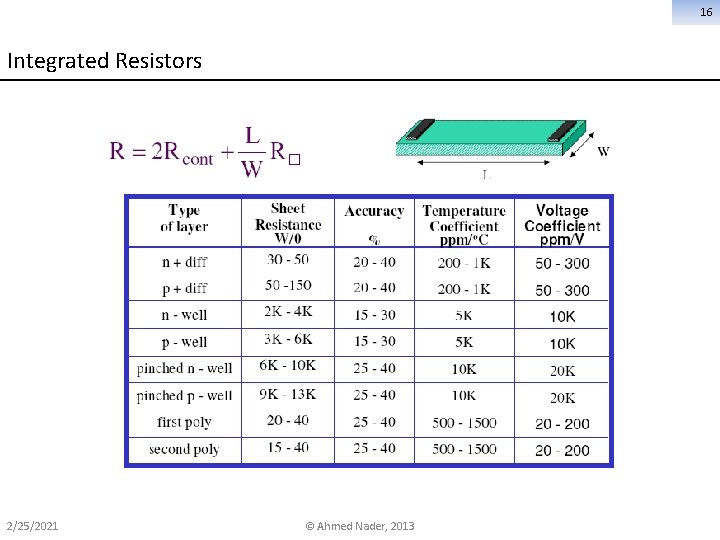

16 Integrated Resistors 2/25/2021 © Ahmed Nader, 2013

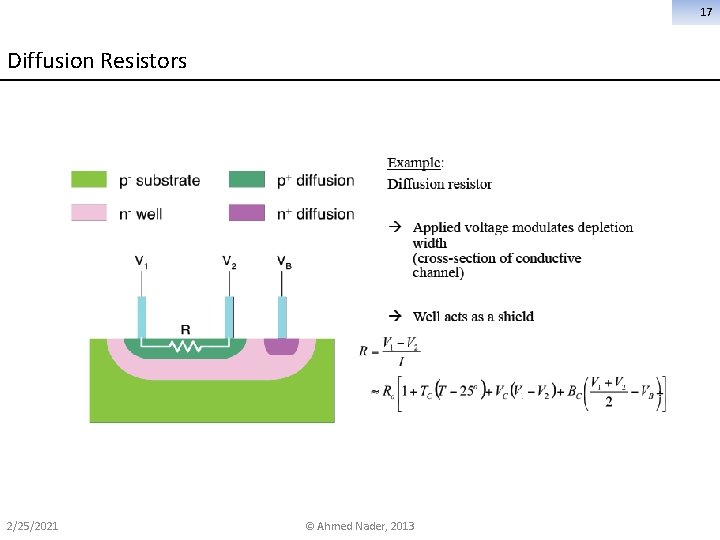

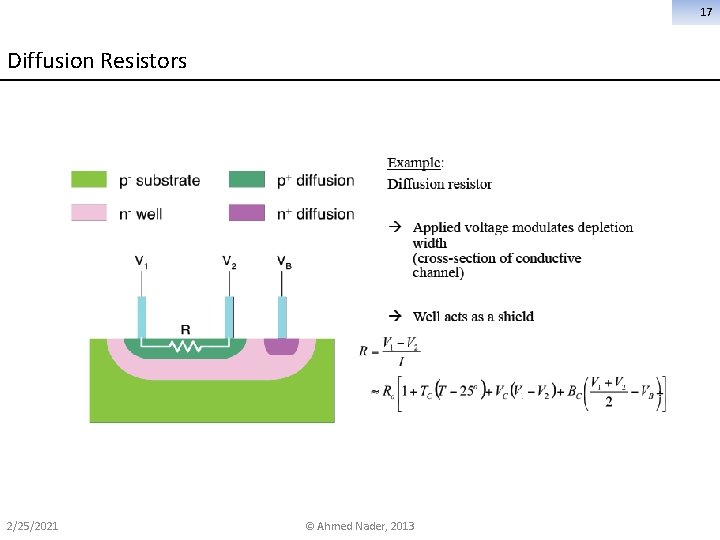

17 Diffusion Resistors 2/25/2021 © Ahmed Nader, 2013

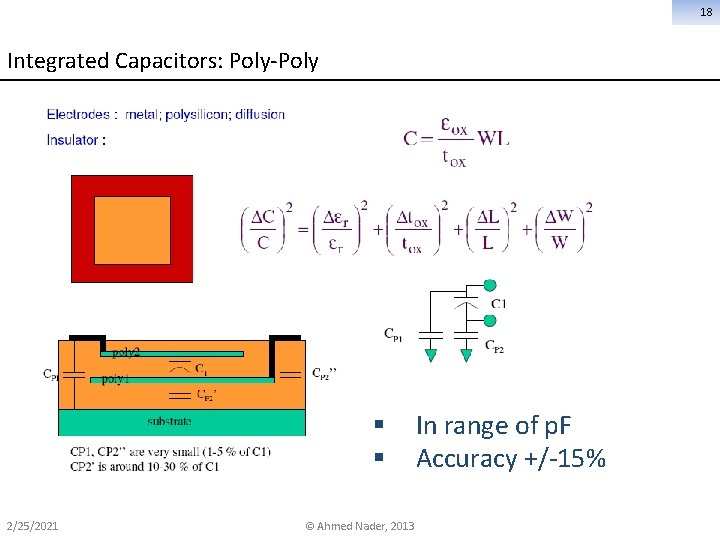

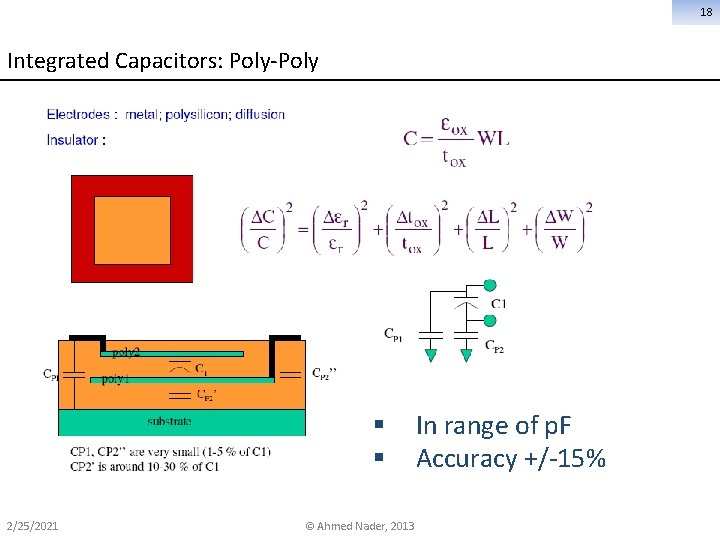

18 Integrated Capacitors: Poly-Poly § In range of p. F § Accuracy +/-15% 2/25/2021 © Ahmed Nader, 2013

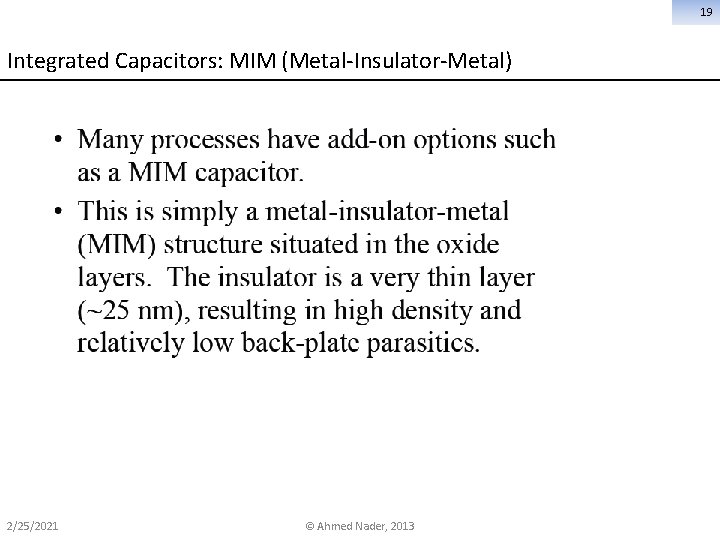

19 Integrated Capacitors: MIM (Metal-Insulator-Metal) 2/25/2021 © Ahmed Nader, 2013

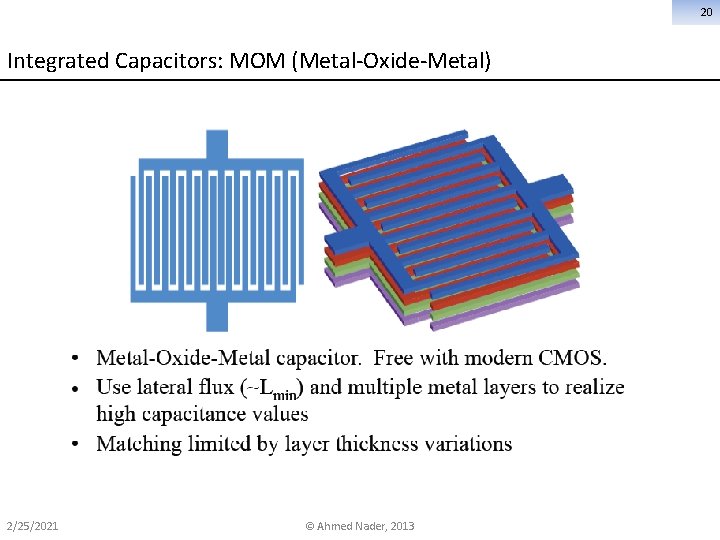

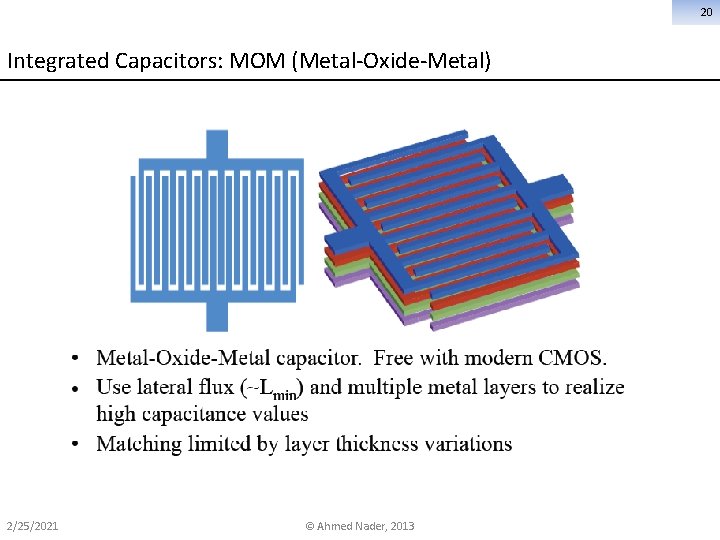

20 Integrated Capacitors: MOM (Metal-Oxide-Metal) 2/25/2021 © Ahmed Nader, 2013

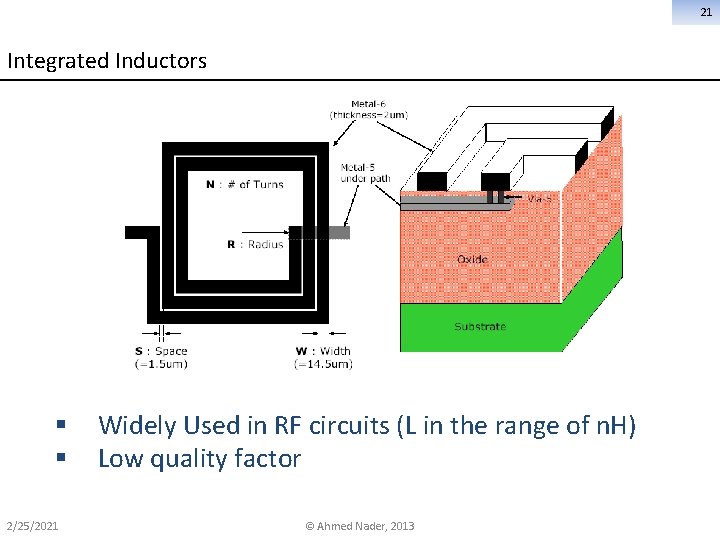

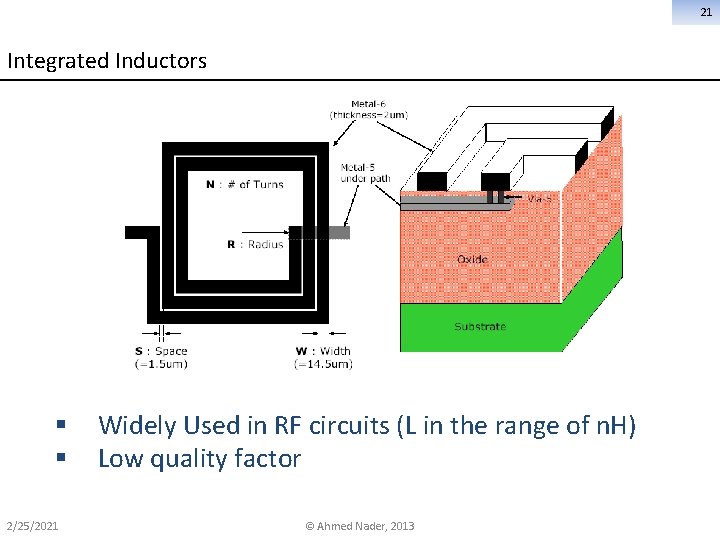

21 Integrated Inductors § Widely Used in RF circuits (L in the range of n. H) § Low quality factor 2/25/2021 © Ahmed Nader, 2013

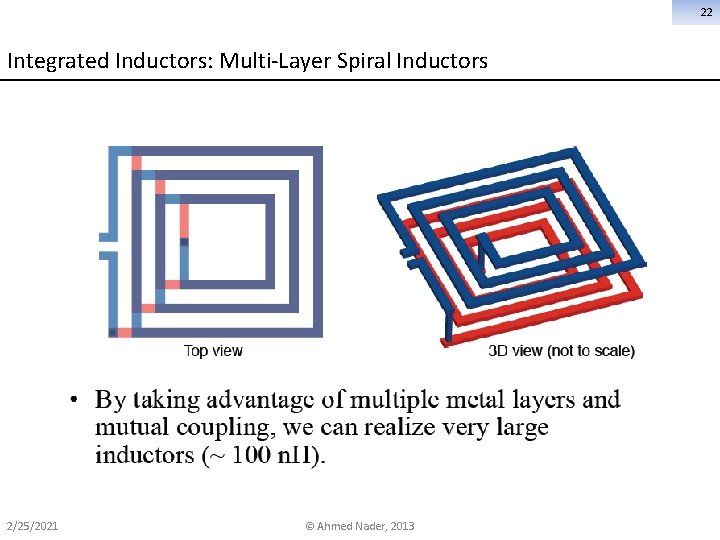

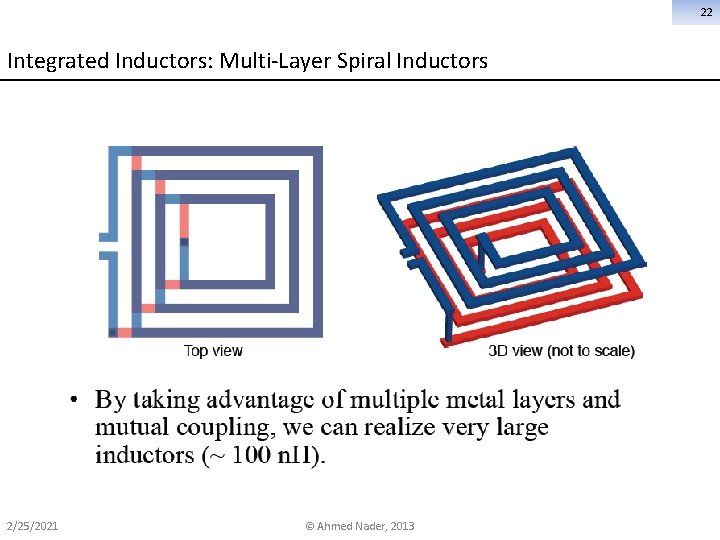

22 Integrated Inductors: Multi-Layer Spiral Inductors 2/25/2021 © Ahmed Nader, 2013

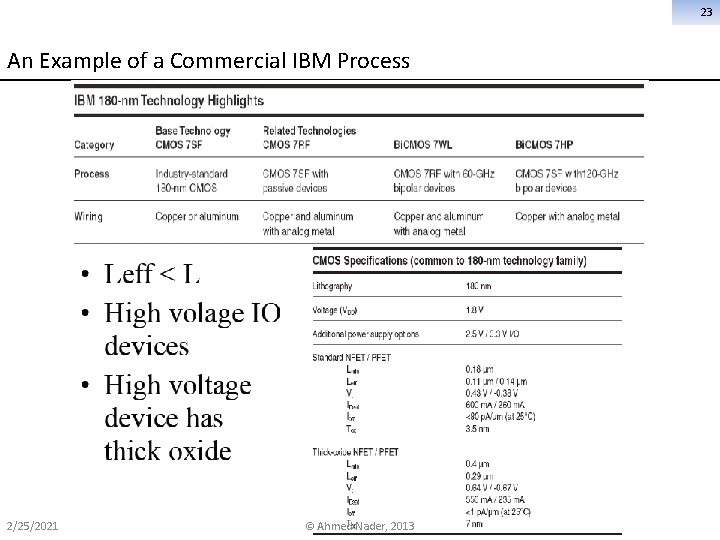

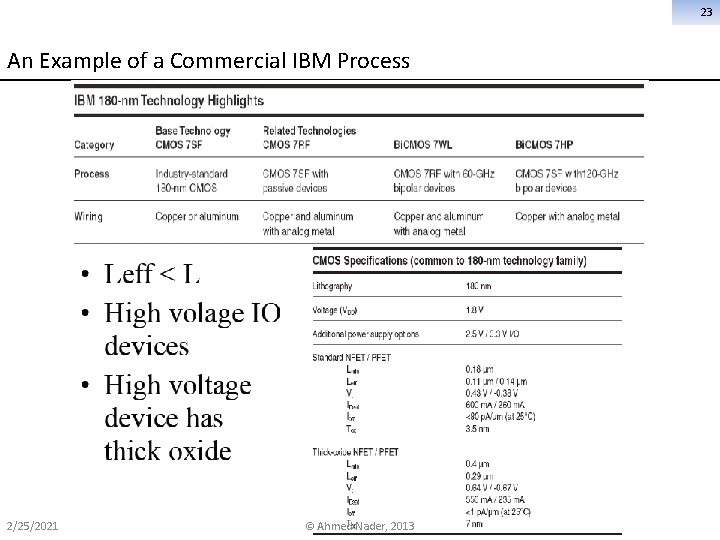

23 An Example of a Commercial IBM Process 2/25/2021 © Ahmed Nader, 2013

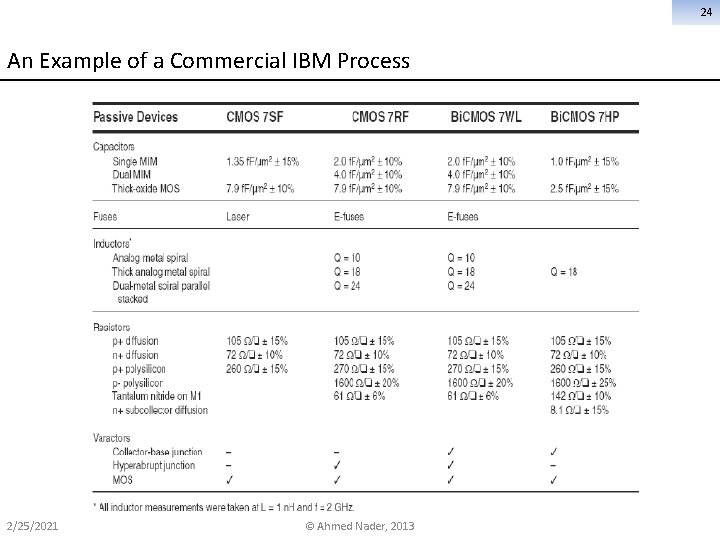

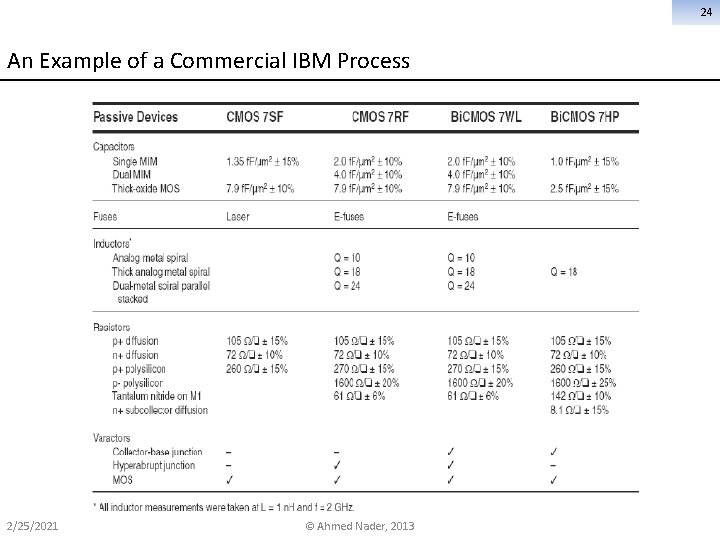

24 An Example of a Commercial IBM Process 2/25/2021 © Ahmed Nader, 2013

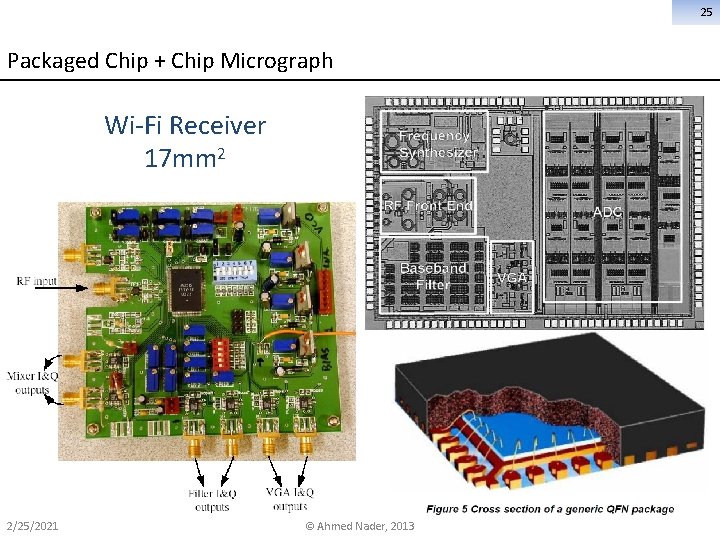

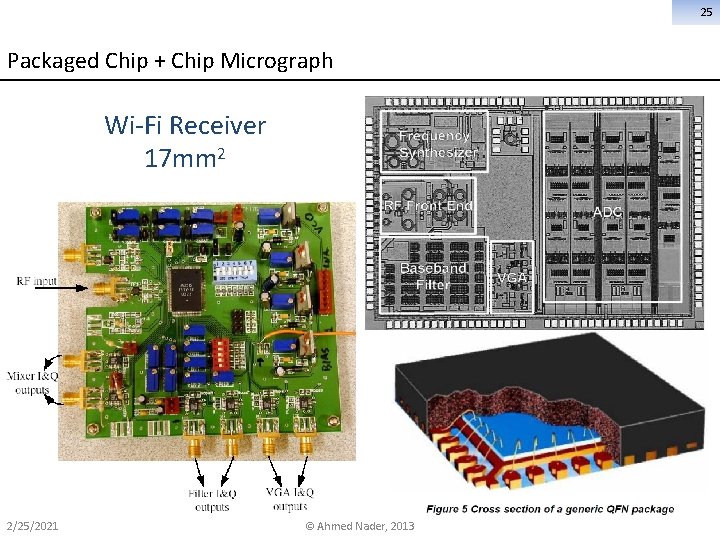

25 Packaged Chip + Chip Micrograph Wi-Fi Receiver 17 mm 2 2/25/2021 © Ahmed Nader, 2013

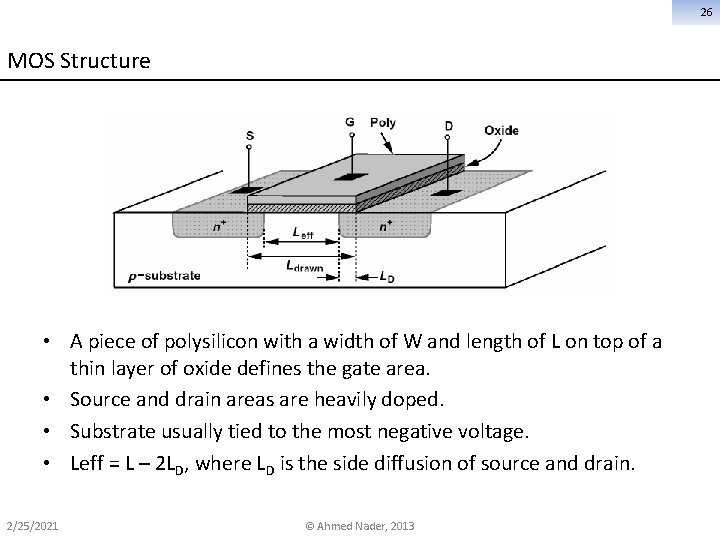

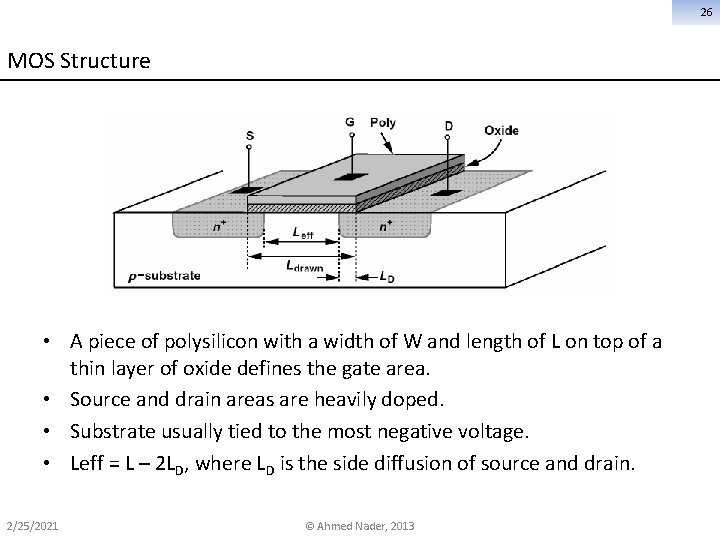

26 MOS Structure • A piece of polysilicon with a width of W and length of L on top of a thin layer of oxide defines the gate area. • Source and drain areas are heavily doped. • Substrate usually tied to the most negative voltage. • Leff = L – 2 LD, where LD is the side diffusion of source and drain. 2/25/2021 © Ahmed Nader, 2013

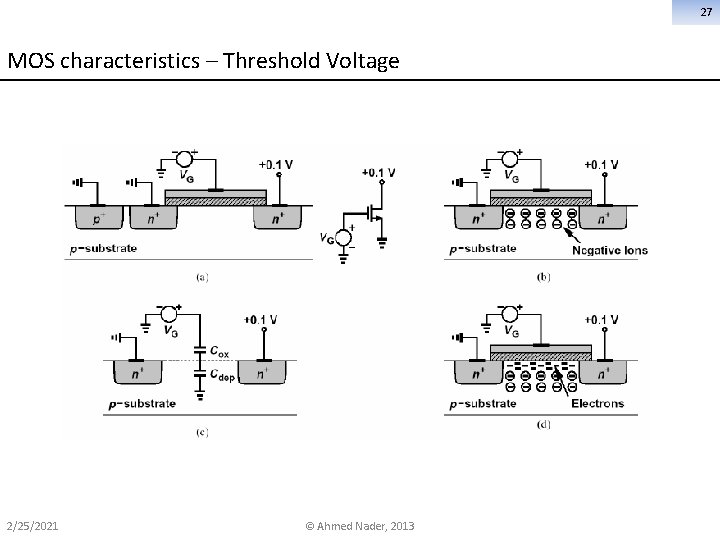

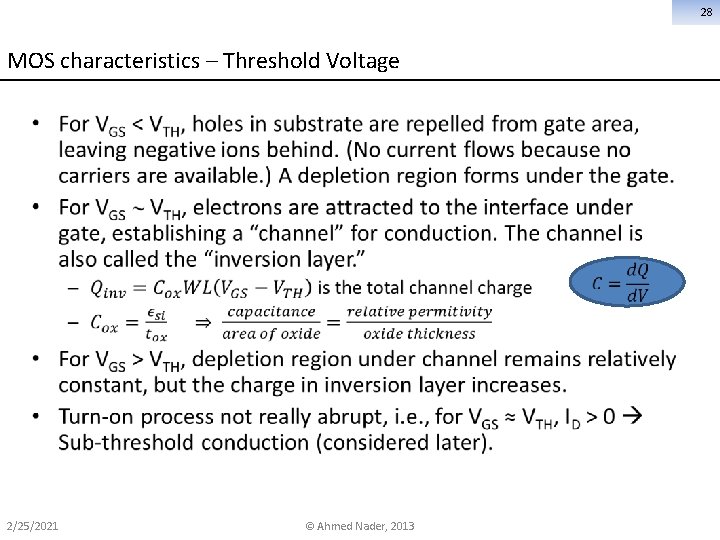

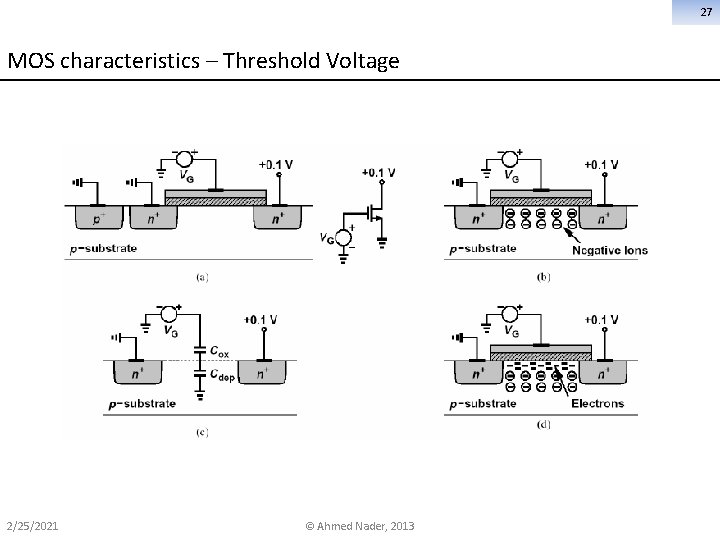

27 MOS characteristics – Threshold Voltage 2/25/2021 © Ahmed Nader, 2013

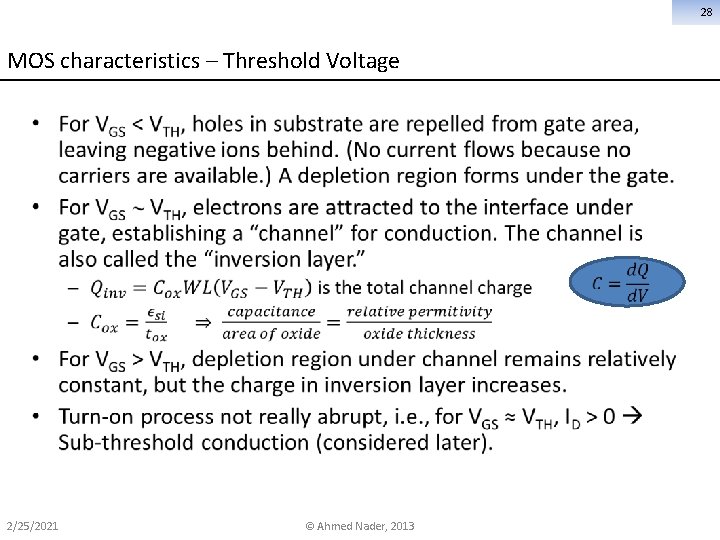

28 MOS characteristics – Threshold Voltage • 2/25/2021 © Ahmed Nader, 2013

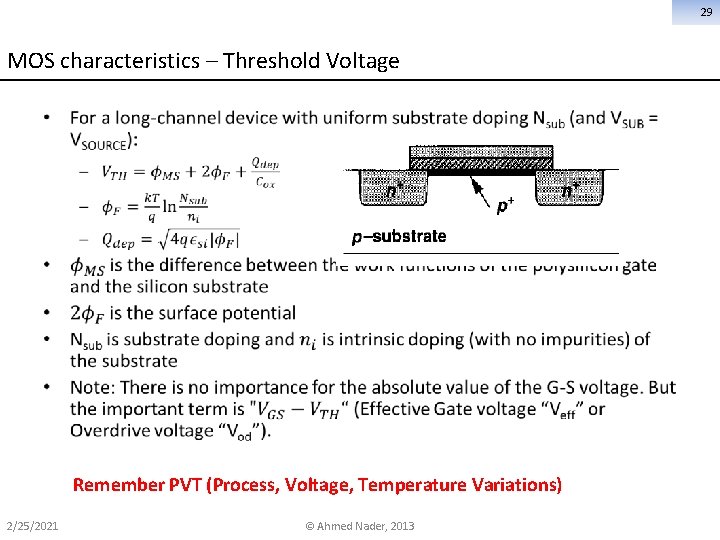

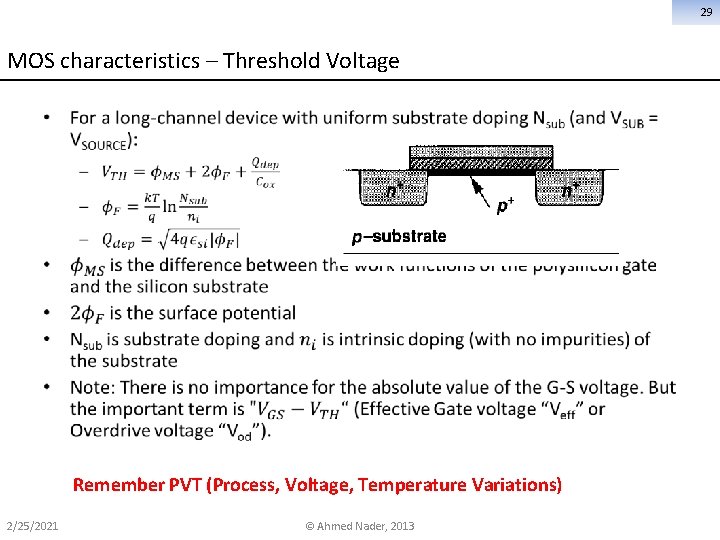

29 MOS characteristics – Threshold Voltage • Remember PVT (Process, Voltage, Temperature Variations) 2/25/2021 © Ahmed Nader, 2013

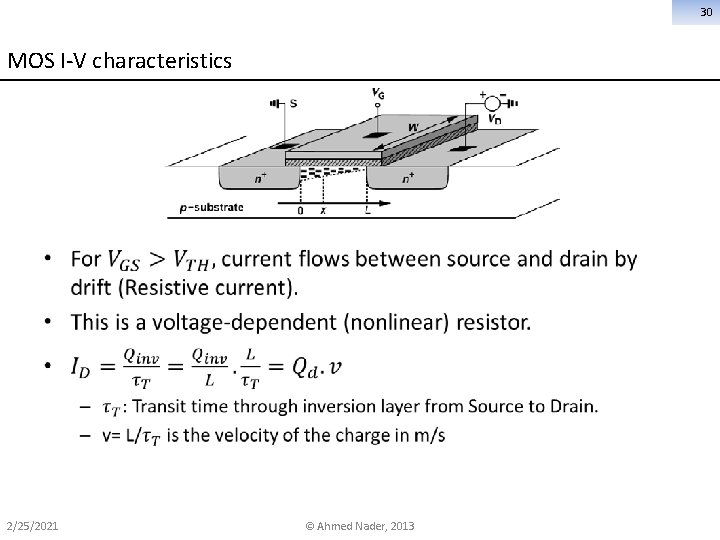

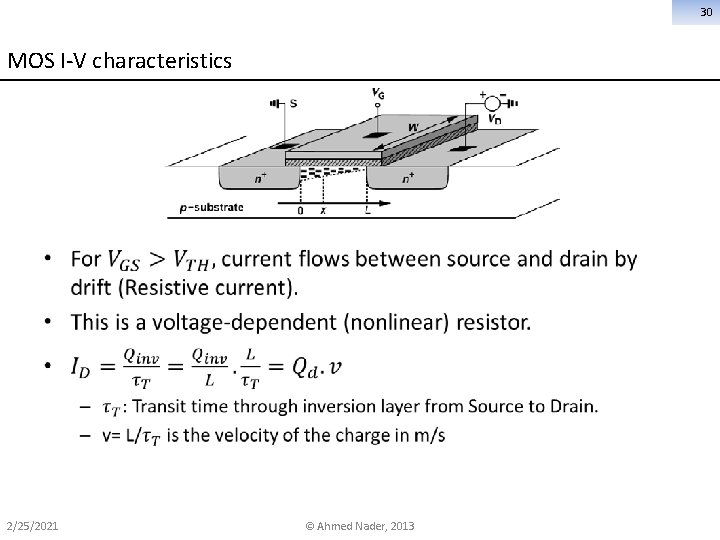

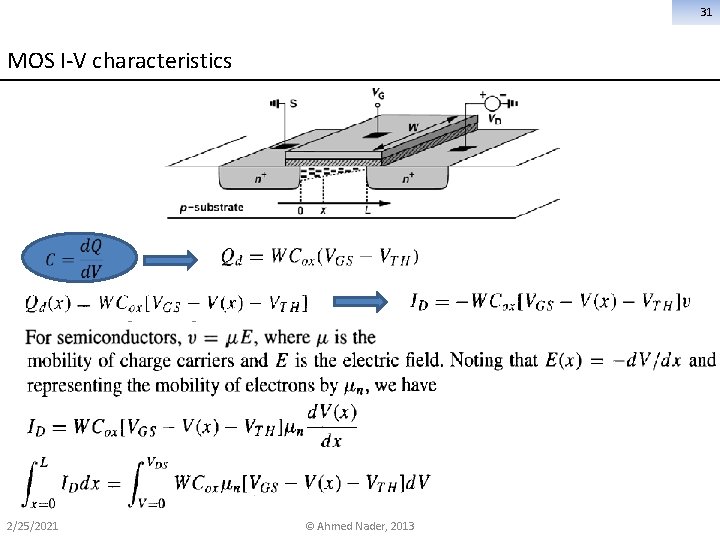

30 MOS I-V characteristics • 2/25/2021 © Ahmed Nader, 2013

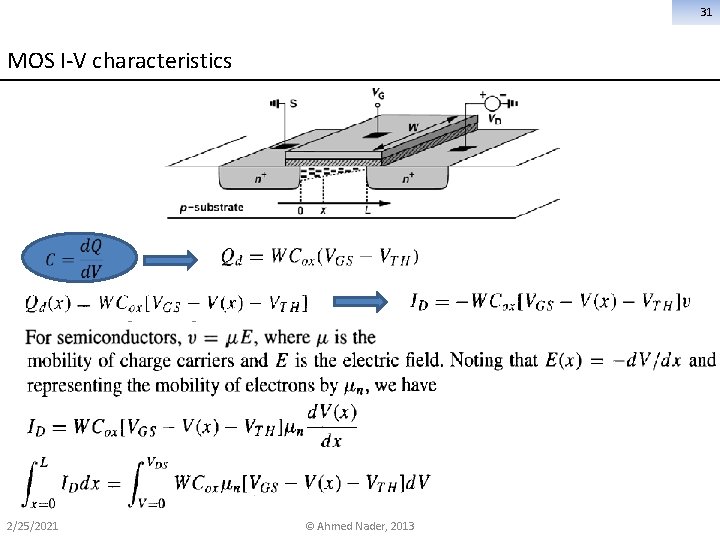

31 MOS I-V characteristics 2/25/2021 © Ahmed Nader, 2013

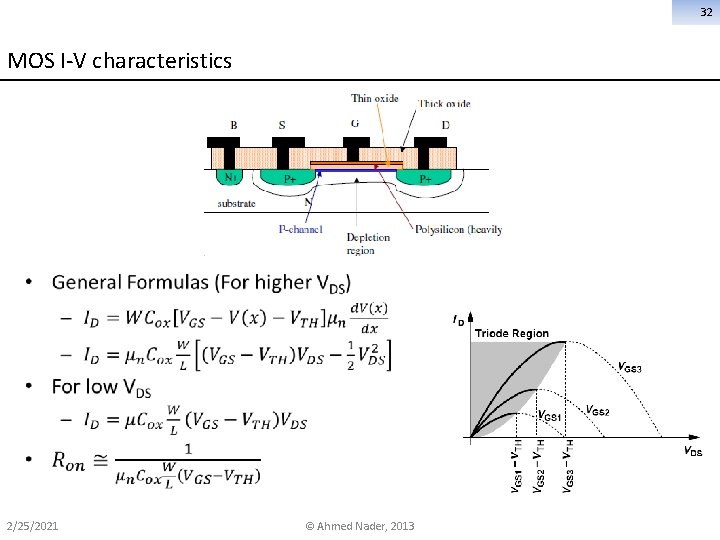

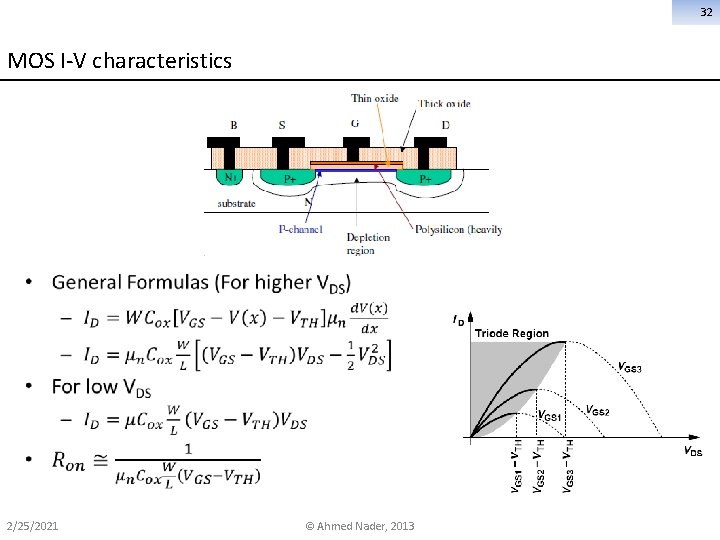

32 MOS I-V characteristics • 2/25/2021 © Ahmed Nader, 2013

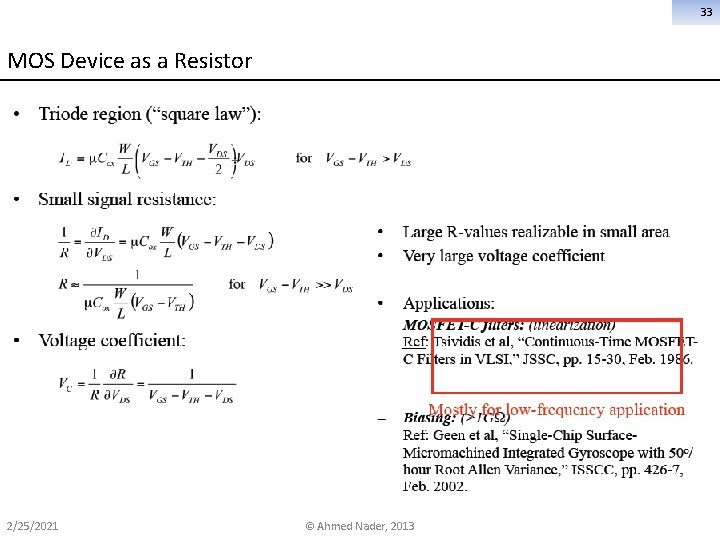

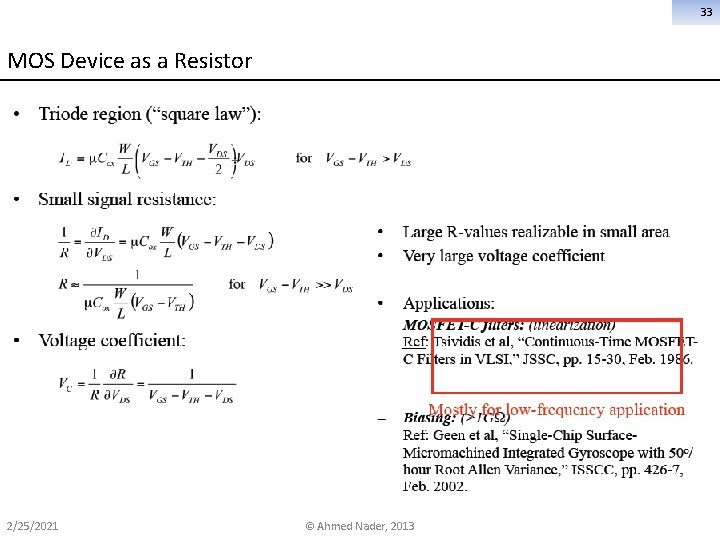

33 MOS Device as a Resistor 2/25/2021 © Ahmed Nader, 2013

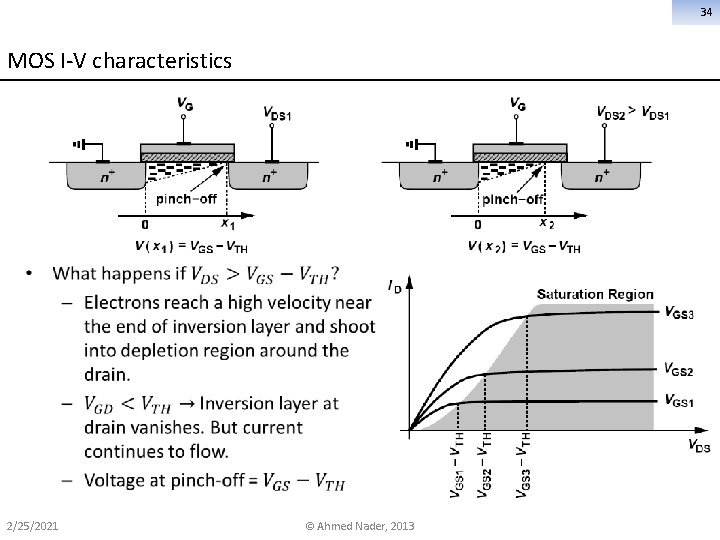

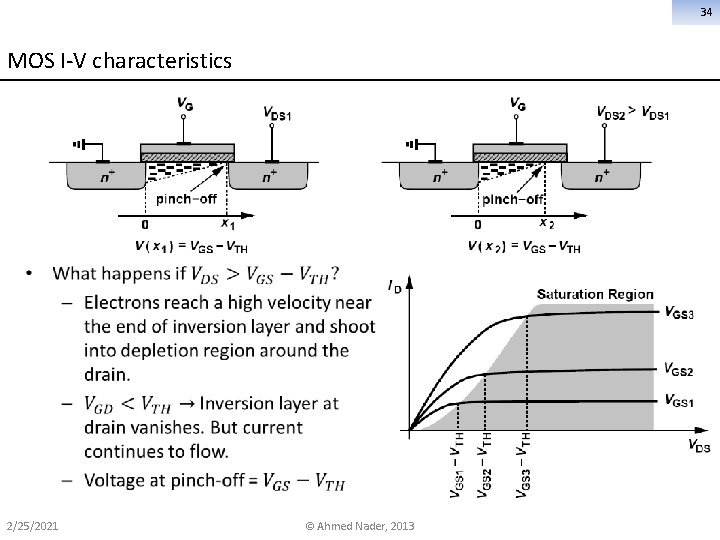

34 MOS I-V characteristics • 2/25/2021 © Ahmed Nader, 2013

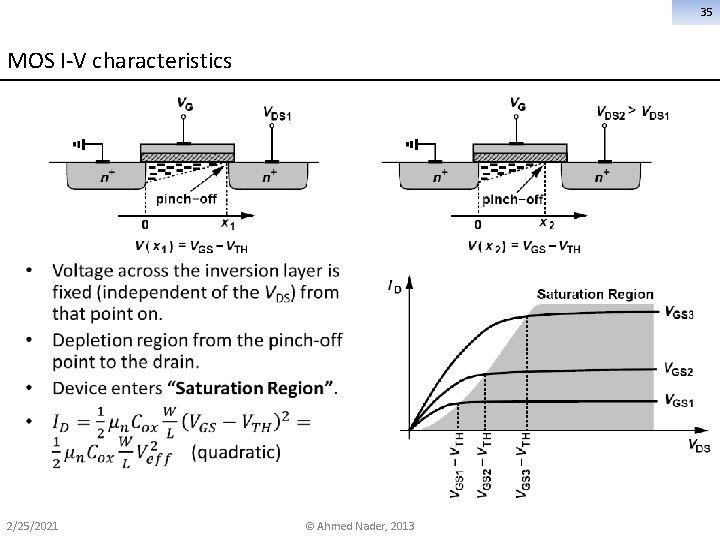

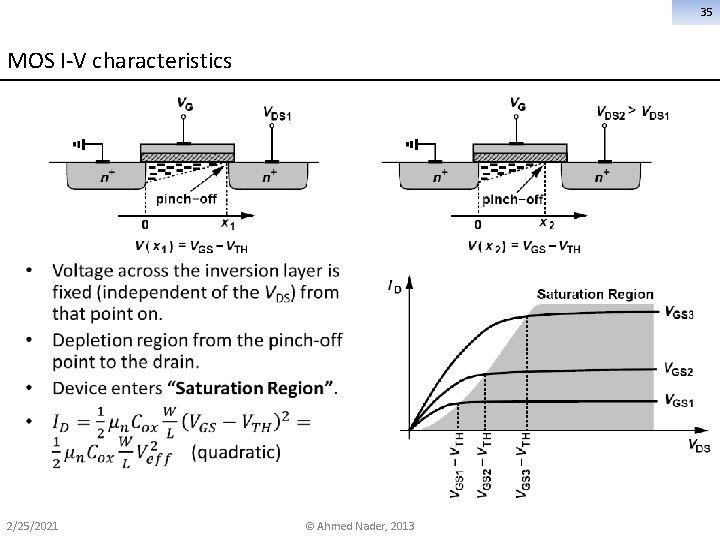

35 MOS I-V characteristics • 2/25/2021 © Ahmed Nader, 2013

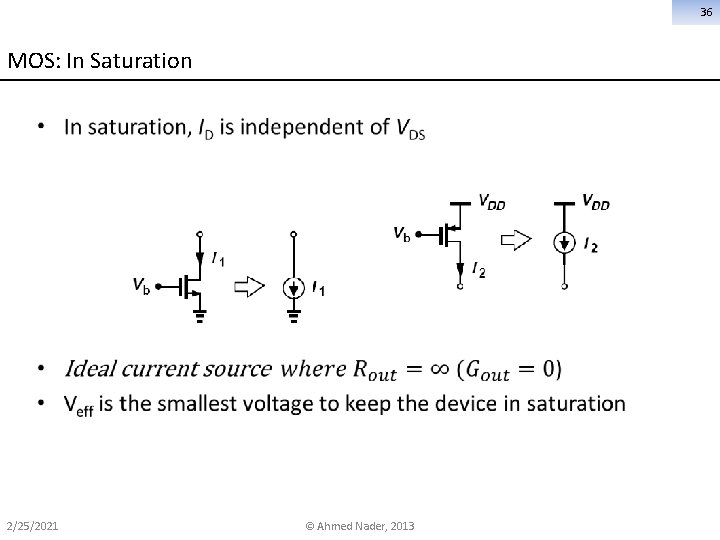

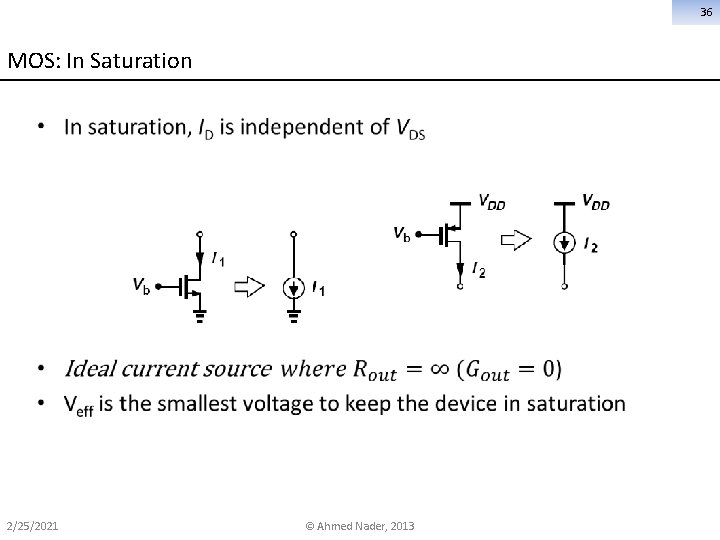

36 MOS: In Saturation • 2/25/2021 © Ahmed Nader, 2013

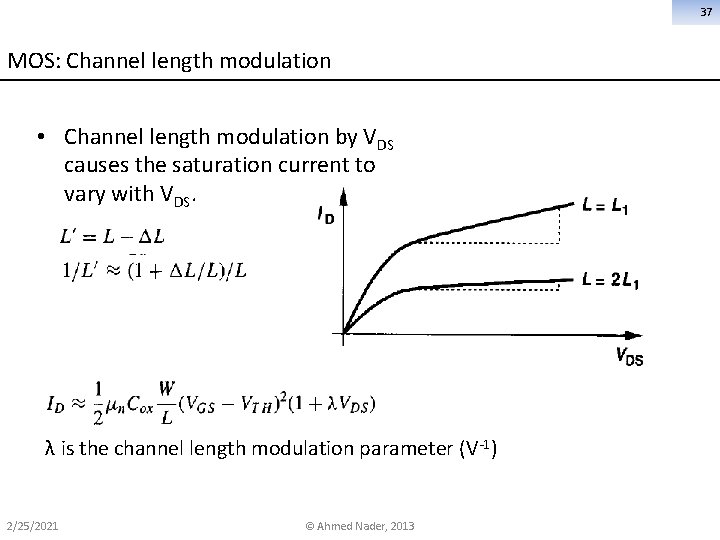

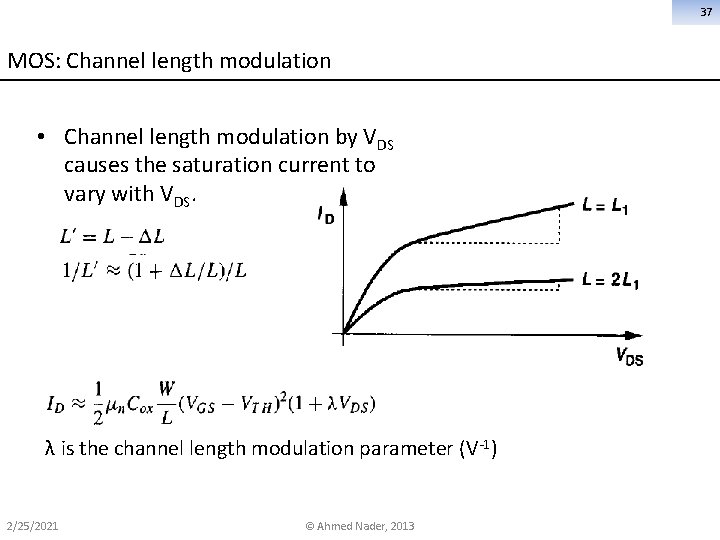

37 MOS: Channel length modulation • Channel length modulation by VDS causes the saturation current to vary with VDS. λ is the channel length modulation parameter (V-1) 2/25/2021 © Ahmed Nader, 2013

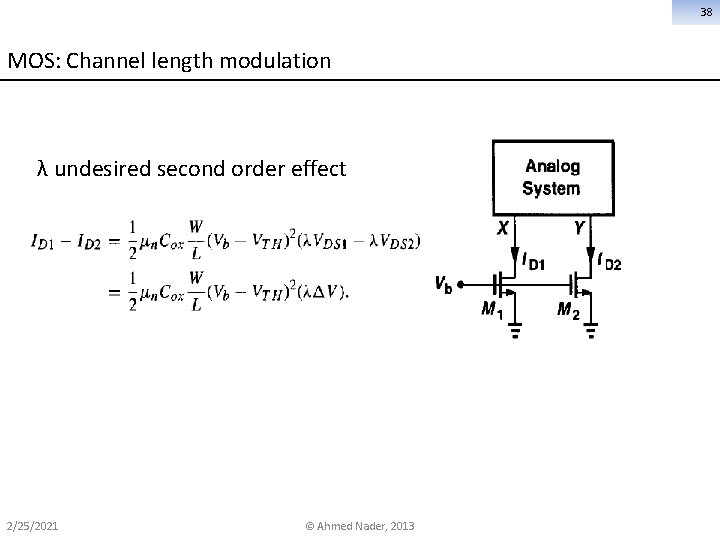

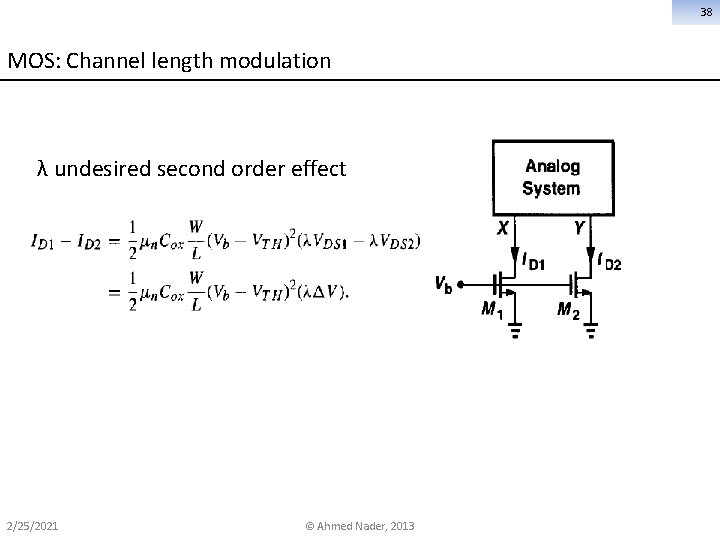

38 MOS: Channel length modulation λ undesired second order effect 2/25/2021 © Ahmed Nader, 2013

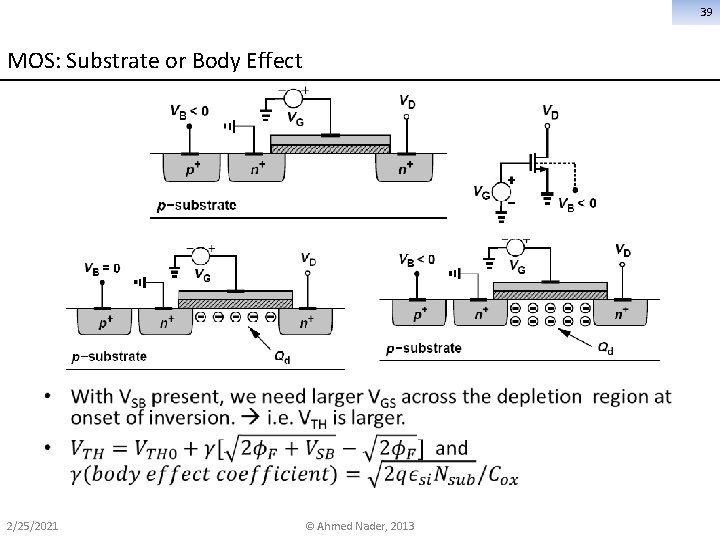

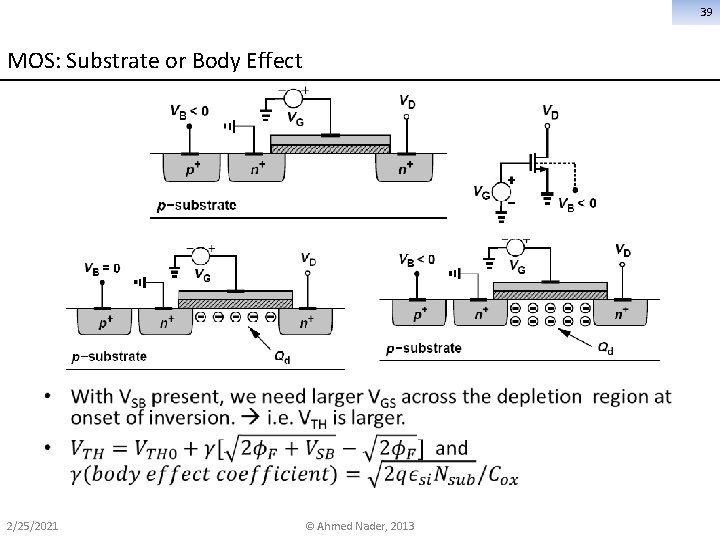

39 MOS: Substrate or Body Effect • 2/25/2021 © Ahmed Nader, 2013

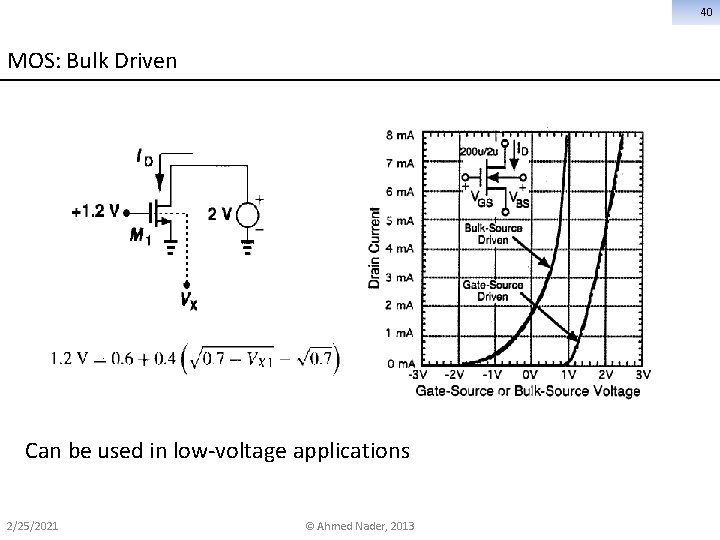

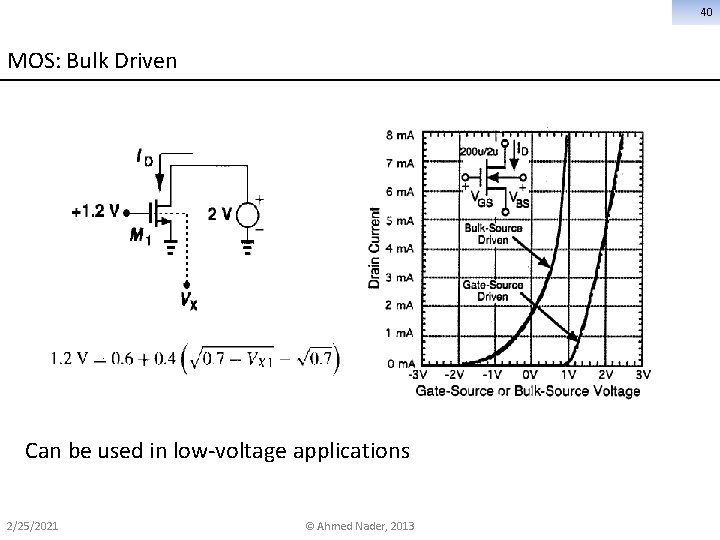

40 MOS: Bulk Driven Can be used in low-voltage applications 2/25/2021 © Ahmed Nader, 2013

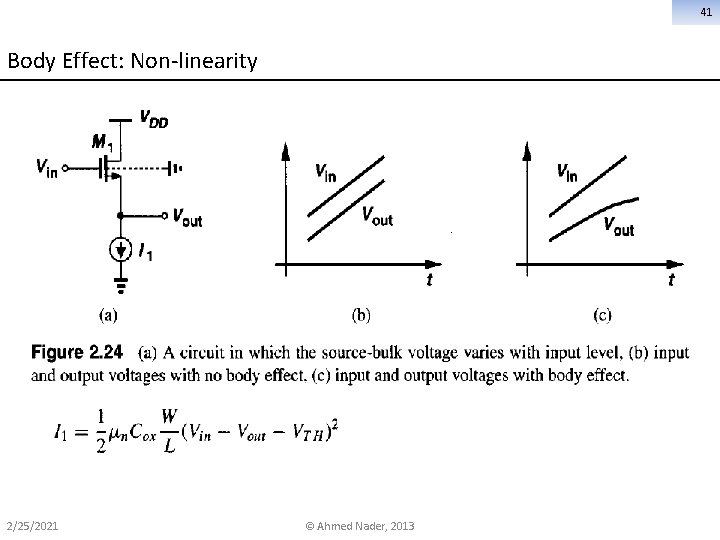

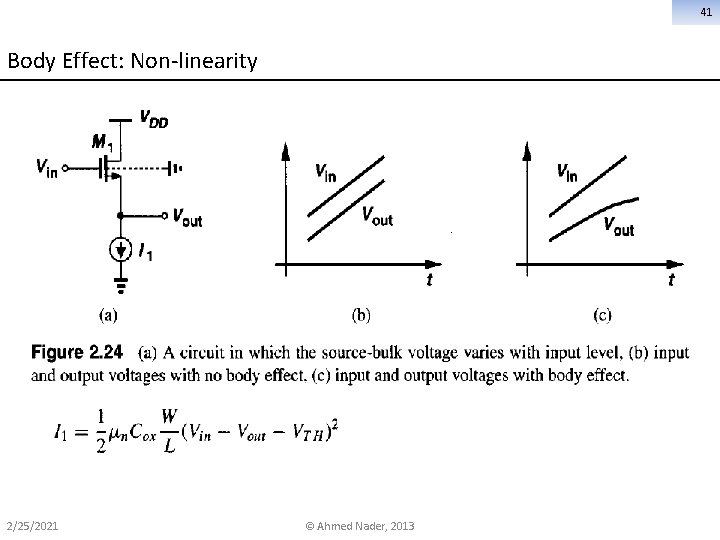

41 Body Effect: Non-linearity 2/25/2021 © Ahmed Nader, 2013

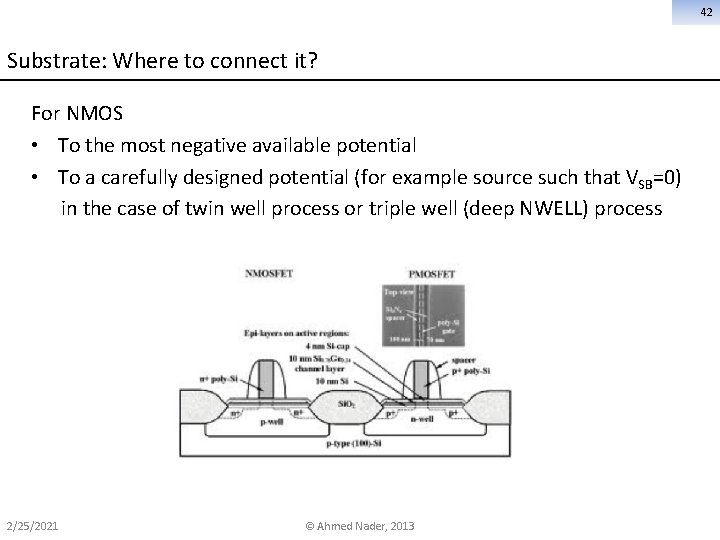

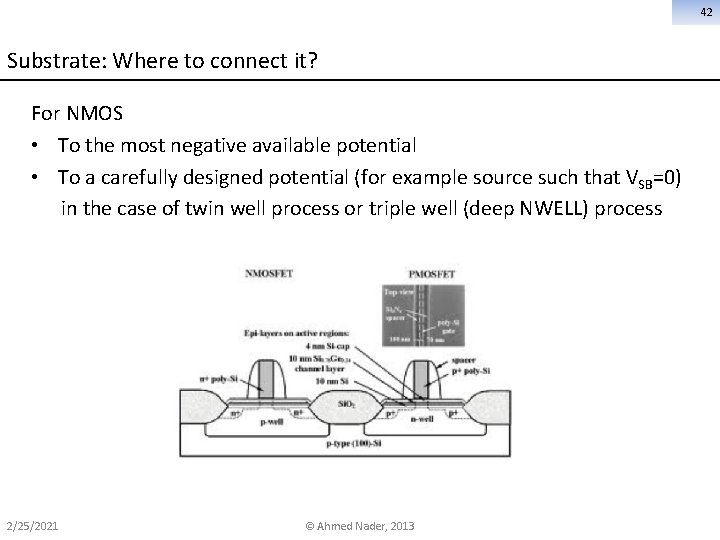

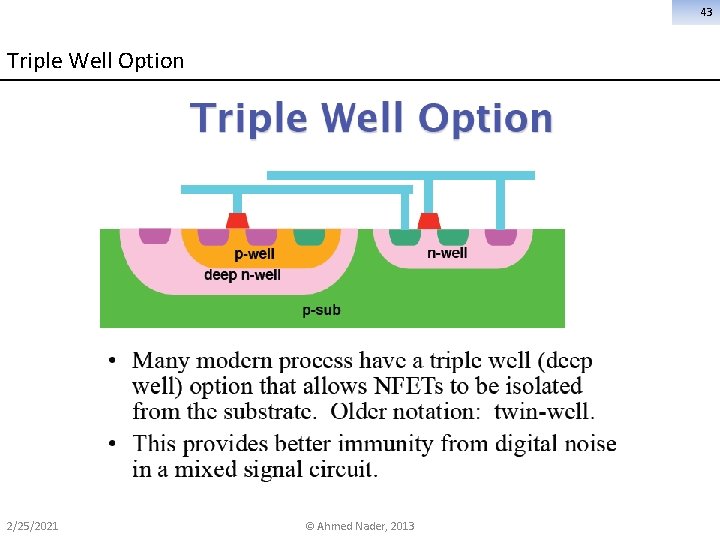

42 Substrate: Where to connect it? For NMOS • To the most negative available potential • To a carefully designed potential (for example source such that VSB=0) in the case of twin well process or triple well (deep NWELL) process 2/25/2021 © Ahmed Nader, 2013

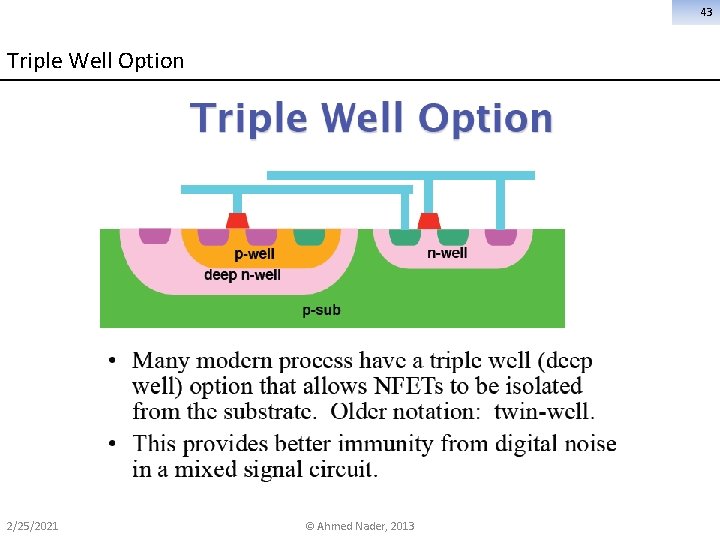

43 Triple Well Option 2/25/2021 © Ahmed Nader, 2013

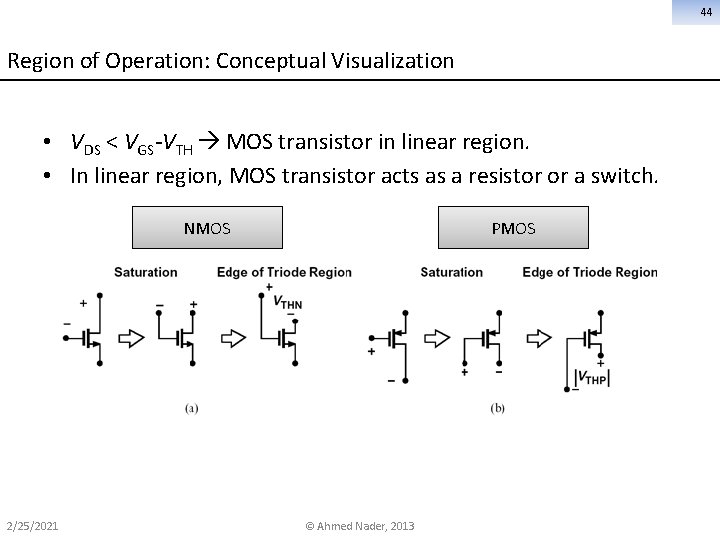

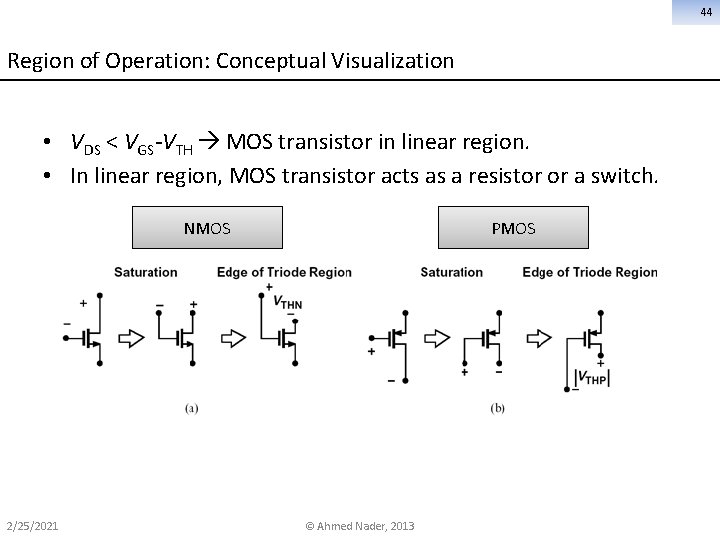

44 Region of Operation: Conceptual Visualization • VDS < VGS-VTH MOS transistor in linear region. • In linear region, MOS transistor acts as a resistor or a switch. NMOS 2/25/2021 PMOS © Ahmed Nader, 2013

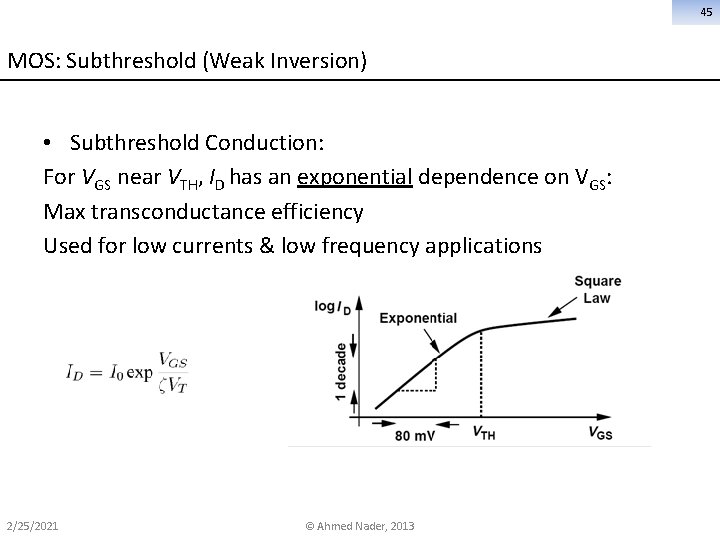

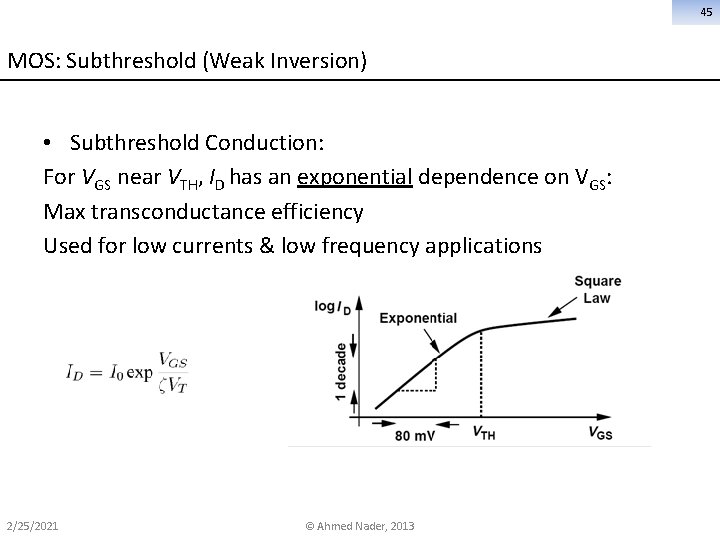

45 MOS: Subthreshold (Weak Inversion) • Subthreshold Conduction: For VGS near VTH, ID has an exponential dependence on VGS: Max transconductance efficiency Used for low currents & low frequency applications 2/25/2021 © Ahmed Nader, 2013

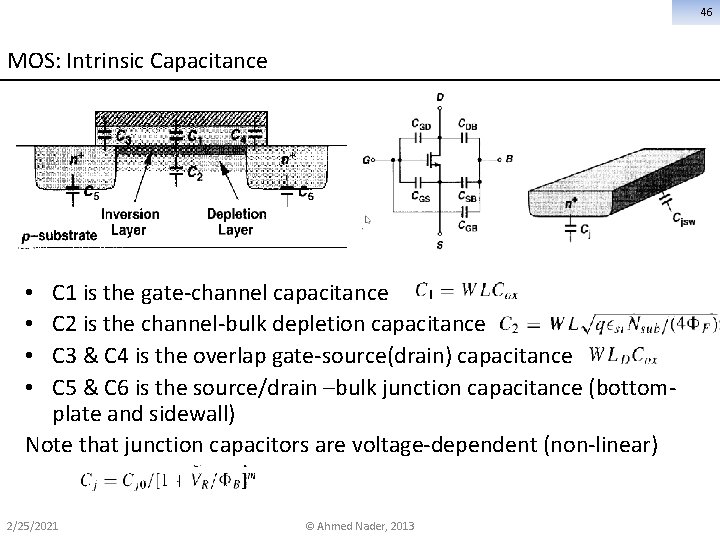

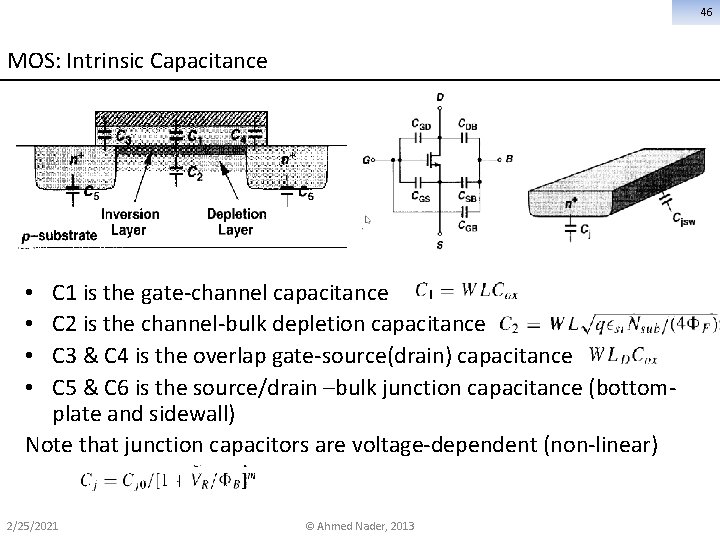

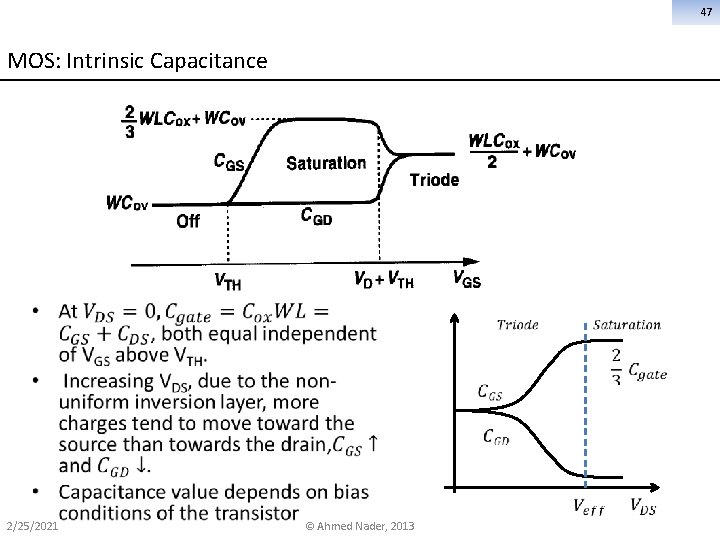

46 MOS: Intrinsic Capacitance C 1 is the gate-channel capacitance C 2 is the channel-bulk depletion capacitance C 3 & C 4 is the overlap gate-source(drain) capacitance C 5 & C 6 is the source/drain –bulk junction capacitance (bottomplate and sidewall) Note that junction capacitors are voltage-dependent (non-linear) • • 2/25/2021 © Ahmed Nader, 2013

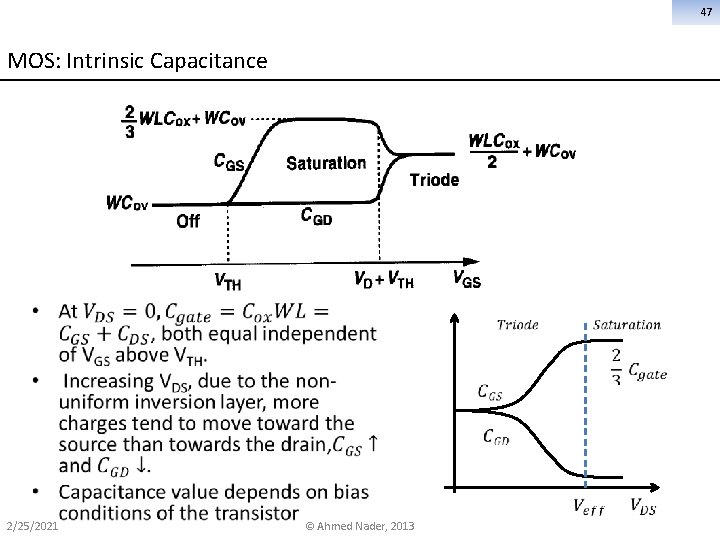

47 MOS: Intrinsic Capacitance • 2/25/2021 © Ahmed Nader, 2013

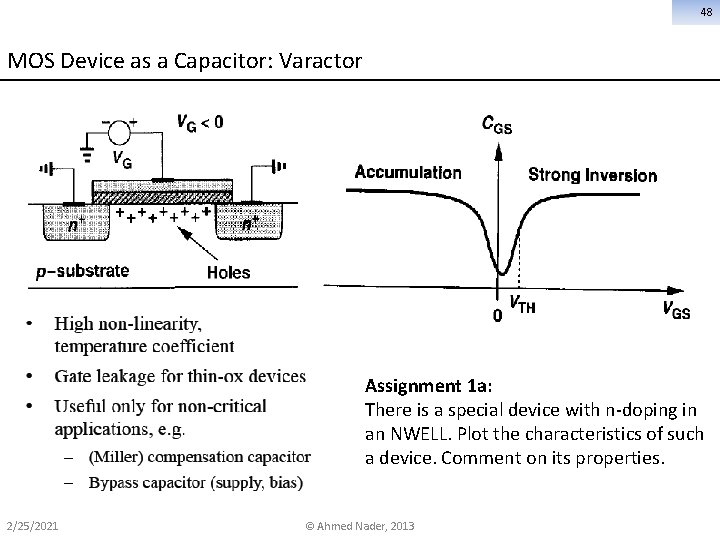

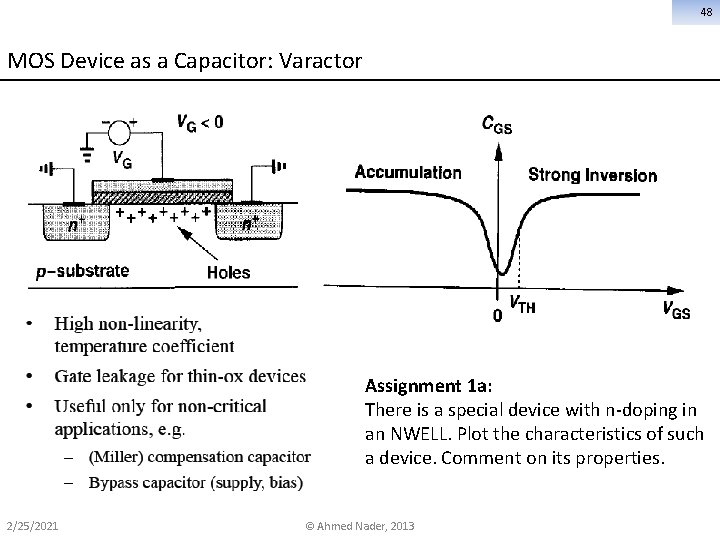

48 MOS Device as a Capacitor: Varactor Assignment 1 a: There is a special device with n-doping in an NWELL. Plot the characteristics of such a device. Comment on its properties. 2/25/2021 © Ahmed Nader, 2013

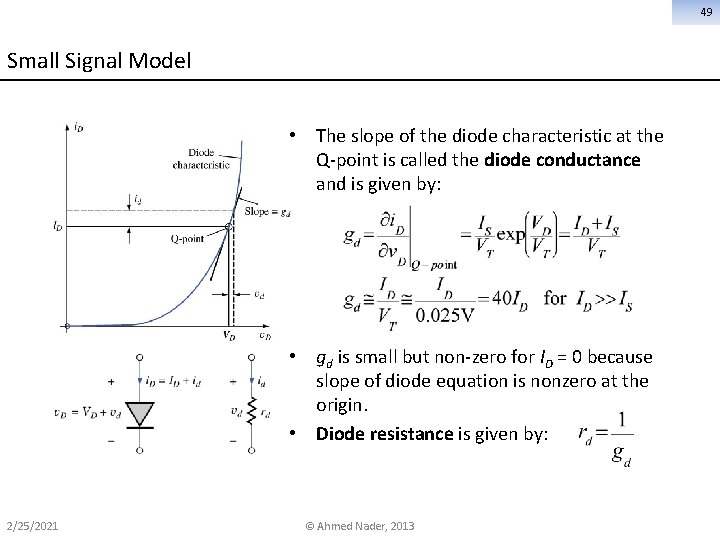

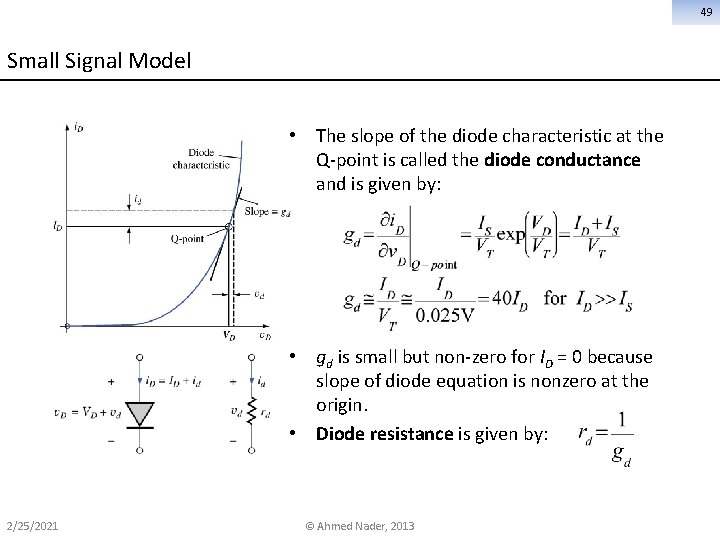

49 Small Signal Model • The slope of the diode characteristic at the Q-point is called the diode conductance and is given by: • gd is small but non-zero for ID = 0 because slope of diode equation is nonzero at the origin. • Diode resistance is given by: 2/25/2021 © Ahmed Nader, 2013

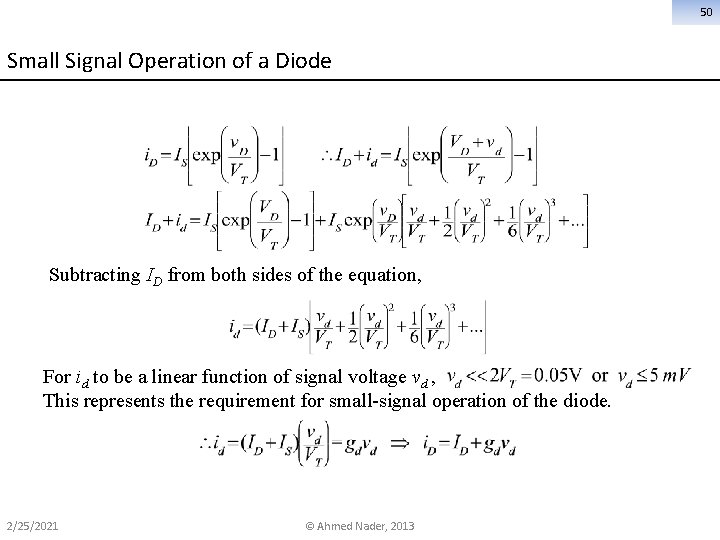

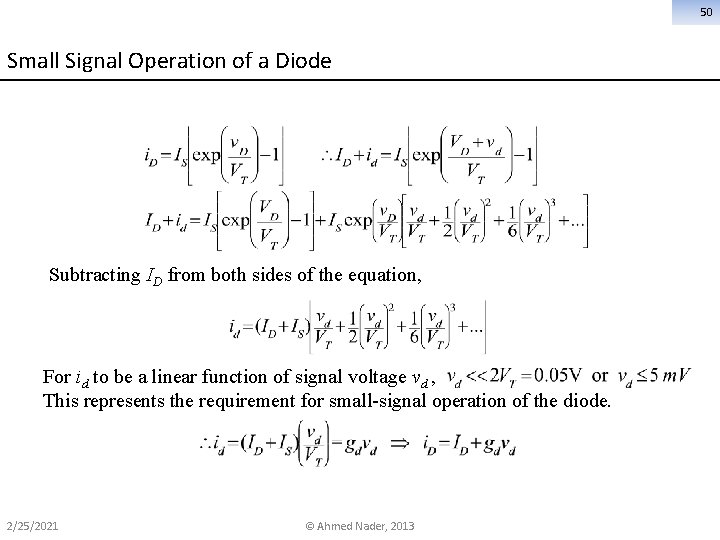

50 Small Signal Operation of a Diode Subtracting ID from both sides of the equation, For id to be a linear function of signal voltage vd , This represents the requirement for small-signal operation of the diode. 2/25/2021 © Ahmed Nader, 2013

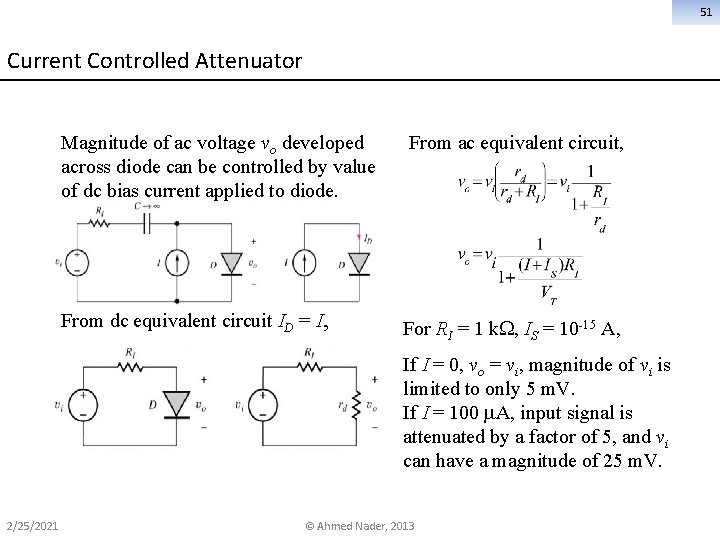

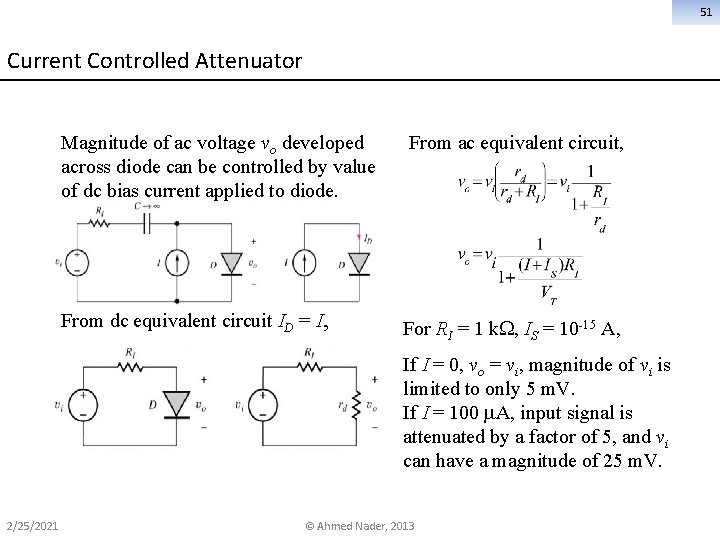

51 Current Controlled Attenuator Magnitude of ac voltage vo developed across diode can be controlled by value of dc bias current applied to diode. From dc equivalent circuit ID = I, From ac equivalent circuit, For RI = 1 k. W, IS = 10 -15 A, If I = 0, vo = vi, magnitude of vi is limited to only 5 m. V. If I = 100 m. A, input signal is attenuated by a factor of 5, and vi can have a magnitude of 25 m. V. 2/25/2021 © Ahmed Nader, 2013

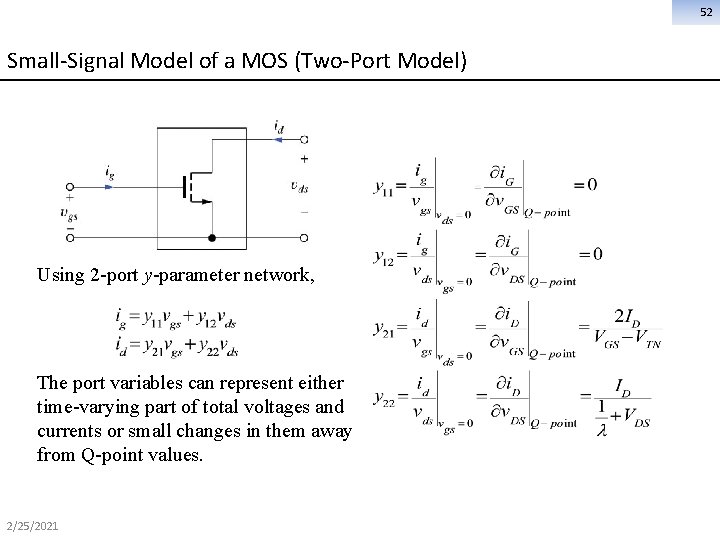

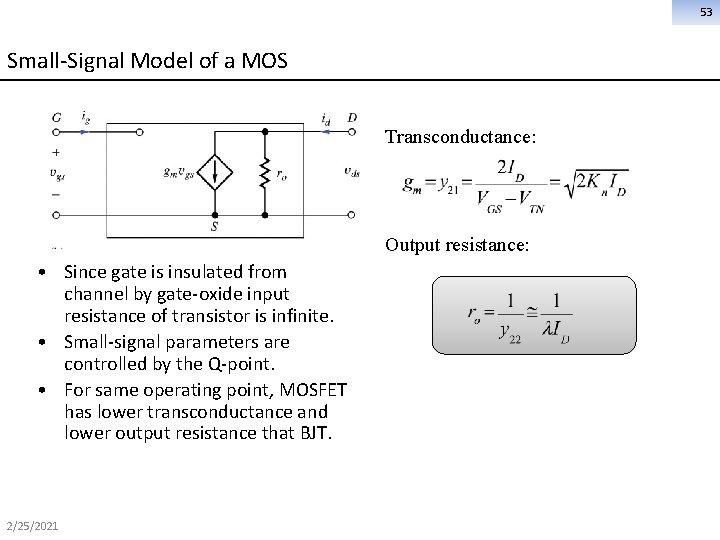

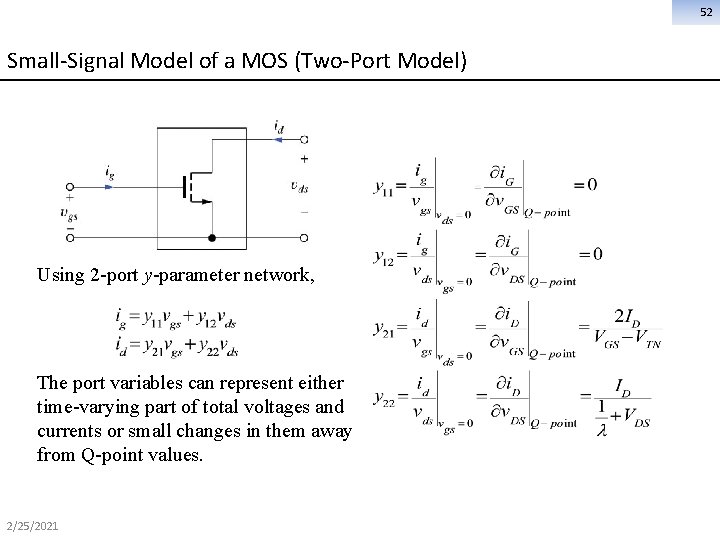

52 Small-Signal Model of a MOS (Two-Port Model) Using 2 -port y-parameter network, The port variables can represent either time-varying part of total voltages and currents or small changes in them away from Q-point values. 2/25/2021

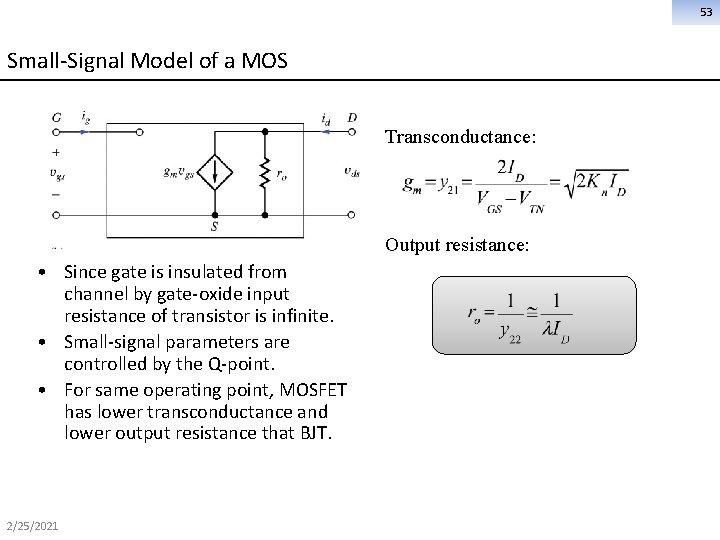

53 Small-Signal Model of a MOS Transconductance: Output resistance: • Since gate is insulated from channel by gate-oxide input resistance of transistor is infinite. • Small-signal parameters are controlled by the Q-point. • For same operating point, MOSFET has lower transconductance and lower output resistance that BJT. 2/25/2021

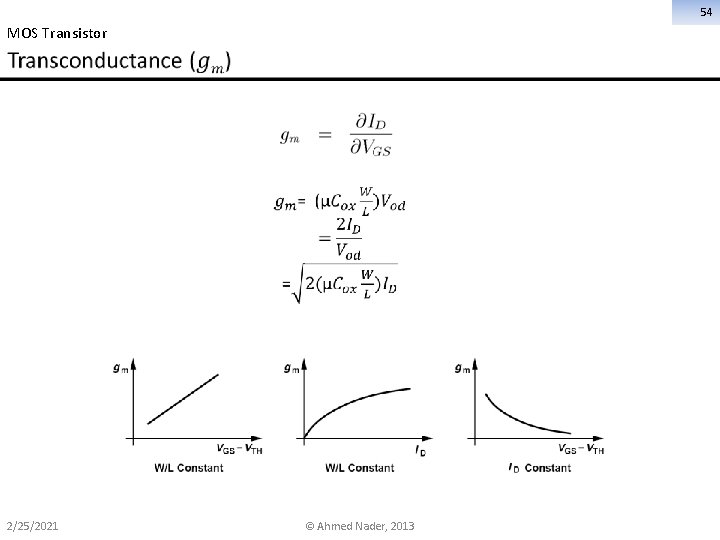

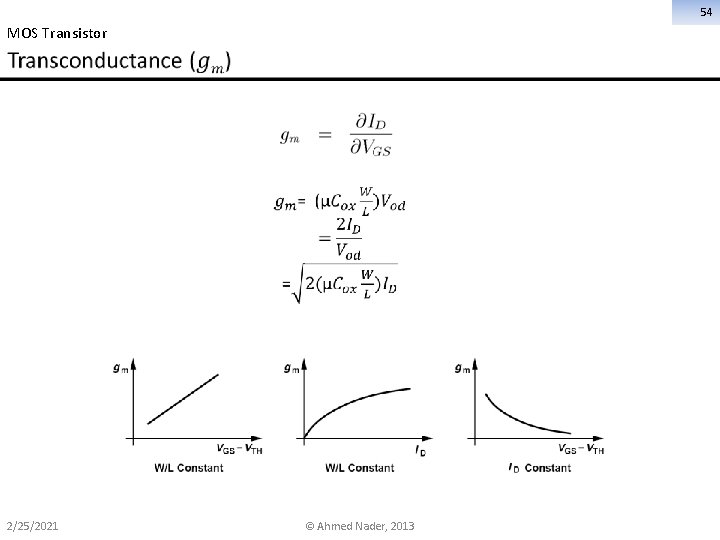

54 MOS Transistor 2/25/2021 © Ahmed Nader, 2013

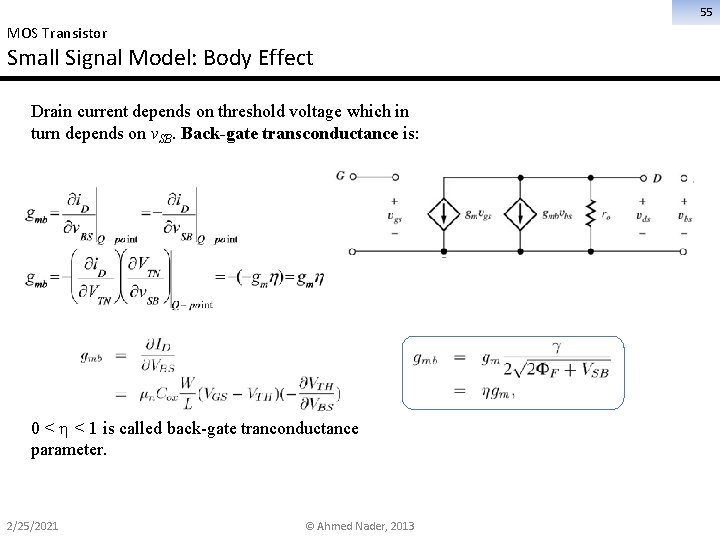

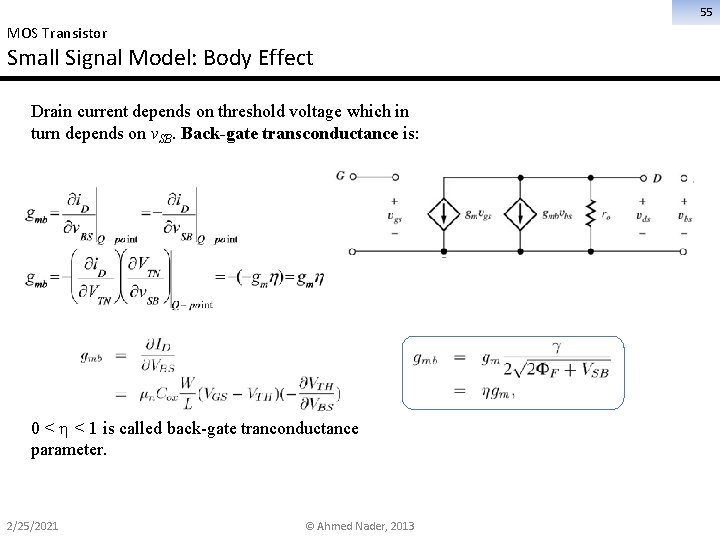

55 MOS Transistor Small Signal Model: Body Effect Drain current depends on threshold voltage which in turn depends on v. SB. Back-gate transconductance is: 0 < < 1 is called back-gate tranconductance parameter. 2/25/2021 © Ahmed Nader, 2013

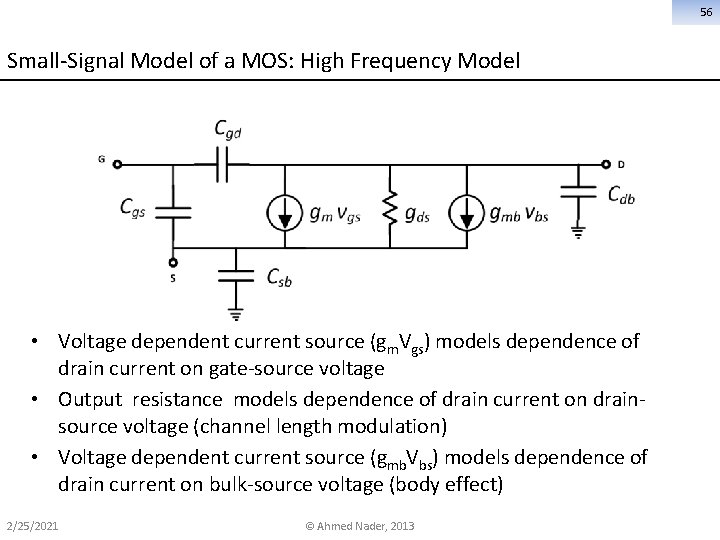

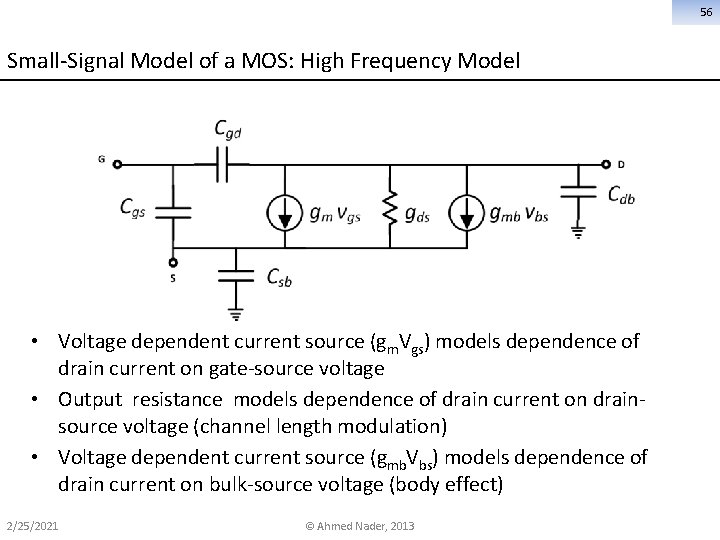

56 Small-Signal Model of a MOS: High Frequency Model • Voltage dependent current source (gm. Vgs) models dependence of drain current on gate-source voltage • Output resistance models dependence of drain current on drainsource voltage (channel length modulation) • Voltage dependent current source (gmb. Vbs) models dependence of drain current on bulk-source voltage (body effect) 2/25/2021 © Ahmed Nader, 2013

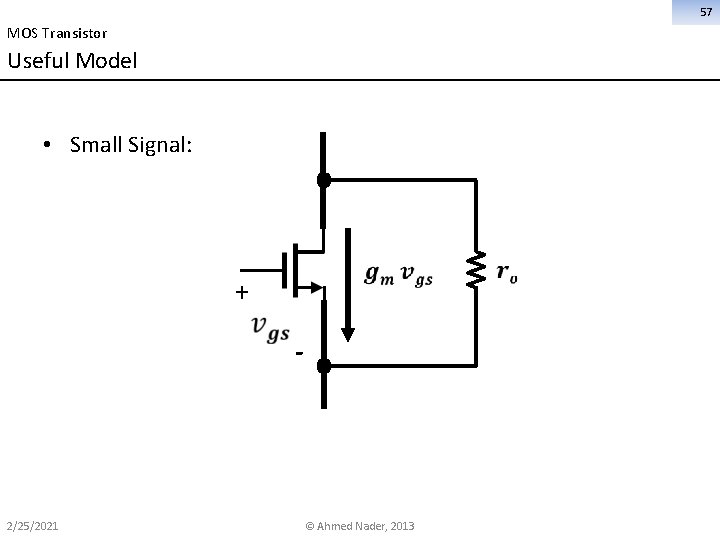

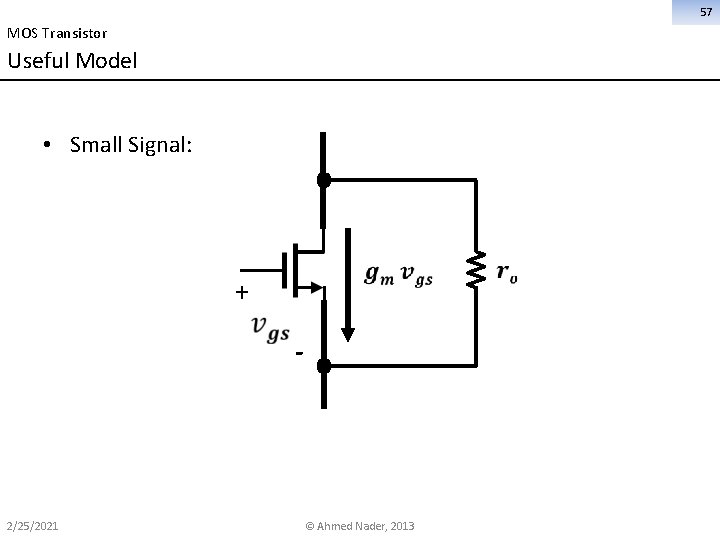

57 MOS Transistor Useful Model • Small Signal: + - 2/25/2021 © Ahmed Nader, 2013

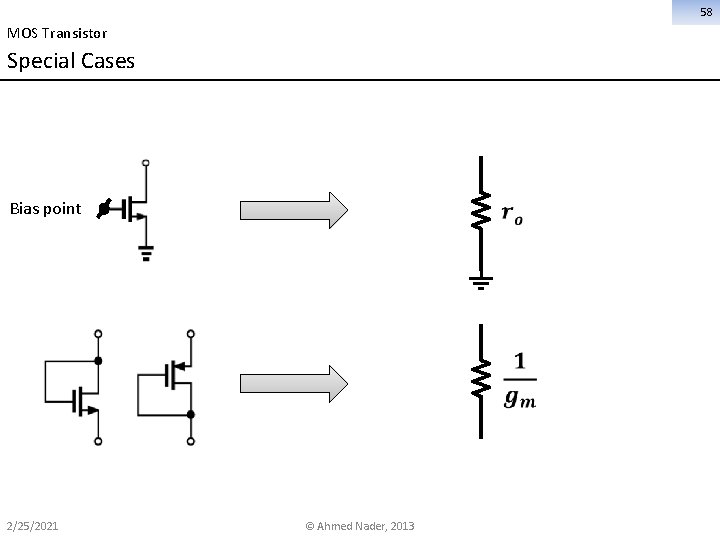

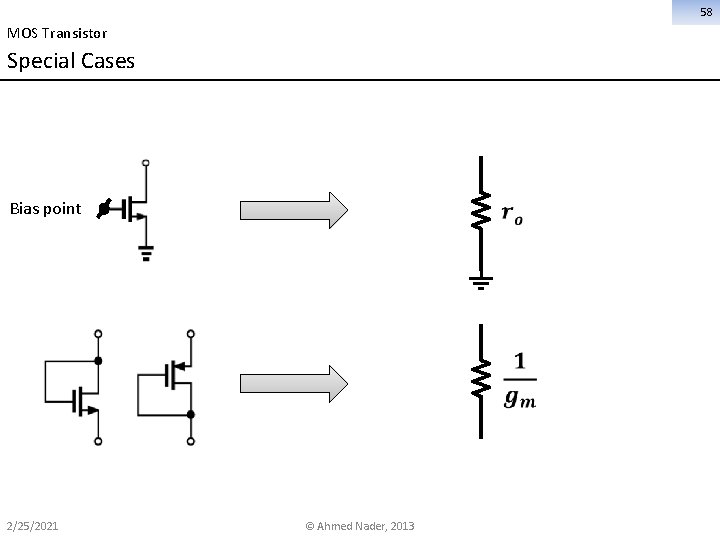

58 MOS Transistor Special Cases Bias point 2/25/2021 © Ahmed Nader, 2013

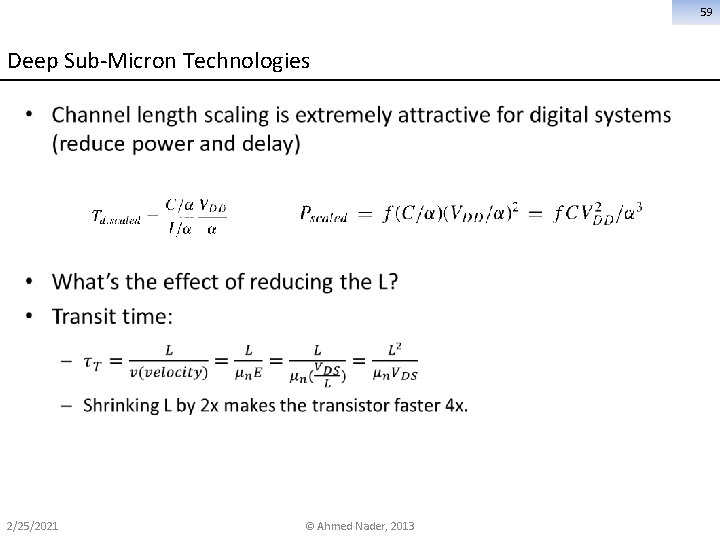

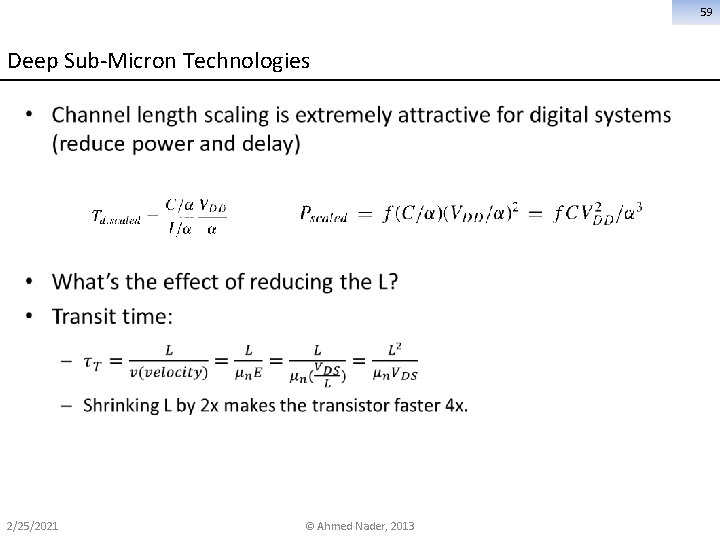

59 Deep Sub-Micron Technologies • 2/25/2021 © Ahmed Nader, 2013

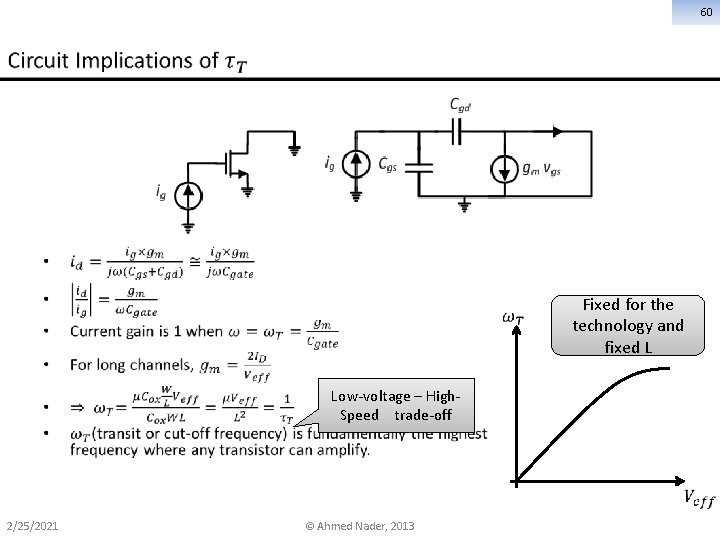

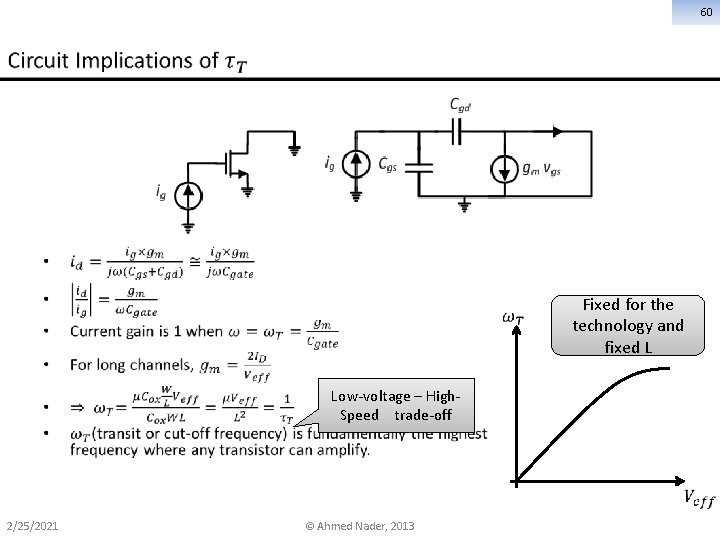

60 • Fixed for the technology and fixed L Low-voltage – High. Speed trade-off 2/25/2021 © Ahmed Nader, 2013

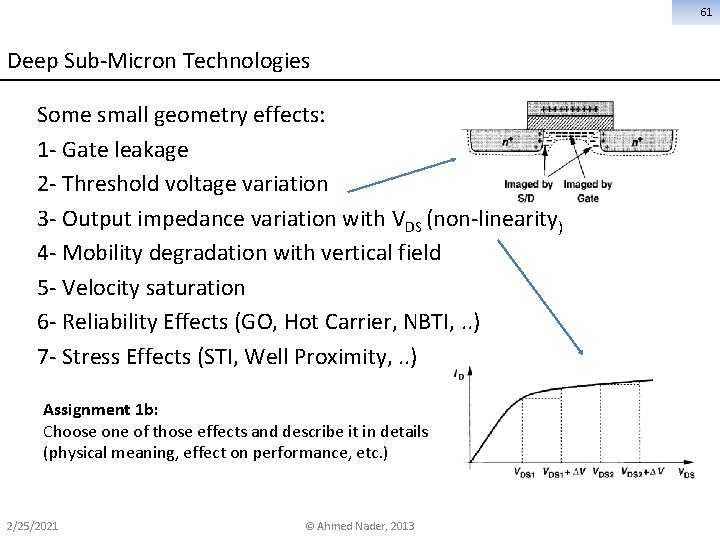

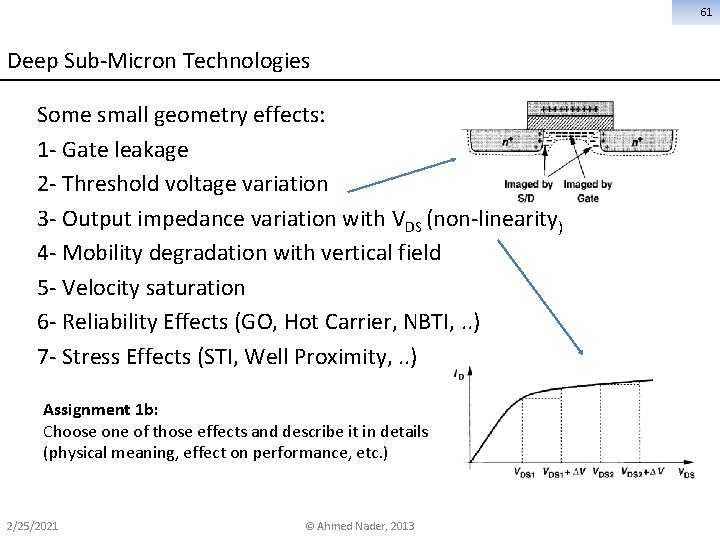

61 Deep Sub-Micron Technologies Some small geometry effects: 1 - Gate leakage 2 - Threshold voltage variation 3 - Output impedance variation with VDS (non-linearity) 4 - Mobility degradation with vertical field 5 - Velocity saturation 6 - Reliability Effects (GO, Hot Carrier, NBTI, . . ) 7 - Stress Effects (STI, Well Proximity, . . ) Assignment 1 b: Choose one of those effects and describe it in details (physical meaning, effect on performance, etc. ) 2/25/2021 © Ahmed Nader, 2013

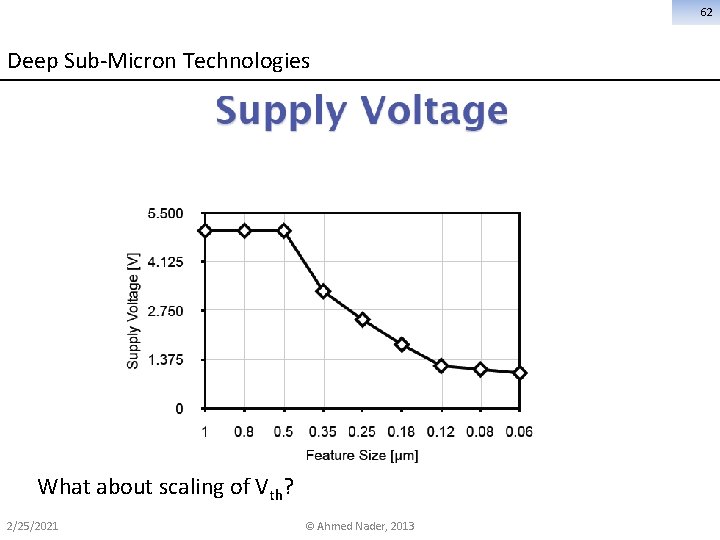

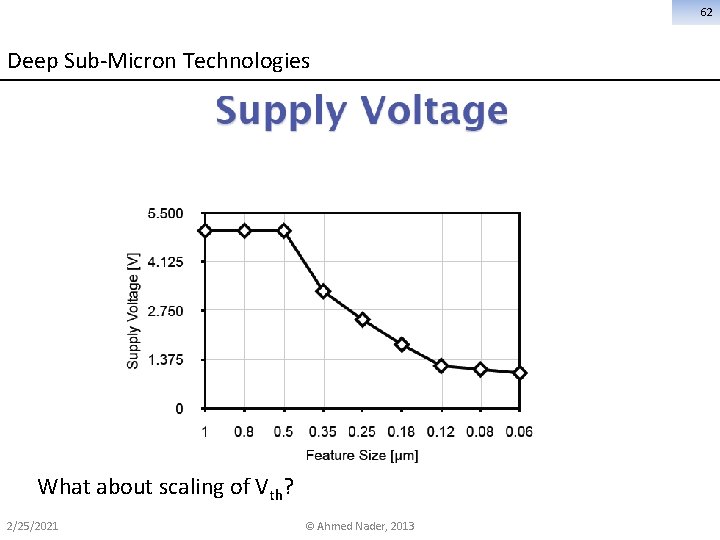

62 Deep Sub-Micron Technologies What about scaling of Vth? 2/25/2021 © Ahmed Nader, 2013

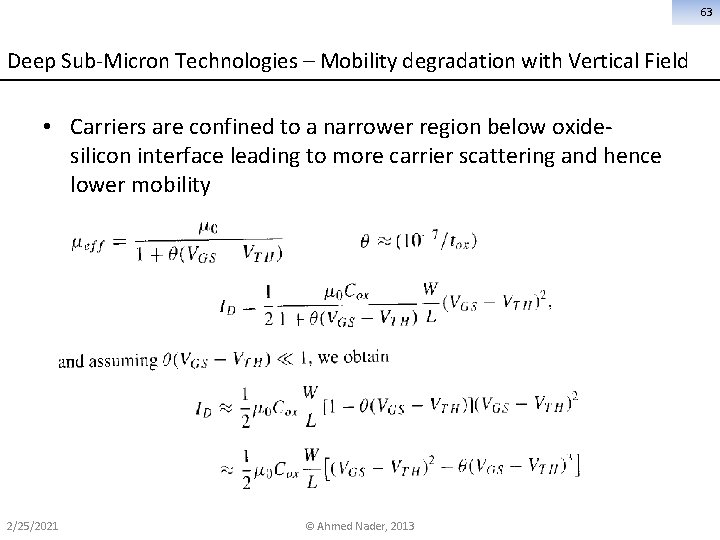

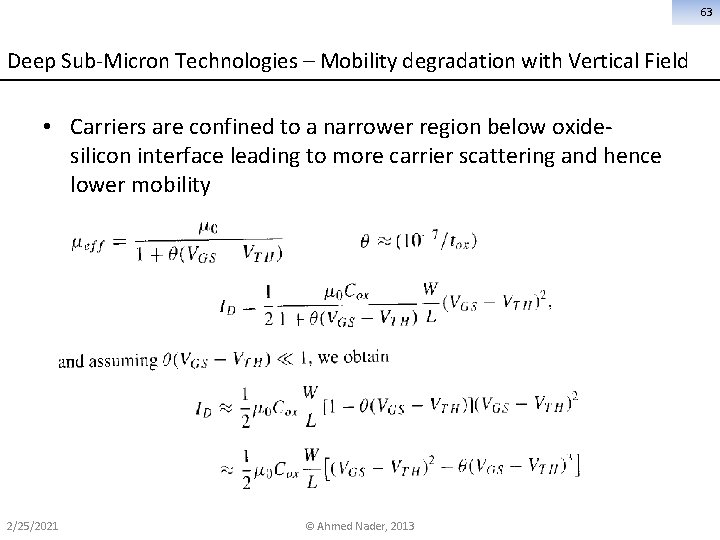

63 Deep Sub-Micron Technologies – Mobility degradation with Vertical Field • Carriers are confined to a narrower region below oxidesilicon interface leading to more carrier scattering and hence lower mobility 2/25/2021 © Ahmed Nader, 2013

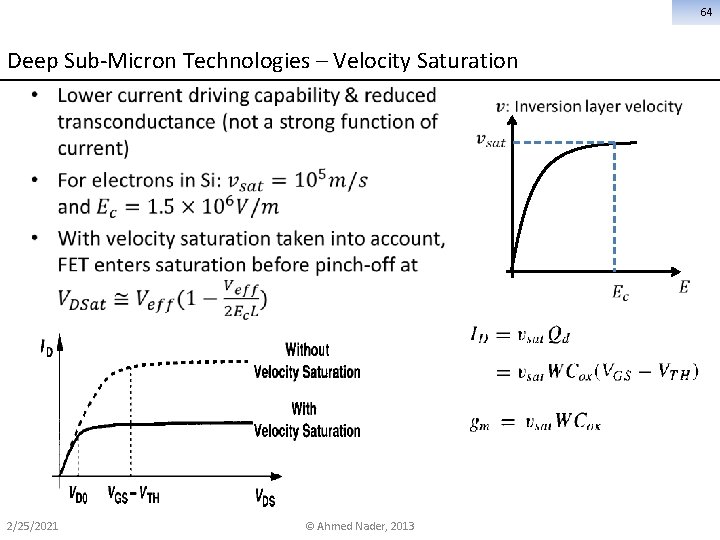

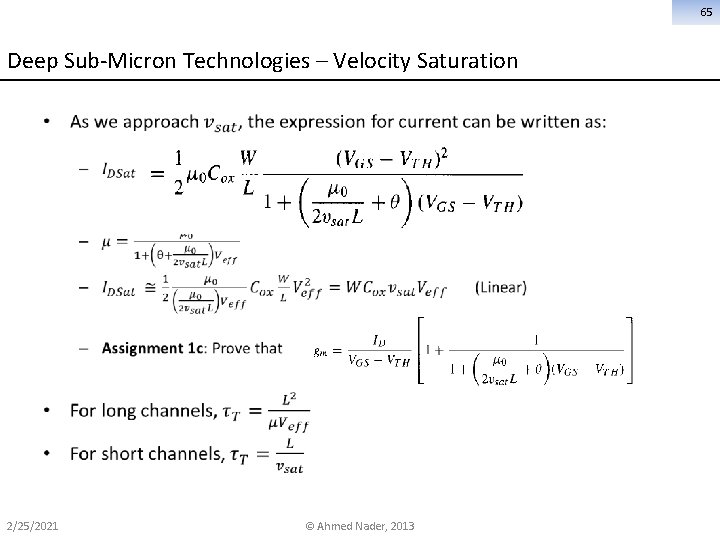

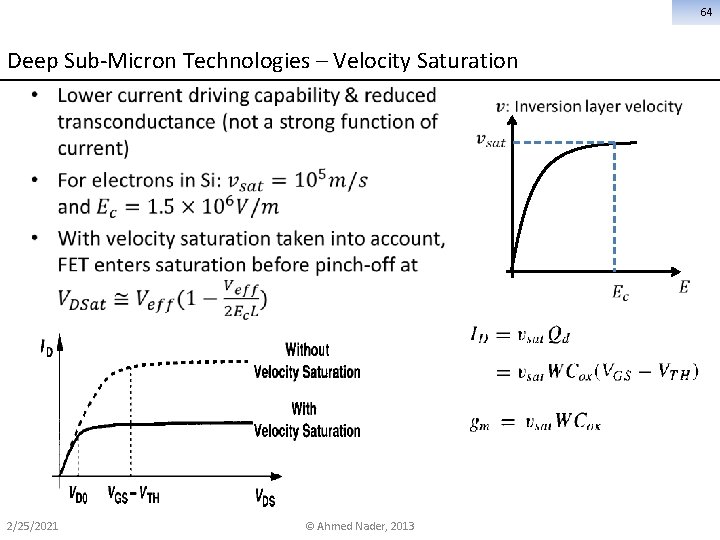

64 Deep Sub-Micron Technologies – Velocity Saturation • 2/25/2021 © Ahmed Nader, 2013

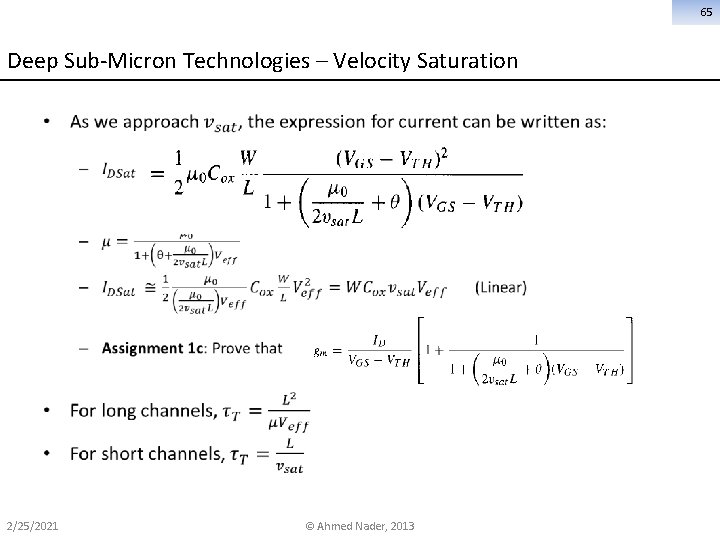

65 Deep Sub-Micron Technologies – Velocity Saturation • 2/25/2021 © Ahmed Nader, 2013

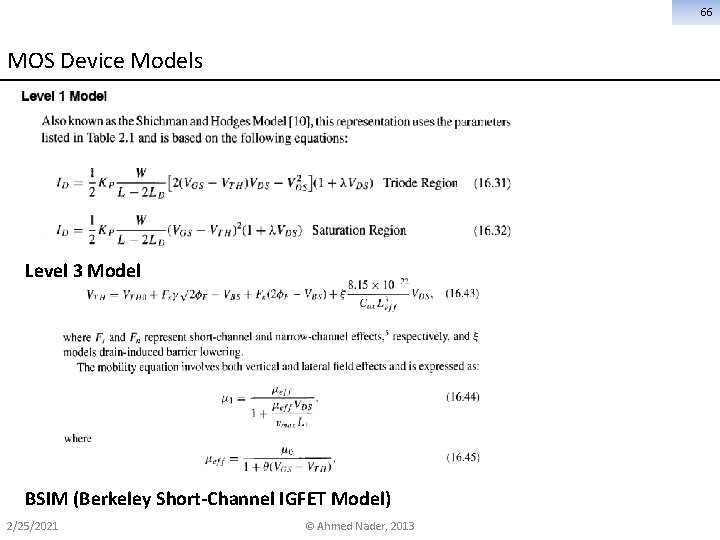

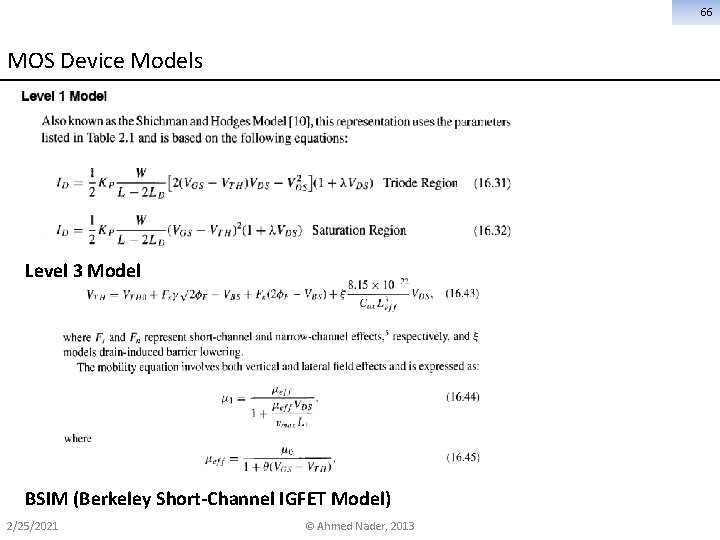

66 MOS Device Models Level 3 Model BSIM (Berkeley Short-Channel IGFET Model) 2/25/2021 © Ahmed Nader, 2013