An Introduction to VHDL Satnam Singh Xilinx FPGAs

- Slides: 26

An Introduction to VHDL Satnam Singh Xilinx

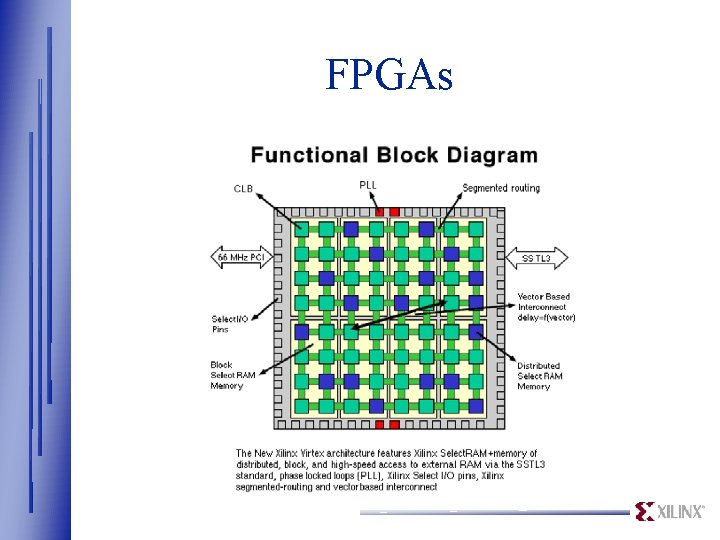

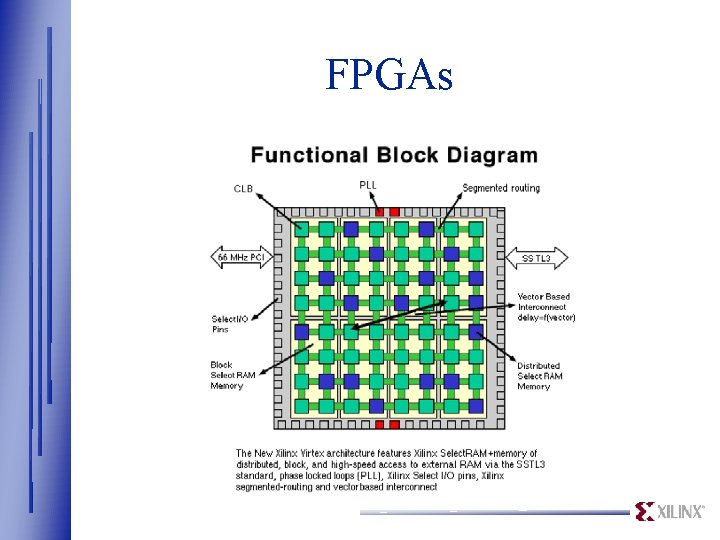

FPGAs

FPGAs

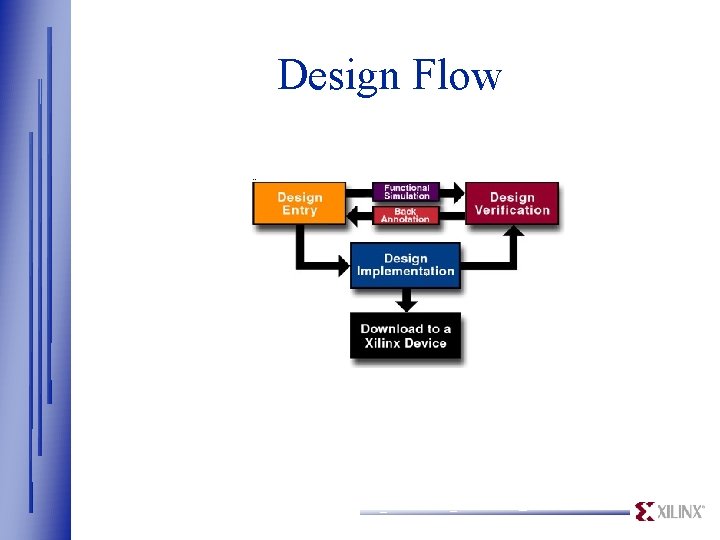

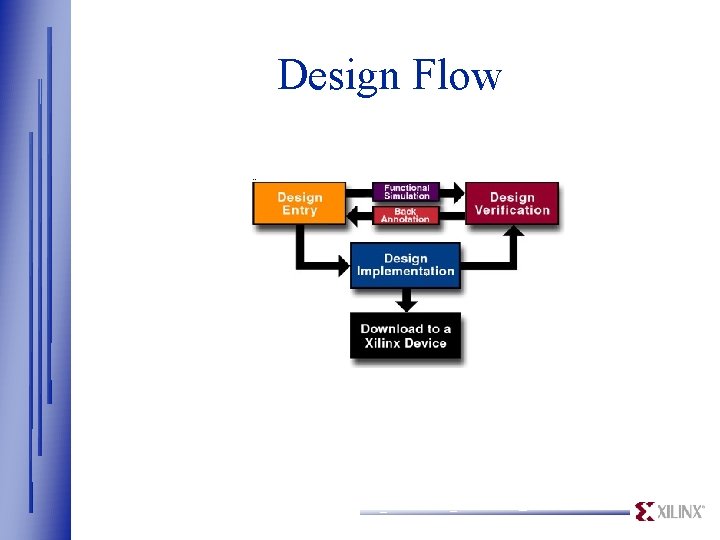

Design Flow

Schematics (Xlib)

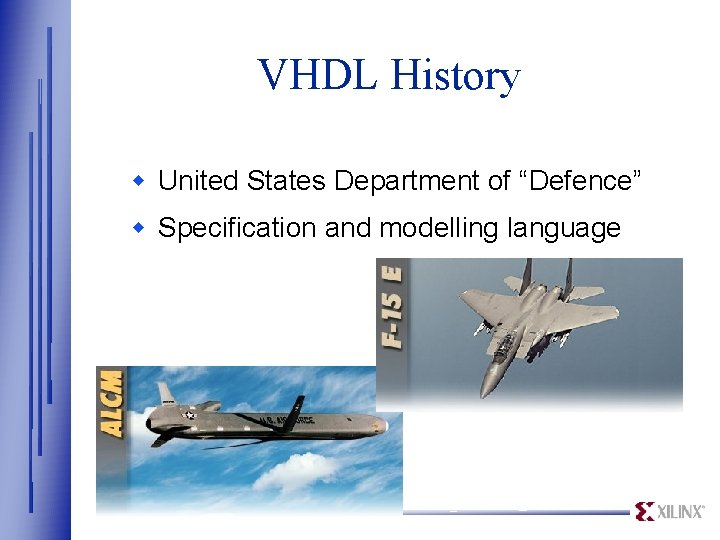

VHDL History w United States Department of “Defence” w Specification and modelling language

VHDL w 1983: Intermetrics, IBM and Texas Instruments awarded design contract for VHDL. w 1985: Final language version produced for DOD w 1987: IEEE Standard 1076 -1987 w 1988 ANSI Standard w “VHSIC Hardware Description Language” w VHSIC = Very High Speed Integrated

How is VHDL Used? w System simulation (modelling) w Test benches w Synthesis

Why not use normal languages? w Programming languages like C and Java are sequential: one thing happens at a time. w Hardware is totally concurrent: every gate is running at the same time as every other gate. w Communication occurs over wire connections.

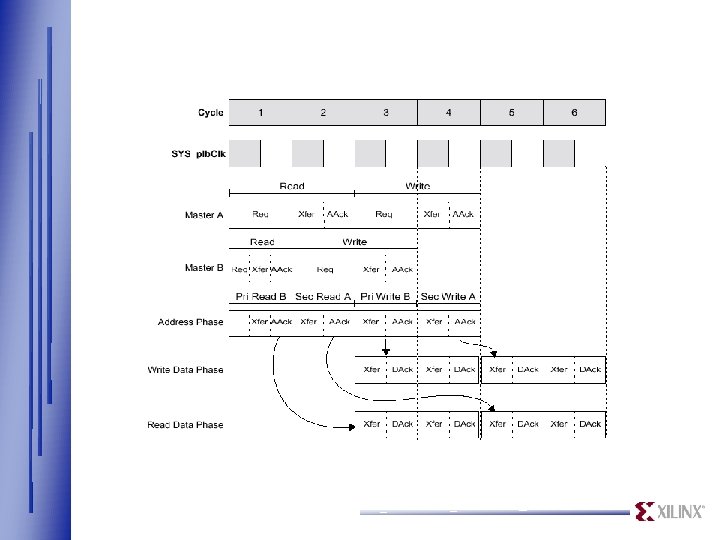

Concurrency Models w Cycle based simulation: every nnanoseconds update the state of the circuit. w Event based: only update the system when certain events occur. w VHDL uses even based simulation.

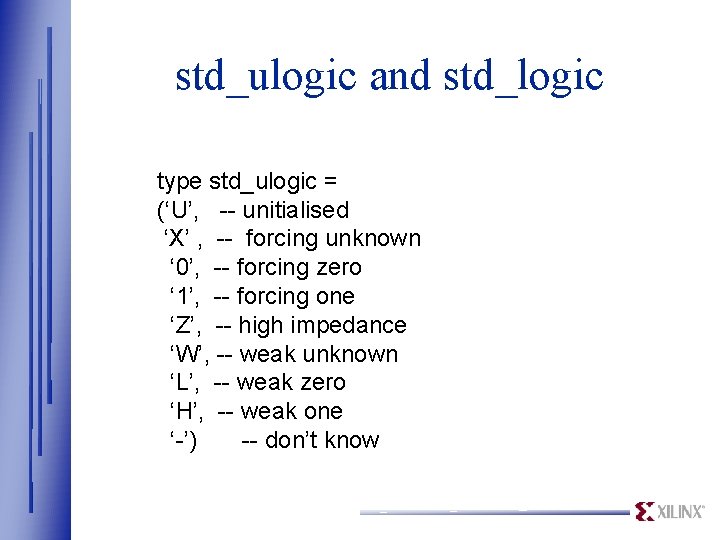

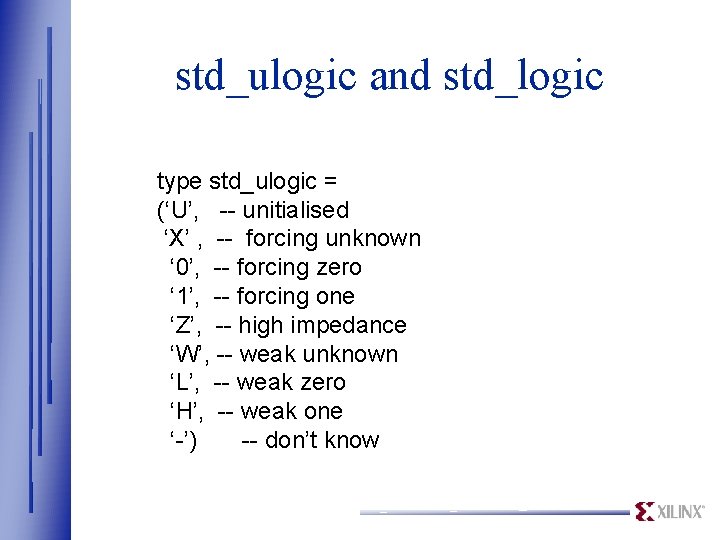

std_ulogic and std_logic type std_ulogic = (‘U’, -- unitialised ‘X’ , -- forcing unknown ‘ 0’, -- forcing zero ‘ 1’, -- forcing one ‘Z’, -- high impedance ‘W’, -- weak unknown ‘L’, -- weak zero ‘H’, -- weak one ‘-’) -- don’t know

nandgate

event based w event based fixed w chain w krav

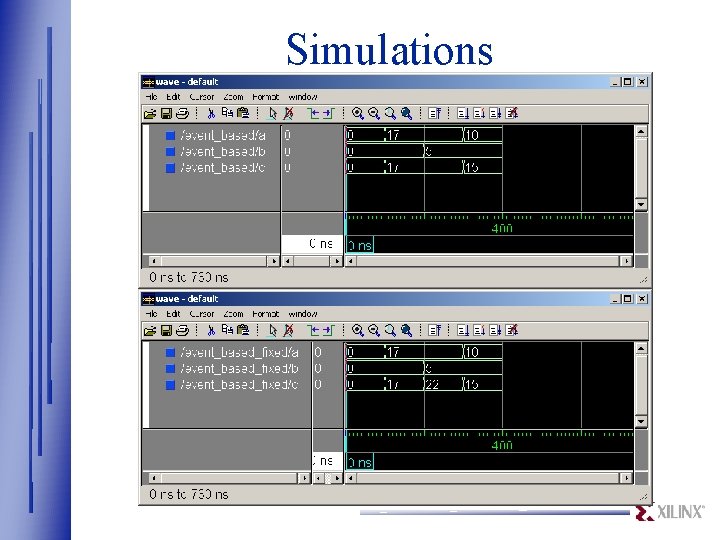

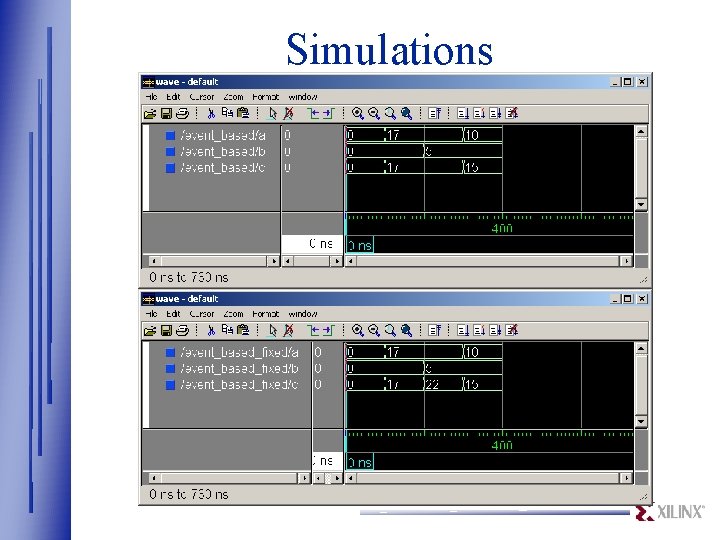

Simulations

counters w counter w resetable counter

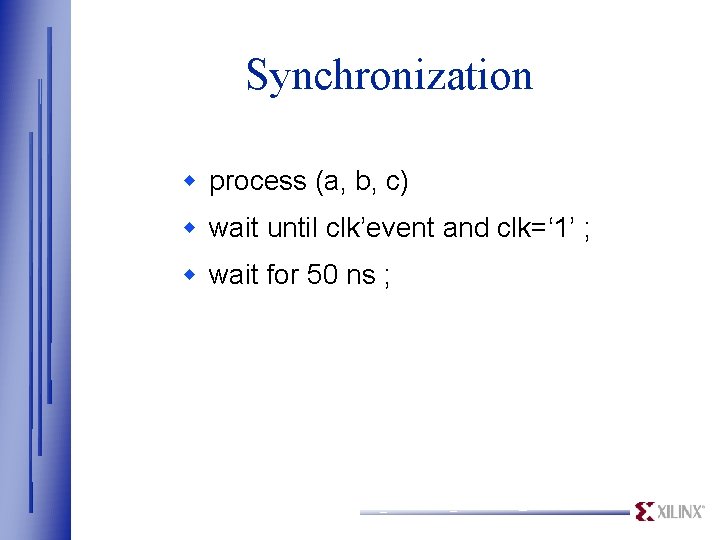

Synchronization w process (a, b, c) w wait until clk’event and clk=‘ 1’ ; w wait for 50 ns ;

variables w multi_adder

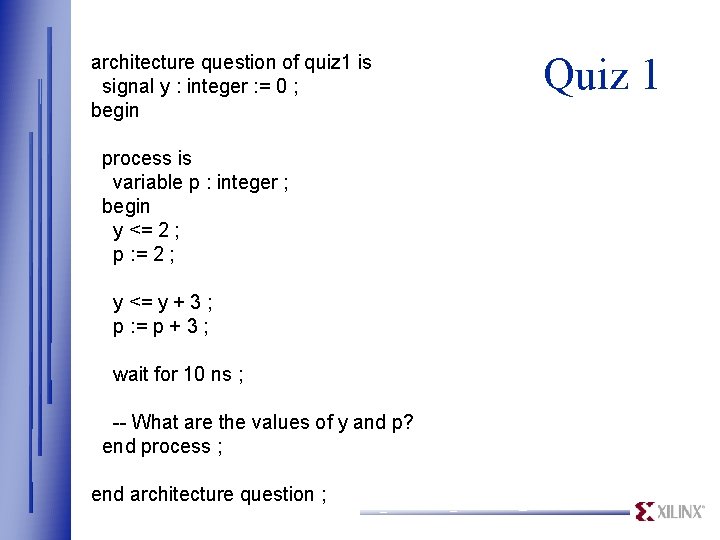

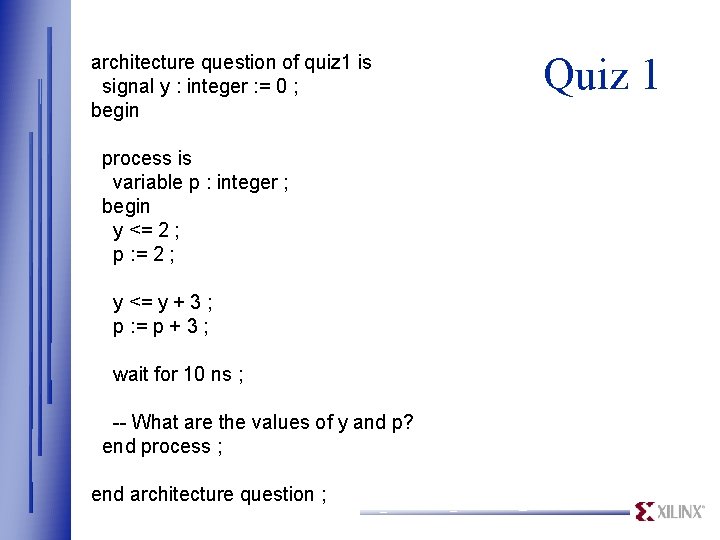

architecture question of quiz 1 is signal y : integer : = 0 ; begin process is variable p : integer ; begin y <= 2 ; p : = 2 ; y <= y + 3 ; p : = p + 3 ; wait for 10 ns ; -- What are the values of y and p? end process ; end architecture question ; Quiz 1

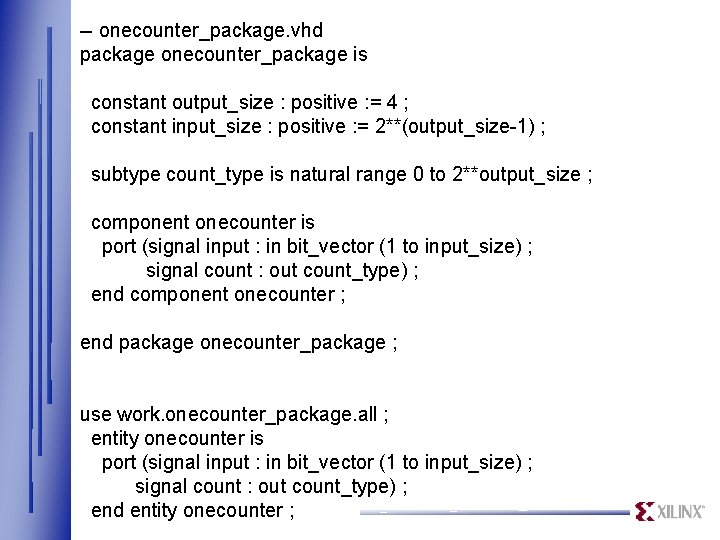

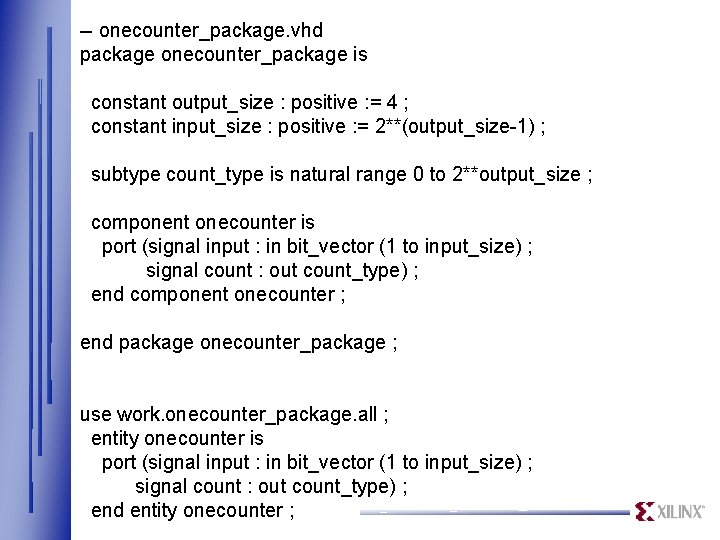

-- onecounter_package. vhd package onecounter_package is constant output_size : positive : = 4 ; constant input_size : positive : = 2**(output_size-1) ; subtype count_type is natural range 0 to 2**output_size ; component onecounter is port (signal input : in bit_vector (1 to input_size) ; signal count : out count_type) ; end component onecounter ; end package onecounter_package ; use work. onecounter_package. all ; entity onecounter is port (signal input : in bit_vector (1 to input_size) ; signal count : out count_type) ; end entity onecounter ;

-- onecounter_behav. vhd use work. onecounter_package. all ; architecture behav of onecounter is begin counting : process (input) variable total : count_type ; begin -- Calculate the total using variables. total : = 0 ; for i in input'range loop if input(i) = '1' then total : = total + 1 ; end if ; end loop ; -- Assign the calculated total to the output signal. count <= total ; end process counting ; end behav ;

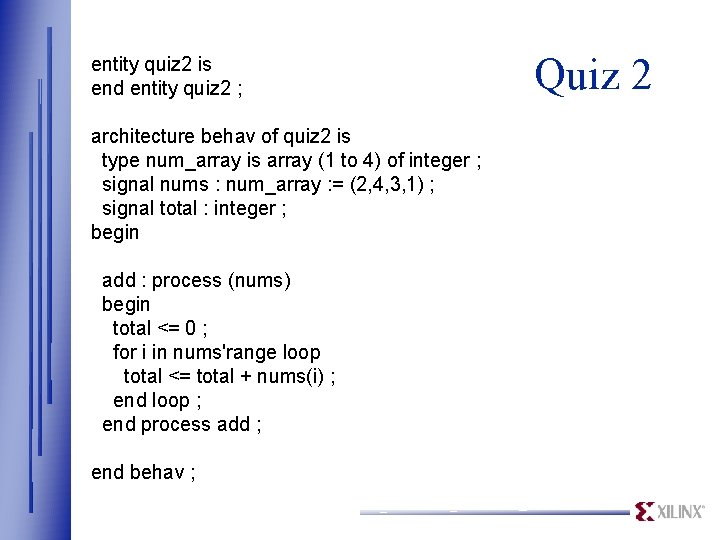

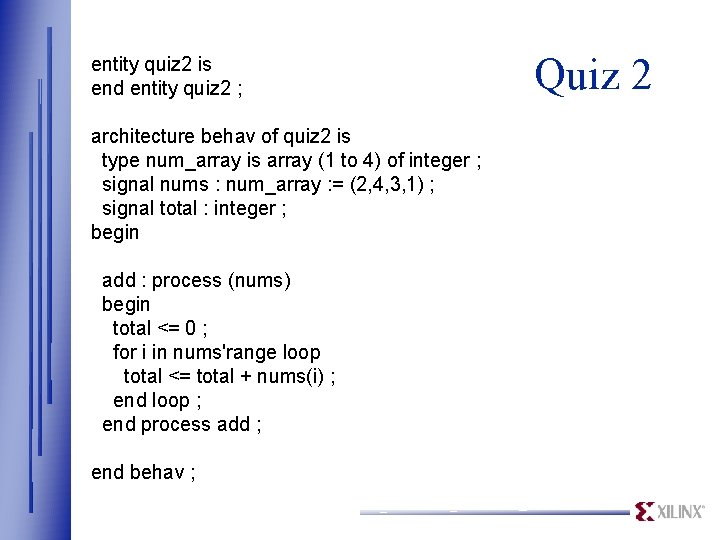

entity quiz 2 is end entity quiz 2 ; architecture behav of quiz 2 is type num_array is array (1 to 4) of integer ; signal nums : num_array : = (2, 4, 3, 1) ; signal total : integer ; begin add : process (nums) begin total <= 0 ; for i in nums'range loop total <= total + nums(i) ; end loop ; end process add ; end behav ; Quiz 2

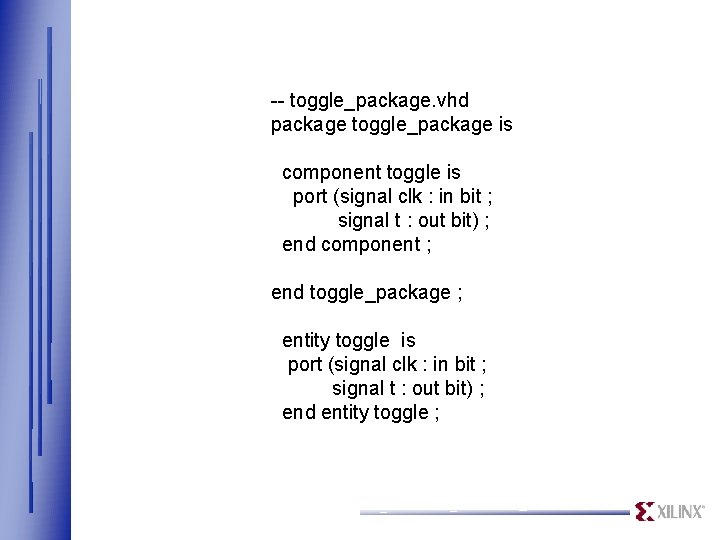

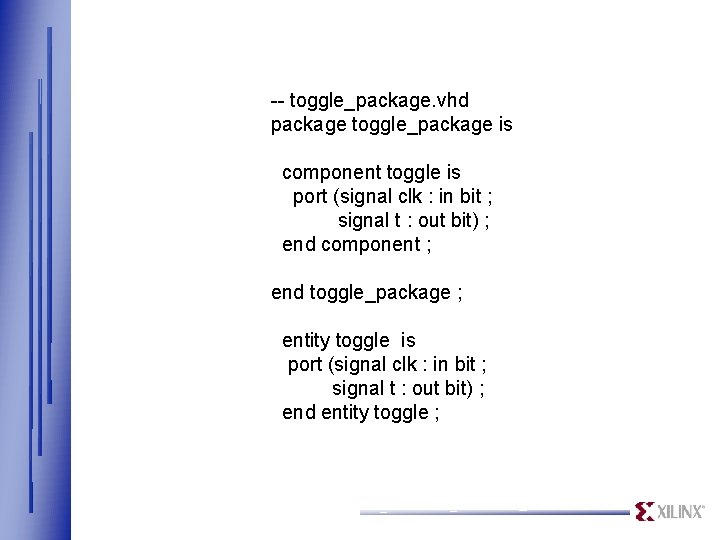

-- toggle_package. vhd package toggle_package is component toggle is port (signal clk : in bit ; signal t : out bit) ; end component ; end toggle_package ; entity toggle is port (signal clk : in bit ; signal t : out bit) ; end entity toggle ;

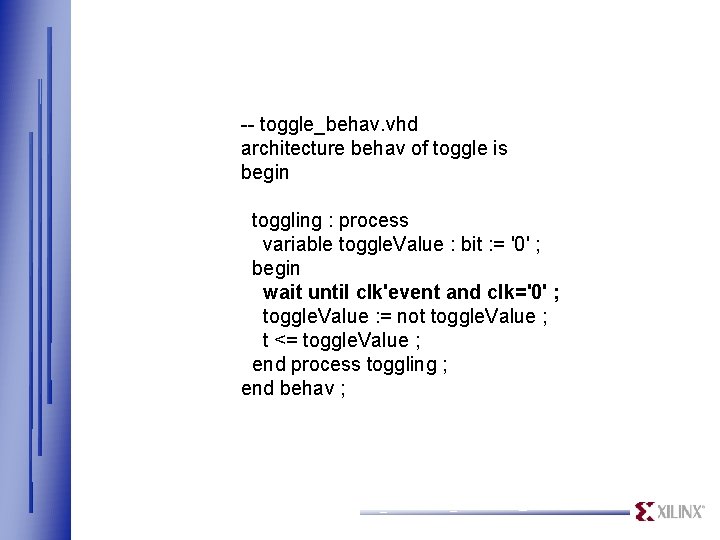

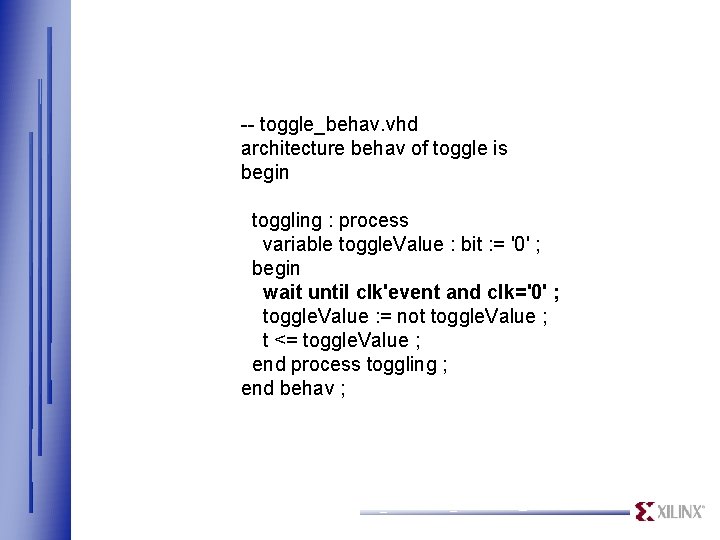

-- toggle_behav. vhd architecture behav of toggle is begin toggling : process variable toggle. Value : bit : = '0' ; begin wait until clk'event and clk='0' ; toggle. Value : = not toggle. Value ; t <= toggle. Value ; end process toggling ; end behav ;

Synthesis w toggle