An Emulated Computer with Assembler for Teaching Undergraduate

An Emulated Computer with Assembler for Teaching Undergraduate Computer Architecture Timothy Daryl Stanley Mu Wang Brigham Young University Hawaii Presented by Bill Yurcik/NCSA

Objective • Demonstrate an 8 -bit computer built using a free logic emulation software package* to make very clear to students how: – Digital logic and binary number systems work – How data paths and control paths work – How devices (Memory, ALU, Clock, Multiplexers) combine to make computers – How a program in memory controls the registers, memory, ALUs and data paths – How instructions are decoded – How an assembler works * Multimedia Logic from www. softronix. com

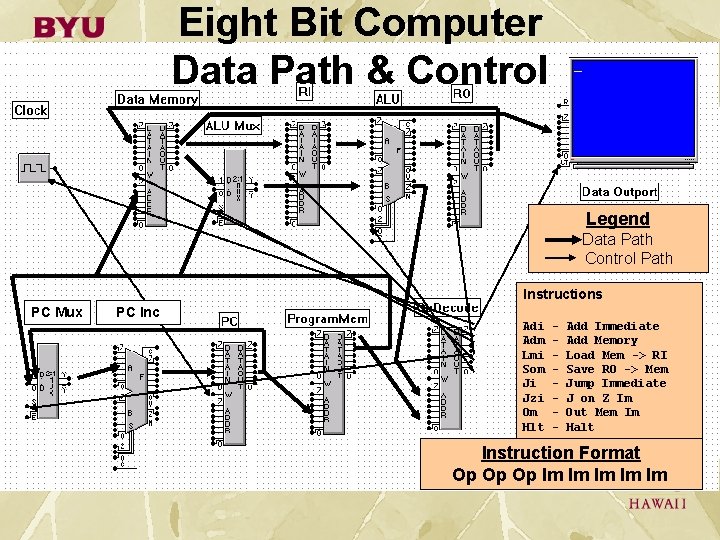

Eight Bit Computer Data Path & Control Legend Data Path Control Path Instructions PC Mux PC Inc Adi Adm Lmi Som Ji Jzi Om Hlt - Add Immediate Add Memory Load Mem -> RI Save RO -> Mem Jump Immediate J on Z Im Out Mem Im Halt Instruction Format Op Op Op Im Im Im

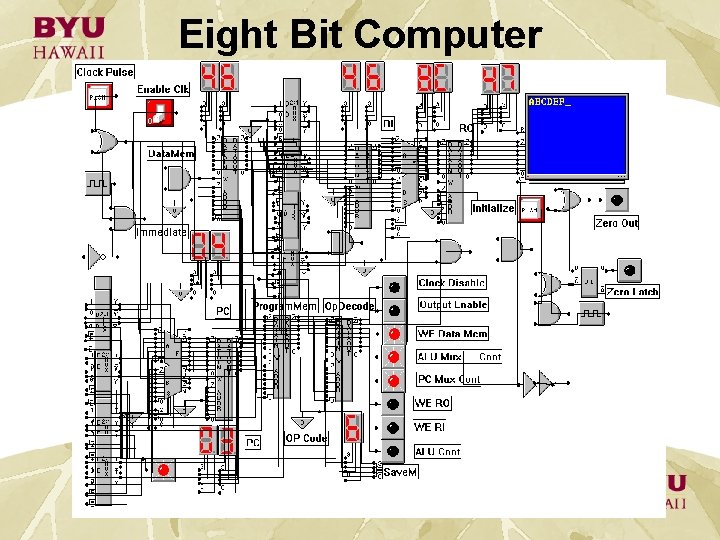

Eight Bit Computer

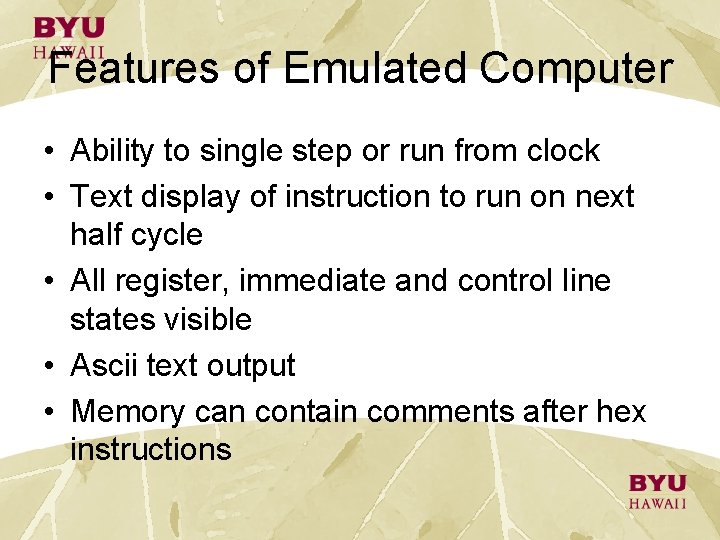

Features of Emulated Computer • Ability to single step or run from clock • Text display of instruction to run on next half cycle • All register, immediate and control line states visible • Ascii text output • Memory can contain comments after hex instructions

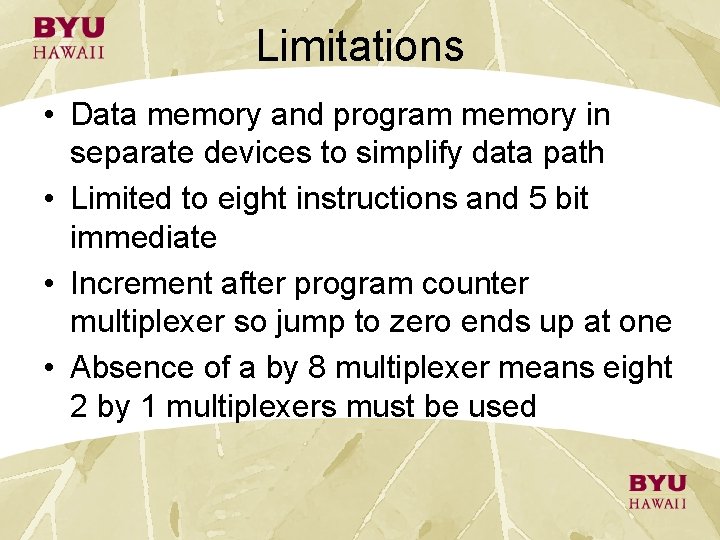

Limitations • Data memory and program memory in separate devices to simplify data path • Limited to eight instructions and 5 bit immediate • Increment after program counter multiplexer so jump to zero ends up at one • Absence of a by 8 multiplexer means eight 2 by 1 multiplexers must be used

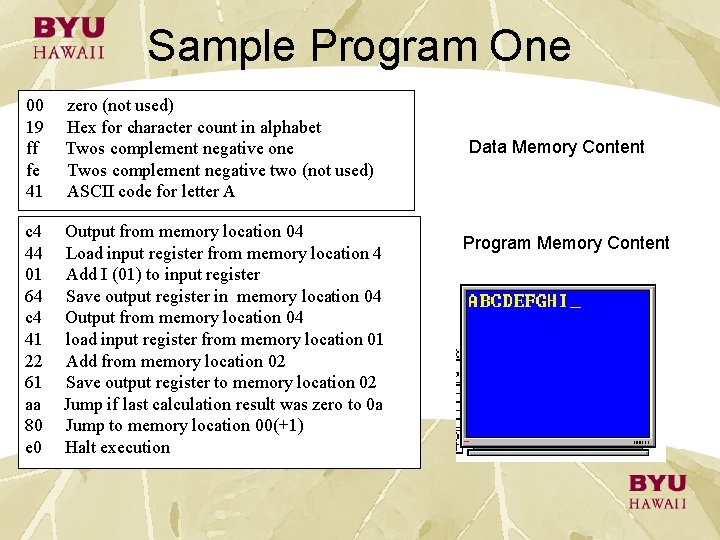

Sample Program One 00 19 ff fe 41 zero (not used) Hex for character count in alphabet Twos complement negative one Twos complement negative two (not used) ASCII code for letter A c 4 44 01 64 c 4 41 22 61 aa 80 e 0 Output from memory location 04 Load input register from memory location 4 Add I (01) to input register Save output register in memory location 04 Output from memory location 04 load input register from memory location 01 Add from memory location 02 Save output register to memory location 02 Jump if last calculation result was zero to 0 a Jump to memory location 00(+1) Halt execution Data Memory Content Program Memory Content

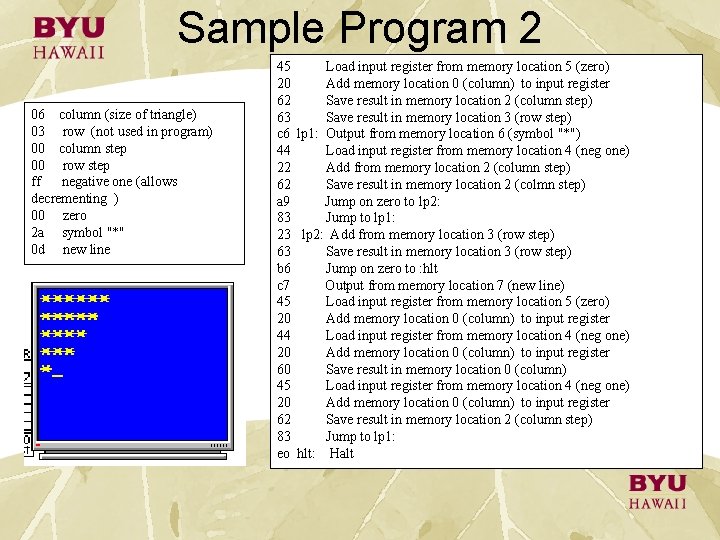

Sample Program 2 06 column (size of triangle) 03 row (not used in program) 00 column step 00 row step ff negative one (allows decrementing ) 00 zero 2 a symbol "*" 0 d new line 45 Load input register from memory location 5 (zero) 20 Add memory location 0 (column) to input register 62 Save result in memory location 2 (column step) 63 Save result in memory location 3 (row step) c 6 lp 1: Output from memory location 6 (symbol "*") 44 Load input register from memory location 4 (neg one) 22 Add from memory location 2 (column step) 62 Save result in memory location 2 (colmn step) a 9 Jump on zero to lp 2: 83 Jump to lp 1: 23 lp 2: Add from memory location 3 (row step) 63 Save result in memory location 3 (row step) b 6 Jump on zero to : hlt c 7 Output from memory location 7 (new line) 45 Load input register from memory location 5 (zero) 20 Add memory location 0 (column) to input register 44 Load input register from memory location 4 (neg one) 20 Add memory location 0 (column) to input register 60 Save result in memory location 0 (column) 45 Load input register from memory location 4 (neg one) 20 Add memory location 0 (column) to input register 62 Save result in memory location 2 (column step) 83 Jump to lp 1: eo hlt: Halt

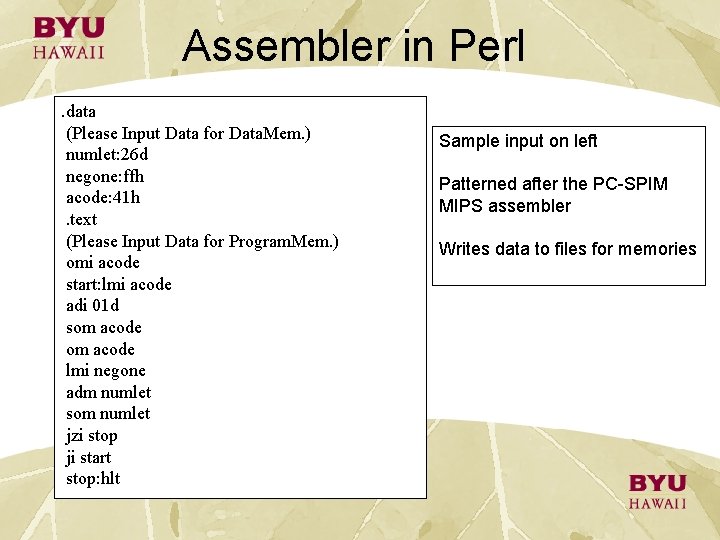

Assembler in Perl. data (Please Input Data for Data. Mem. ) numlet: 26 d negone: ffh acode: 41 h. text (Please Input Data for Program. Mem. ) omi acode start: lmi acode adi 01 d som acode lmi negone adm numlet som numlet jzi stop ji start stop: hlt Sample input on left Patterned after the PC-SPIM MIPS assembler Writes data to files for memories

Conclusions • 8 bit Computer designed using Multimedia Logic from www. softronix. com • Files available at http: //cs. byuh. edu/links. html • Demonstrates data path and control path • Design and implementation of operation codes demonstrated • Provided the starting point of many student design project designs including 16 bit computers

Optional additional material

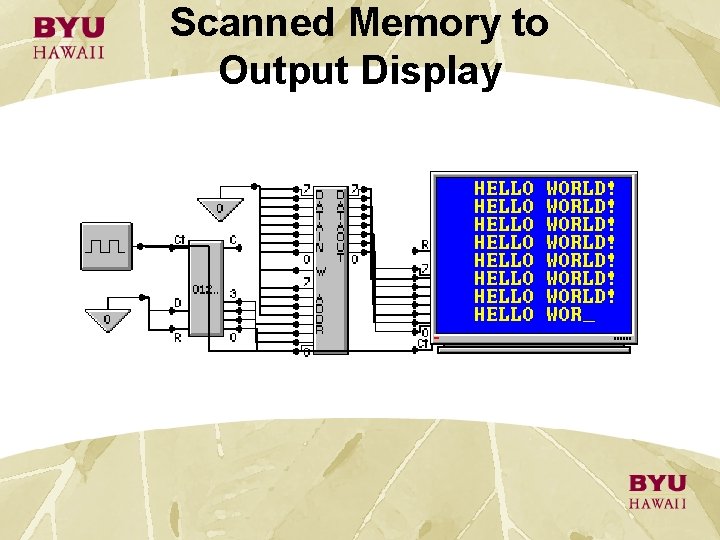

Scanned Memory to Output Display

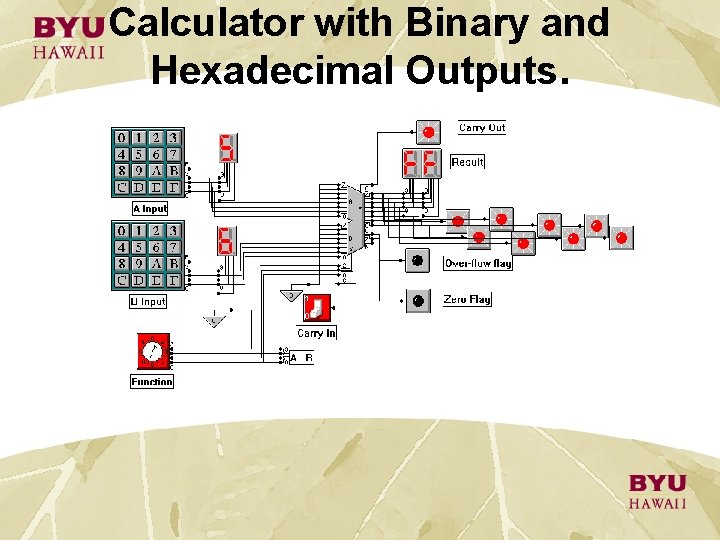

Calculator with Binary and Hexadecimal Outputs.

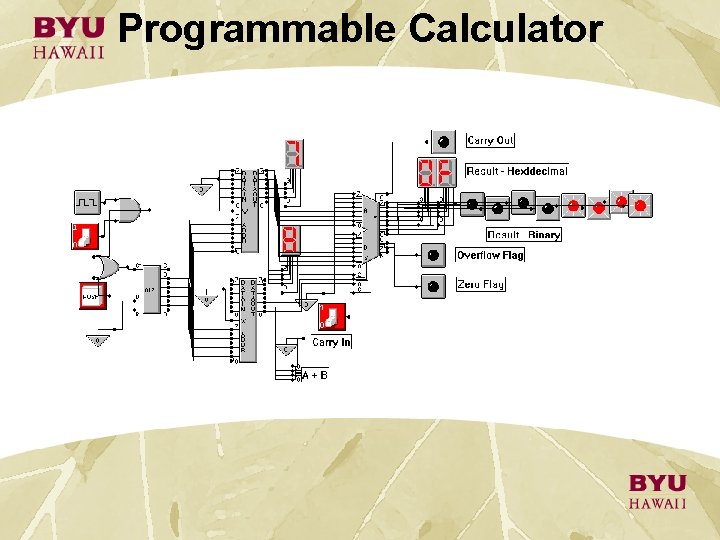

Programmable Calculator

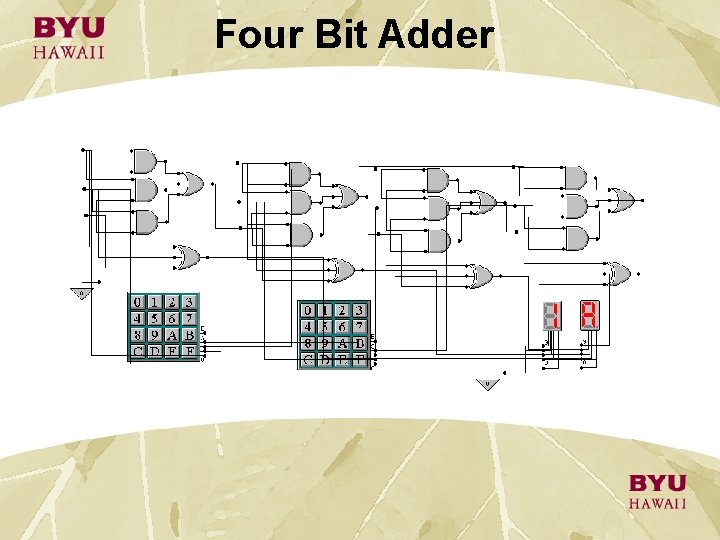

Four Bit Adder

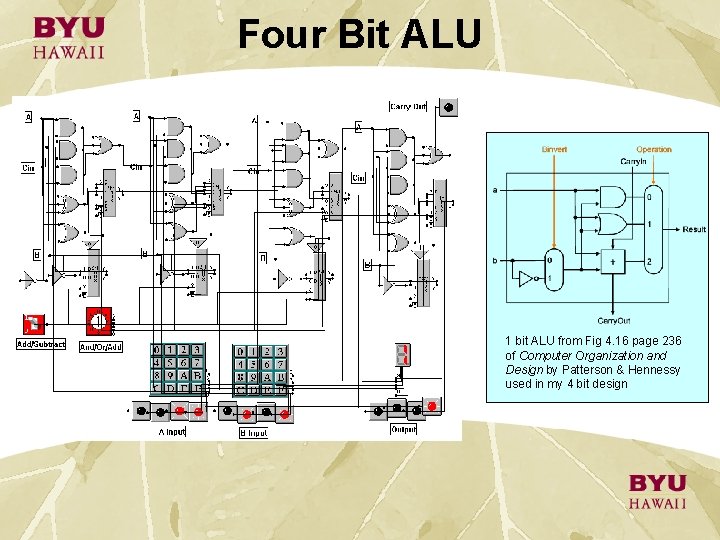

Four Bit ALU 1 bit ALU from Fig 4. 16 page 236 of Computer Organization and Design by Patterson & Hennessy used in my 4 bit design

- Slides: 16