AN ASSEMBLY LANGUAGE SIMULATOR TO ILLUSTRATE COMPUTER ARCHITECTURE

AN ASSEMBLY LANGUAGE SIMULATOR TO ILLUSTRATE COMPUTER ARCHITECTURE DESIGN Marwan Shaban, Ph. D. and Adam J. Rocke, Ph. D. Seminole State College

AGENDA • Motivation • Solution • Existing Tools • Design Considerations • Examples • Instruction Encoding • Numeric Representation • Procedures • Future Revisions

CONVERGENCE COLLEGE NETWORK (CCN) • Funded by the National Convergence Technology Center (NSF Advanced Technological Education Center) • Manages the CCN community of practice featuring 64 schools in 24 states that regularly shares expertise and best practices • Engages a national Business and Industry Leadership Team (BILT) to identify needed IT job skills to keep curriculum current with industry trends • Trains faculty on emerging technologies through in -depth professional development • Developing seven regional hubs to create new relationships and boost 2+2+2 articulation pathways • Disseminates materials and processes via webinars, social media, and presentations

MOTIVATION • Seminole State College – BS IST Program • CDA 3100 – Introduction to Computer Architecture • “This course provides an introduction to computer taxonomy, description languages, conventional computer architecture, microprogramming, instruction sets, I/O techniques, memory, survey of non-conventional architecture and software interfaces. ” • New text covering the RISC-V Instruction Set Architecture (ISA). • Alternatives include MIPS and ARM. • Existing simulator tools did not meet our requirements.

MOTIVATION • Teaching assembly language without a simulator is like teaching: • auto repair without cars, • music without instruments, or • swimming without water. • It is difficult to illustrate computer architecture concepts without appropriate tools. • A language simulator can illustrate these concepts and allow students to test assembly language execution.

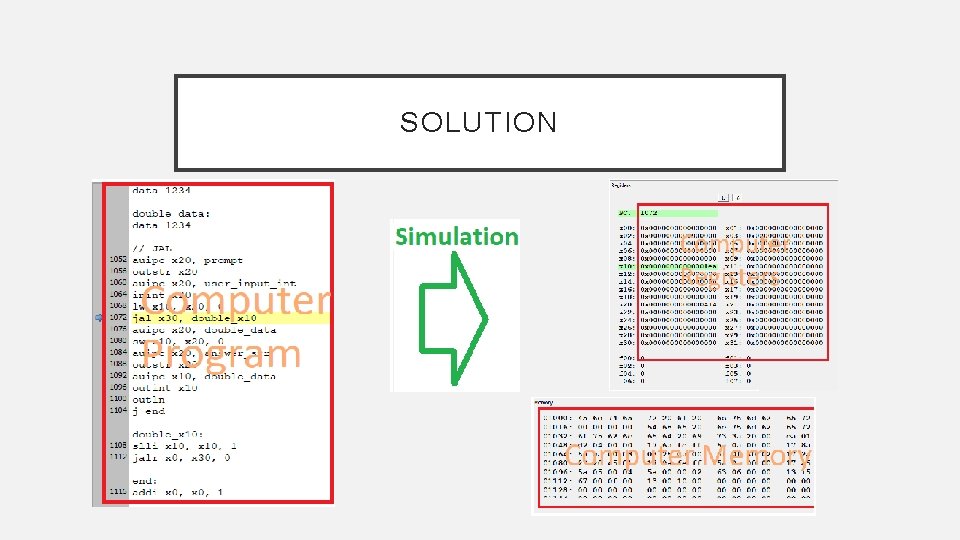

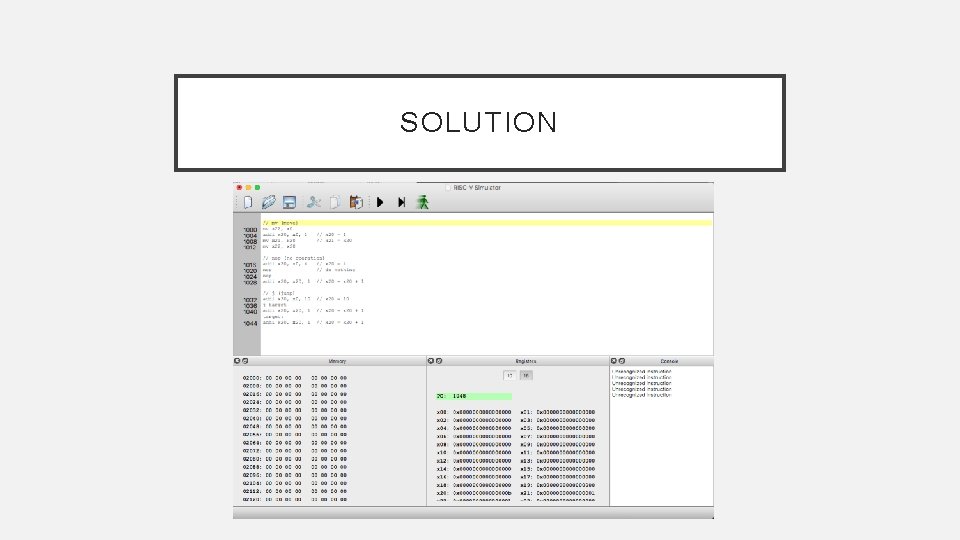

SOLUTION • Funding a solution is cost prohibitive. • In addition to being faculty, we are also practitioners. • We developed the RISC-V simulator to specifically address teaching of computer architecture and assembly language concepts. • It allows students to create and simulate the execution of programs. • This in turn facilitates understanding of internal computer operations. • We are solving a teaching problem using technology.

SOLUTION

SOLUTION

EXISTING TOOLS • Many existing tools are available: • https: //github. com/riscv-wiki/RISC-V-Software-Status • Fire. Sim - https: //fires. im/ • Fire. Sim is a cycle-accurate, FPGA-accelerated scale-out computer system simulation platform. • Imperas - http: //www. imperas. com/riscv • RISC-V system emulator with library of over 200 components of Ethernet, USB, CAN, UARTs, and many other peripherals. • Spike - https: //github. com/riscv-isa-sim • The RISC-V ISA Simulator implements a functional model of one or more RISC-V processors. • Existing tools do not meet our goals as they: • do not visually update memory and registers in real time, • operate via the command-line, • focus on simulating multiple nodes, and • many are unmaintained.

EDUCATIONAL VS. INDUSTRIAL SOFTWARE • Industrial tools often have too many features. • May be inappropriate for classroom use. • Difficult and time consuming to learn. • Educational software can be more user friendly. • Goal: make the experience fun and encourage student engagement. • Educational focus allowed us to leave out certain features. • Omit uncommon instructions. • Do not need memory segmentation common in other assemblers. • The result is a reduced development time and simpler end product.

DESIGN CONSIDERATIONS • Focus on education. • Design for usability. • Release as open source to encourage collaboration. • Implement the simulator using cross-platform and free components. • Use QT as the application framework. • The simulator should be fast, portable, and extensible. • The simulator is written in C++.

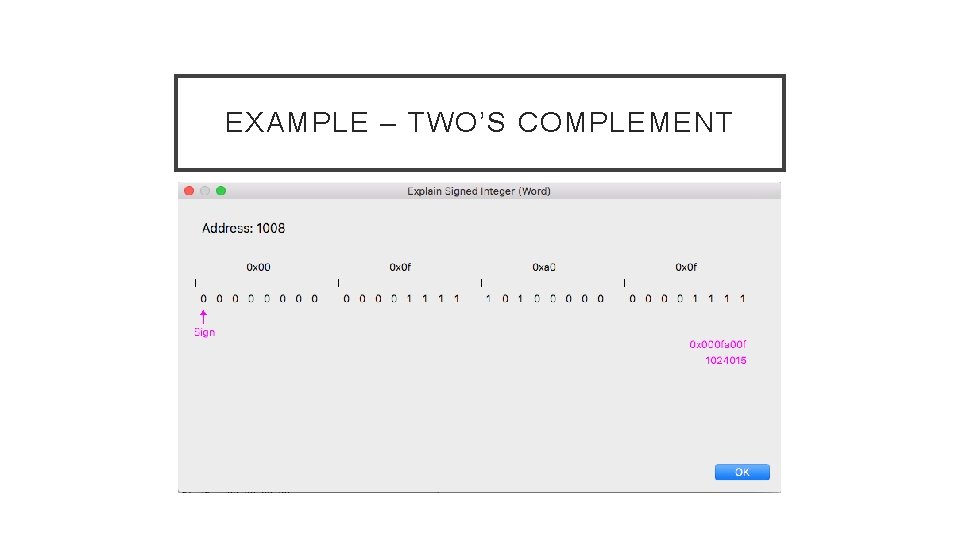

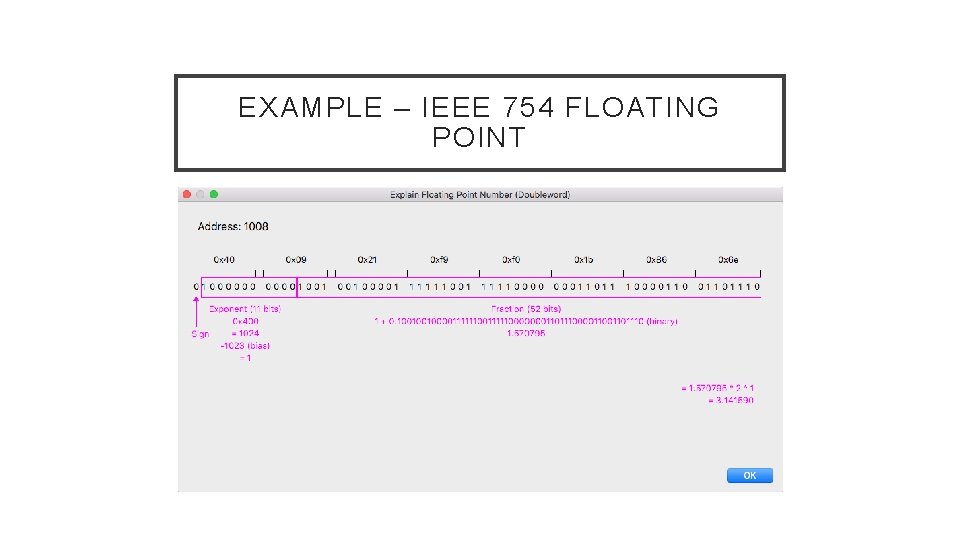

SIMULATOR FEATURE LIST • Register array and memory update in real time. • Set breakpoints and step through programs one instruction at a time. • "Explain Instruction". • Instruction format, encoding, and binary values shown for all instructions. • Faithful implementation of the RISC-V architecture, for instance: • two's compliment signed integer representation and the • IEEE 754 format for floating point numbers. • Implement the most important instructions. • Instructions such as doubleword variants are not currently implemented.

ADDITIONAL SIMULATOR FEATURES • Support for labels and breakpoints. • Some pseudo-instructions, such as J, MV, NOP, are implemented. • Enable basic input and output functions. • Assemble instructions in real-time. • Support constant data. • The simulator currently runs on Windows, mac. OS and Linux.

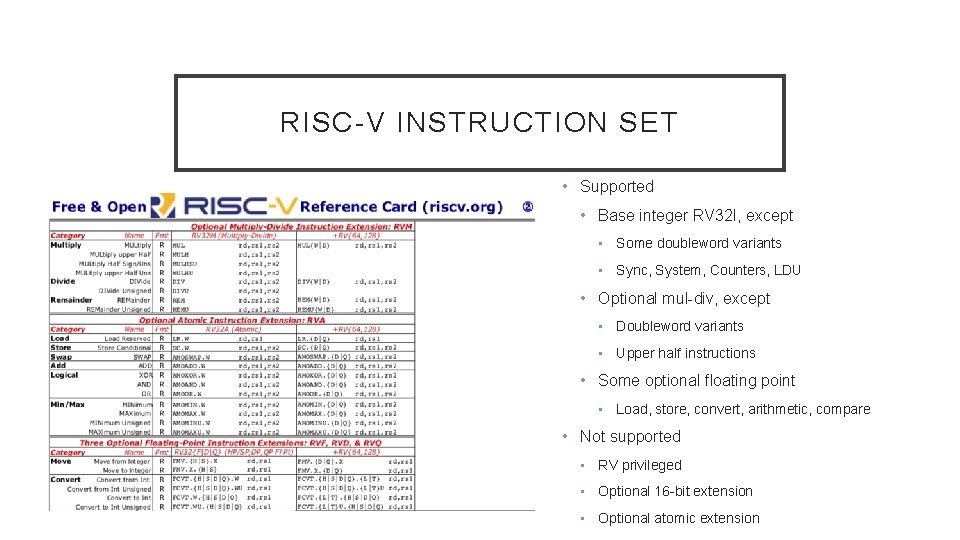

RISC-V INSTRUCTION SET • Supported • • • Base integer RV 32 I, except • Some doubleword variants • Sync, System, Counters, LDU Optional mul-div, except • Doubleword variants • Upper half instructions Some optional floating point • • Load, store, convert, arithmetic, compare Not supported • RV privileged • Optional 16 -bit extension • Optional atomic extension • Base integer RV 32 I, except • Some doubleword variants • Sync, System, Counters, LDU • Optional mul-div, except • Doubleword variants • Upper half instructions • Some optional floating point • Load, store, convert, arithmetic, compare • Not supported • RV privileged • Optional 16 -bit extension • Optional atomic extension

DEMONSTRATION • Create new program. • Execute instructions. • Registers and memory update in real time. • Program is assembled as it is being edited. • Load an existing program. • Demonstrate pseudo-instructions such as j and mv. • Input-output example. • Other samples to demonstrate functionality are available.

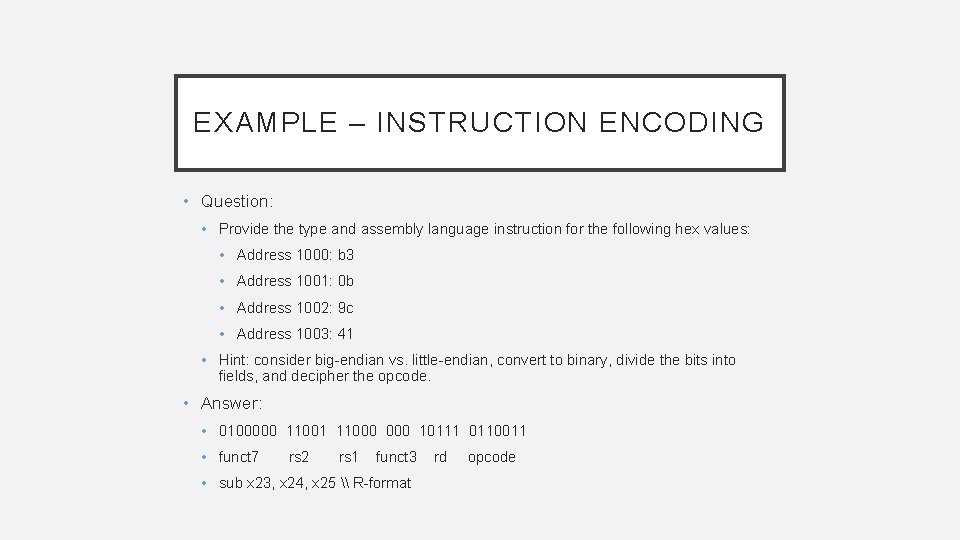

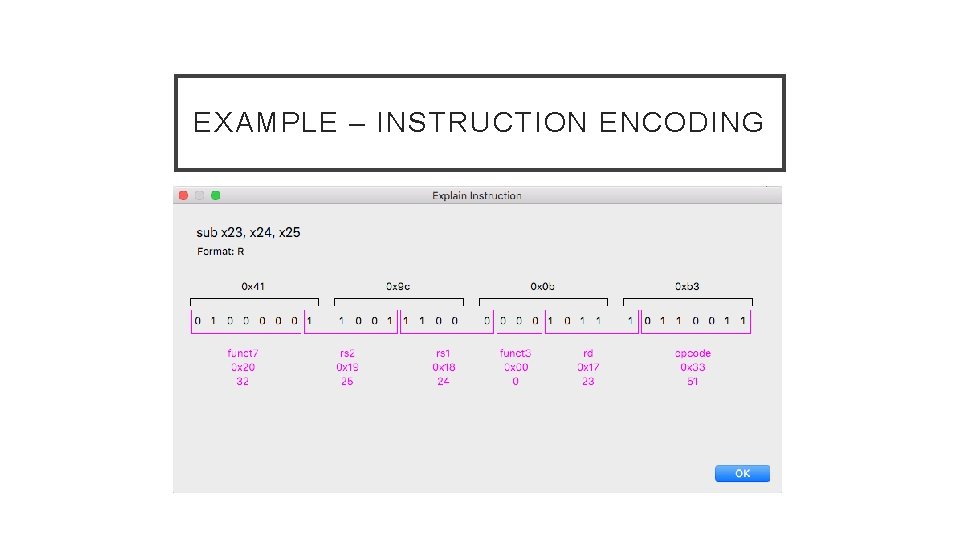

EXAMPLE – INSTRUCTION ENCODING • Question: • Provide the type and assembly language instruction for the following hex values: • Address 1000: b 3 • Address 1001: 0 b • Address 1002: 9 c • Address 1003: 41 • Hint: consider big-endian vs. little-endian, convert to binary, divide the bits into fields, and decipher the opcode. • Answer: • 0100000 11001 11000 10111 0110011 • funct 7 rs 2 rs 1 funct 3 • sub x 23, x 24, x 25 \ R-format rd opcode

EXAMPLE – INSTRUCTION ENCODING

EXAMPLE – NUMERIC REPRESENTATION positive: data 1024015 negative: data – 12 pi: data 3. 14159 one_point_one: data 1. 1

EXAMPLE – TWO’S COMPLEMENT

EXAMPLE – IEEE 754 FLOATING POINT

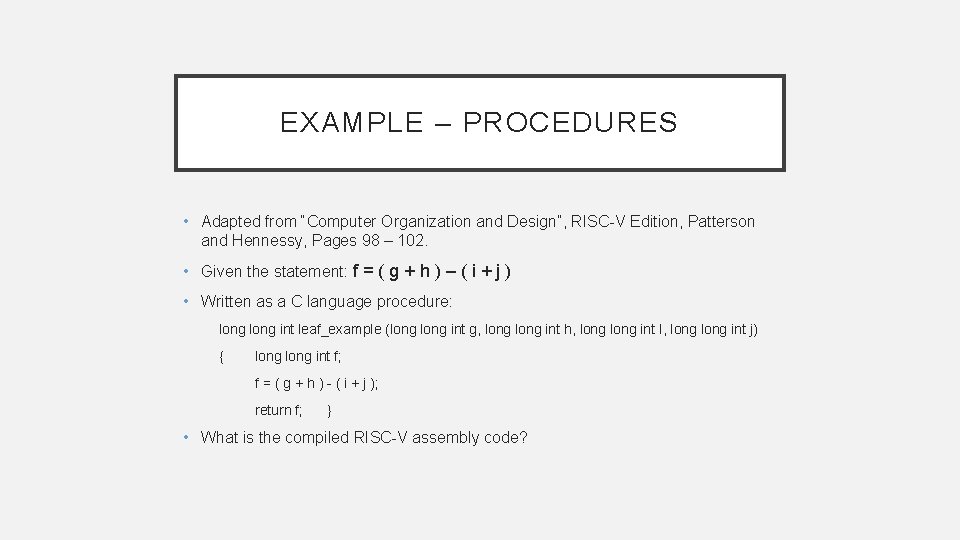

EXAMPLE – PROCEDURES • Adapted from “Computer Organization and Design”, RISC-V Edition, Patterson and Hennessy, Pages 98 – 102. • Given the statement: f = ( g + h ) – ( i + j ) • Written as a C language procedure: long int leaf_example (long int g, long int h, long int I, long int j) { long int f; f = ( g + h ) - ( i + j ); return f; } • What is the compiled RISC-V assembly code?

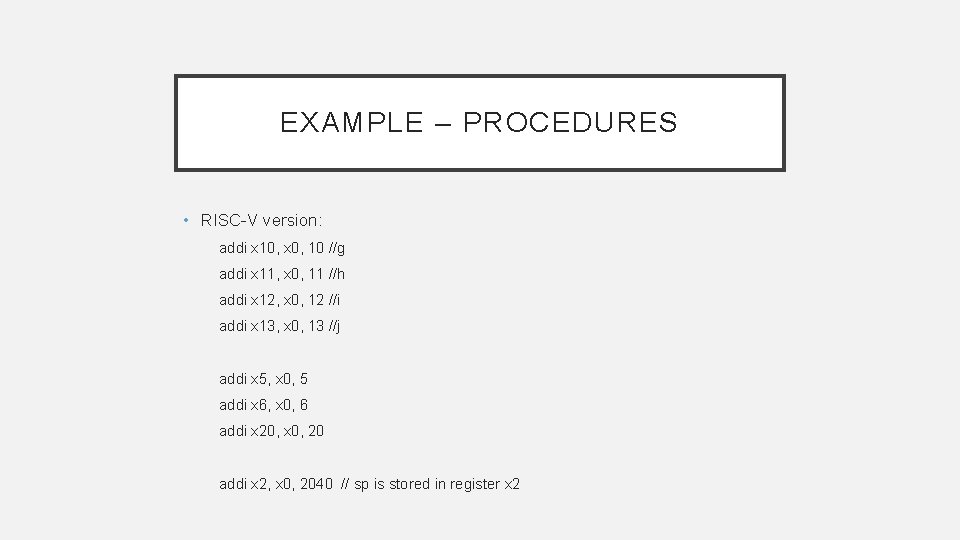

EXAMPLE – PROCEDURES • RISC-V version: addi x 10, x 0, 10 //g addi x 11, x 0, 11 //h addi x 12, x 0, 12 //i addi x 13, x 0, 13 //j addi x 5, x 0, 5 addi x 6, x 0, 6 addi x 20, x 0, 20 addi x 2, x 0, 2040 // sp is stored in register x 2

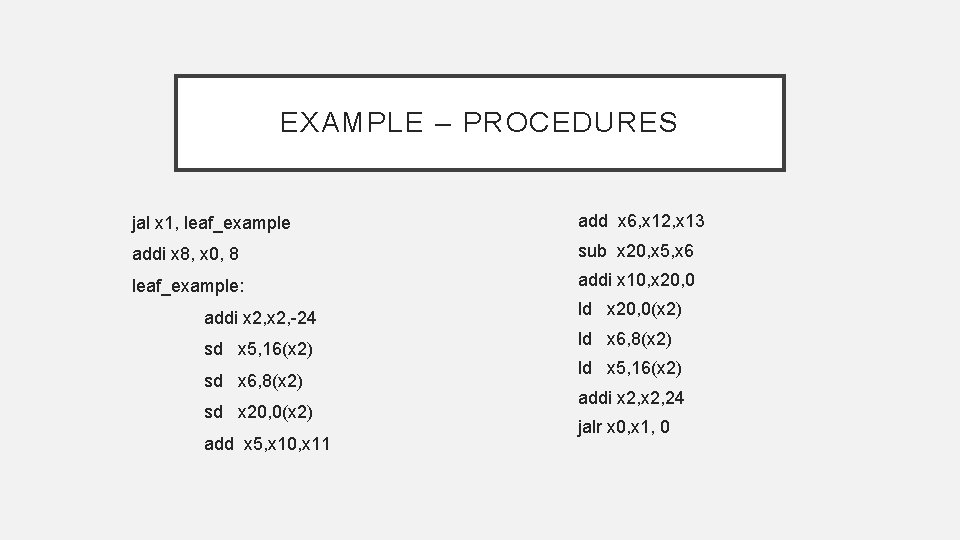

EXAMPLE – PROCEDURES jal x 1, leaf_example add x 6, x 12, x 13 addi x 8, x 0, 8 sub x 20, x 5, x 6 leaf_example: addi x 10, x 20, 0 addi x 2, -24 sd x 5, 16(x 2) sd x 6, 8(x 2) sd x 20, 0(x 2) add x 5, x 10, x 11 ld x 20, 0(x 2) ld x 6, 8(x 2) ld x 5, 16(x 2) addi x 2, 24 jalr x 0, x 1, 0

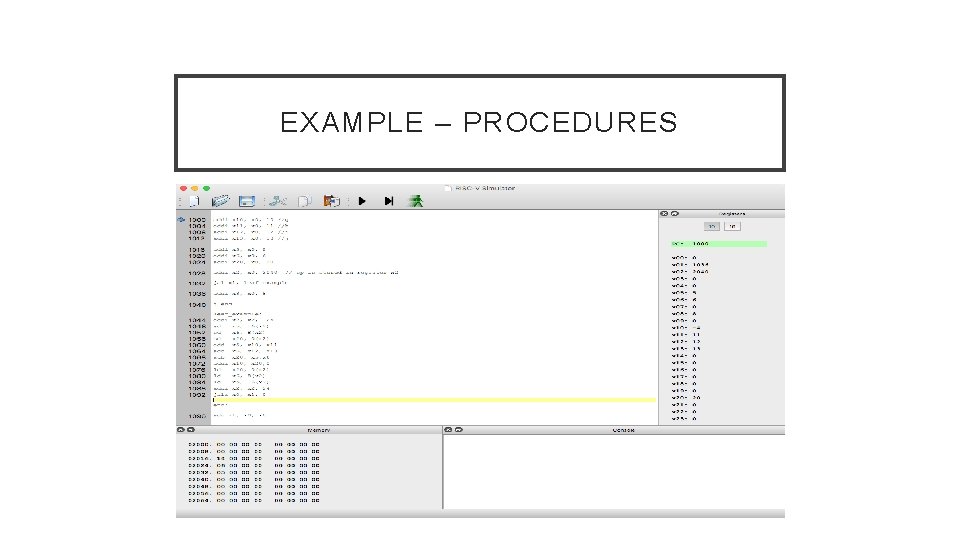

EXAMPLE – PROCEDURES

STUDENT RESPONSE • First used in the classroom in the Spring 2018 semester. • Initial reviews are favorable. • Provides a hands-on component to the course. • Enhances learning. • Fun and engaging for the students. • Student have requested new features. • Add a “reset button”. • Provide a way to enter values directly.

FUTURE DEVELOPMENT • Add usability enhancements such as automatic resizing of windows. • Preserve the PC location after a user edits the program. • Add functionality to directly modify registers and memory.

SIMULATOR DOWNLOAD • The simulator can be used in various courses including: • computer architecture, • assembly language programming, • or general programming. • Git. Hub repository: • https: //github. com/Professor. Shaban/risc-v-simulator. git • Build using QT Creator

QUESTIONS AND CONTACT INFORMATION • Professor Marwan Shaban, Ph. D. • shabanm@seminolestate. edu • Professor Adam J. Rocke, Ph. D. • rockea@seminolestate. edu

- Slides: 28