An Architectural Exploration of Via Patterned Gate Arrays

- Slides: 23

An Architectural Exploration of Via Patterned Gate Arrays Chetan Patel, Anthony Cozzie, Herman Schmit, Larry Pileggi Center for Silicon Systems Implementation Carnegie Mellon University 1

Outline q Overview of VPGA q q CLB exploration of Look-Up Table sizes q q q 2 Area Model Delay Model Results Interconnect exploration q q Exploring the area between ASICs and Programmable ICs. Switch Block Crossbar Results Conclusion Carnegie Mellon University Center for Silicon System Implementation

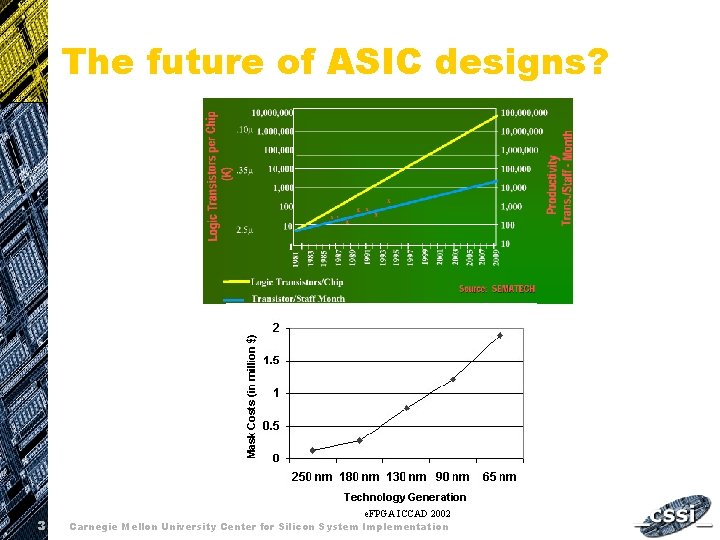

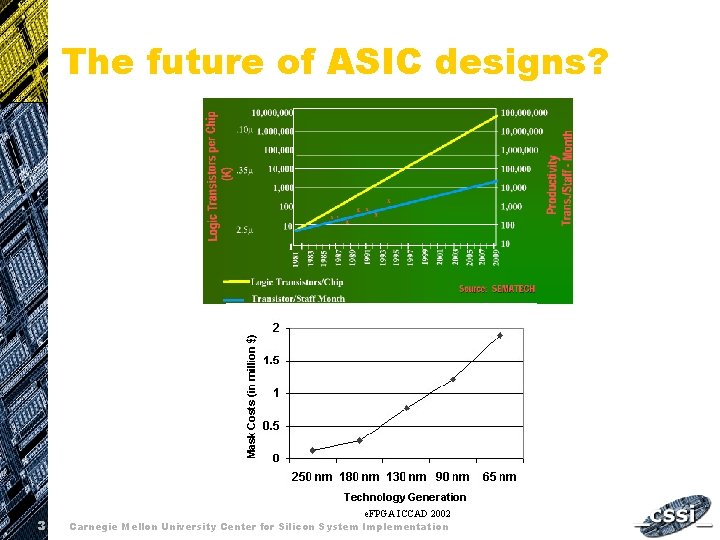

The future of ASIC designs? 3 e. FPGA ICCAD 2002 Carnegie Mellon University Center for Silicon System Implementation

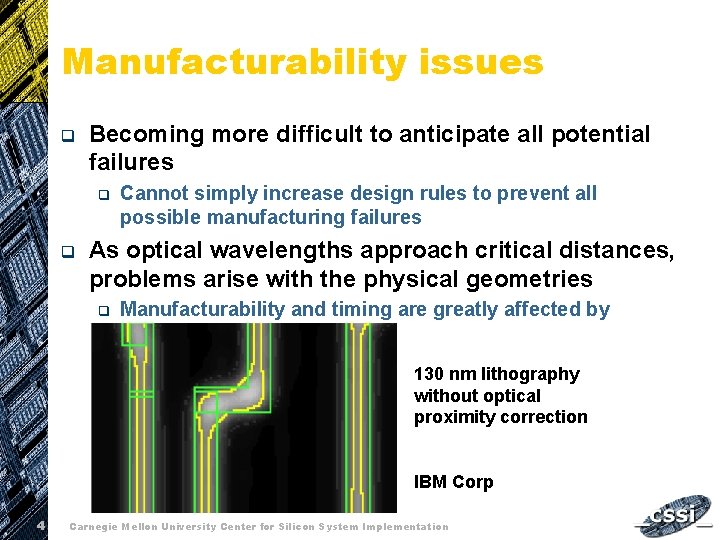

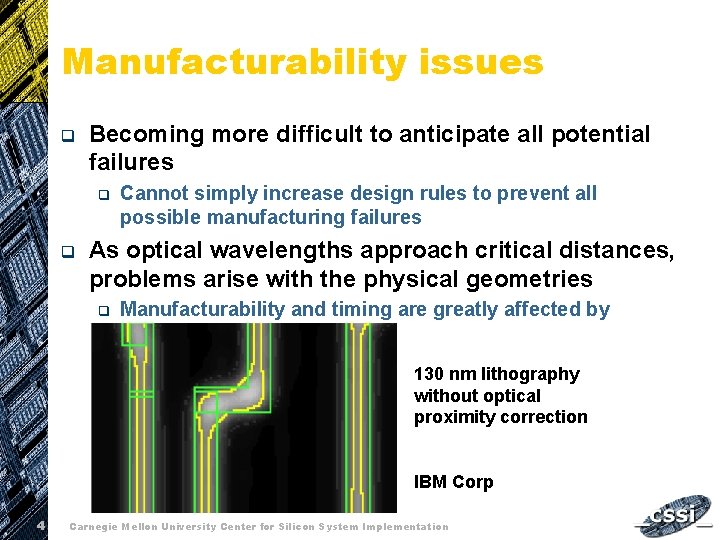

Manufacturability issues q Becoming more difficult to anticipate all potential failures q q Cannot simply increase design rules to prevent all possible manufacturing failures As optical wavelengths approach critical distances, problems arise with the physical geometries q Manufacturability and timing are greatly affected by process variations 130 nm lithography without optical proximity correction IBM Corp 4 Carnegie Mellon University Center for Silicon System Implementation

Programmable ICs q q 5 Programmable ICs combat the problem facing ASICs by offering numerous advantages P Regular geometrical patterns P Predictability P Built-in testability P Reprogrammability With advantages comes critical disadvantages Lower performance Higher power Larger chip area Carnegie Mellon University Center for Silicon System Implementation

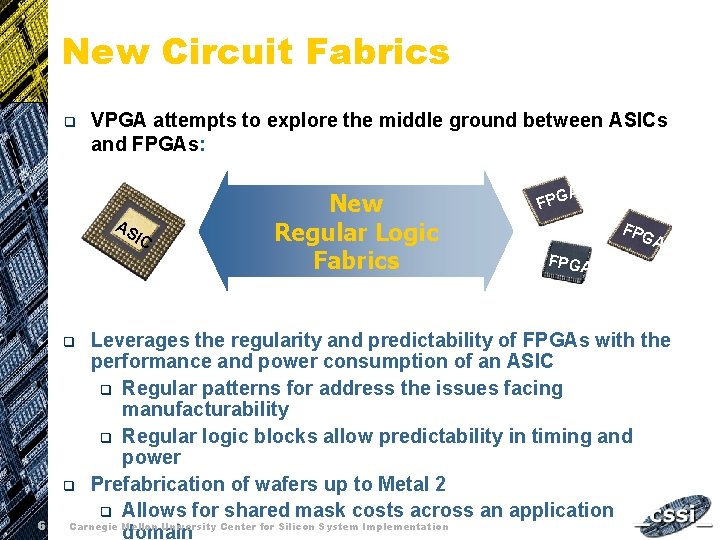

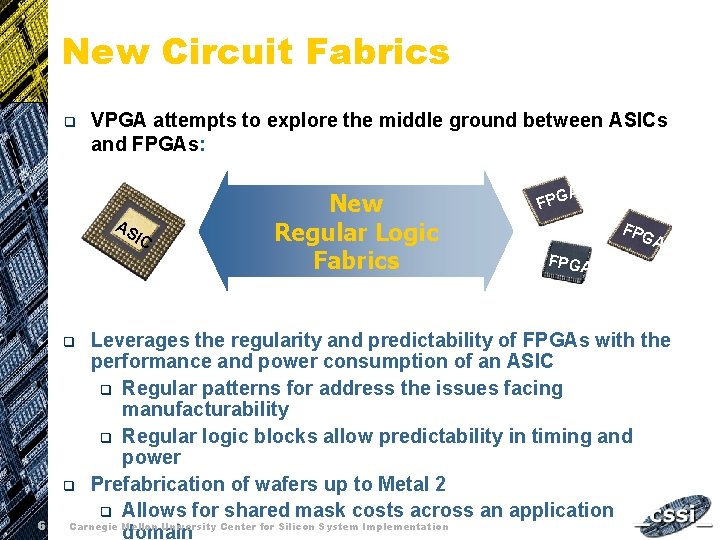

New Circuit Fabrics q VPGA attempts to explore the middle ground between ASICs and FPGAs: AS IC A FPGA Leverages the regularity and predictability of FPGAs with the performance and power consumption of an ASIC q Regular patterns for address the issues facing manufacturability q Regular logic blocks allow predictability in timing and power q Prefabrication of wafers up to Metal 2 q Allows for shared mask costs across an application Carnegie Mellon University Center for Silicon System Implementation domain q 6 New Regular Logic Fabrics

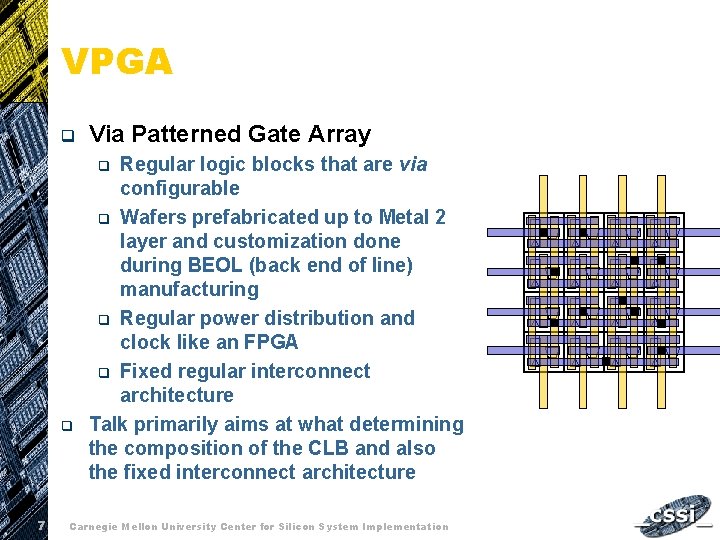

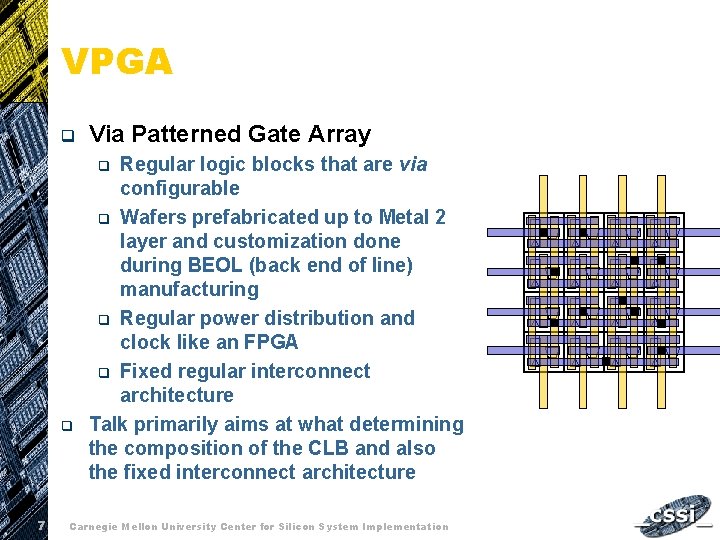

VPGA q Via Patterned Gate Array Regular logic blocks that are via configurable q Wafers prefabricated up to Metal 2 layer and customization done during BEOL (back end of line) manufacturing q Regular power distribution and clock like an FPGA q Fixed regular interconnect architecture Talk primarily aims at what determining the composition of the CLB and also the fixed interconnect architecture q q 7 Carnegie Mellon University Center for Silicon System Implementation

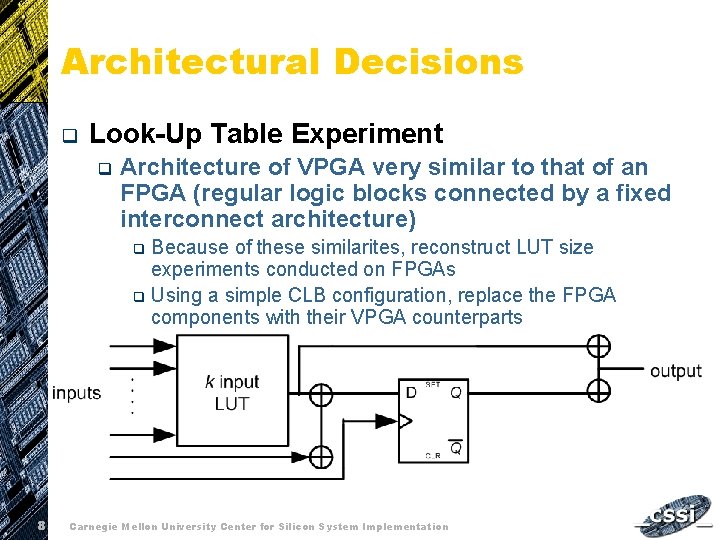

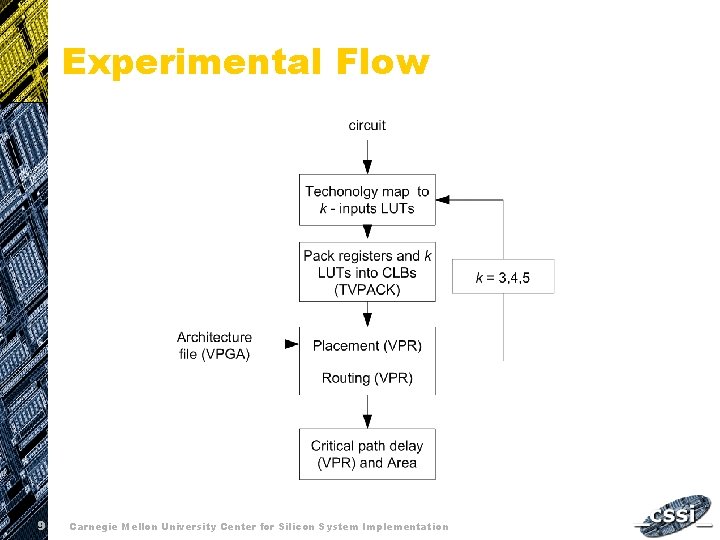

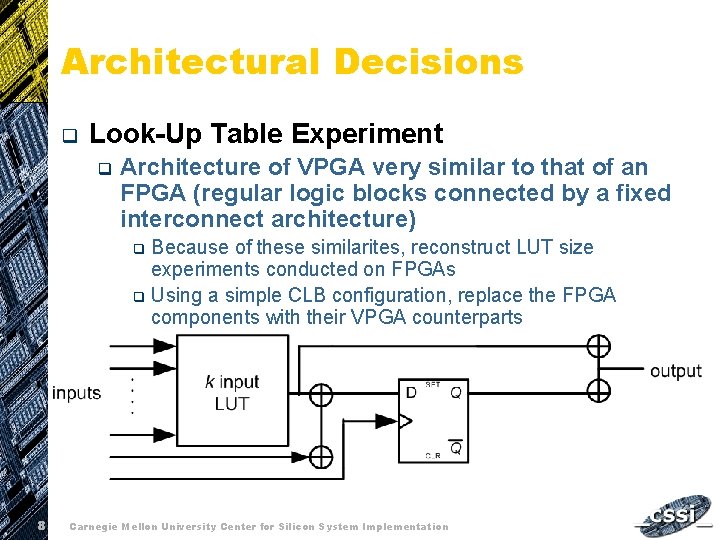

Architectural Decisions q Look-Up Table Experiment q Architecture of VPGA very similar to that of an FPGA (regular logic blocks connected by a fixed interconnect architecture) Because of these similarites, reconstruct LUT size experiments conducted on FPGAs q Using a simple CLB configuration, replace the FPGA components with their VPGA counterparts q 8 Carnegie Mellon University Center for Silicon System Implementation

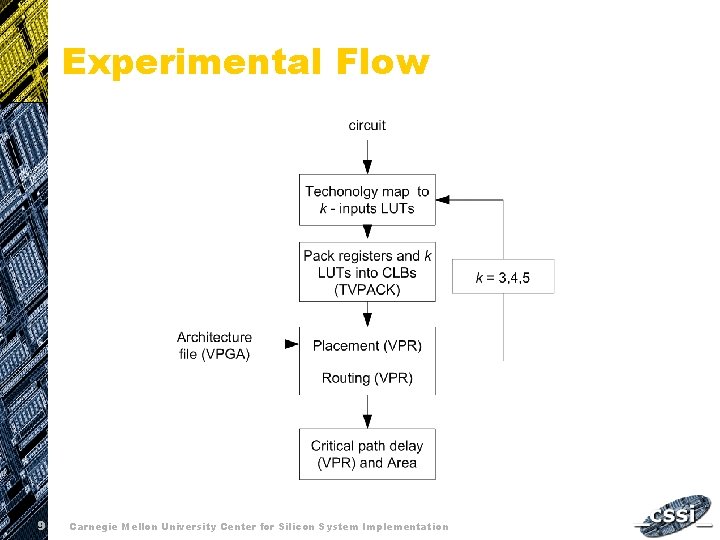

Experimental Flow 9 Carnegie Mellon University Center for Silicon System Implementation

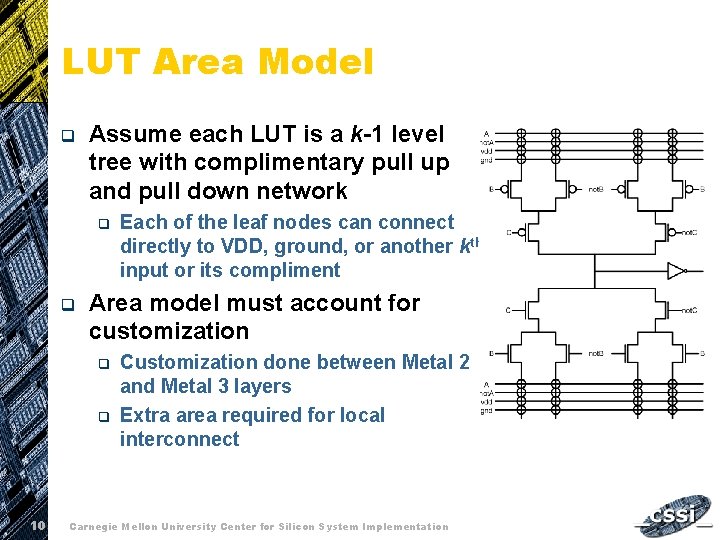

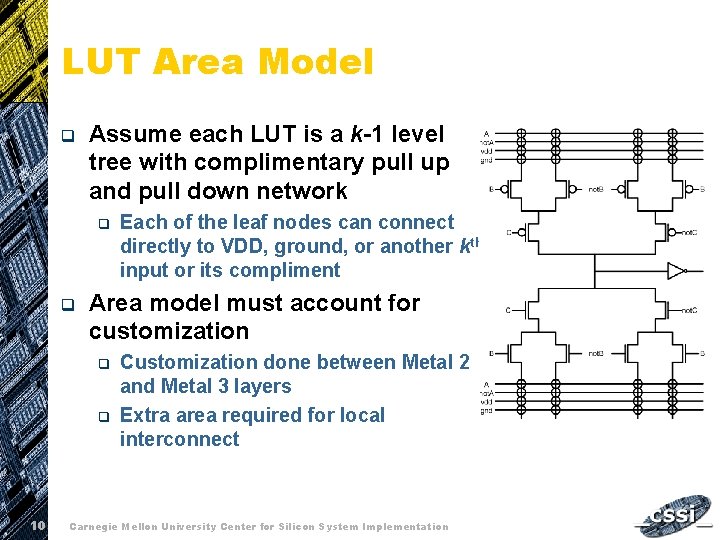

LUT Area Model q Assume each LUT is a k-1 level tree with complimentary pull up and pull down network q q Area model must account for customization q q 10 Each of the leaf nodes can connect directly to VDD, ground, or another kth input or its compliment Customization done between Metal 2 and Metal 3 layers Extra area required for local interconnect Carnegie Mellon University Center for Silicon System Implementation

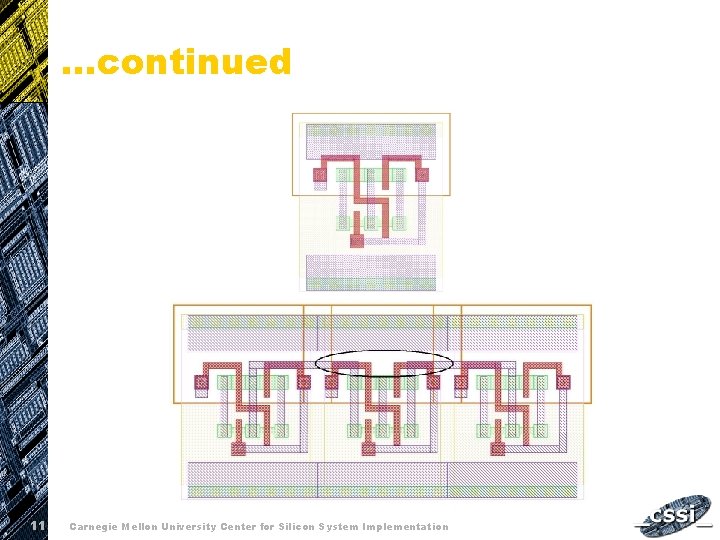

…continued 11 Carnegie Mellon University Center for Silicon System Implementation

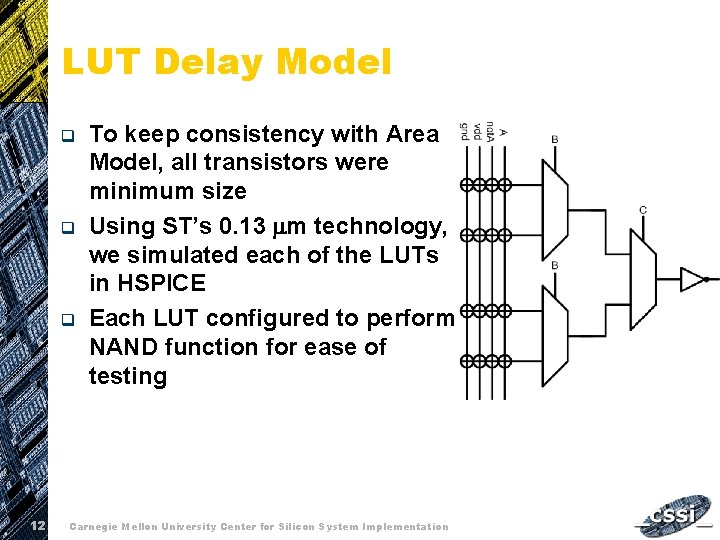

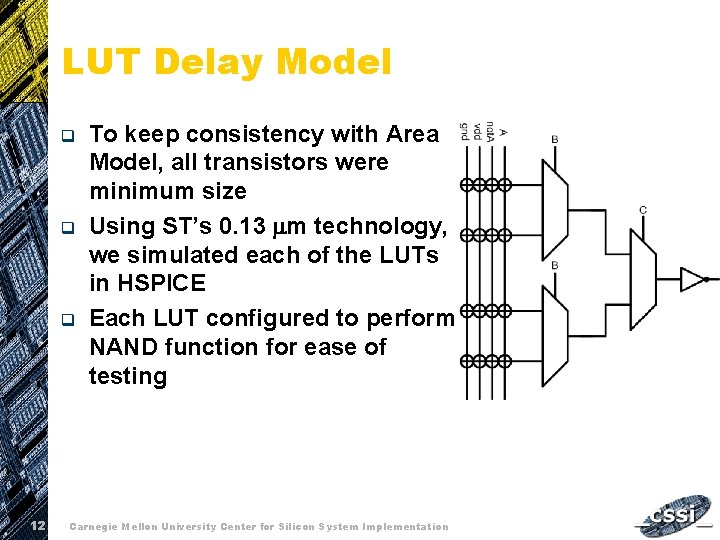

LUT Delay Model q q q 12 To keep consistency with Area Model, all transistors were minimum size Using ST’s 0. 13 mm technology, we simulated each of the LUTs in HSPICE Each LUT configured to perform NAND function for ease of testing Carnegie Mellon University Center for Silicon System Implementation

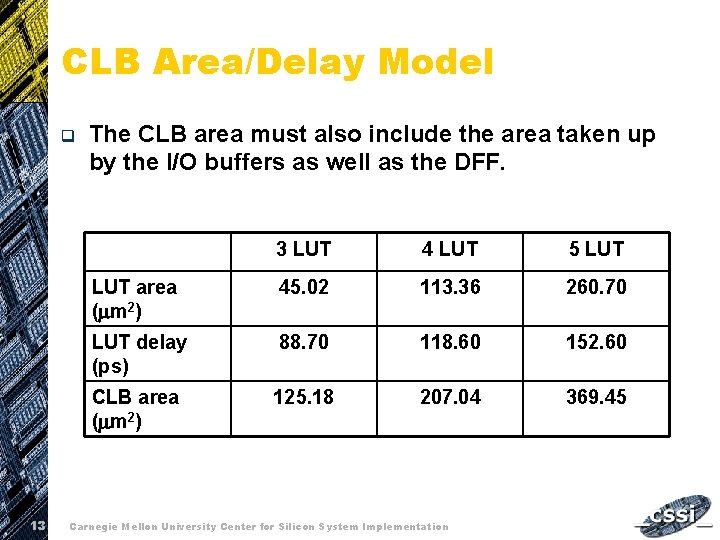

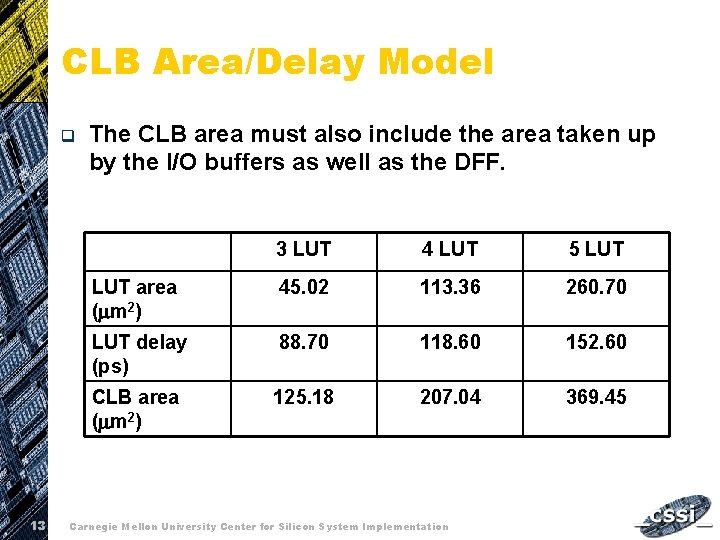

CLB Area/Delay Model q 13 The CLB area must also include the area taken up by the I/O buffers as well as the DFF. 3 LUT 4 LUT 5 LUT area (mm 2) 45. 02 113. 36 260. 70 LUT delay (ps) 88. 70 118. 60 152. 60 CLB area (mm 2) 125. 18 207. 04 369. 45 Carnegie Mellon University Center for Silicon System Implementation

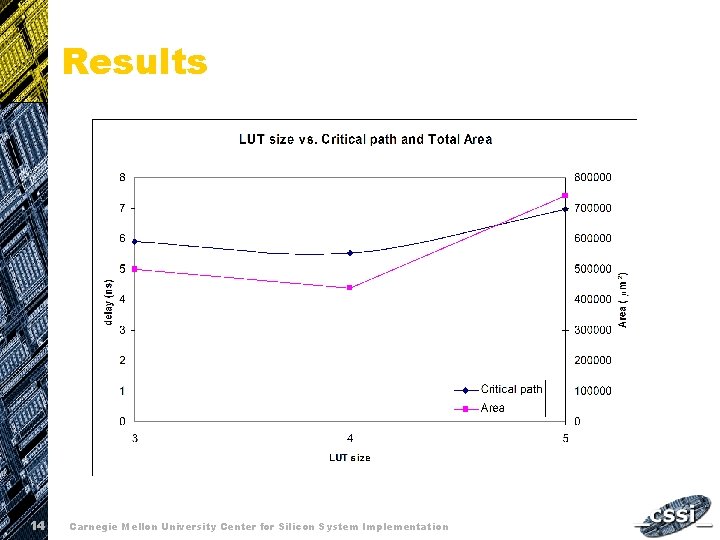

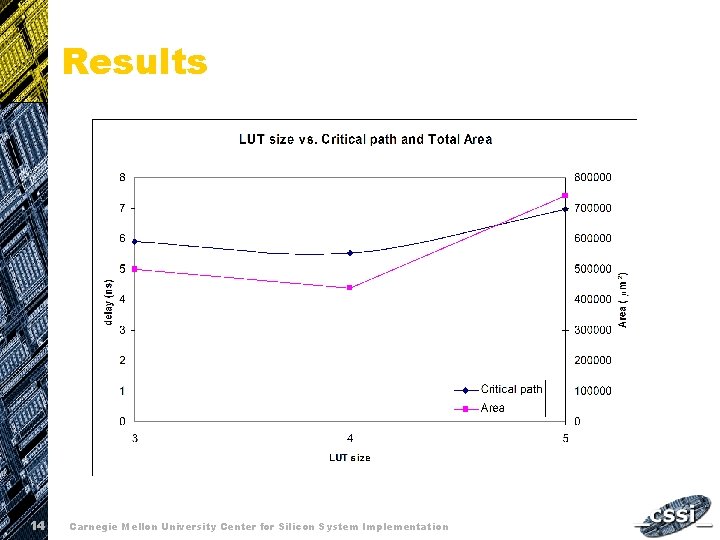

Results 14 Carnegie Mellon University Center for Silicon System Implementation

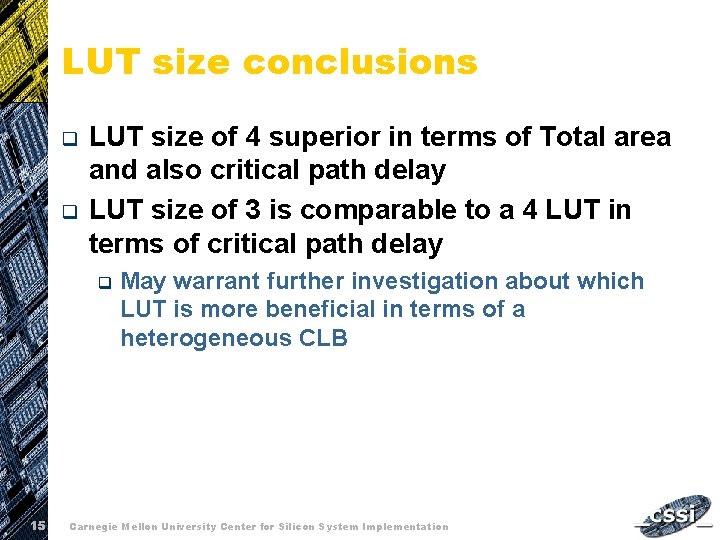

LUT size conclusions q q LUT size of 4 superior in terms of Total area and also critical path delay LUT size of 3 is comparable to a 4 LUT in terms of critical path delay q 15 May warrant further investigation about which LUT is more beneficial in terms of a heterogeneous CLB Carnegie Mellon University Center for Silicon System Implementation

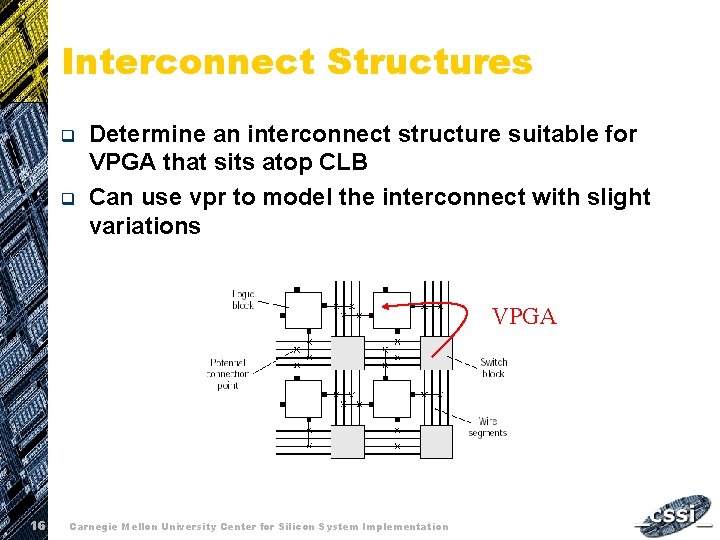

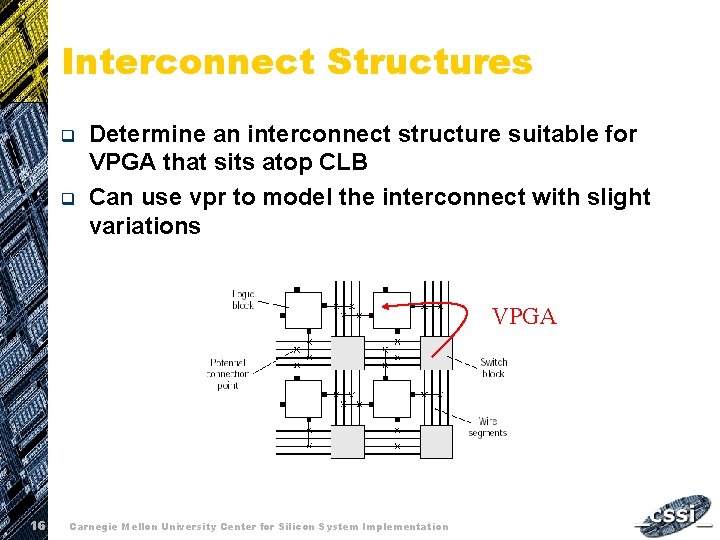

Interconnect Structures q q Determine an interconnect structure suitable for VPGA that sits atop CLB Can use vpr to model the interconnect with slight variations VPGA 16 Carnegie Mellon University Center for Silicon System Implementation

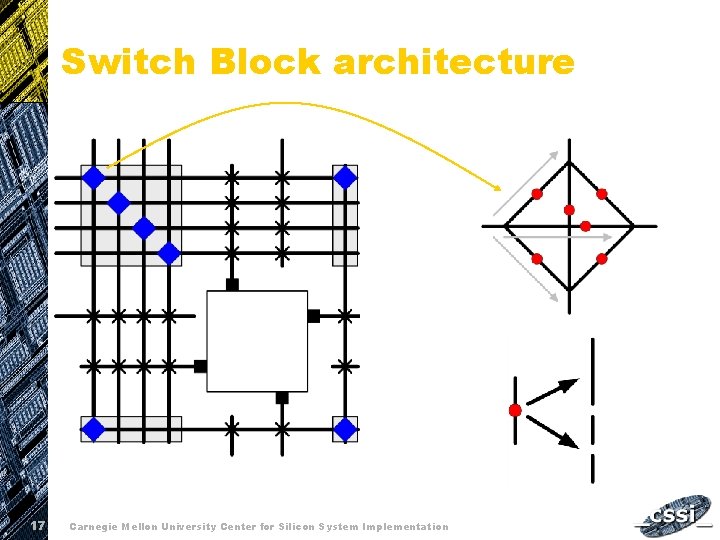

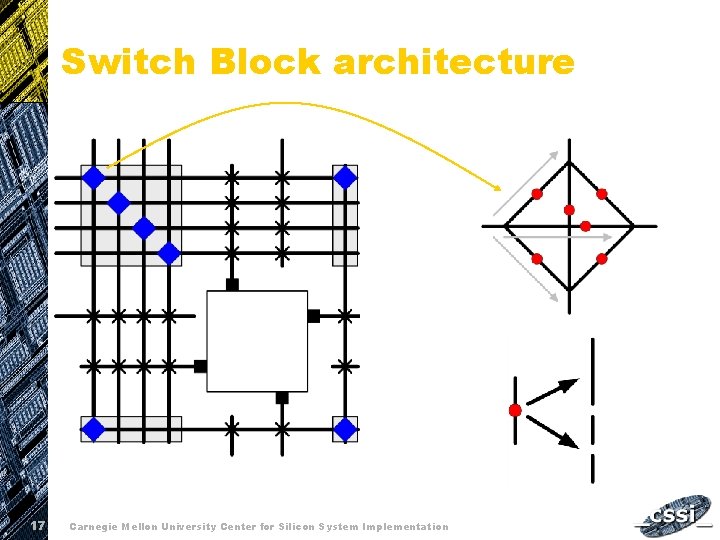

Switch Block architecture 17 Carnegie Mellon University Center for Silicon System Implementation

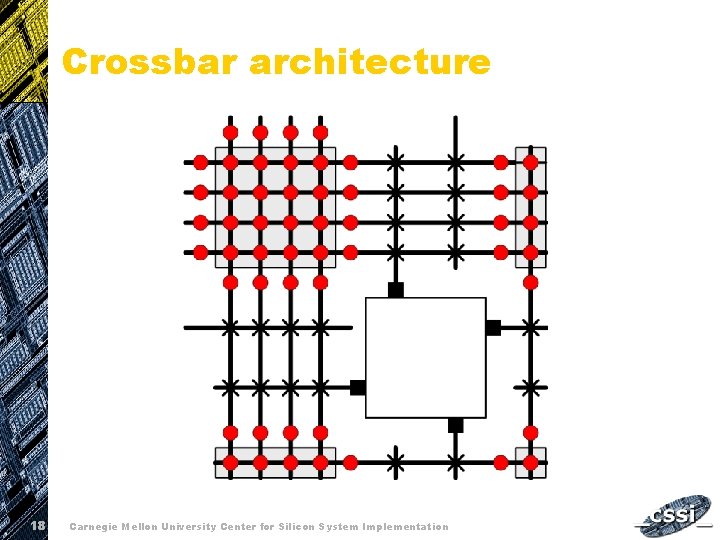

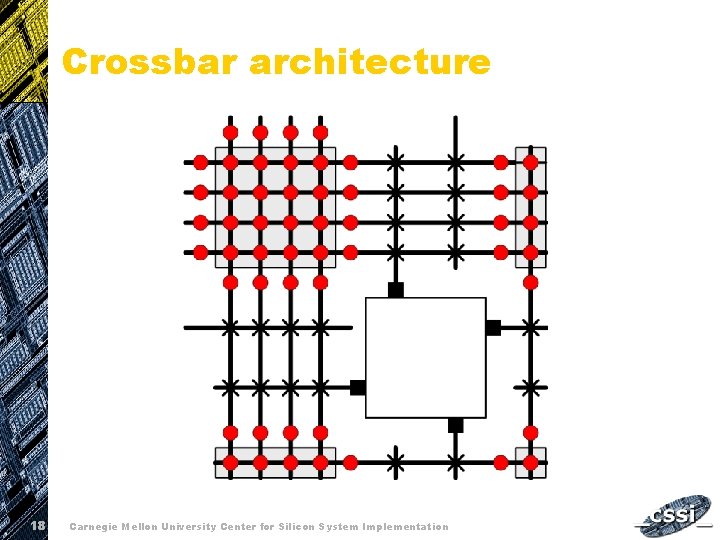

Crossbar architecture 18 Carnegie Mellon University Center for Silicon System Implementation

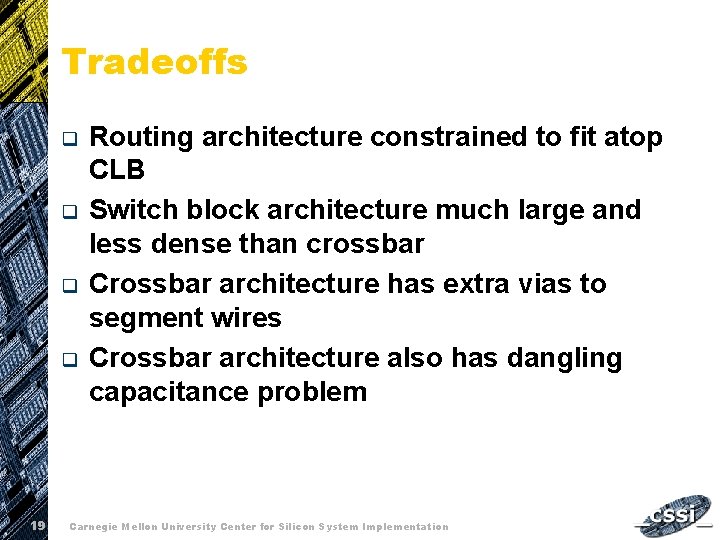

Tradeoffs q q 19 Routing architecture constrained to fit atop CLB Switch block architecture much large and less dense than crossbar Crossbar architecture has extra vias to segment wires Crossbar architecture also has dangling capacitance problem Carnegie Mellon University Center for Silicon System Implementation

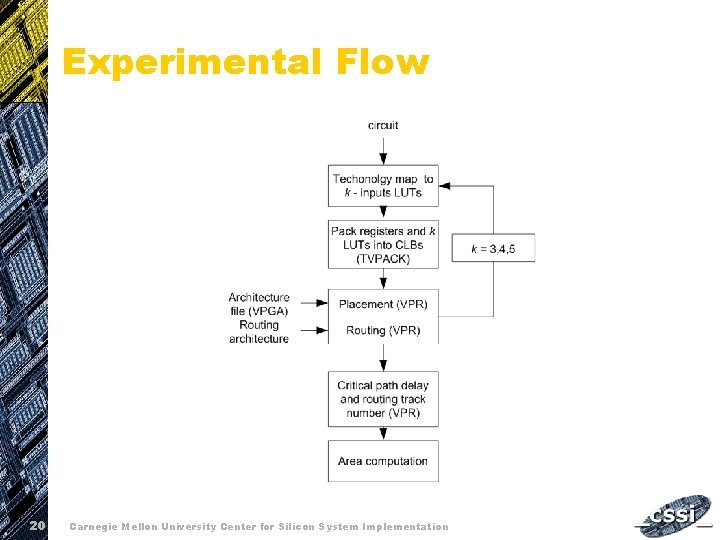

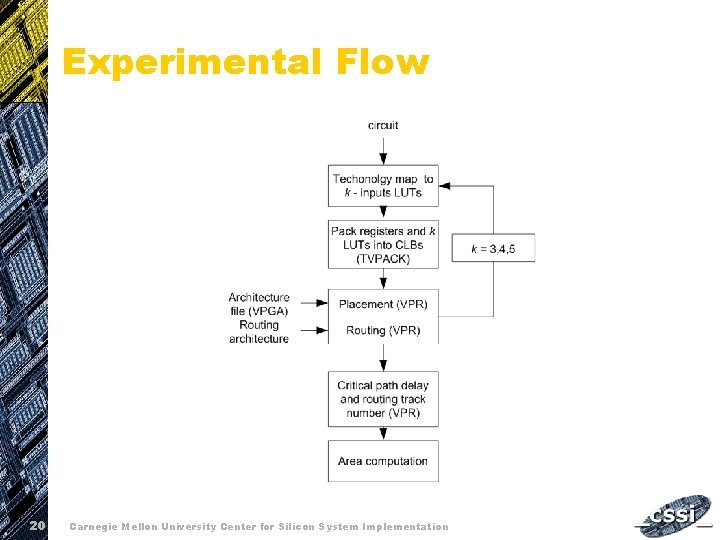

Experimental Flow 20 Carnegie Mellon University Center for Silicon System Implementation

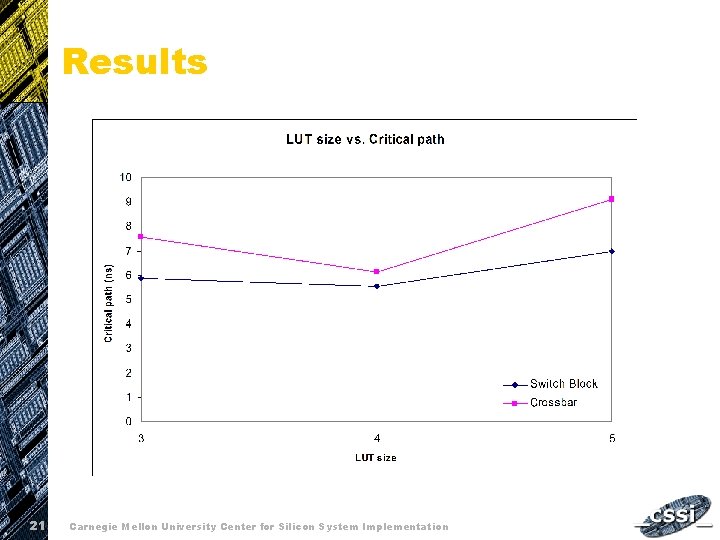

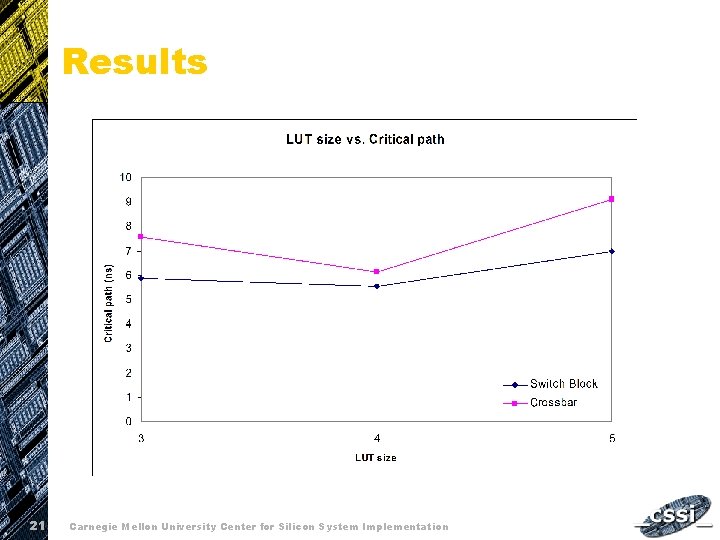

Results 21 Carnegie Mellon University Center for Silicon System Implementation

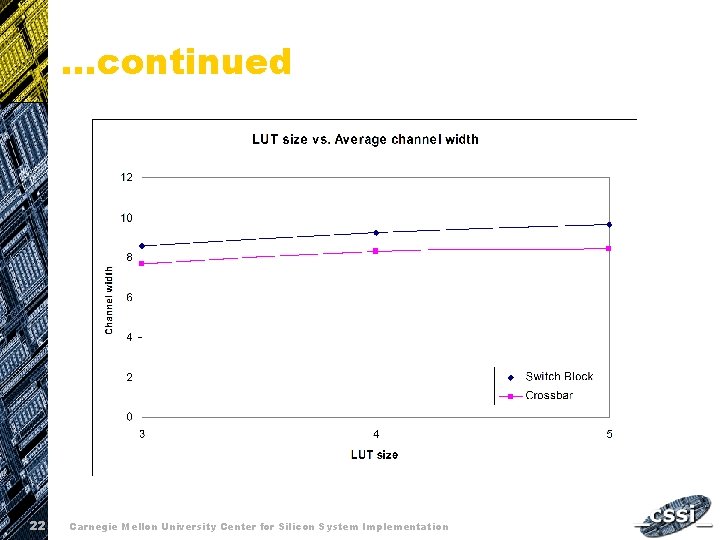

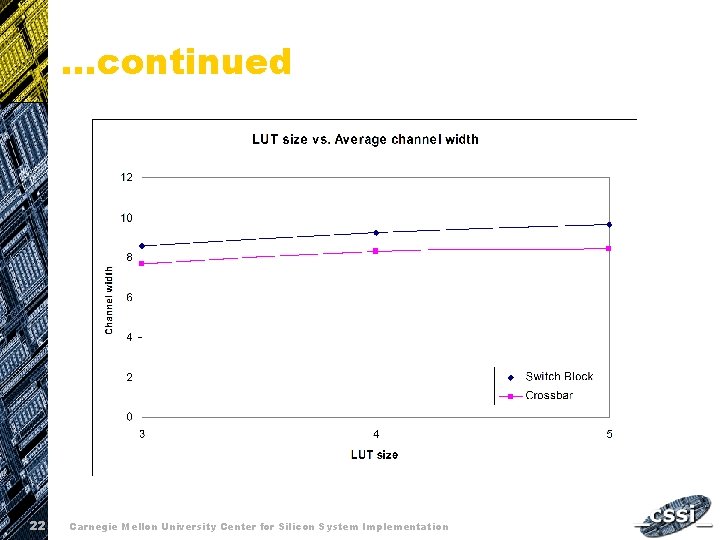

…continued 22 Carnegie Mellon University Center for Silicon System Implementation

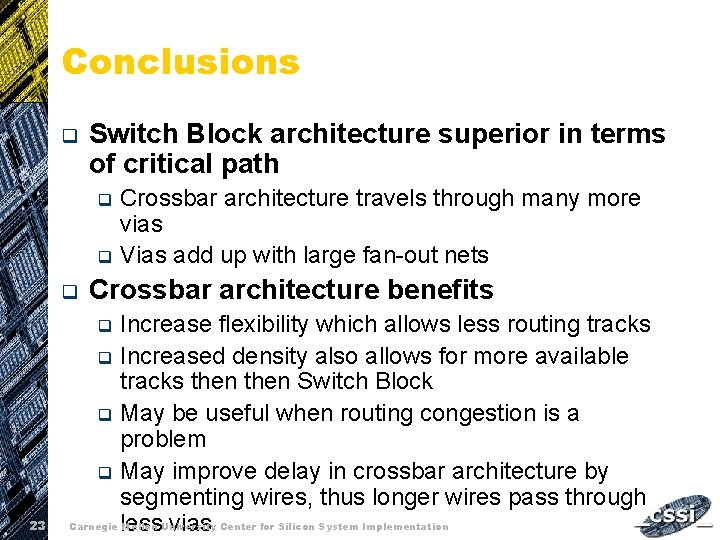

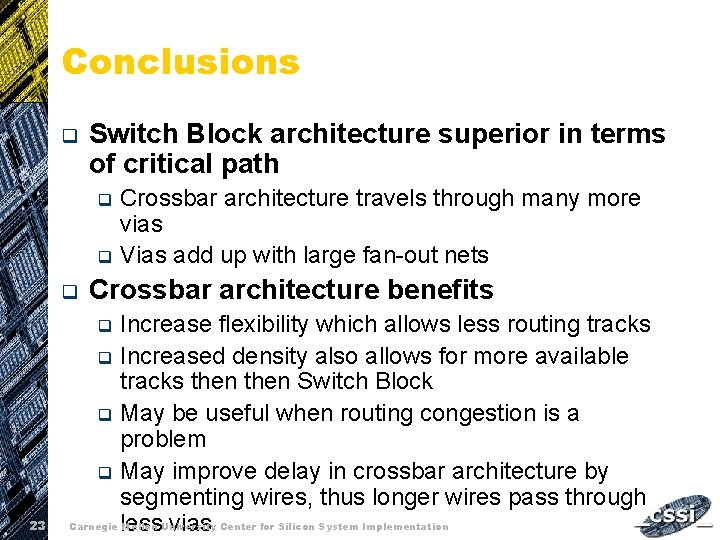

Conclusions q Switch Block architecture superior in terms of critical path Crossbar architecture travels through many more vias q Vias add up with large fan-out nets q q Crossbar architecture benefits Increase flexibility which allows less routing tracks q Increased density also allows for more available tracks then Switch Block q May be useful when routing congestion is a problem q May improve delay in crossbar architecture by segmenting wires, thus longer wires pass through Carnegie less Mellon University vias Center for Silicon System Implementation q 23