An adaptable FPGAbased System for Regular Expression Matching

An adaptable FPGA-based System for Regular Expression Matching Authors: Ivano Bonesana, Marco Paolieri, Marco D. Santambrogio Publisher: DATE (Design, Automation and Test in Europe) 2008 Present: Chung-Chan Wu Date: April 23 2008 Department of Computer Science and Information Engineering National Cheng Kung University, Taiwan R. O. C. 1

Outline l l l Introduction Re. CPU Framework Flow Re. CPU Instruction Structure Architecture Description Experimental Result 2

Introduction l l l RE:Regular Expression We do not build either Deterministic nor Nondeterministic Finite Automaton of the RE The architecture is optimized to execute computations in a parallel and pipelined way VLIW design style (Very long instruction word ) We developed a compiler to translate REs into bitwise instructions. 3

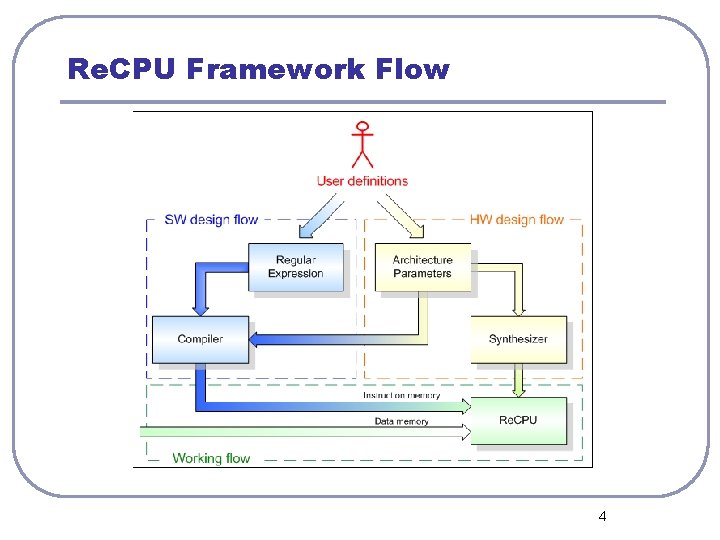

Re. CPU Framework Flow 4

Regular Expression 5

Compilation Phase l By modifying the number of clusters (parameters) in the Re. CPU • • • l Performance Power area The compiler • • written in Python starting from the high level description of the RE generates the files be loaded in the instruction memory 6

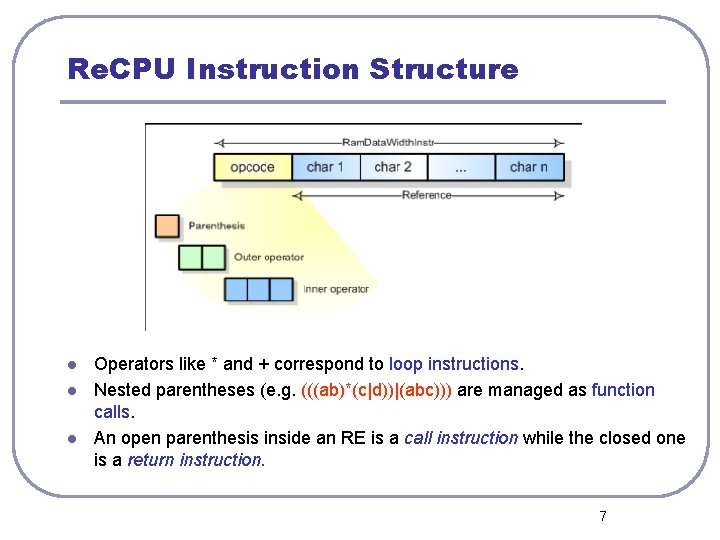

Re. CPU Instruction Structure l l l Operators like * and + correspond to loop instructions. Nested parentheses (e. g. (((ab)*(c|d))|(abc))) are managed as function calls. An open parenthesis inside an RE is a call instruction while the closed one is a return instruction. 7

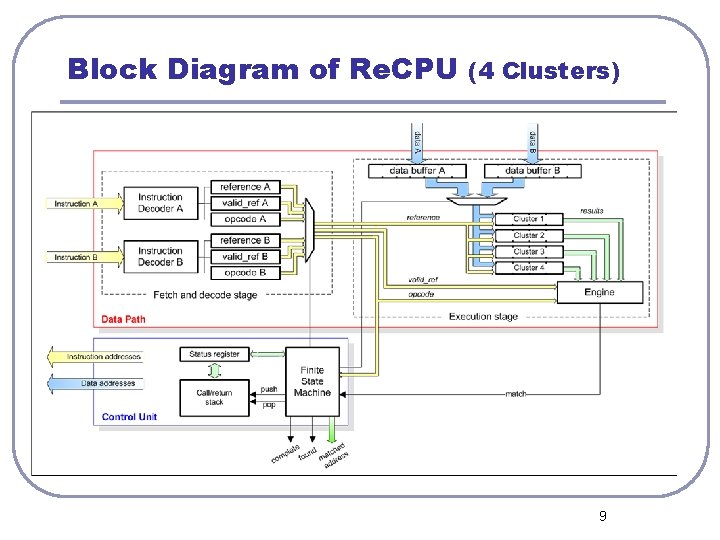

Architecture Description l l Re. CPU uses two separate memories: • • Data memory for the input text instruction memory for the RE In the Data Path are placed all the different parallel comparators organized in Clusters. Cluster Width:The total number of elements in a cluster The processor is composed of several Clusters - the total number is indicated as NCluster 8

Block Diagram of Re. CPU (4 Clusters) 9

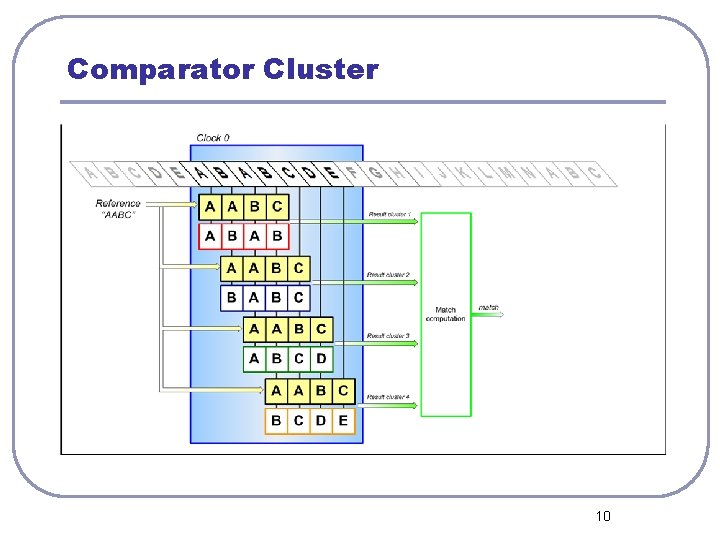

Comparator Cluster 10

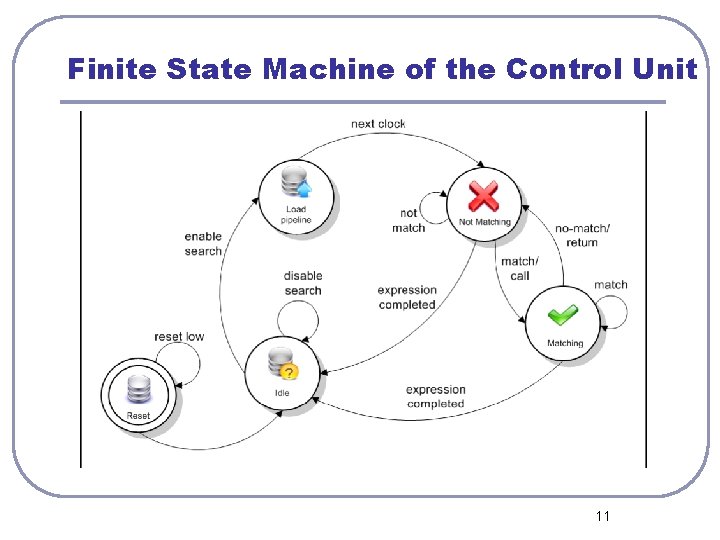

Finite State Machine of the Control Unit 11

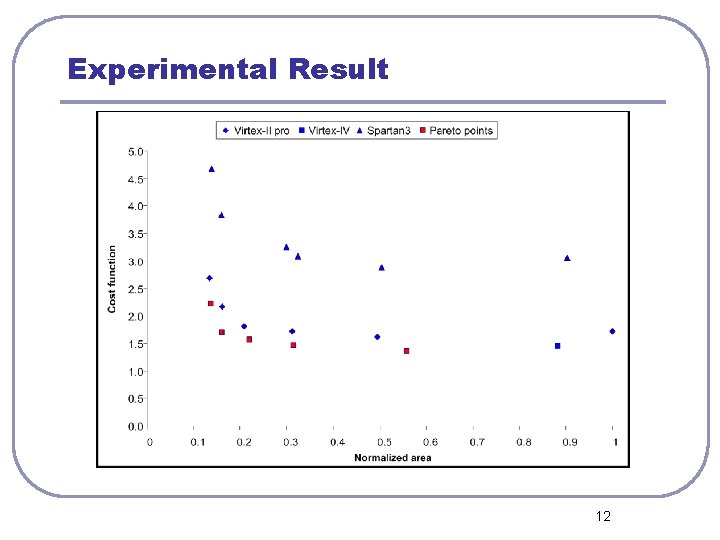

Experimental Result 12

Experimental Result 13

- Slides: 13