ALU 2 Multiplication Division a shifting register method

- Slides: 9

ALU (2) Multiplication & Division a ) shifting register method b ) booth’s Representation b ) Parallel array Multiplication c ) parallel Array Divider By : Maskie Z. Oematan

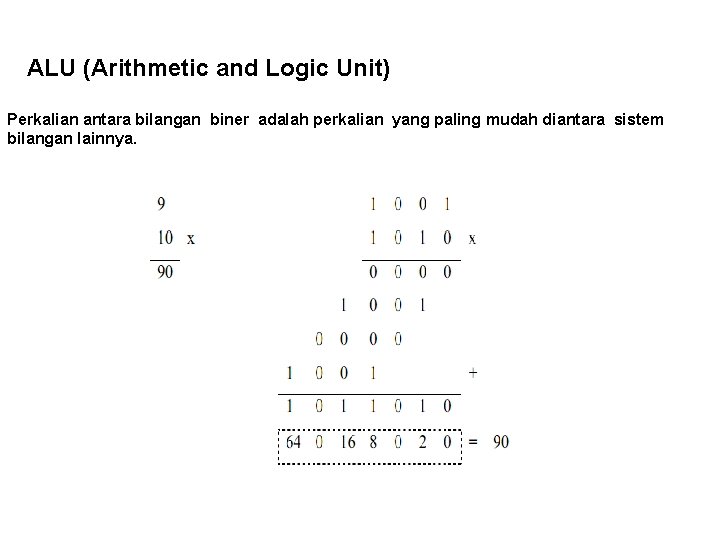

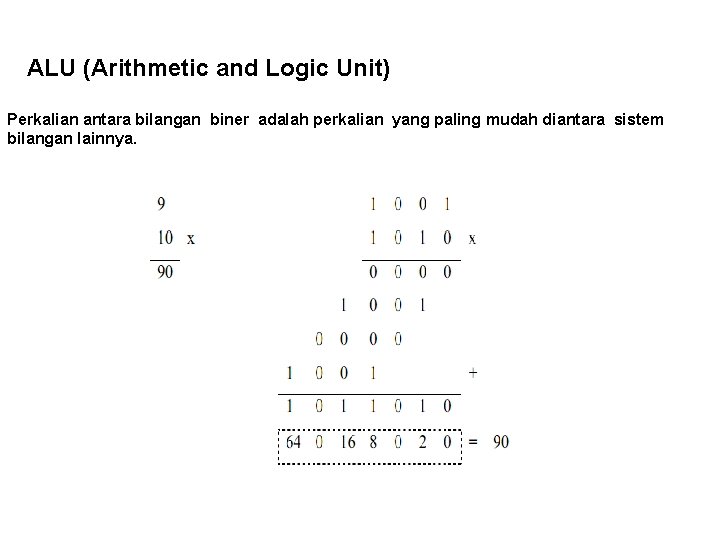

ALU (Arithmetic and Logic Unit) Perkalian antara bilangan biner adalah perkalian yang paling mudah diantara sistem bilangan lainnya.

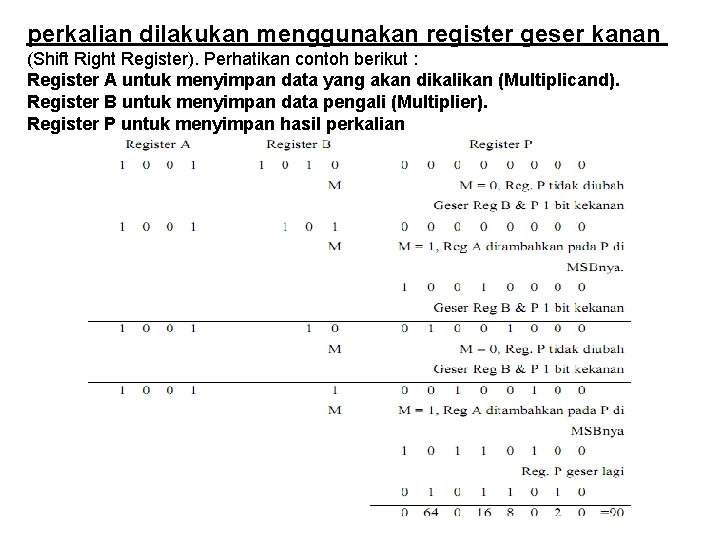

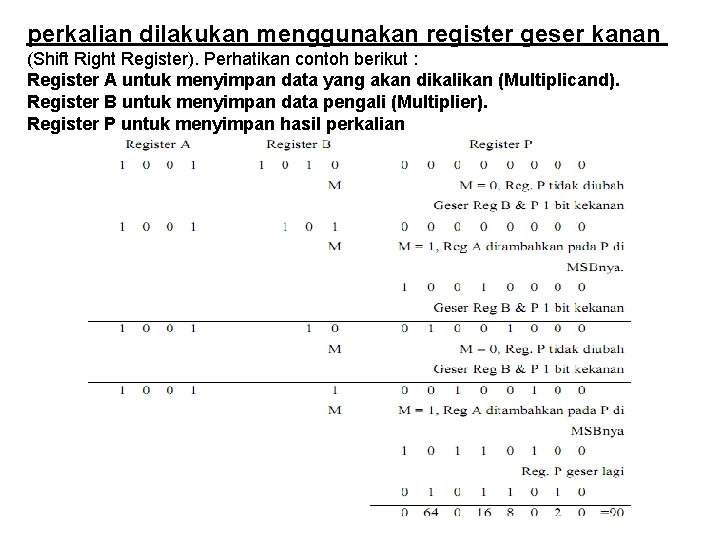

perkalian dilakukan menggunakan register geser kanan (Shift Right Register). Perhatikan contoh berikut : Register A untuk menyimpan data yang akan dikalikan (Multiplicand). Register B untuk menyimpan data pengali (Multiplier). Register P untuk menyimpan hasil perkalian

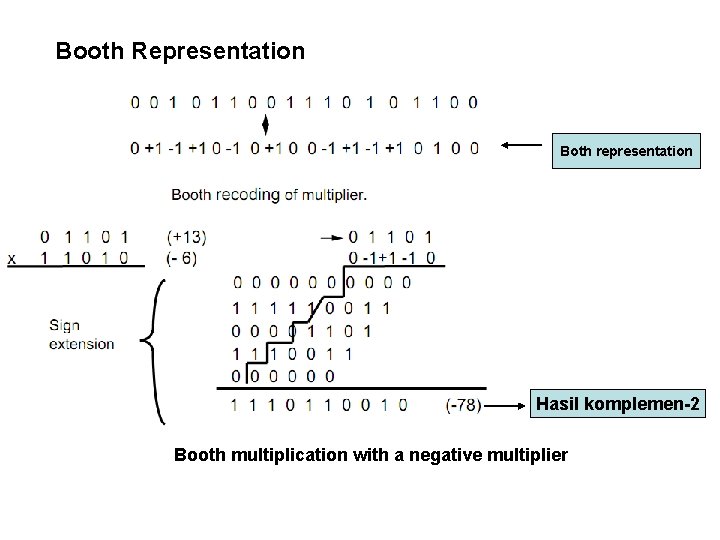

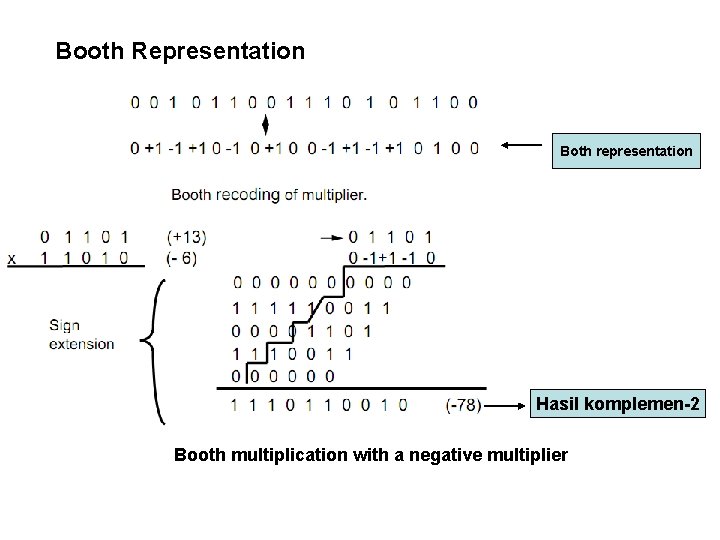

Booth Representation Both representation Hasil komplemen-2 Booth multiplication with a negative multiplier

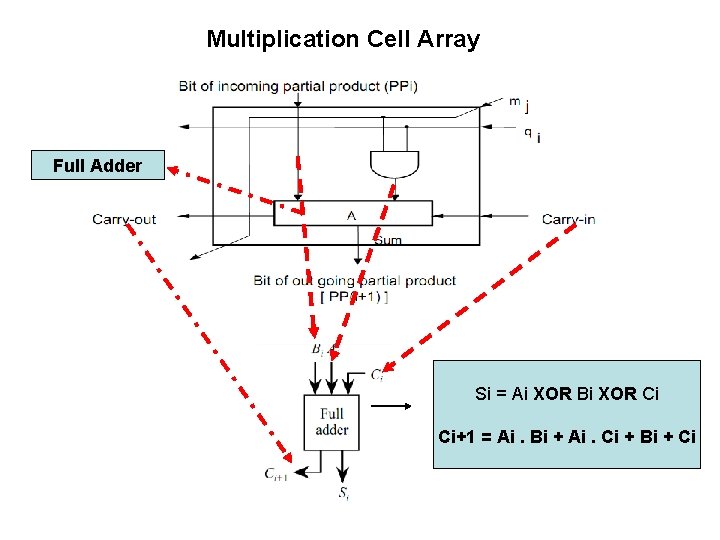

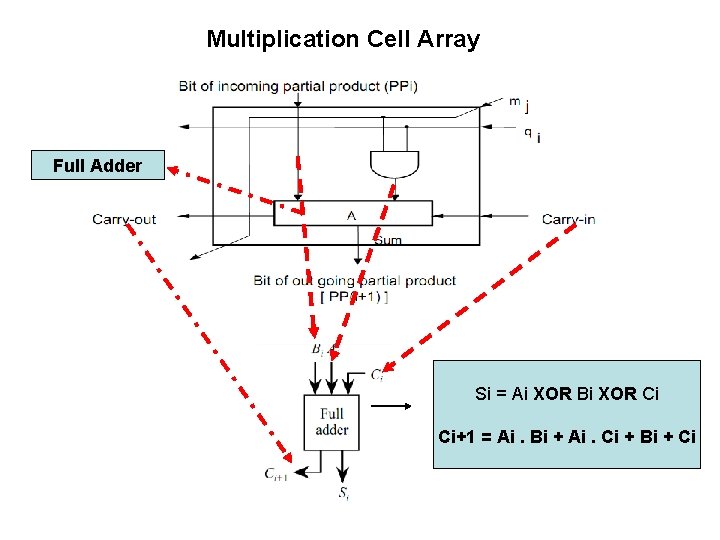

Multiplication Cell Array Full Adder Si = Ai XOR Bi XOR Ci Ci+1 = Ai. Bi + Ai. Ci + Bi + Ci

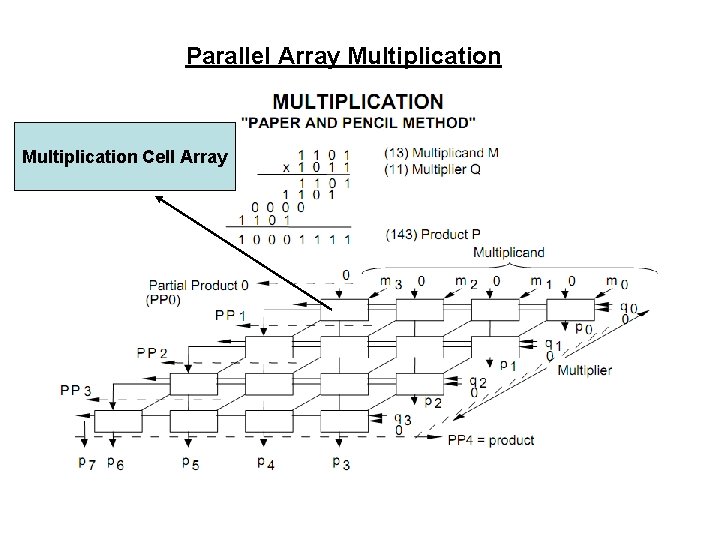

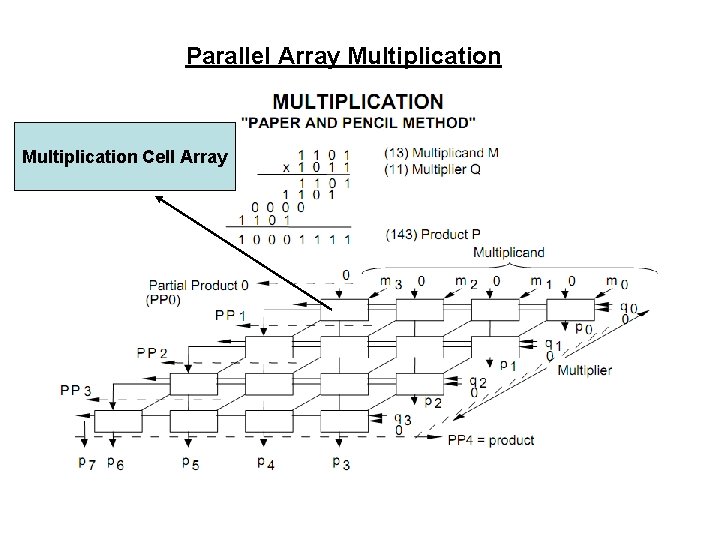

Parallel Array Multiplication Cell Array

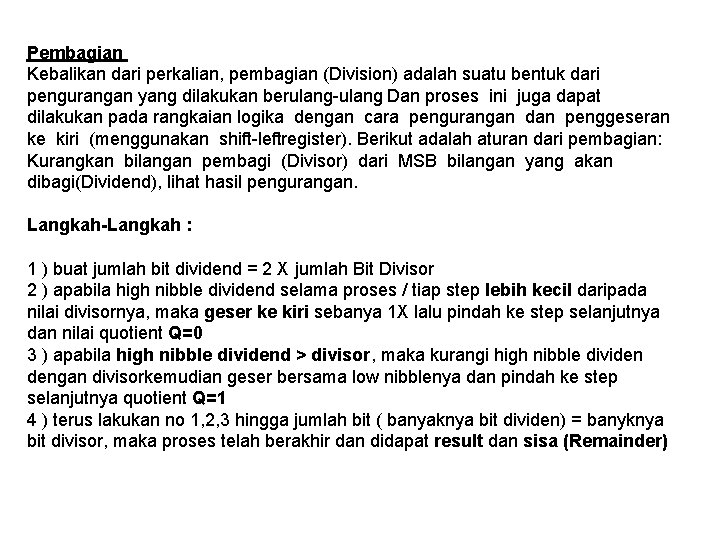

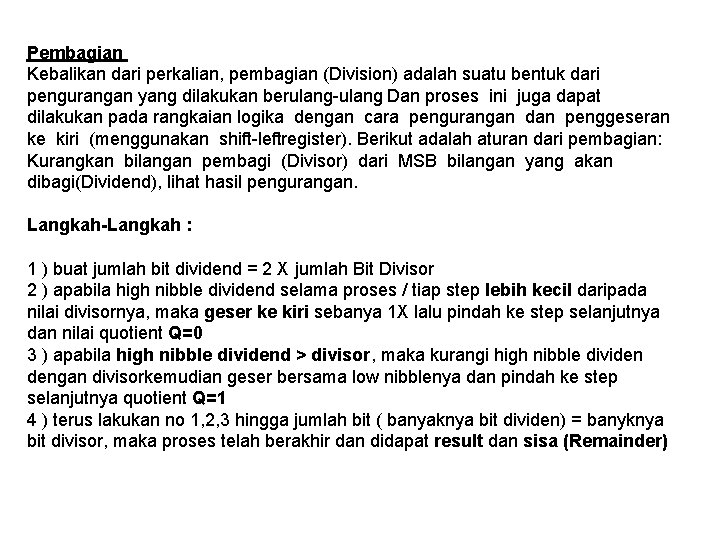

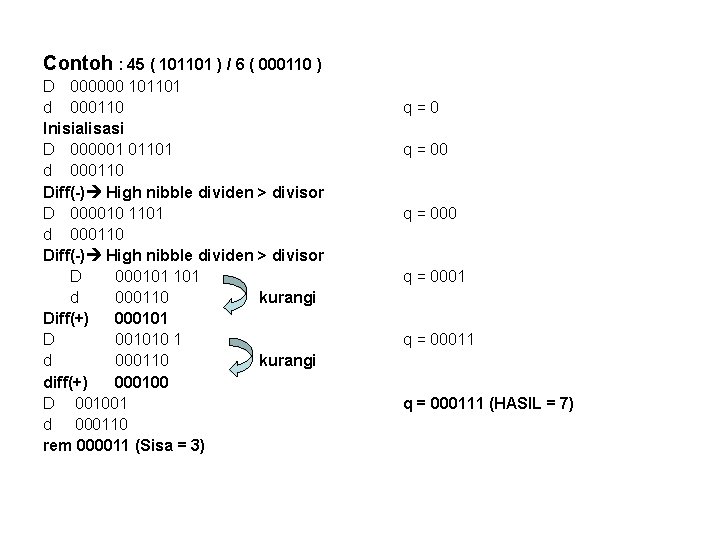

Pembagian Kebalikan dari perkalian, pembagian (Division) adalah suatu bentuk dari pengurangan yang dilakukan berulang. Dan proses ini juga dapat dilakukan pada rangkaian logika dengan cara pengurangan dan penggeseran ke kiri (menggunakan shift leftregister). Berikut adalah aturan dari pembagian: Kurangkan bilangan pembagi (Divisor) dari MSB bilangan yang akan dibagi(Dividend), lihat hasil pengurangan. Langkah-Langkah : 1 ) buat jumlah bit dividend = 2 X jumlah Bit Divisor 2 ) apabila high nibble dividend selama proses / tiap step lebih kecil daripada nilai divisornya, maka geser ke kiri sebanya 1 X lalu pindah ke step selanjutnya dan nilai quotient Q=0 3 ) apabila high nibble dividend > divisor, maka kurangi high nibble dividen dengan divisorkemudian geser bersama low nibblenya dan pindah ke step selanjutnya quotient Q=1 4 ) terus lakukan no 1, 2, 3 hingga jumlah bit ( banyaknya bit dividen) = banyknya bit divisor, maka proses telah berakhir dan didapat result dan sisa (Remainder)

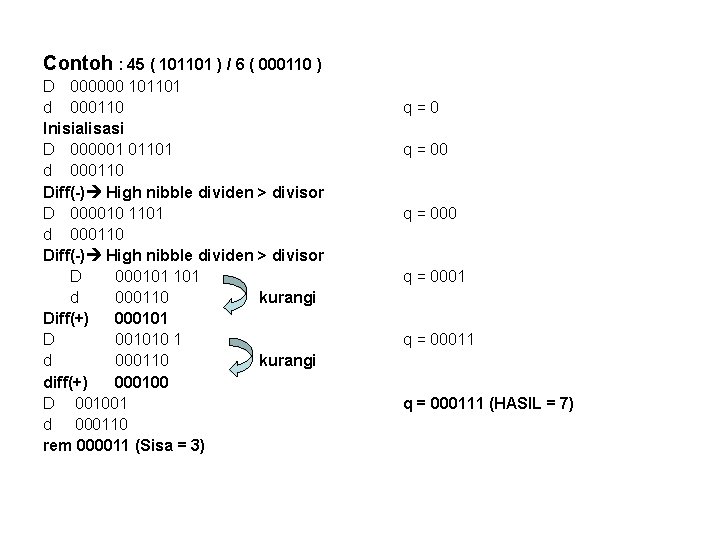

Contoh : 45 ( 101101 ) / 6 ( 000110 ) D 000000 101101 d 000110 Inisialisasi D 000001 01101 d 000110 Diff(-) High nibble dividen > divisor D 000010 1101 d 000110 Diff(-) High nibble dividen > divisor D 000101 d 000110 kurangi Diff(+) 000101 D 001010 1 d 000110 kurangi diff(+) 000100 D 001001 d 000110 rem 000011 (Sisa = 3) q=0 q = 00011 q = 000111 (HASIL = 7)

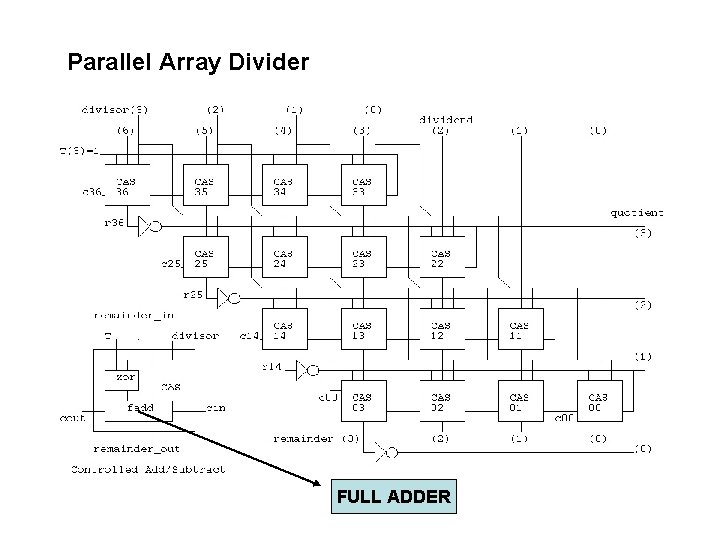

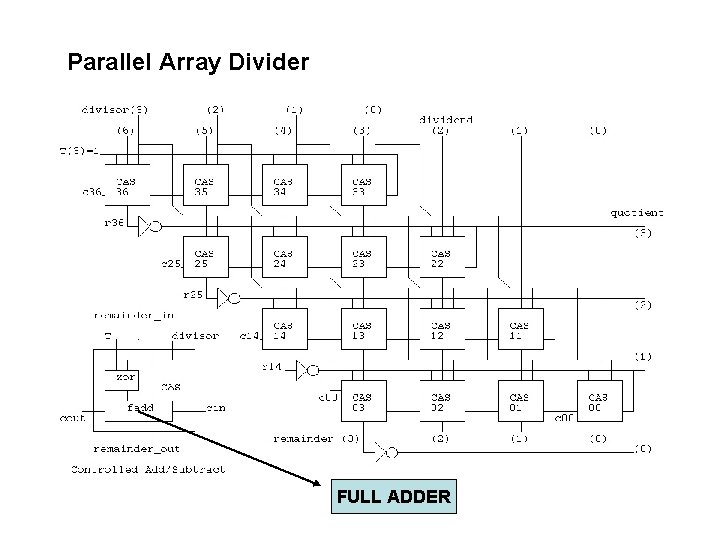

Parallel Array Divider FULL ADDER