ALICETRD digital chip Falk Lesser Kirchhoff Institut fr

- Slides: 27

ALICE-TRD digital chip Falk Lesser Kirchhoff Institut für Physik lesser@kip. uni-heidelberg. de

Inhalt • • • 2 Ziele des ALICE-Experiments Das TRD-System Lineare Regression Implementierungsansätze Der Prozessorkern femto. Java 1 Projekt-Status

Ziele des ALICE-Experiments • • ALICE ist eines der vier großen Experimente am LHC Studien am Quark Gluonen Plasma (QGP) Ereignisrate beträgt 4*103 Kollisionen pro Sekunde (Pb + Pb) Teilchenmultiplizität von etwa 16000 Teilchen in der Akzeptanz des Detektors (zentrales Event) • Suche nach high pt Elektron-Positron Paaren (e+ e-) – Teilchen mit einem Transversalimpuls 3 Ge. V/c – 5 % aller zentralen Pb + Pb beinhalten e+e- -Paare – Identifizierung der Teilchen über die Ablenkung in r/ -Ebene – Ablenkung der gesuchten Teilchen < 2. 0 mm bei pt 3 Ge. V/c – ohne Trigger jährliche Produktion Y = 1000 • Trigger auf interessante Ereignisse 3

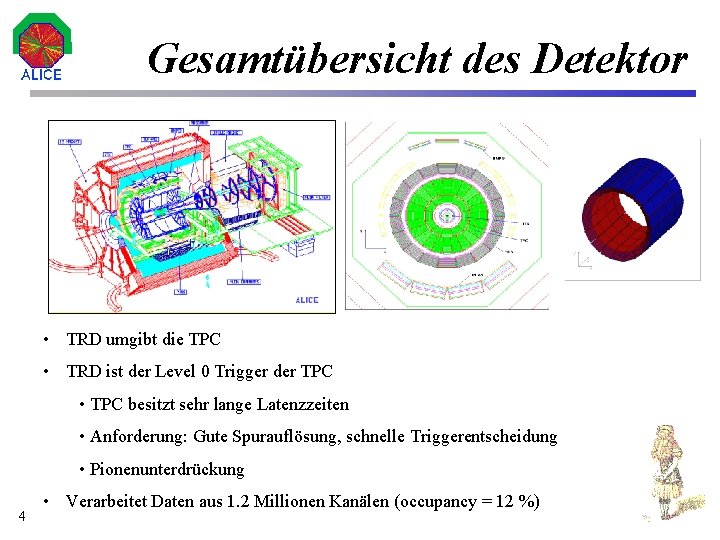

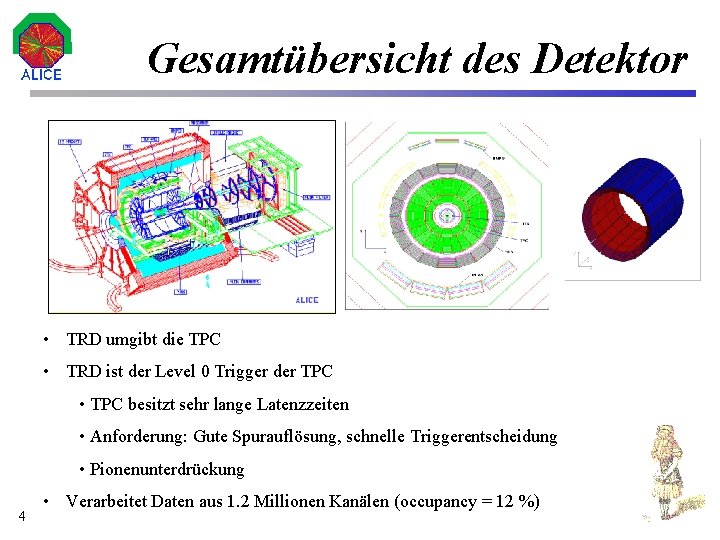

Gesamtübersicht des Detektor • TRD umgibt die TPC • TRD ist der Level 0 Trigger der TPC • TPC besitzt sehr lange Latenzzeiten • Anforderung: Gute Spurauflösung, schnelle Triggerentscheidung • Pionenunterdrückung 4 • Verarbeitet Daten aus 1. 2 Millionen Kanälen (occupancy = 12 %)

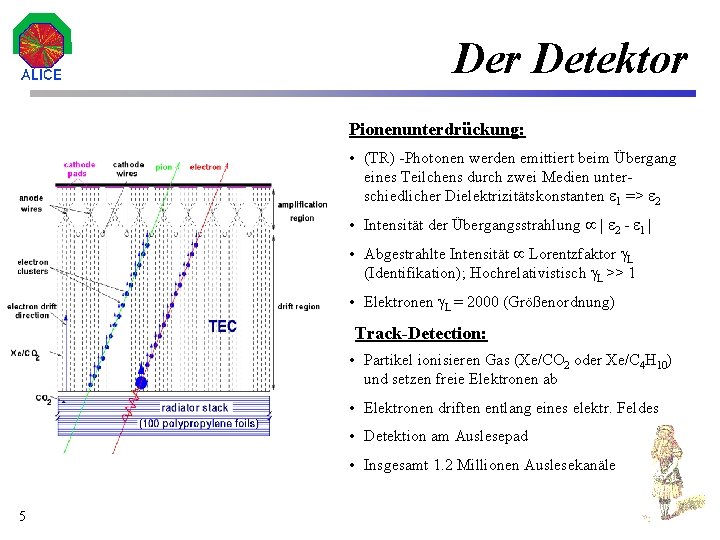

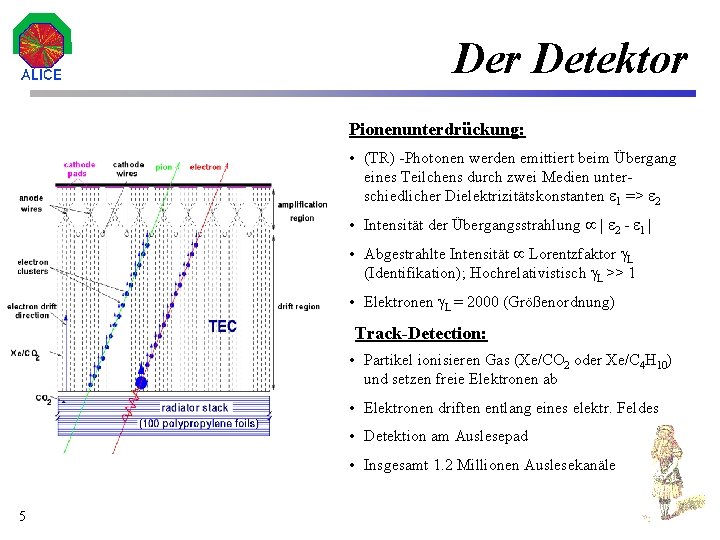

Der Detektor Pionenunterdrückung: • (TR) -Photonen werden emittiert beim Übergang eines Teilchens durch zwei Medien unterschiedlicher Dielektrizitätskonstanten 1 => 2 • Intensität der Übergangsstrahlung | 2 - 1 | • Abgestrahlte Intensität Lorentzfaktor L (Identifikation); Hochrelativistisch L >> 1 • Elektronen L = 2000 (Größenordnung) Track-Detection: • Partikel ionisieren Gas (Xe/CO 2 oder Xe/C 4 H 10) und setzen freie Elektronen ab • Elektronen driften entlang eines elektr. Feldes • Detektion am Auslesepad • Insgesamt 1. 2 Millionen Auslesekanäle 5

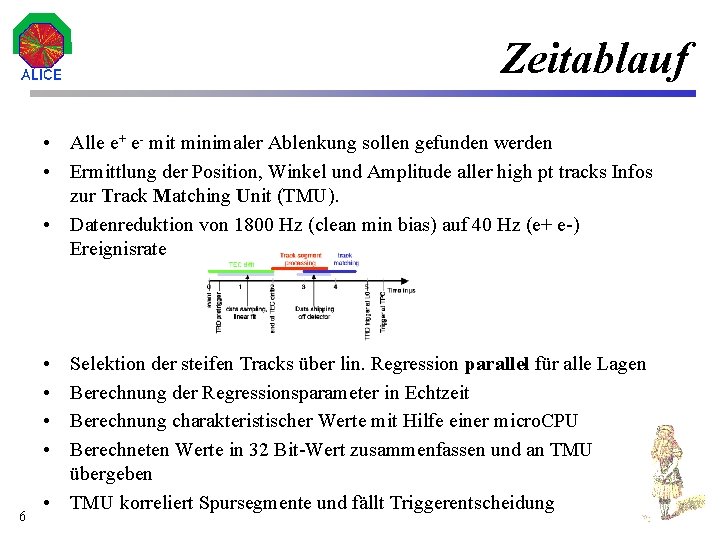

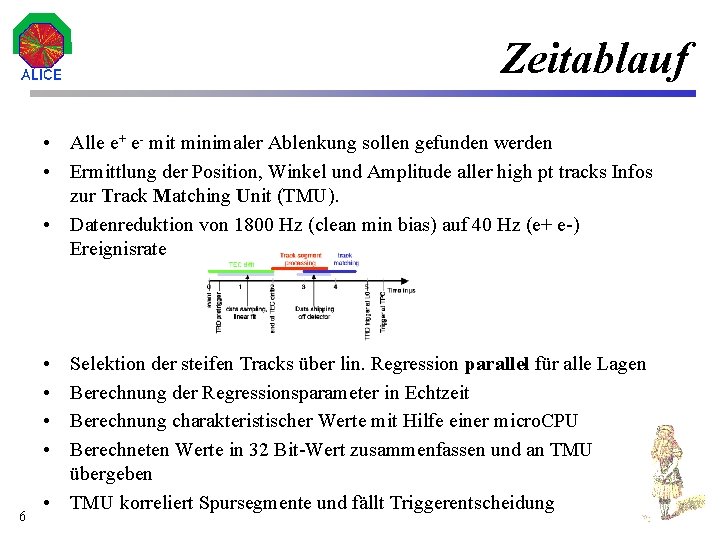

Zeitablauf • Alle e+ e- mit minimaler Ablenkung sollen gefunden werden • Ermittlung der Position, Winkel und Amplitude aller high pt tracks Infos zur Track Matching Unit (TMU). • Datenreduktion von 1800 Hz (clean min bias) auf 40 Hz (e+ e-) Ereignisrate • • 6 Selektion der steifen Tracks über lin. Regression parallel für alle Lagen Berechnung der Regressionsparameter in Echtzeit Berechnung charakteristischer Werte mit Hilfe einer micro. CPU Berechneten Werte in 32 Bit-Wert zusammenfassen und an TMU übergeben • TMU korreliert Spursegmente und fällt Triggerentscheidung

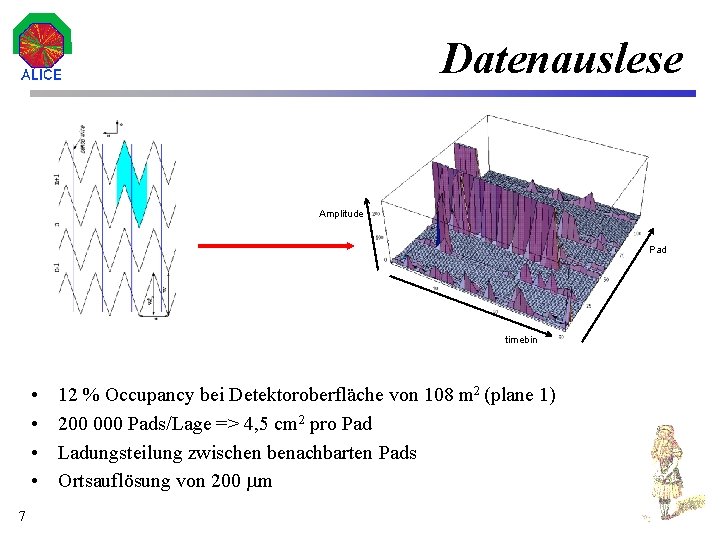

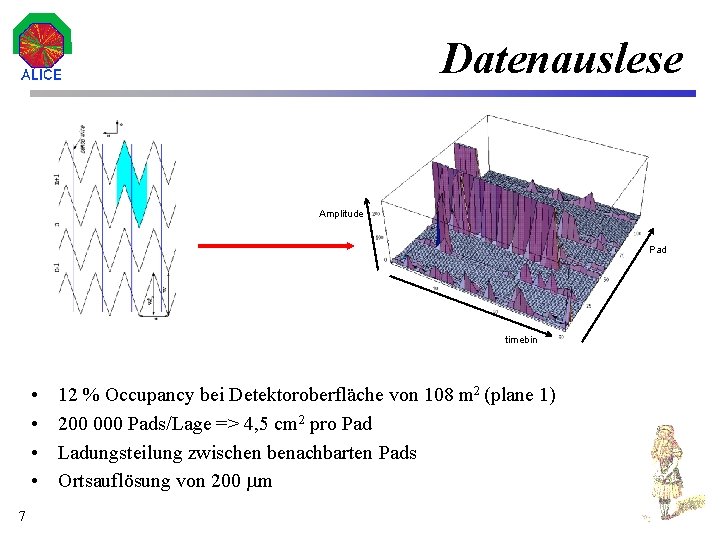

Datenauslese Amplitude Pad timebin • • 7 12 % Occupancy bei Detektoroberfläche von 108 m 2 (plane 1) 200 000 Pads/Lage => 4, 5 cm 2 pro Pad Ladungsteilung zwischen benachbarten Pads Ortsauflösung von 200 m

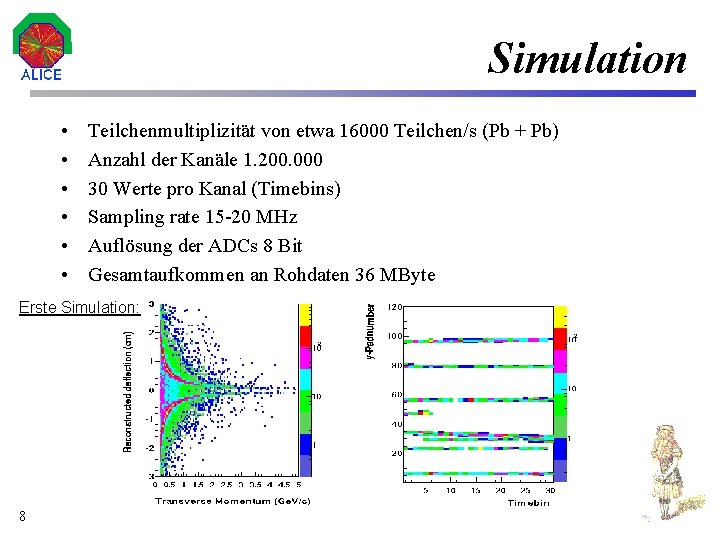

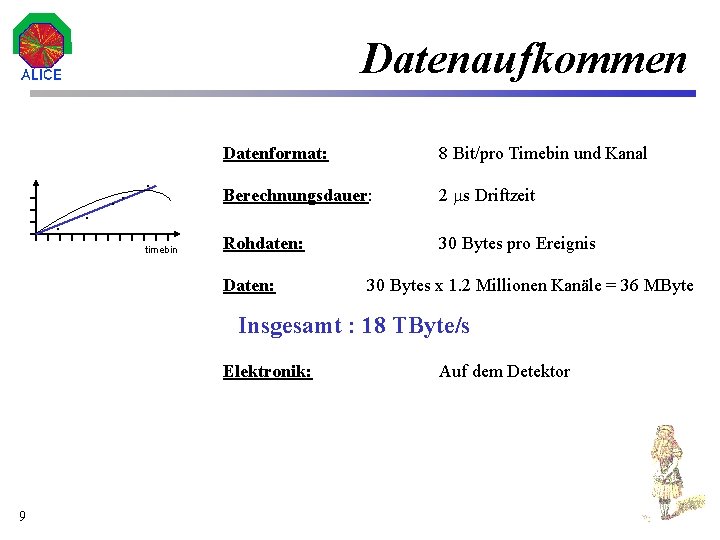

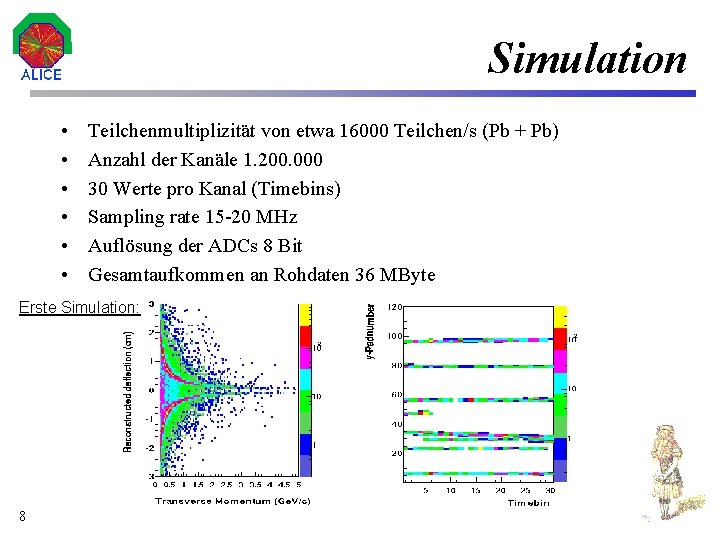

Simulation • • • Teilchenmultiplizität von etwa 16000 Teilchen/s (Pb + Pb) Anzahl der Kanäle 1. 200. 000 30 Werte pro Kanal (Timebins) Sampling rate 15 -20 MHz Auflösung der ADCs 8 Bit Gesamtaufkommen an Rohdaten 36 MByte Erste Simulation: 8

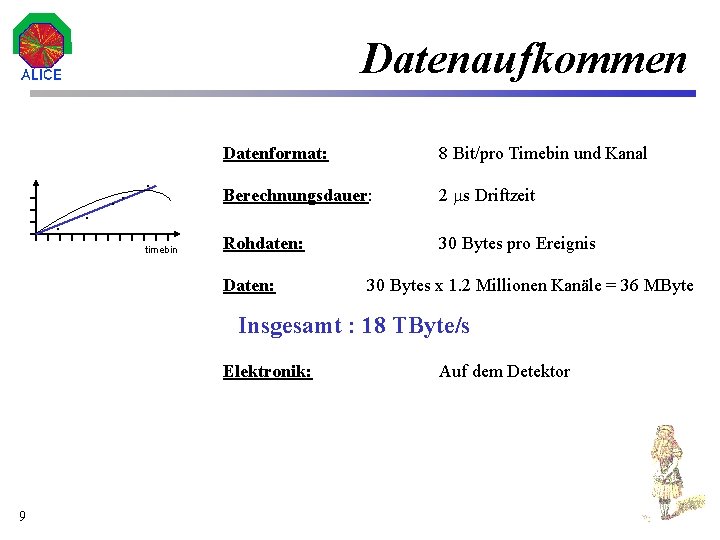

Datenaufkommen . . . timebin Datenformat: 8 Bit/pro Timebin und Kanal Berechnungsdauer: 2 s Driftzeit Rohdaten: 30 Bytes pro Ereignis Daten: 30 Bytes x 1. 2 Millionen Kanäle = 36 MByte Insgesamt : 18 TByte/s Elektronik: 9 Auf dem Detektor

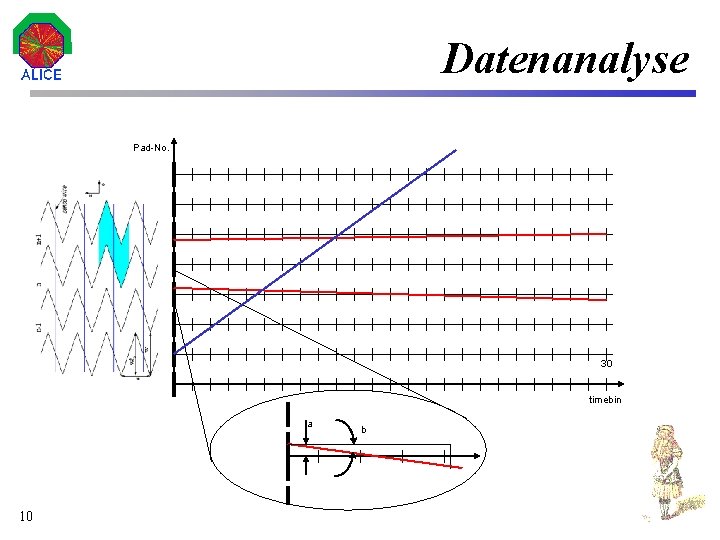

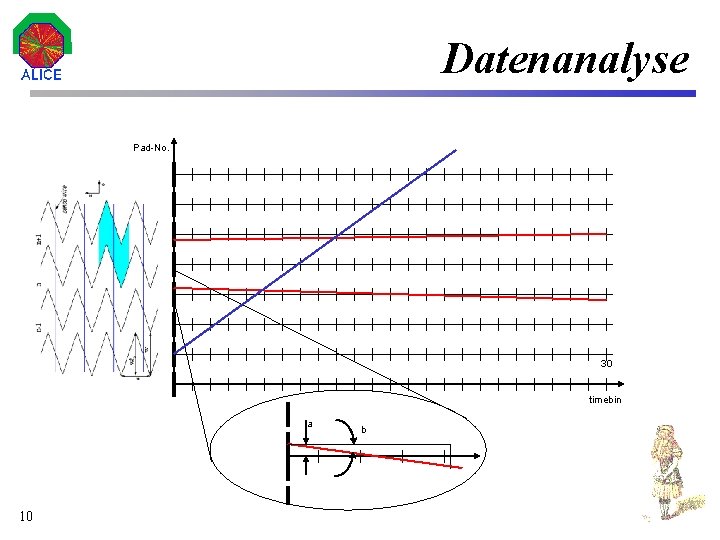

Datenanalyse Pad-No. 30 timebin a 10 b

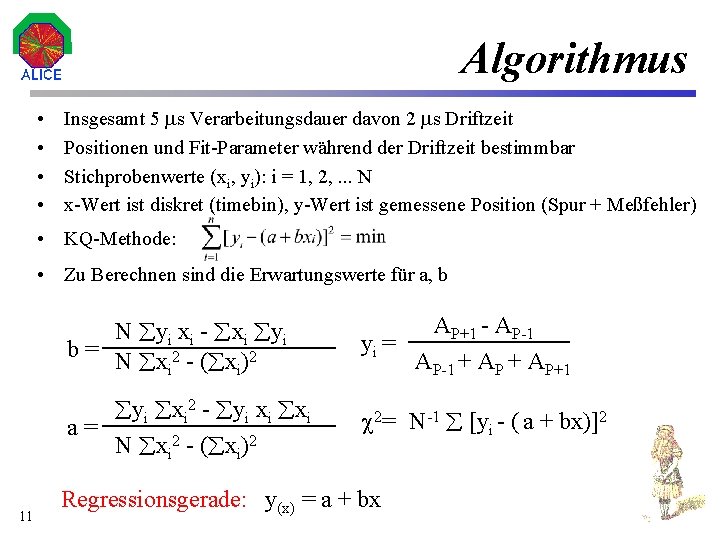

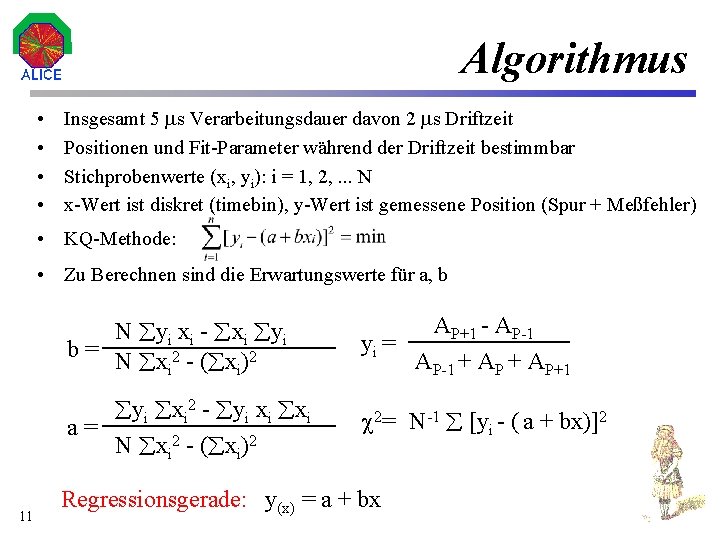

Algorithmus • • Insgesamt 5 s Verarbeitungsdauer davon 2 s Driftzeit Positionen und Fit-Parameter während der Driftzeit bestimmbar Stichprobenwerte (xi, yi): i = 1, 2, . . . N x-Wert ist diskret (timebin), y-Wert ist gemessene Position (Spur + Meßfehler) • KQ-Methode: • Zu Berechnen sind die Erwartungswerte für a, b 11 N yi xi - xi yi b = N x 2 - ( x )2 i i AP+1 - AP-1 yi = AP-1 + AP+1 yi xi 2 - yi xi xi a= N xi 2 - ( xi)2 2= N-1 [yi - ( a + bx)]2 Regressionsgerade: y(x) = a + bx

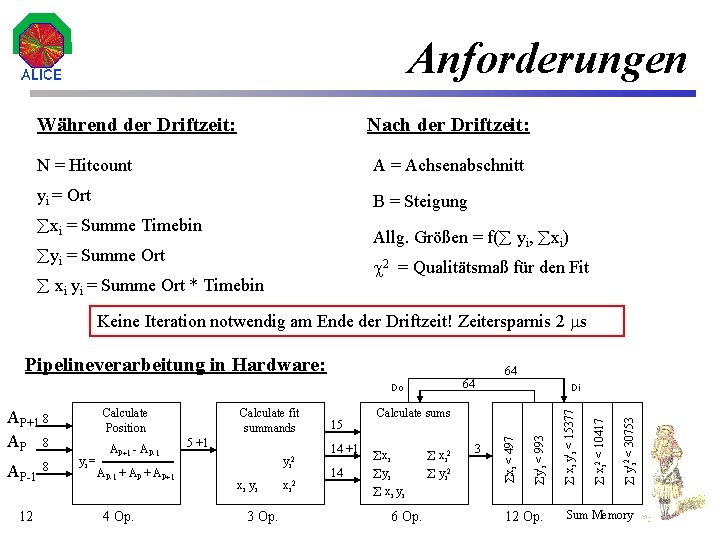

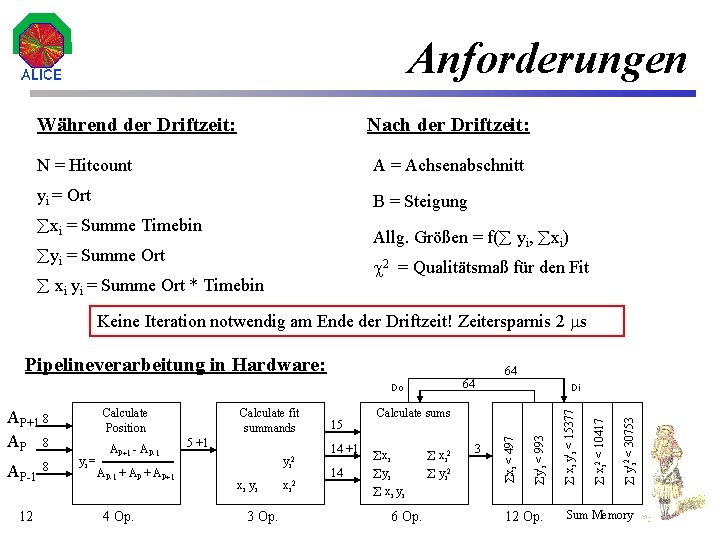

Anforderungen Während der Driftzeit: Nach der Driftzeit: N = Hitcount A = Achsenabschnitt yi = Ort B = Steigung xi = Summe Timebin Allg. Größen = f( yi, xi) yi = Summe Ort 2 = Qualitätsmaß für den Fit xi yi = Summe Ort * Timebin Keine Iteration notwendig am Ende der Driftzeit! Zeitersparnis 2 s Pipelineverarbeitung in Hardware: 64 12 4 Op. xi yi 3 Op. xi 2 14 +1 14 xi yi 6 Op. xi 2 yi 2 3 12 Op. y'i 2 < 30753 AP-1 + AP+1 yi 2 Calculate sums xi 2 < 10417 8 5 +1 15 y'i < 993 AP-1 yi = AP+1 - AP-1 Calculate fit summands xi < 497 Calculate Position Di xi y'i < 15377 Do AP+1 8 AP 8 64 Sum Memory

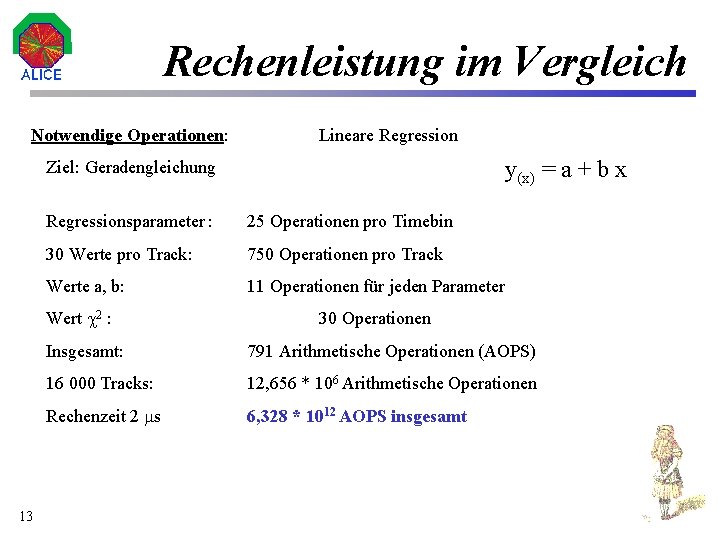

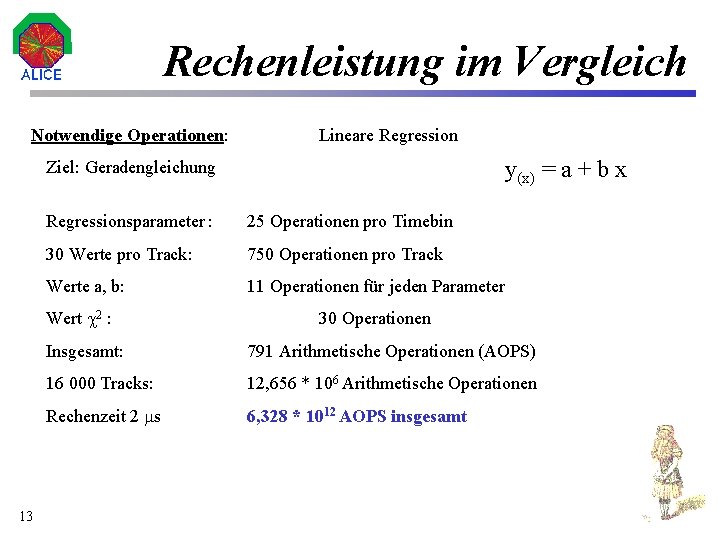

Rechenleistung im Vergleich Notwendige Operationen: Lineare Regression y(x) = a + b x Ziel: Geradengleichung Regressionsparameter : 25 Operationen pro Timebin 30 Werte pro Track: 750 Operationen pro Track Werte a, b: 11 Operationen für jeden Parameter Wert 2 : 13 30 Operationen Insgesamt: 791 Arithmetische Operationen (AOPS) 16 000 Tracks: 12, 656 * 106 Arithmetische Operationen Rechenzeit 2 s 6, 328 * 1012 AOPS insgesamt

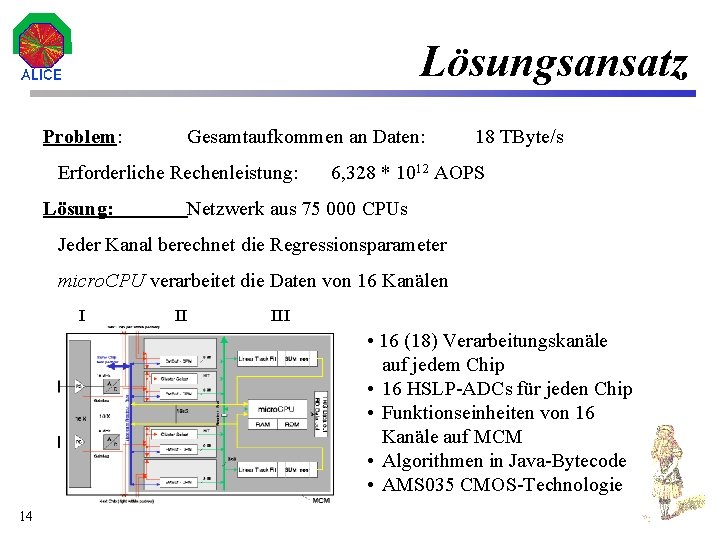

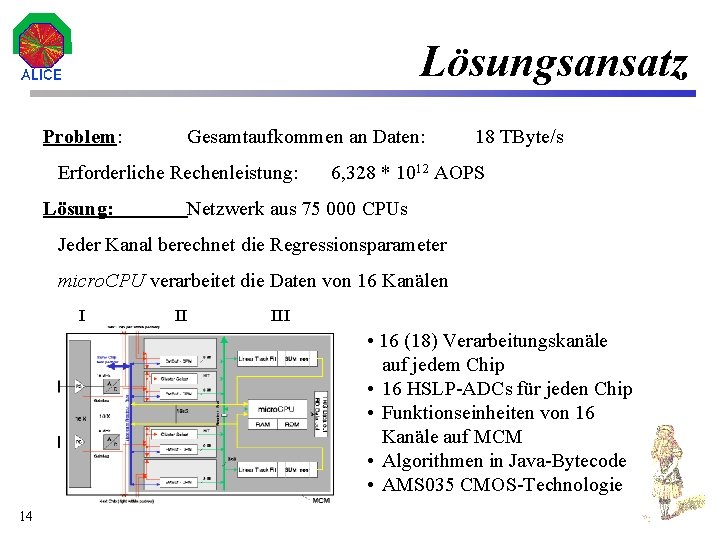

Lösungsansatz Problem: Gesamtaufkommen an Daten: Erforderliche Rechenleistung: Lösung: 18 TByte/s 6, 328 * 1012 AOPS Netzwerk aus 75 000 CPUs Jeder Kanal berechnet die Regressionsparameter micro. CPU verarbeitet die Daten von 16 Kanälen I II III • 16 (18) Verarbeitungskanäle auf jedem Chip • 16 HSLP-ADCs für jeden Chip • Funktionseinheiten von 16 Kanäle auf MCM • Algorithmen in Java-Bytecode • AMS 035 CMOS-Technologie 14

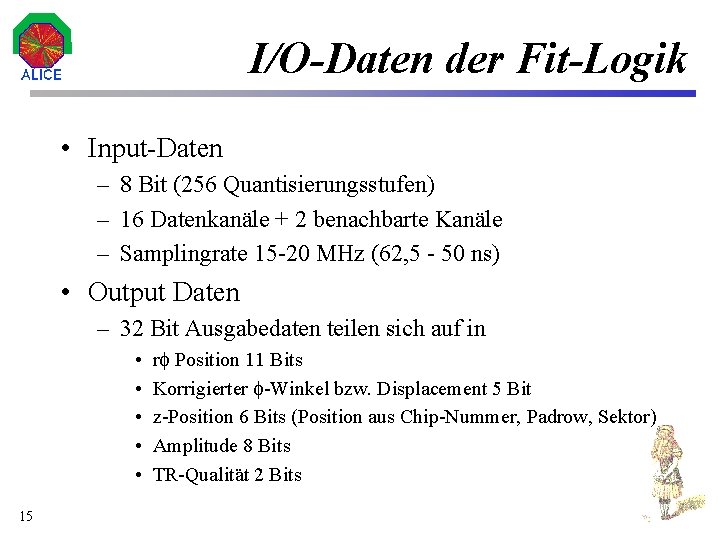

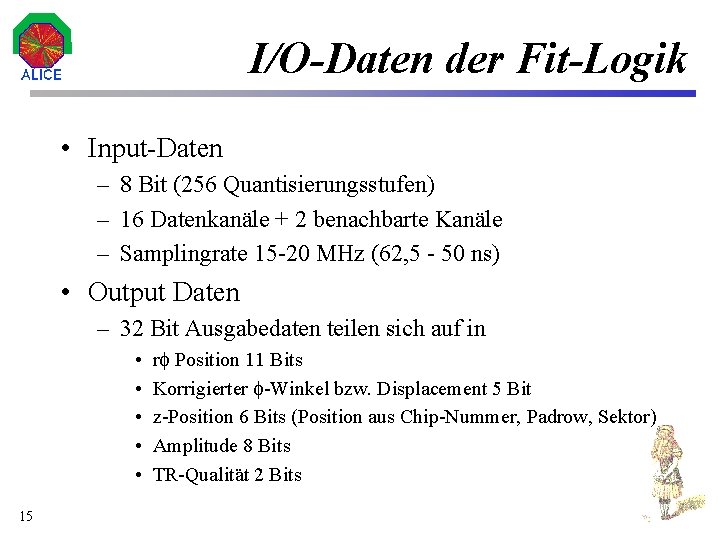

I/O-Daten der Fit-Logik • Input-Daten – 8 Bit (256 Quantisierungsstufen) – 16 Datenkanäle + 2 benachbarte Kanäle – Samplingrate 15 -20 MHz (62, 5 - 50 ns) • Output Daten – 32 Bit Ausgabedaten teilen sich auf in • • • 15 r Position 11 Bits Korrigierter -Winkel bzw. Displacement 5 Bit z-Position 6 Bits (Position aus Chip-Nummer, Padrow, Sektor) Amplitude 8 Bits TR-Qualität 2 Bits

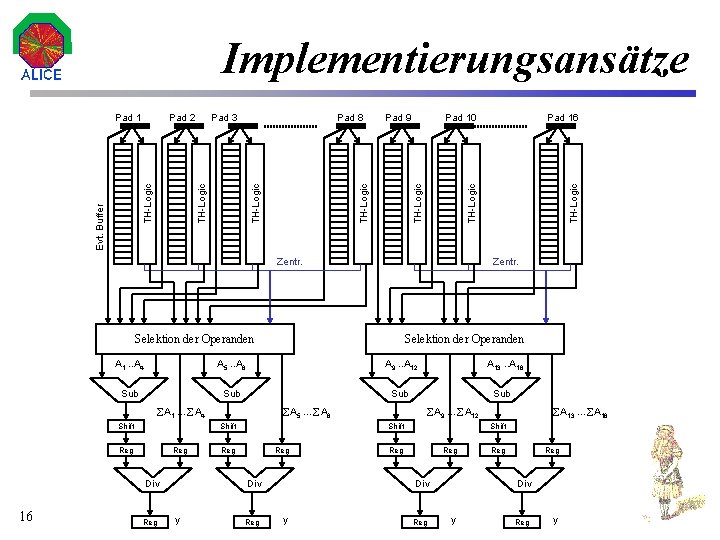

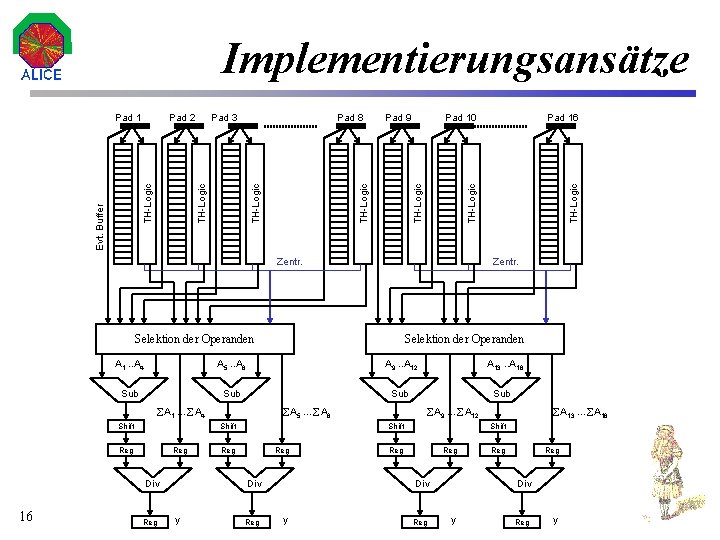

Implementierungsansätze Zentr. A 5. . A 8 A 9. . A 12 Sub Sub A 5. . . A 8 Shift Reg Div 16 Selektion der Operanden A 1. . A 4 Shift Reg Div y A 13. . A 16 Sub A 9. . . A 12 Shift Reg TH-Logic Zentr. Selektion der Operanden A 1. . . A 4 Pad 16 TH-Logic Pad 10 TH-Logic Pad 9 TH-Logic Pad 8 TH-Logic Evt. Buffer Pad 3 TH-Logic Pad 2 TH-Logic Pad 1 Shift Reg Div y A 13. . . A 16 Reg Reg Div y Reg y

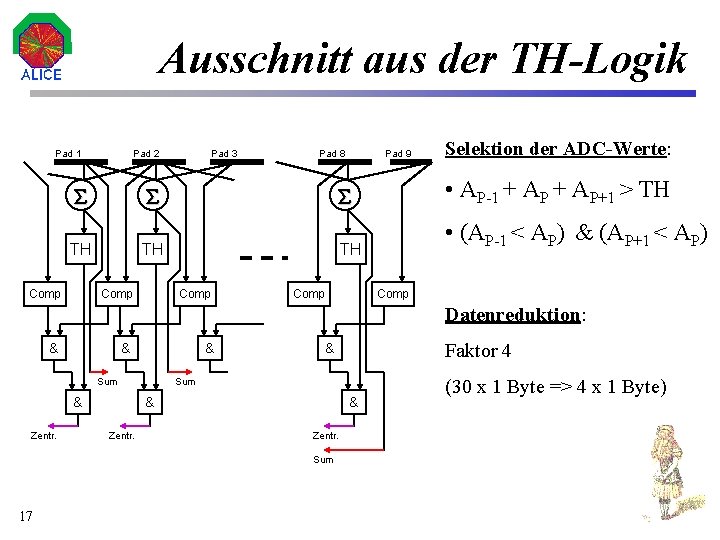

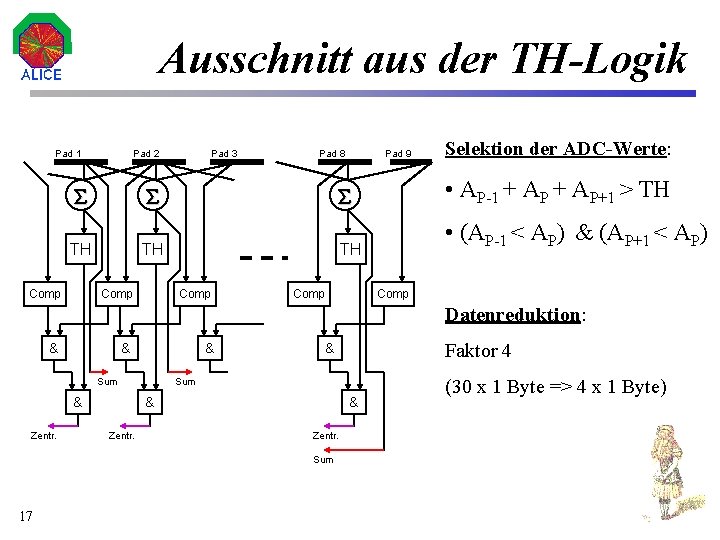

Ausschnitt aus der TH-Logik Pad 1 Pad 2 Pad 3 Pad 8 Pad 9 TH TH TH Comp Selektion der ADC-Werte: • AP-1 + AP+1 > TH • (AP-1 < AP) & (AP+1 < AP) Comp Datenreduktion: & & & Sum & Zentr. Sum 17 Faktor 4 & (30 x 1 Byte => 4 x 1 Byte)

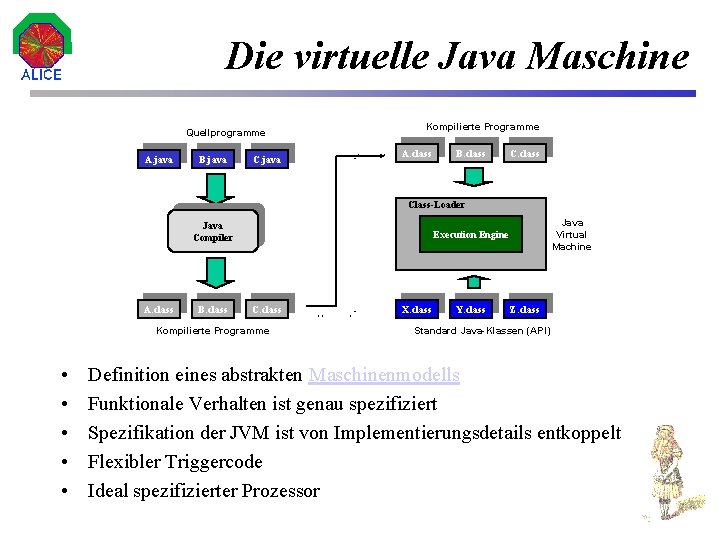

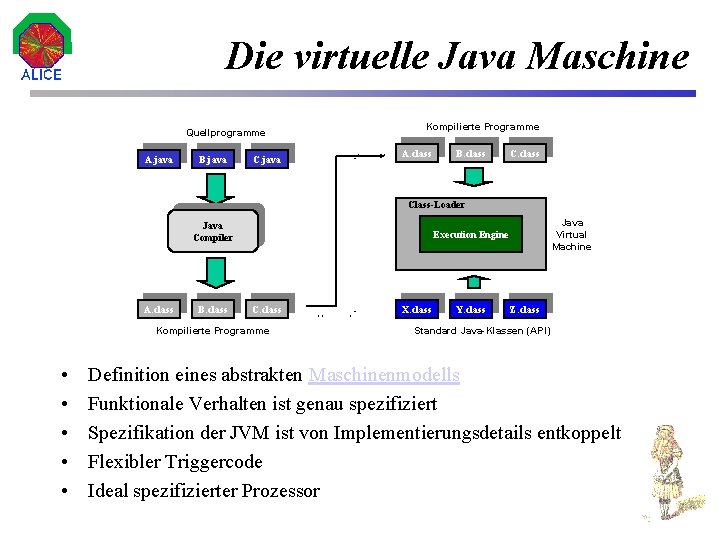

Die virtuelle Java Maschine Quellprogramme A. java B. java C. java Kompilierte Programme A. class B. class Class-Loader Java Compiler A. class B. class C. class Kompilierte Programme • • • Java Virtual Machine Execution Engine X. class Y. class Z. class Standard Java-Klassen (API) Definition eines abstrakten Maschinenmodells Funktionale Verhalten ist genau spezifiziert Spezifikation der JVM ist von Implementierungsdetails entkoppelt Flexibler Triggercode Ideal spezifizierter Prozessor

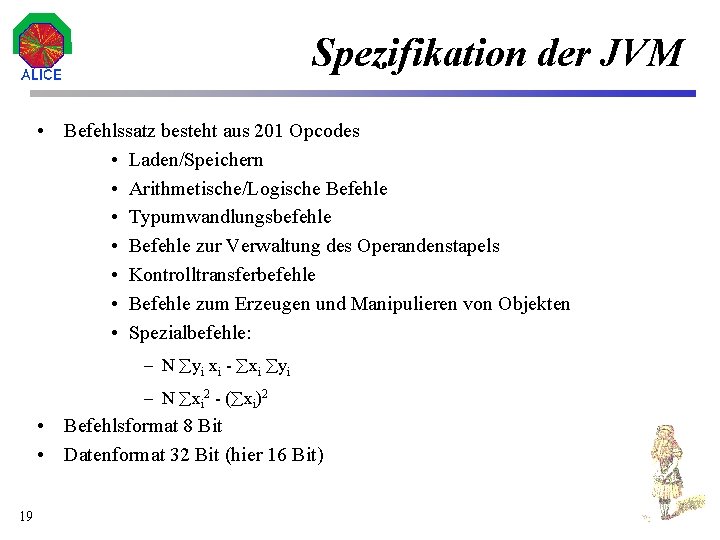

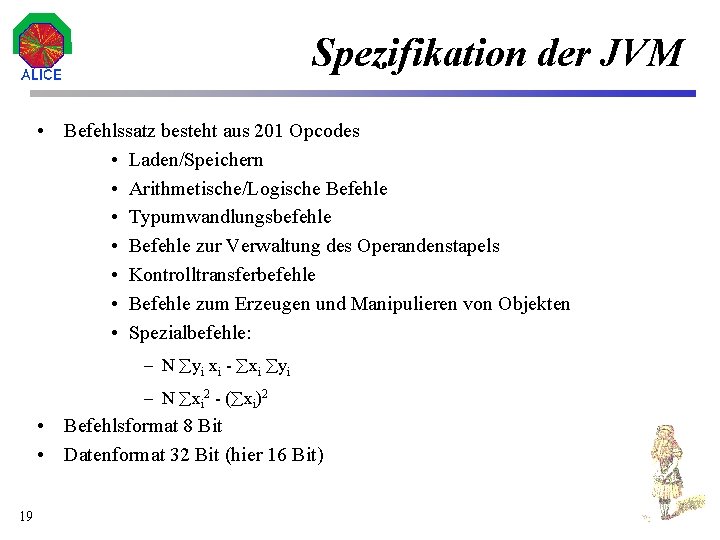

Spezifikation der JVM • Befehlssatz besteht aus 201 Opcodes • Laden/Speichern • Arithmetische/Logische Befehle • Typumwandlungsbefehle • Befehle zur Verwaltung des Operandenstapels • Kontrolltransferbefehle • Befehle zum Erzeugen und Manipulieren von Objekten • Spezialbefehle: – N yi xi - xi yi – N xi 2 - ( xi)2 • Befehlsformat 8 Bit • Datenformat 32 Bit (hier 16 Bit) 19

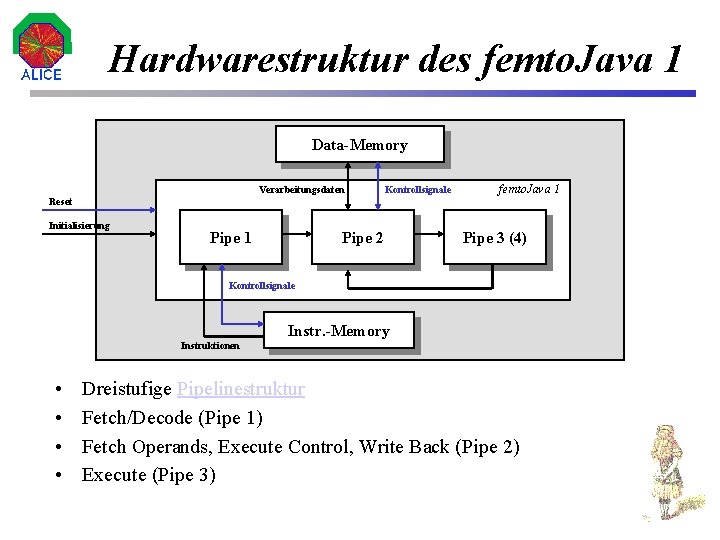

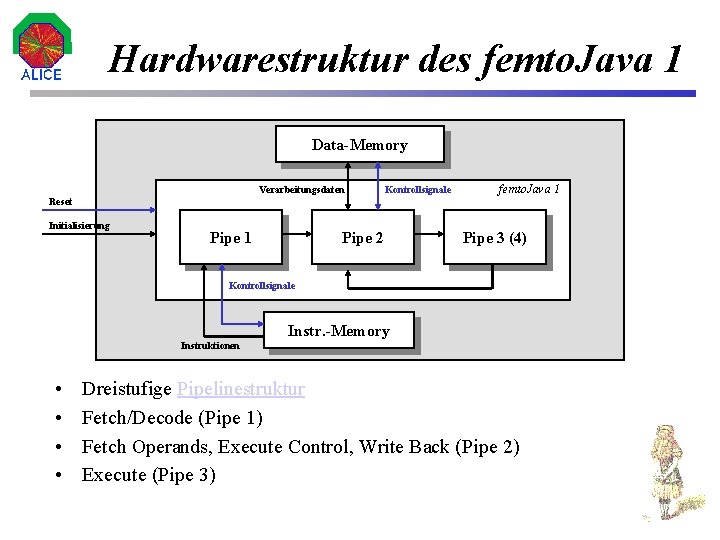

Hardwarestruktur des femto. Java 1 Data-Memory Verarbeitungsdaten Kontrollsignale femto. Java 1 Reset Initialisierung Pipe 1 Pipe 2 Pipe 3 (4) Kontrollsignale Instr. -Memory Instruktionen • • Dreistufige Pipelinestruktur Fetch/Decode (Pipe 1) Fetch Operands, Execute Control, Write Back (Pipe 2) Execute (Pipe 3)

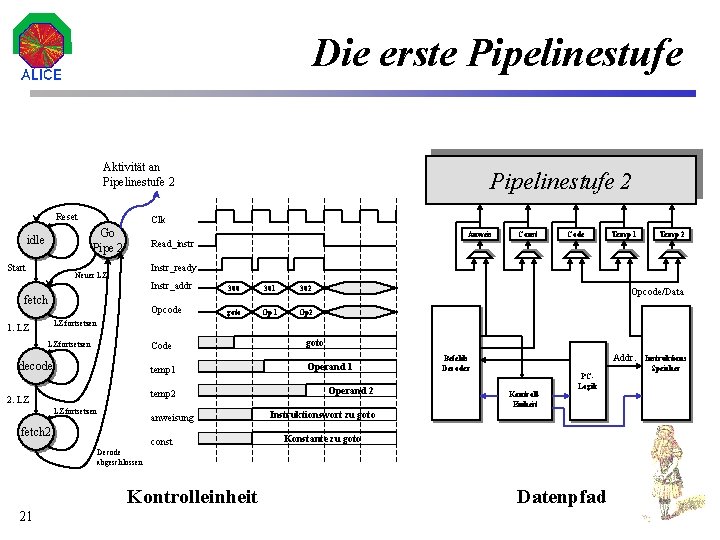

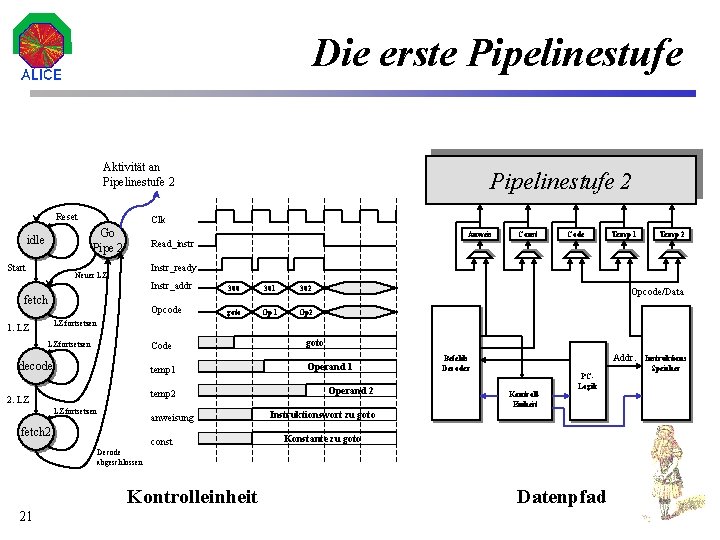

Die erste Pipelinestufe Aktivität an Pipelinestufe 2 Reset Clk Go Pipe 2 idle Start Pipelinestufe 2 Anweis Read_instr Const Code Temp 2 Instr_ready Neuer LZ fetch Instr_addr 300 301 302 Opcode goto Op 1 Op 2 Opcode/Data LZ fortsetzen 1. LZ LZ fortsetzen decode Code goto temp 1 Operand 1 temp 2 2. LZ LZ fortsetzen anweisung fetch 2 const Operand 2 Addr. Befehls Decoder Kontroll. Einheit PCLogik Instruktionswort zu goto Konstante zu goto Decode abgeschlossen Kontrolleinheit 21 Temp 1 Datenpfad Instruktions Speicher

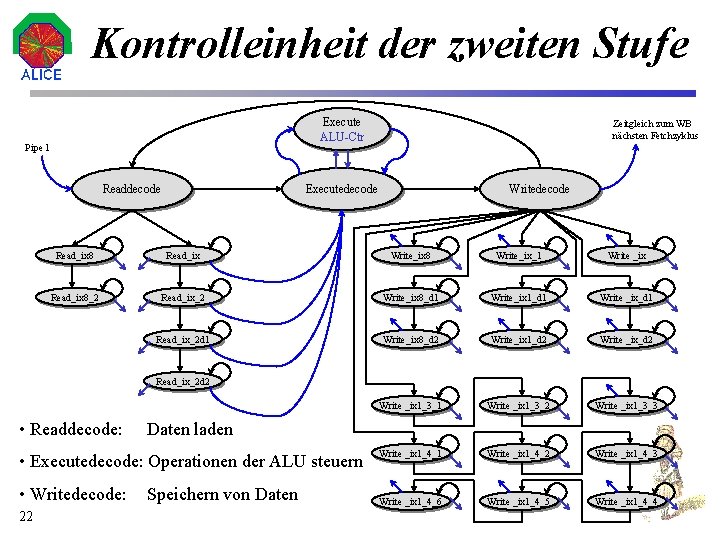

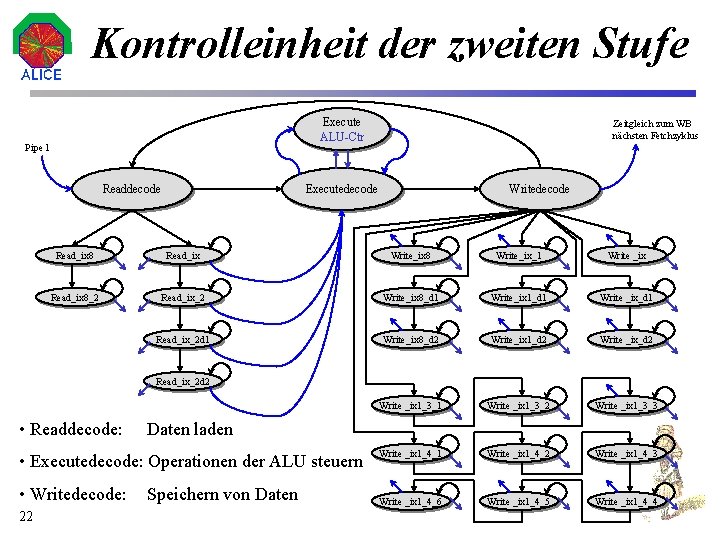

Kontrolleinheit der zweiten Stufe Execute ALU-Ctr Pipe 1 Readdecode Zeitgleich zum WB nächsten Fetchzyklus Executedecode Writedecode Read_ix 8 Read_ix Write_ix 8 Write_ix_1 Write _ix Read_ix 8_2 Read_ix_2 Write_ix 8_d 1 Write_ix 1_d 1 Write _ix_d 1 Read_ix_2 d 1 Write_ix 8_d 2 Write_ix 1_d 2 Write _ix 1_3_1 Write _ix 1_3_2 Write _ix 1_3_3 Write _ix 1_4_1 Write _ix 1_4_2 Write _ix 1_4_3 Write _ix 1_4_6 Write _ix 1_4_5 Write _ix 1_4_4 Read_ix_2 d 2 • Readdecode: Daten laden • Executedecode: Operationen der ALU steuern • Writedecode: 22 Speichern von Daten

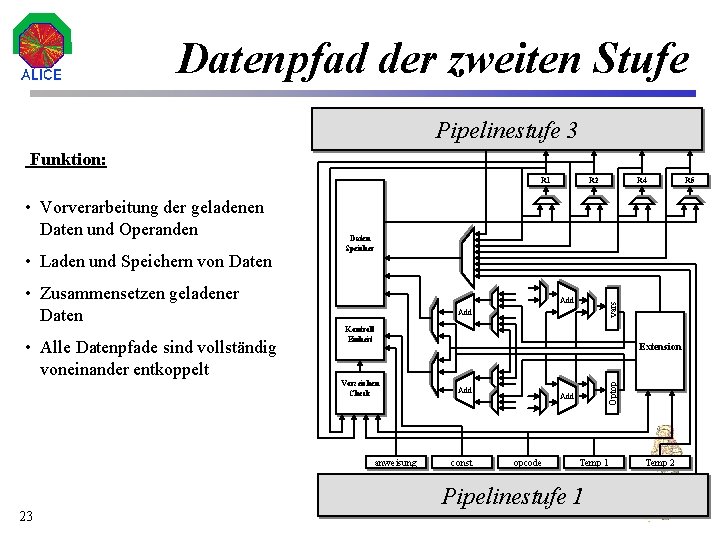

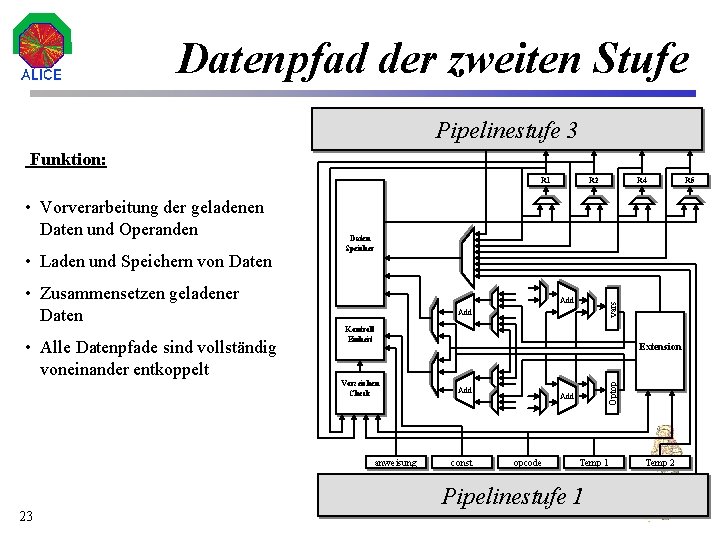

Datenpfad der zweiten Stufe Pipelinestufe 3 Funktion: R 1 Daten Speicher • Zusammensetzen geladener Daten • Alle Datenpfade sind vollständig voneinander entkoppelt Add Kontroll Einheit Vorzeichen Check anweisung 23 vars • Laden und Speichern von Daten R 4 Extension Add const Optop • Vorverarbeitung der geladenen Daten und Operanden R 2 Add opcode Temp 1 Pipelinestufe 1 Temp 2 R 5

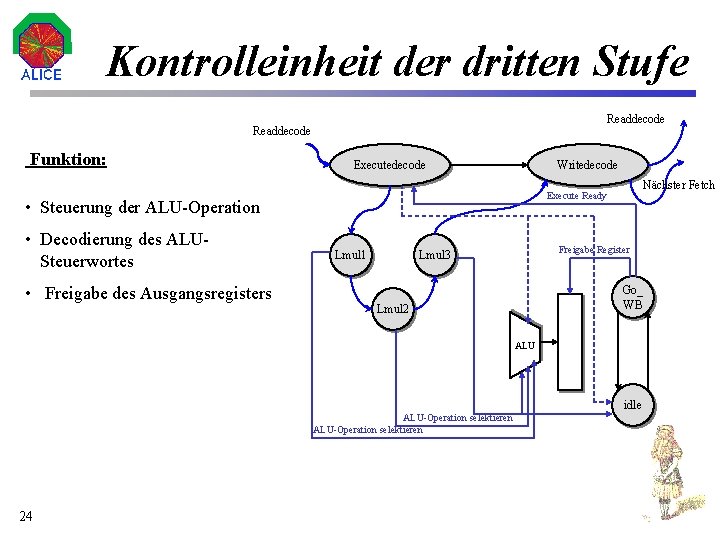

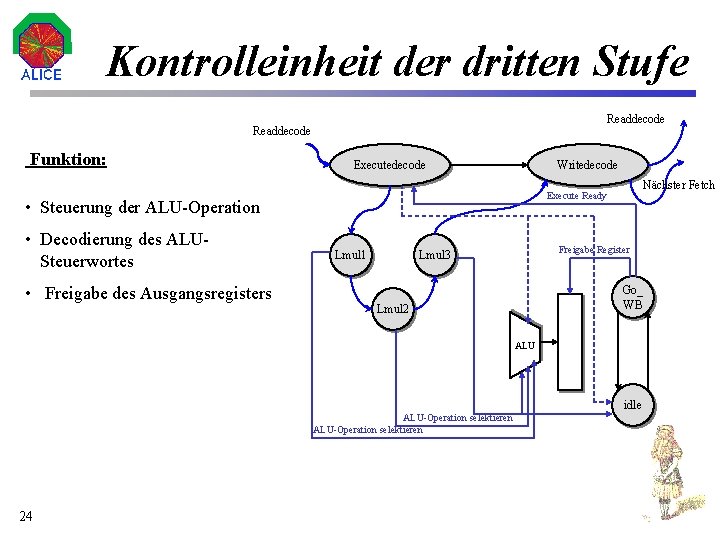

Kontrolleinheit der dritten Stufe Readdecode Funktion: Executedecode Writedecode • Steuerung der ALU-Operation • Decodierung des ALUSteuerwortes • Freigabe des Ausgangsregisters Nächster Fetch Execute Ready Lmul 1 Freigabe Register Lmul 3 Go_ WB Lmul 2 ALU idle ALU-Operation selektieren 24

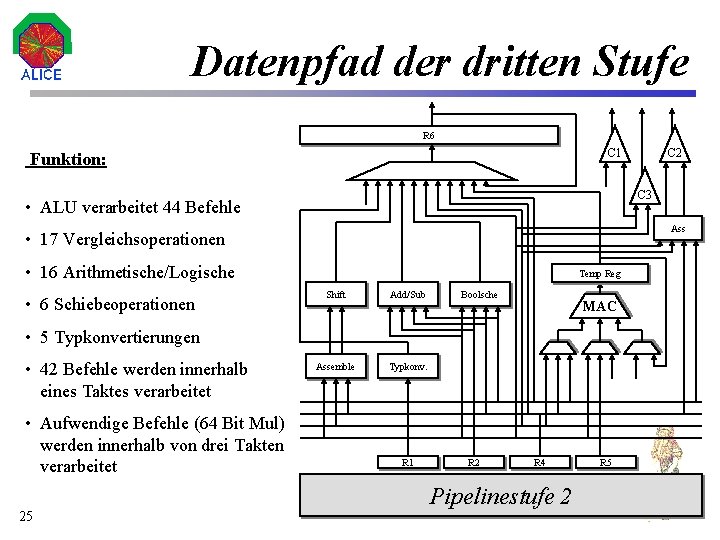

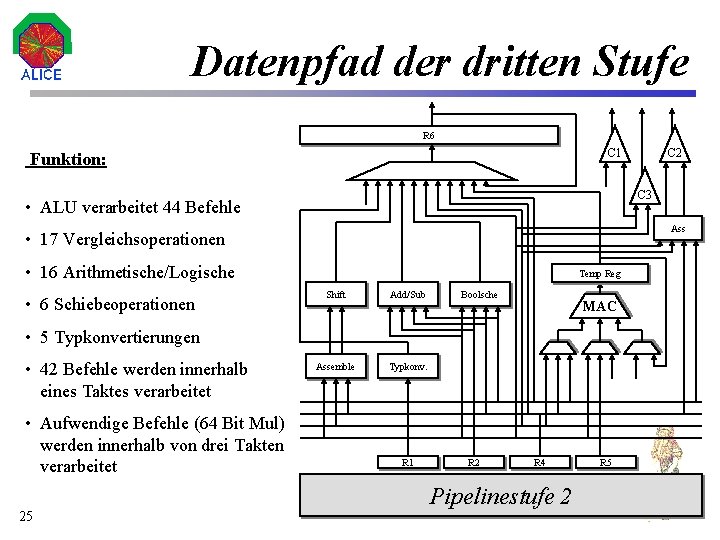

Datenpfad der dritten Stufe R 6 C 1 Funktion: C 3 • ALU verarbeitet 44 Befehle Ass • 17 Vergleichsoperationen • 16 Arithmetische/Logische • 6 Schiebeoperationen Temp Reg Shift Add/Sub Assemble Typkonv. Boolsche MAC • 5 Typkonvertierungen • 42 Befehle werden innerhalb eines Taktes verarbeitet • Aufwendige Befehle (64 Bit Mul) werden innerhalb von drei Takten verarbeitet 25 C 2 R 1 R 2 R 4 Pipelinestufe 2 R 5

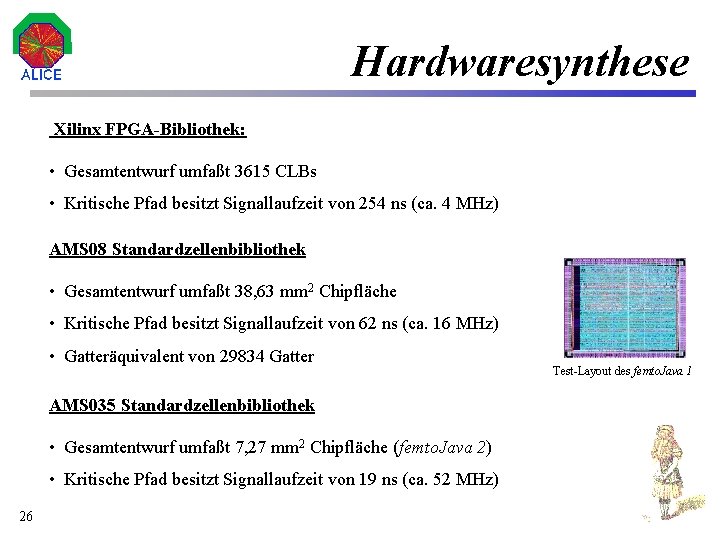

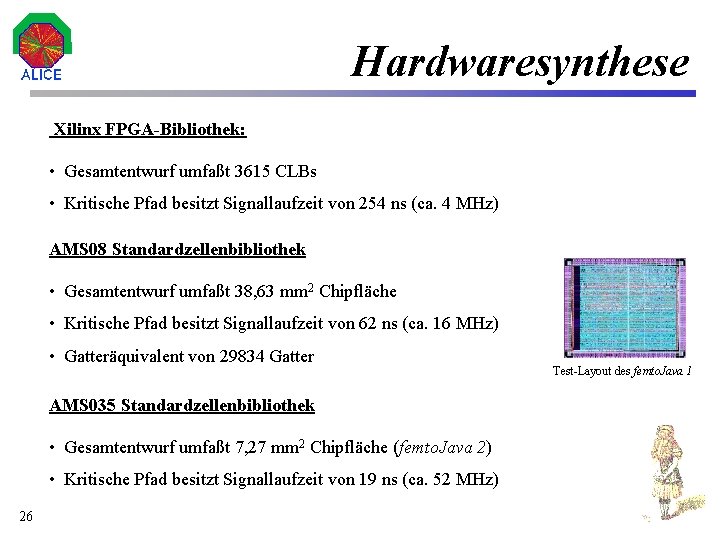

Hardwaresynthese Xilinx FPGA-Bibliothek: • Gesamtentwurf umfaßt 3615 CLBs • Kritische Pfad besitzt Signallaufzeit von 254 ns (ca. 4 MHz) AMS 08 Standardzellenbibliothek • Gesamtentwurf umfaßt 38, 63 mm 2 Chipfläche • Kritische Pfad besitzt Signallaufzeit von 62 ns (ca. 16 MHz) • Gatteräquivalent von 29834 Gatter AMS 035 Standardzellenbibliothek • Gesamtentwurf umfaßt 7, 27 mm 2 Chipfläche (femto. Java 2) • Kritische Pfad besitzt Signallaufzeit von 19 ns (ca. 52 MHz) 26 Test-Layout des femto. Java 1

Projektstatus • Implementierung der „Linear track fit engine“ – Simulationsmodel liegt vor und wird iterativ verbessert – Werte aus Simulation bestimmen die Implementierungsstruktur der Hardwarerealisierung • Erster Prototyp der micro. CPU ist vorhanden – Hardwarerealiesierung der LTFE liegt vor (VHDL-Modell) – Tape out Q 1 `00 – Nächster Designschritt der micro. CPU Q 2 `00 27