ALICE High Level Trigger The ALICE HighLevelTrigger Torsten

- Slides: 26

ALICE High Level Trigger The ALICE High-Level-Trigger Torsten Alt - KIP Heidelberg IRTG 28/02/2007 1

Overview The ALICE High-Level-Trigger: • dataflow in the ALICE experiment • trigger systems : L 0, L 1, L 2 • TPC – largest datasource • High-Level-Trigger: Tasks & Implementation The HLT Read. Out-Receiver-Card (H-RORC): • Tasks & Requirements • Implementation Torsten Alt - KIP Heidelberg IRTG 28/02/2007 2

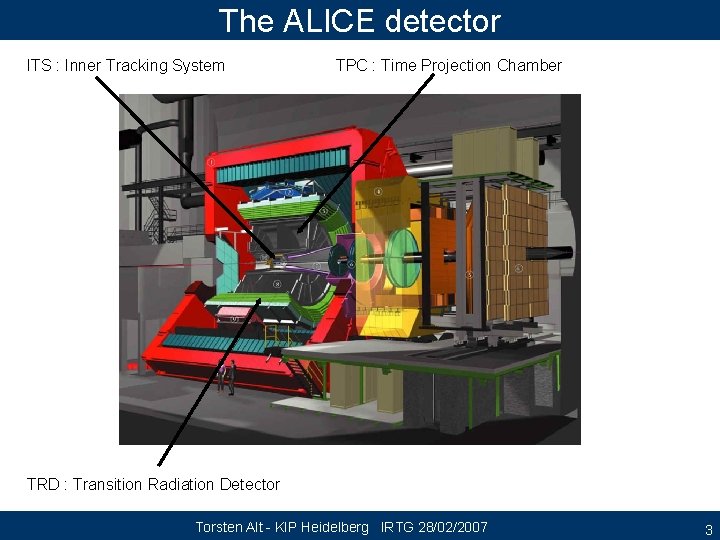

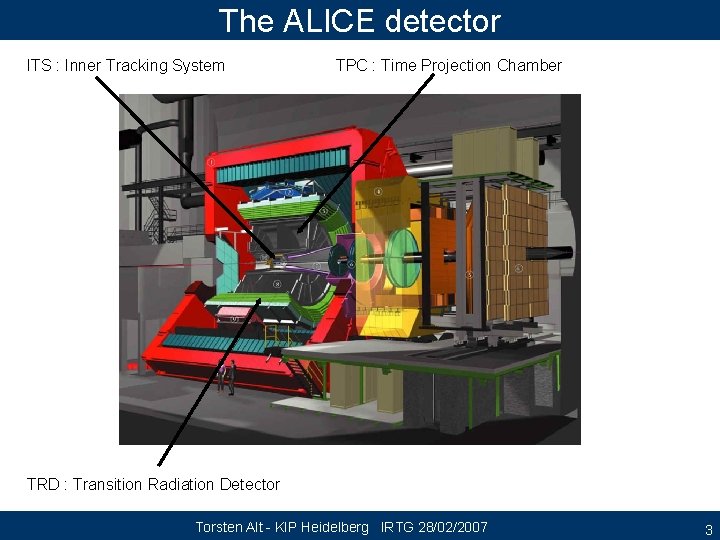

The ALICE detector ITS : Inner Tracking System TPC : Time Projection Chamber TRD : Transition Radiation Detector Torsten Alt - KIP Heidelberg IRTG 28/02/2007 3

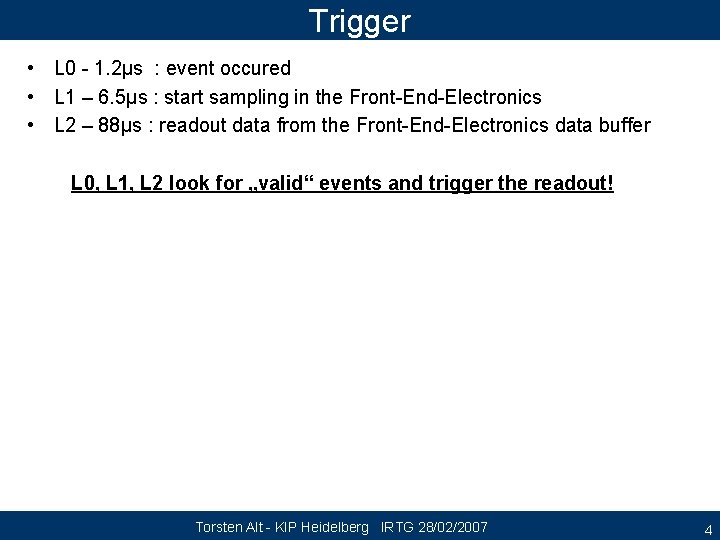

Trigger • L 0 - 1. 2µs : event occured • L 1 – 6. 5µs : start sampling in the Front-End-Electronics • L 2 – 88µs : readout data from the Front-End-Electronics data buffer L 0, L 1, L 2 look for „valid“ events and trigger the readout! Torsten Alt - KIP Heidelberg IRTG 28/02/2007 4

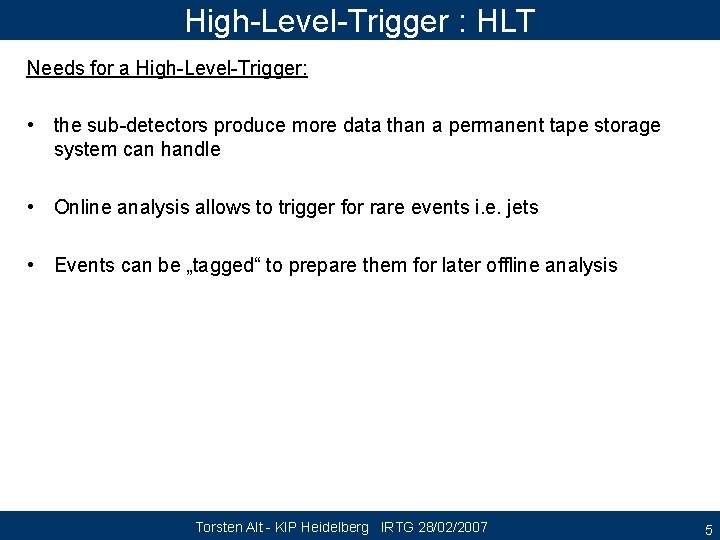

High-Level-Trigger : HLT Needs for a High-Level-Trigger: • the sub-detectors produce more data than a permanent tape storage system can handle • Online analysis allows to trigger for rare events i. e. jets • Events can be „tagged“ to prepare them for later offline analysis Torsten Alt - KIP Heidelberg IRTG 28/02/2007 5

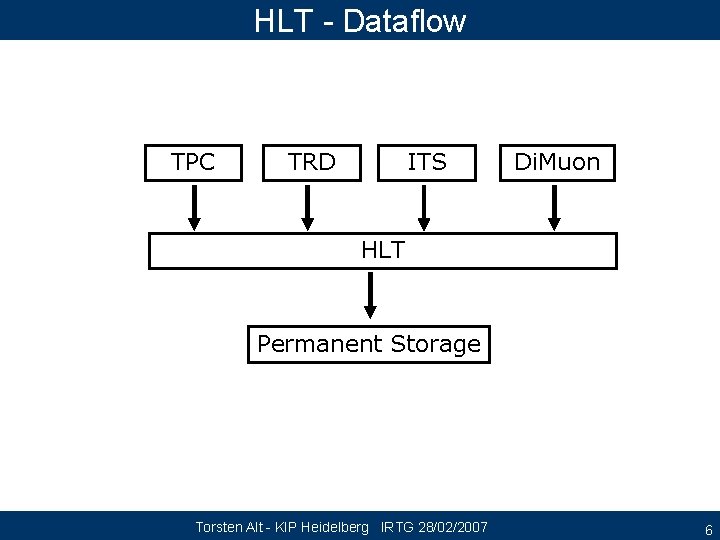

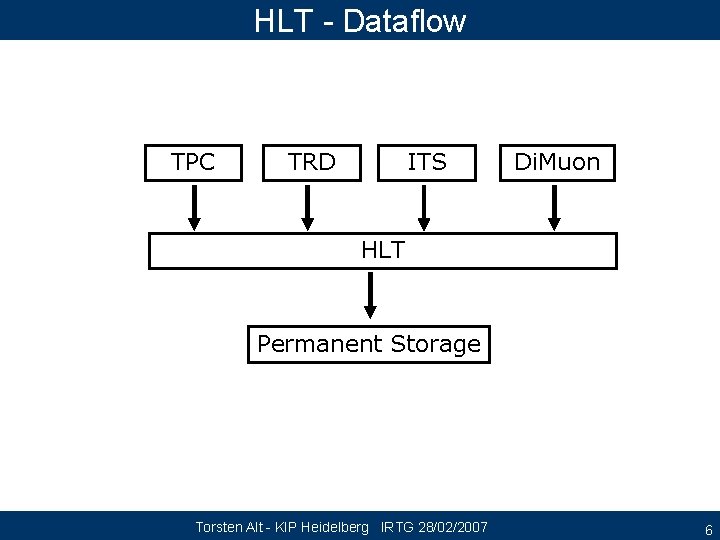

HLT - Dataflow TPC TRD ITS Di. Muon HLT Permanent Storage Torsten Alt - KIP Heidelberg IRTG 28/02/2007 6

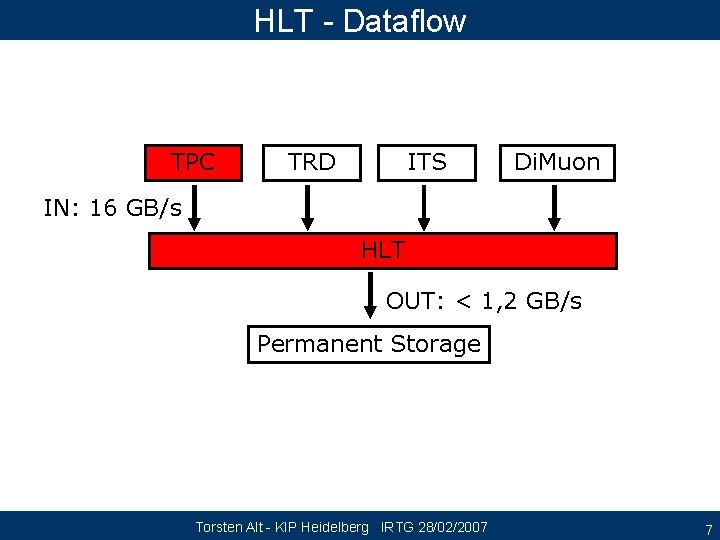

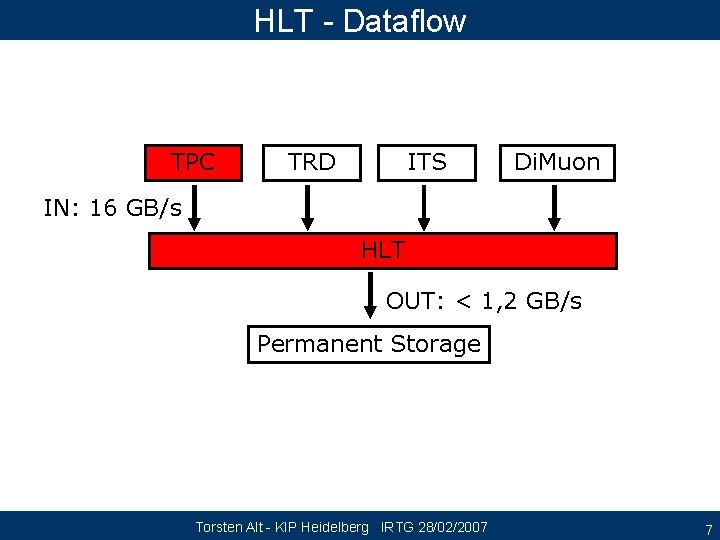

HLT - Dataflow TPC TRD ITS Di. Muon IN: 16 GB/s HLT OUT: < 1, 2 GB/s Permanent Storage Torsten Alt - KIP Heidelberg IRTG 28/02/2007 7

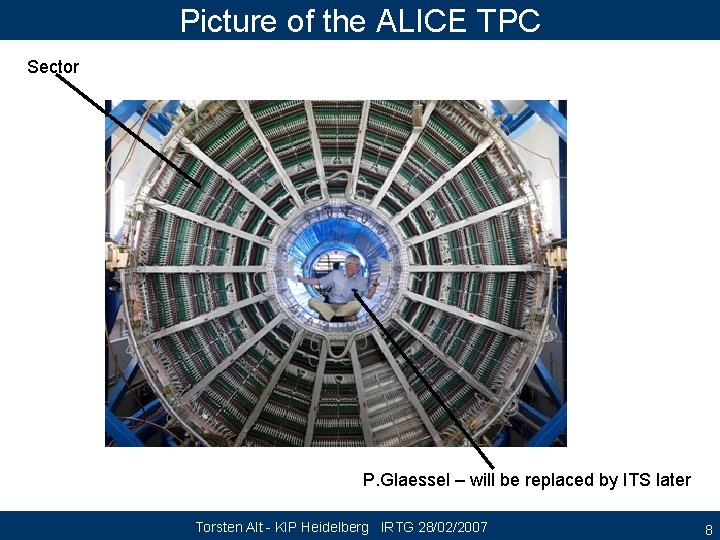

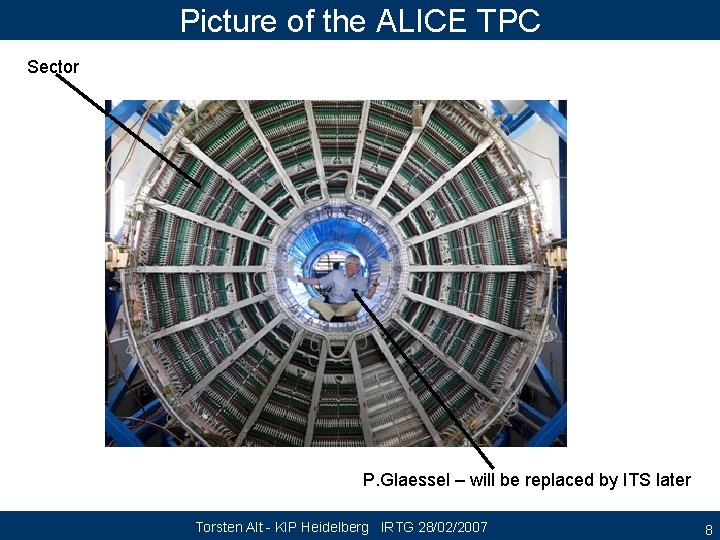

Picture of the ALICE TPC Sector P. Glaessel – will be replaced by ITS later Torsten Alt - KIP Heidelberg IRTG 28/02/2007 8

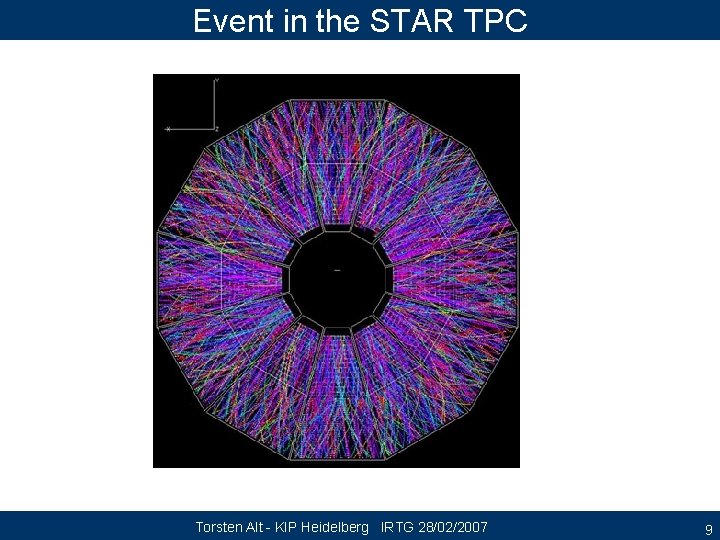

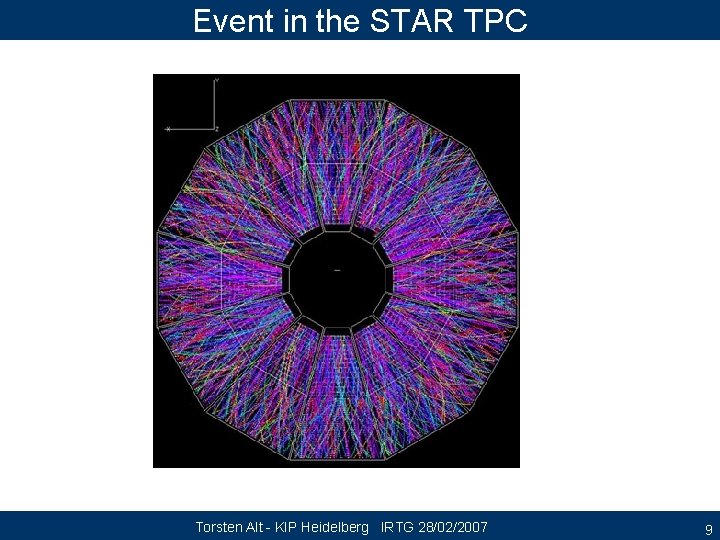

Event in the STAR TPC Torsten Alt - KIP Heidelberg IRTG 28/02/2007 9

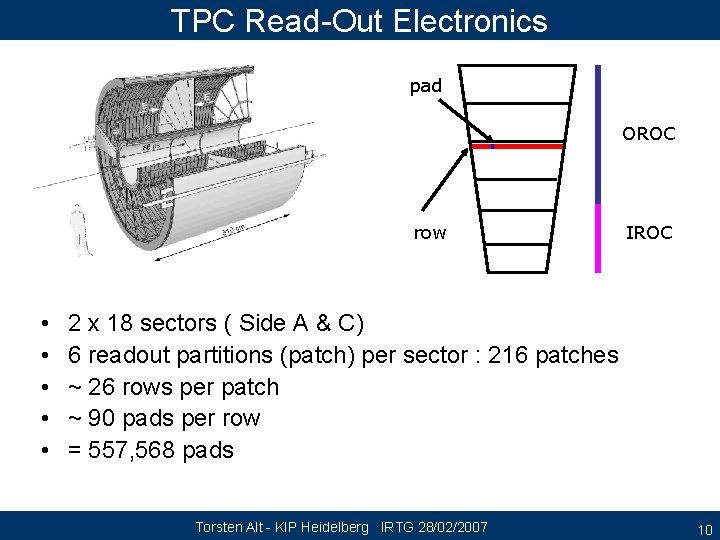

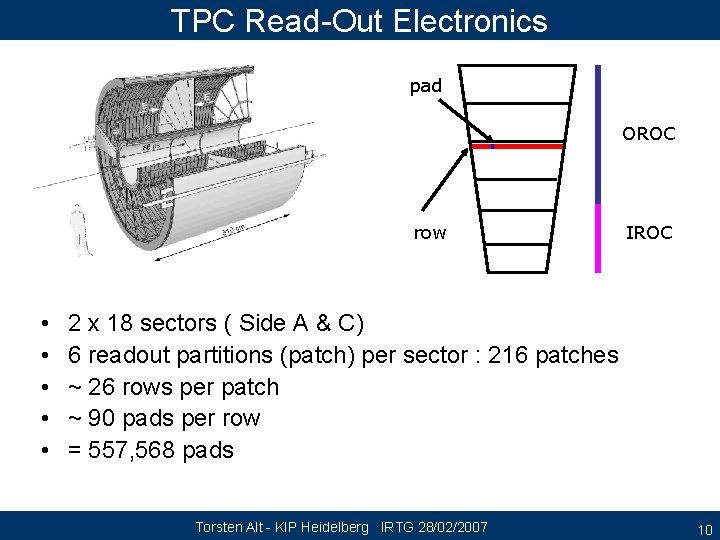

TPC Read-Out Electronics pad OROC row • • • IROC 2 x 18 sectors ( Side A & C) 6 readout partitions (patch) per sector : 216 patches ~ 26 rows per patch ~ 90 pads per row = 557, 568 pads Torsten Alt - KIP Heidelberg IRTG 28/02/2007 10

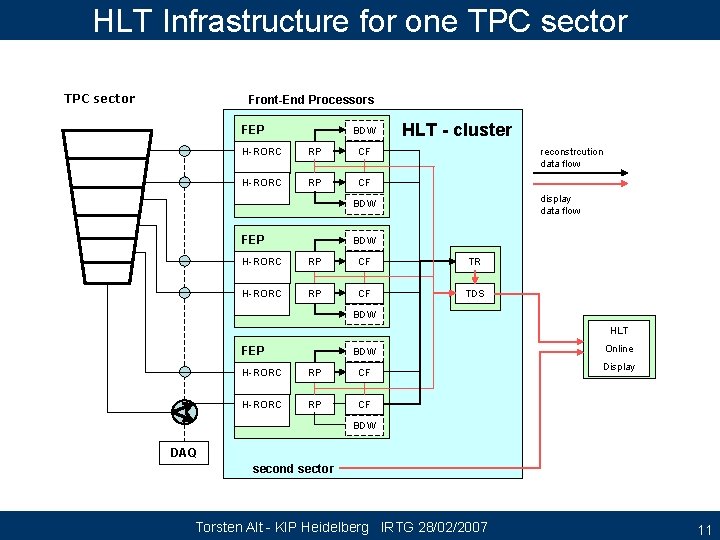

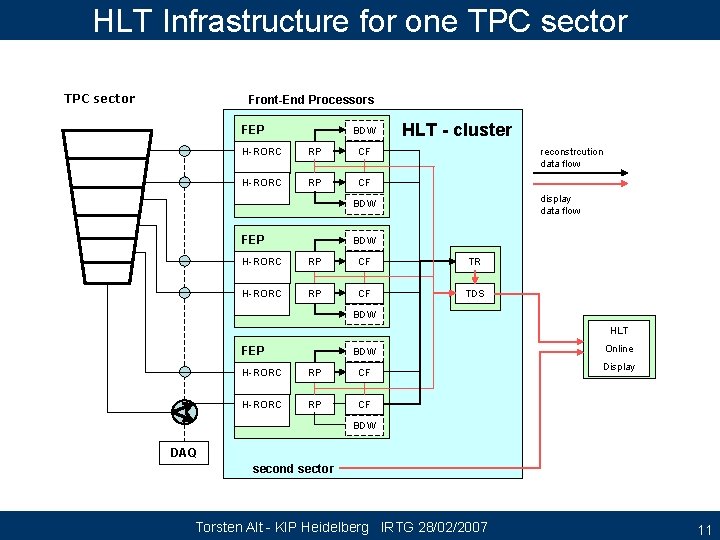

HLT Infrastructure for one TPC sector Front-End Processors FEP BDW H-RORC RP CF HLT - cluster reconstrcution data flow display data flow BDW FEP BDW H-RORC RP CF TR H-RORC RP CF TDS BDW HLT FEP BDW H-RORC RP CF Online Display BDW DAQ second sector Torsten Alt - KIP Heidelberg IRTG 28/02/2007 11

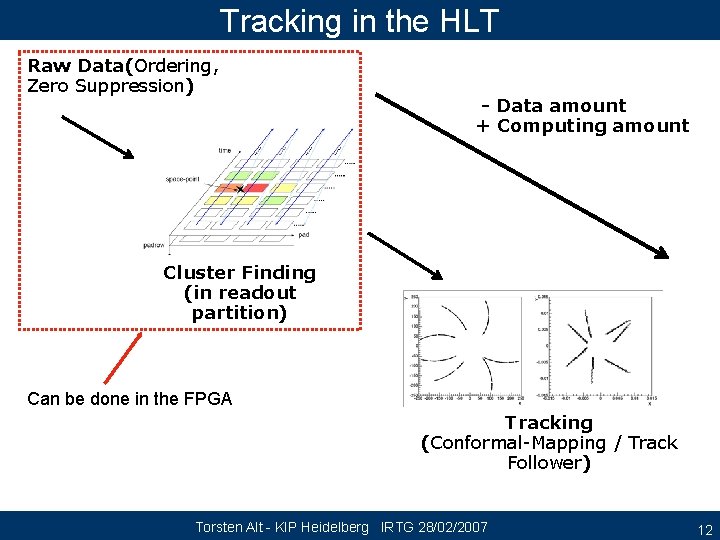

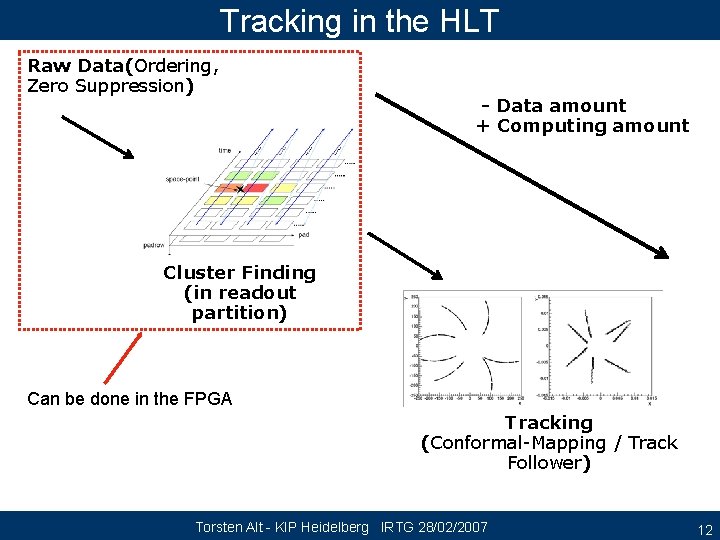

Tracking in the HLT Raw Data(Ordering, Zero Suppression) - Data amount + Computing amount Cluster Finding (in readout partition) Can be done in the FPGA Tracking (Conformal-Mapping / Track Follower) Torsten Alt - KIP Heidelberg IRTG 28/02/2007 12

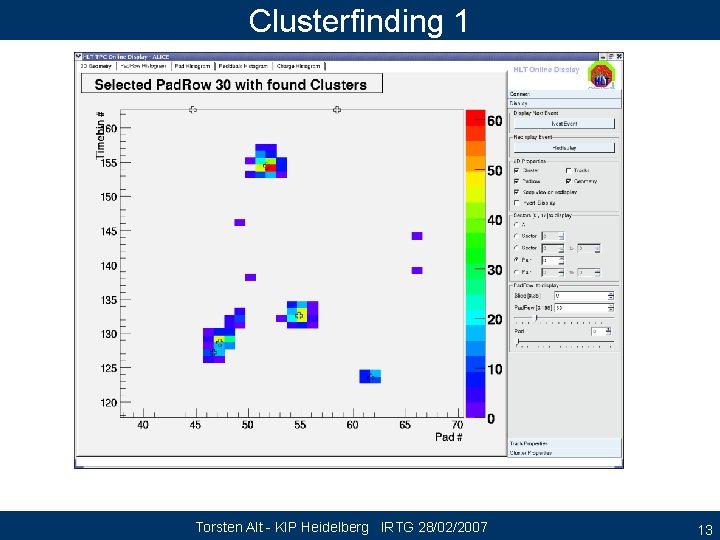

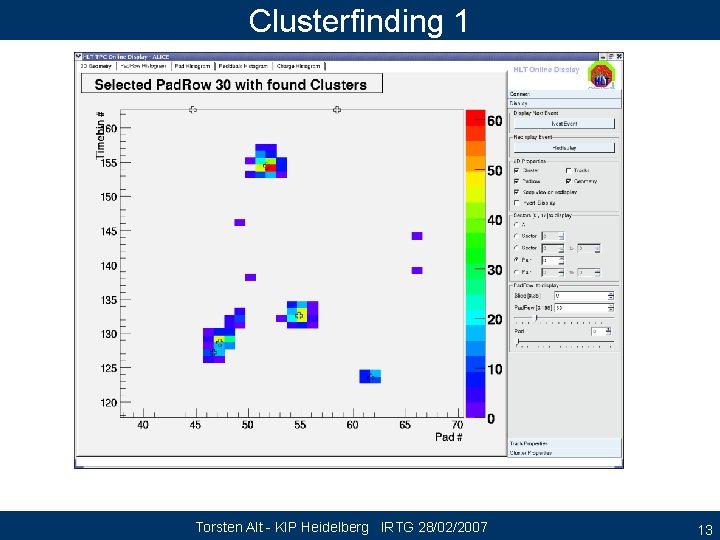

Clusterfinding 1 Torsten Alt - KIP Heidelberg IRTG 28/02/2007 13

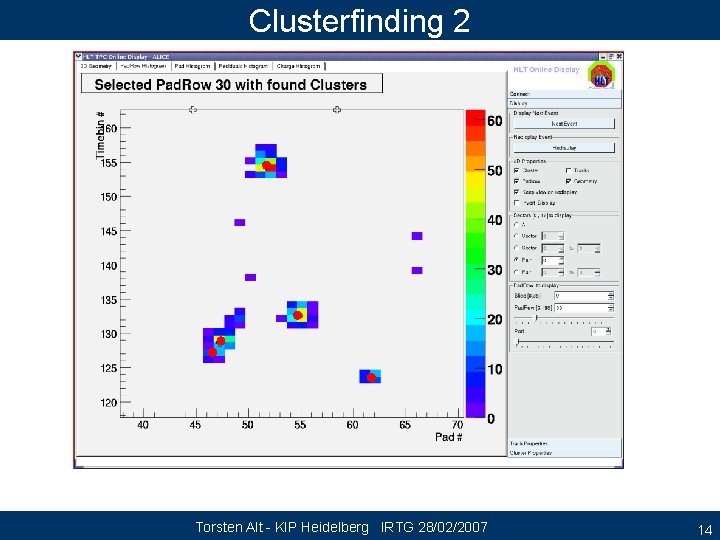

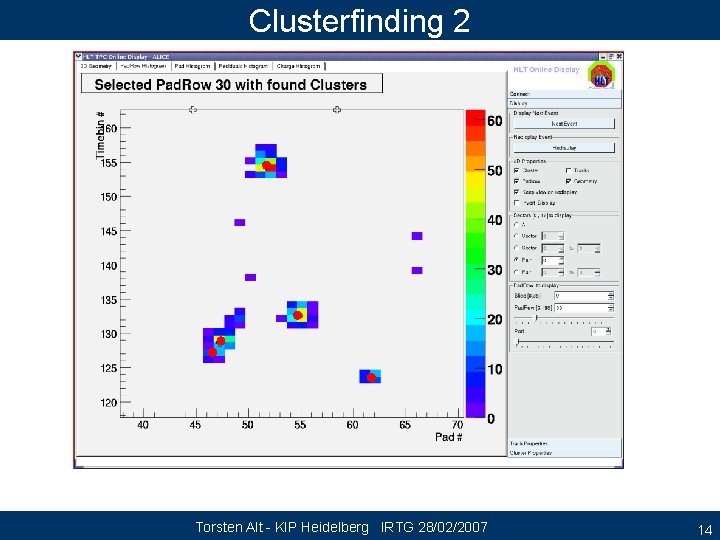

Clusterfinding 2 Torsten Alt - KIP Heidelberg IRTG 28/02/2007 14

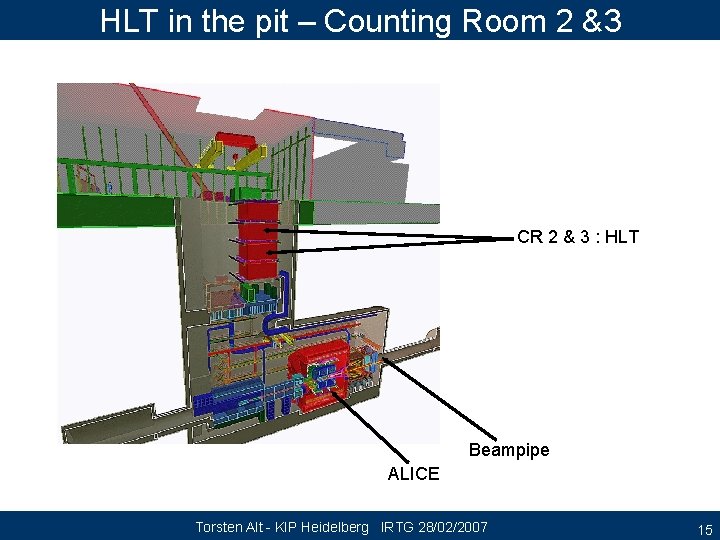

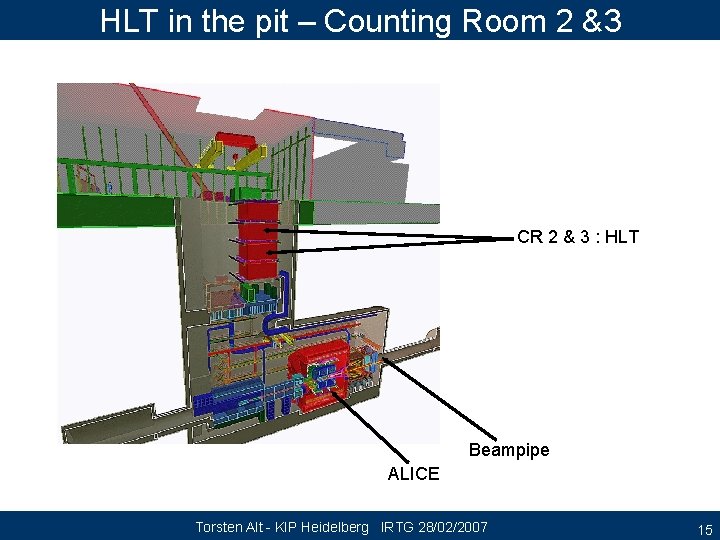

HLT in the pit – Counting Room 2 &3 CR 2 & 3 : HLT Beampipe ALICE Torsten Alt - KIP Heidelberg IRTG 28/02/2007 15

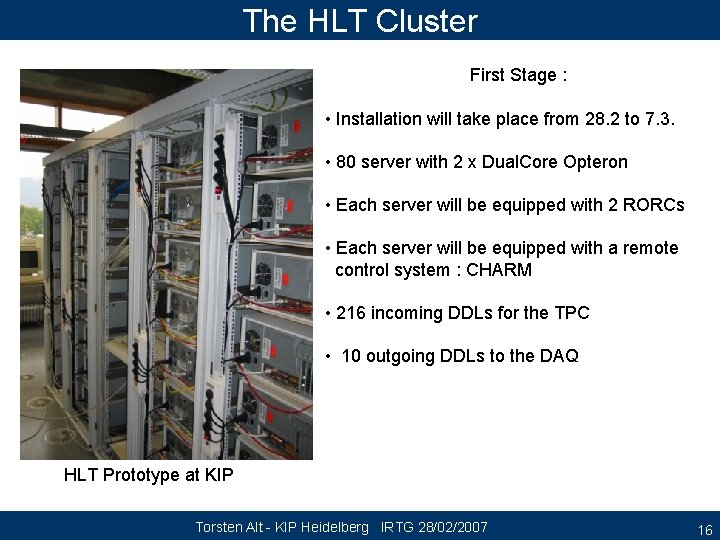

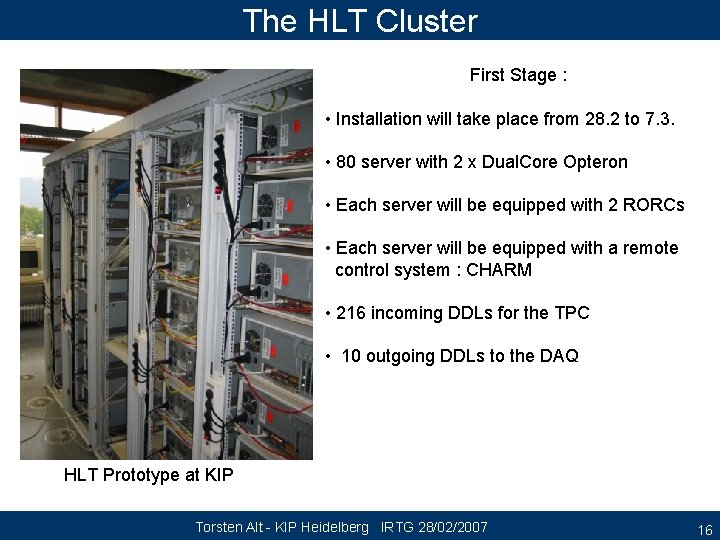

The HLT Cluster First Stage : • Installation will take place from 28. 2 to 7. 3. • 80 server with 2 x Dual. Core Opteron • Each server will be equipped with 2 RORCs • Each server will be equipped with a remote control system : CHARM • 216 incoming DDLs for the TPC • 10 outgoing DDLs to the DAQ HLT Prototype at KIP Torsten Alt - KIP Heidelberg IRTG 28/02/2007 16

The H-RORC Torsten Alt - KIP Heidelberg IRTG 28/02/2007 17

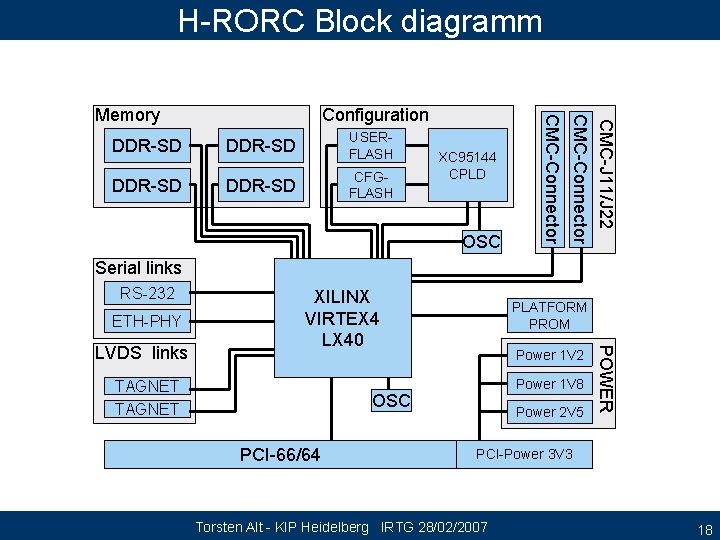

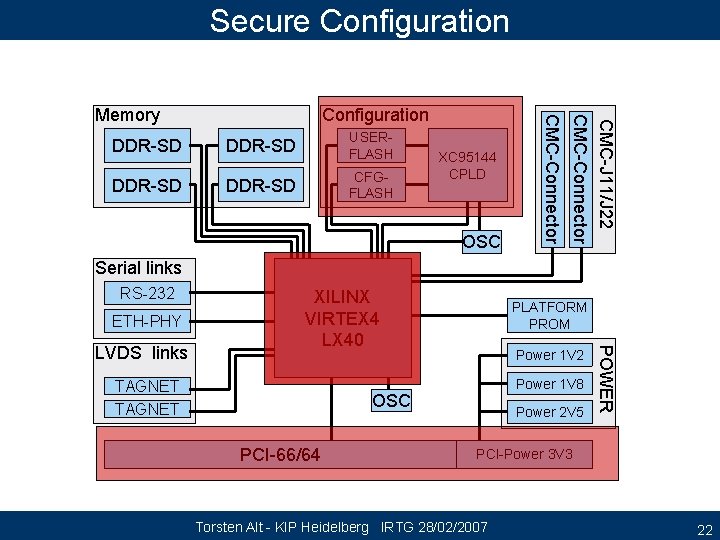

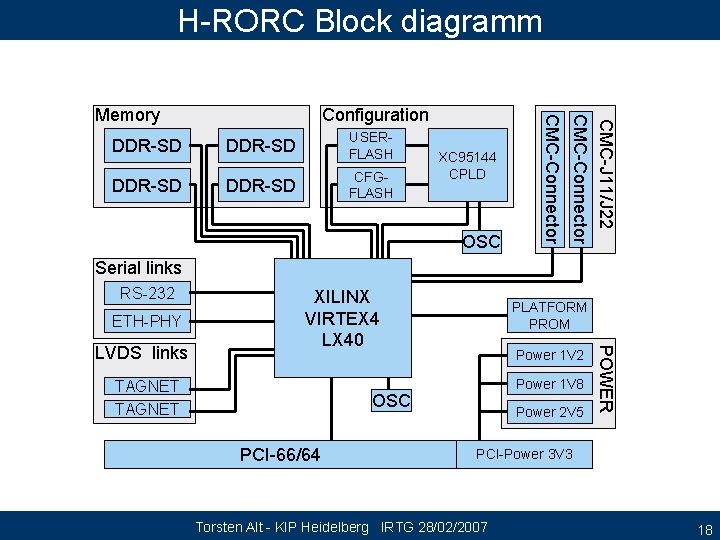

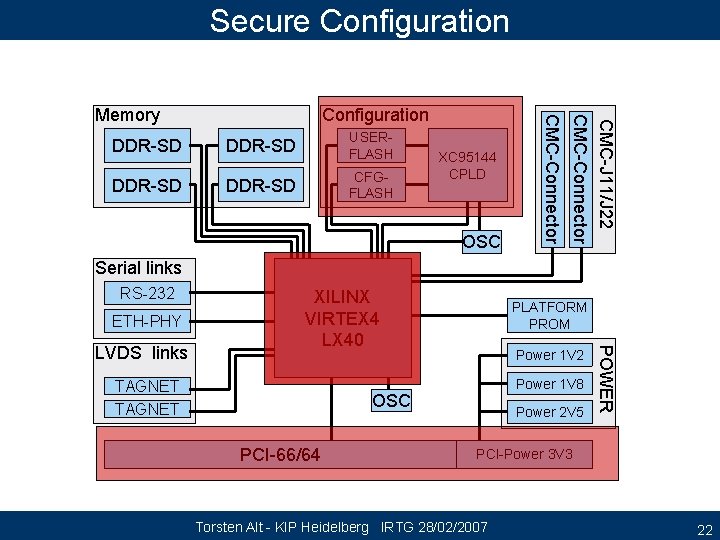

H-RORC Block diagramm DDR-SD USERFLASH DDR-SD CFGFLASH XC 95144 CPLD OSC CMC-J 11/J 22 CMC-Connector Configuration CMC-Connector Memory Serial links RS-232 ETH-PHY TAGNET PLATFORM PROM Power 1 V 2 Power 1 V 8 OSC PCI-66/64 Power 2 V 5 POWER LVDS links XILINX VIRTEX 4 LX 40 PCI-Power 3 V 3 Torsten Alt - KIP Heidelberg IRTG 28/02/2007 18

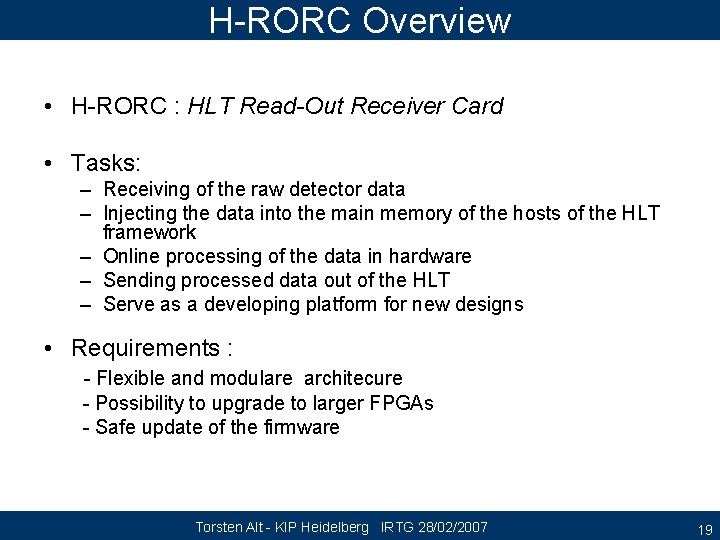

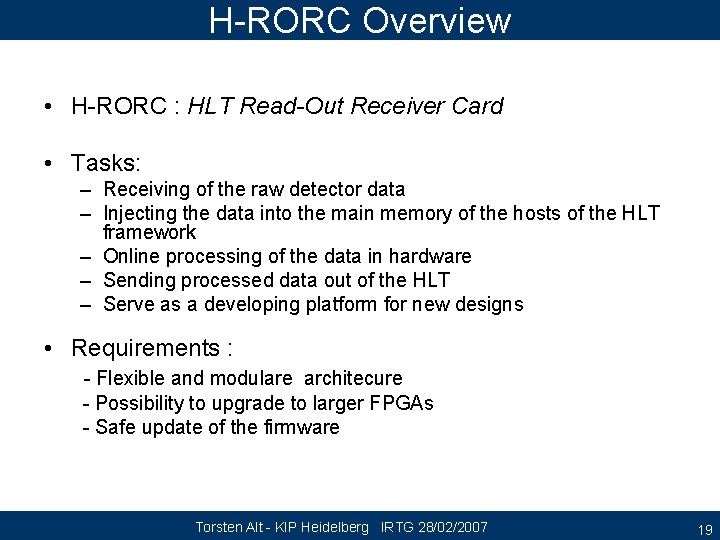

H-RORC Overview • H-RORC : HLT Read-Out Receiver Card • Tasks: – Receiving of the raw detector data – Injecting the data into the main memory of the hosts of the HLT framework – Online processing of the data in hardware – Sending processed data out of the HLT – Serve as a developing platform for new designs • Requirements : - Flexible and modulare architecure - Possibility to upgrade to larger FPGAs - Safe update of the firmware Torsten Alt - KIP Heidelberg IRTG 28/02/2007 19

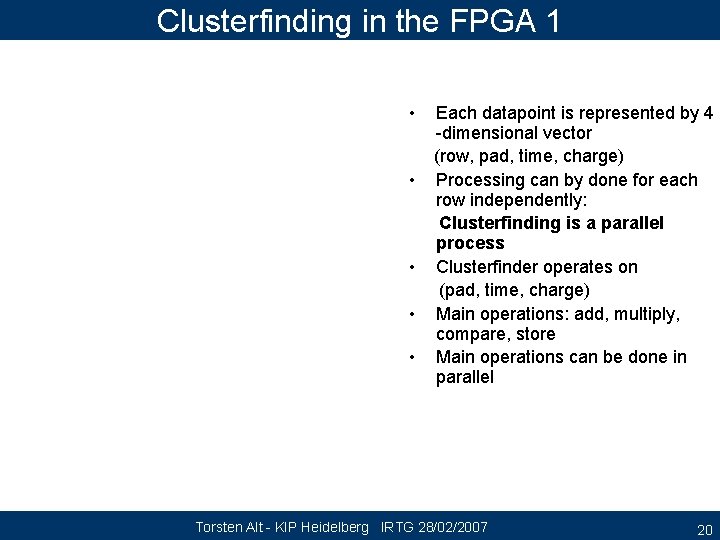

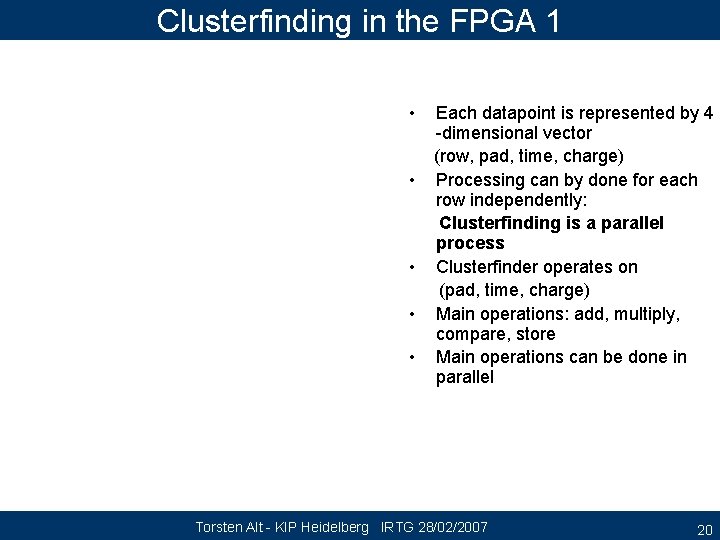

Clusterfinding in the FPGA 1 • • • Each datapoint is represented by 4 -dimensional vector (row, pad, time, charge) Processing can by done for each row independently: Clusterfinding is a parallel process Clusterfinder operates on (pad, time, charge) Main operations: add, multiply, compare, store Main operations can be done in parallel Torsten Alt - KIP Heidelberg IRTG 28/02/2007 20

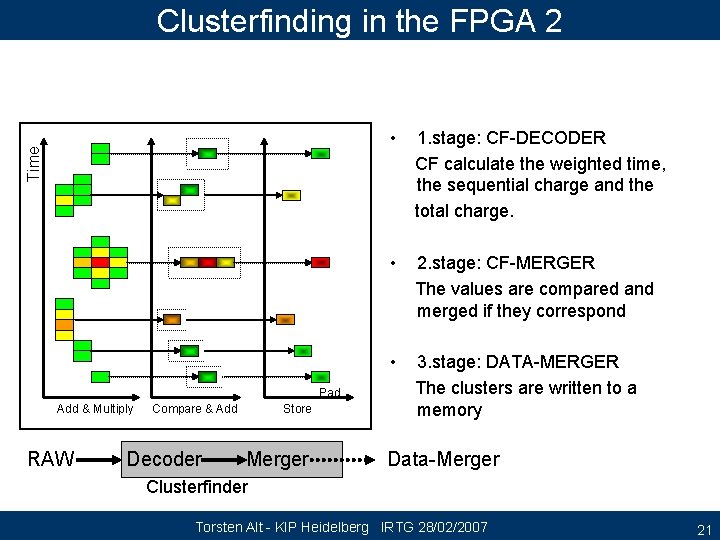

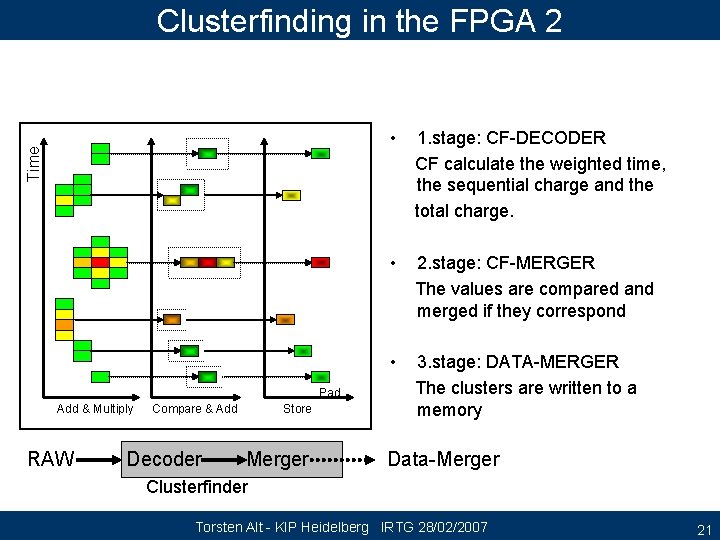

Time Clusterfinding in the FPGA 2 Pad Add & Multiply RAW Compare & Add Decoder Store Merger • 1. stage: CF-DECODER CF calculate the weighted time, the sequential charge and the total charge. • 2. stage: CF-MERGER The values are compared and merged if they correspond • 3. stage: DATA-MERGER The clusters are written to a memory Data-Merger Clusterfinder Torsten Alt - KIP Heidelberg IRTG 28/02/2007 21

Secure Configuration DDR-SD USERFLASH DDR-SD CFGFLASH XC 95144 CPLD OSC CMC-J 11/J 22 CMC-Connector Configuration CMC-Connector Memory Serial links RS-232 ETH-PHY TAGNET PLATFORM PROM Power 1 V 2 Power 1 V 8 OSC PCI-66/64 Power 2 V 5 POWER LVDS links XILINX VIRTEX 4 LX 40 PCI-Power 3 V 3 Torsten Alt - KIP Heidelberg IRTG 28/02/2007 22

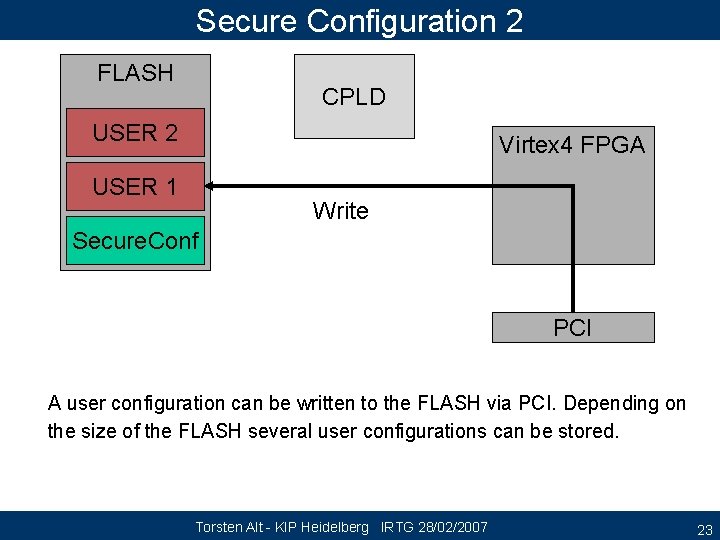

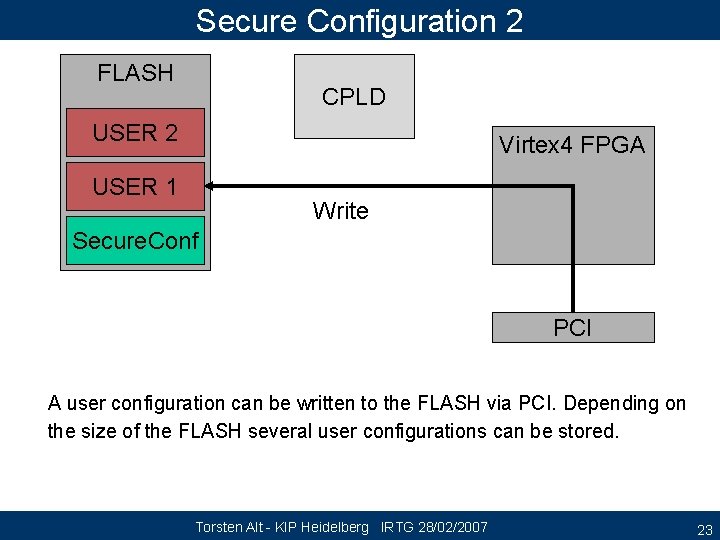

Secure Configuration 2 FLASH CPLD USER 2 Virtex 4 FPGA USER 1 Write Secure. Conf PCI A user configuration can be written to the FLASH via PCI. Depending on the size of the FLASH several user configurations can be stored. Torsten Alt - KIP Heidelberg IRTG 28/02/2007 23

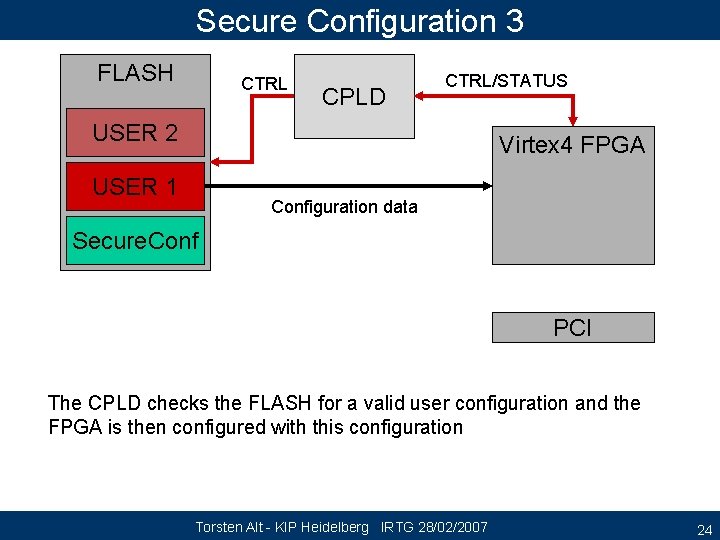

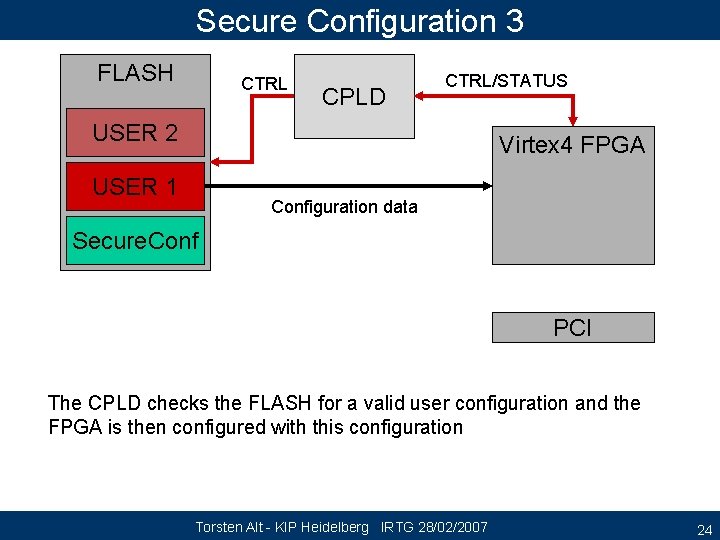

Secure Configuration 3 FLASH CTRL CPLD CTRL/STATUS USER 2 Virtex 4 FPGA USER 1 Configuration data Secure. Conf PCI The CPLD checks the FLASH for a valid user configuration and the FPGA is then configured with this configuration Torsten Alt - KIP Heidelberg IRTG 28/02/2007 24

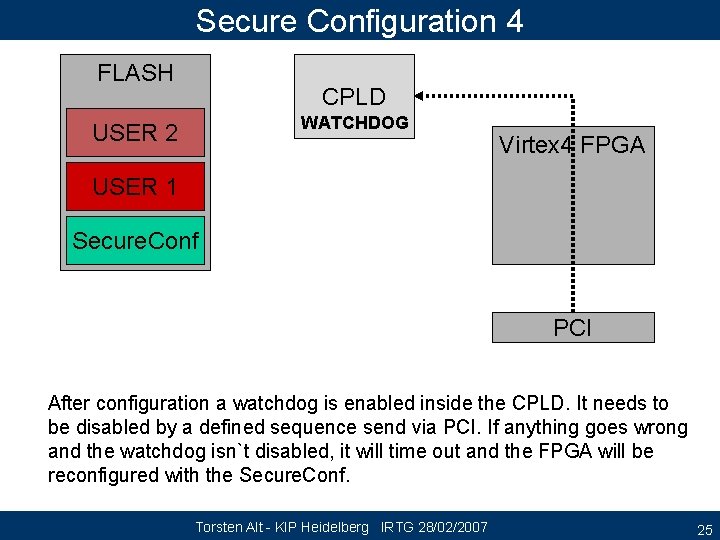

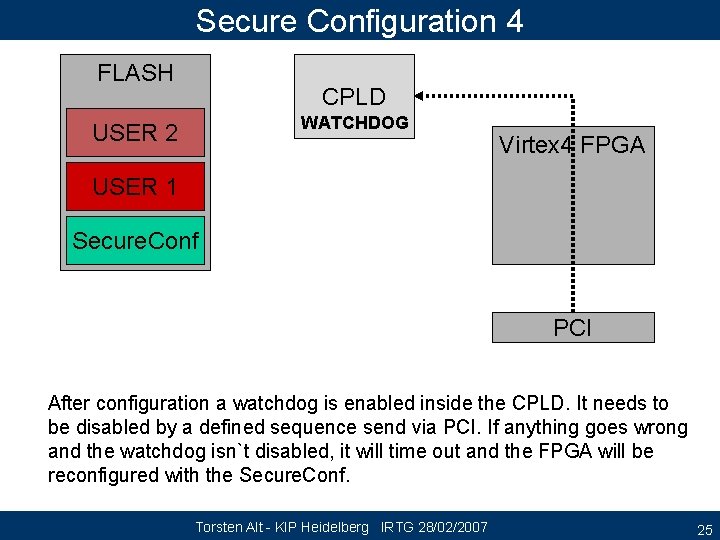

Secure Configuration 4 FLASH CPLD WATCHDOG USER 2 Virtex 4 FPGA USER 1 Secure. Conf PCI After configuration a watchdog is enabled inside the CPLD. It needs to be disabled by a defined sequence send via PCI. If anything goes wrong and the watchdog isn`t disabled, it will time out and the FPGA will be reconfigured with the Secure. Conf. Torsten Alt - KIP Heidelberg IRTG 28/02/2007 25

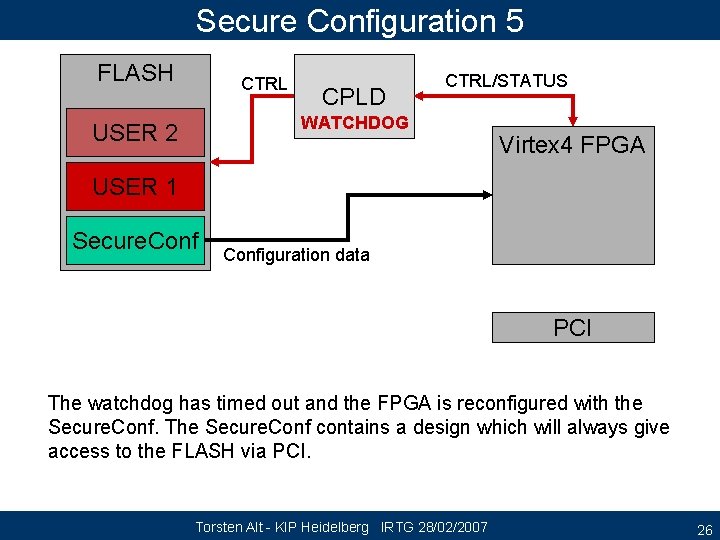

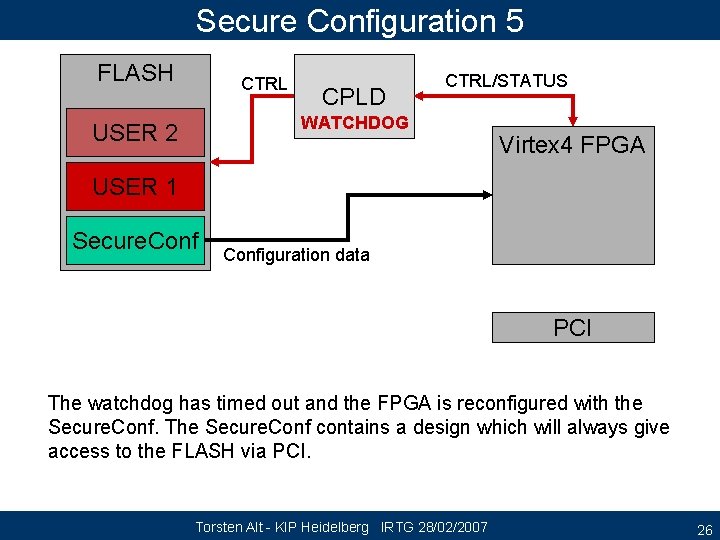

Secure Configuration 5 FLASH CTRL CPLD CTRL/STATUS WATCHDOG USER 2 Virtex 4 FPGA USER 1 Secure. Configuration data PCI The watchdog has timed out and the FPGA is reconfigured with the Secure. Conf. The Secure. Conf contains a design which will always give access to the FLASH via PCI. Torsten Alt - KIP Heidelberg IRTG 28/02/2007 26