ALICE ASICs A Kluge 14 Feb 2019 SAMPA

ALICE ASICs A. Kluge 14 Feb, 2019

SAMPA TSMC 130 nm ALICE 32 -channel mixed mode TPC/MCH common front-end ASIC incl. front-end, ADC, DSP University of Sao Paulo (USP), University of Bergen, CERN (consultancy) Finished and fully produced Technical problems Single event latch-up (SEL) detected in commercial memory library Analysis of schematics and layout, Laser and radiation tests campaign, Replacement of problematic memory cells, resubmission, laser and radiation test campaign, all initiated by Electronics coordination All resolved No impact on schedule as 2 nd submission was foreseen in schedule Comments Initiated and coordinated by ALICE electronics coordination A. Kluge Increase initially unexperienced small team to a large appropriately sized team Consolidate design specifications given by detector team Intensive coordination between designers and detector teams using the ASIC, for design specification, design, prototype test and application test in the fore field of ASIC submissions full system mixed/mode sign-off simulations verified system functionality before simulation , 14 Feb, 2019 2

ALPIDE Towerjazz CMOS 180 nm, ALICE Monolithic active pixel ASIC, integrating sensor and read-out ASIC, (15 x 30 mm 2, 29 um x 27 um pixel size) CCNU Wuhan, CERN Geneva, YONSEI Seoul, INFN Cagliari, INFN Torino, IPHC Strasbourg, IRFU Saclay, NIKHEF Amsterdam Finished and fully produced Technical problems On-chip power supply decoupling of PLL, single-event-latch up on custom block Analysis/measurements of problem in lab and in beam, separation of power supply/increase substrate contact and re-submission All resolved None impact on schedule as sufficient contingency was available in the planning Comments A. Kluge ASIC system specifications team, ASIC designers and test team were working in close relationship during all phases of the design with strong in-project electronics coordination between the teams full system mixed/mode sign-off simulations verified system functionality before simulation top-down design approach, dedicated verification engineer implemented by in-project electronics coordination distributed design team made efficient work more difficult. , 14 Feb, 2019 3

FEERIC AMS, CMOS 0. 35 um; 8 -ch. RPC front-end ASIC LPC Clermont-Ferrand Finished and fully produced A. Kluge , 14 Feb, 2019 4

TDCpix (NA 62) IBM/GF 130 nm, Pixel ASIC with 100 ps time binning CERN Finished and fully produced Technical problems Integration in available space All resolved No impact on schedule First submission was fully functional Comments ASIC design team and team driving the specifications were largely overlapping; no changes during design phase Full system analog/digital sign-off simulations on component and system level before submission Strong inter-disciplinary coordination in planning phase for electro-mechanical integration, specification, design and test A. Kluge , 14 Feb, 2019 5

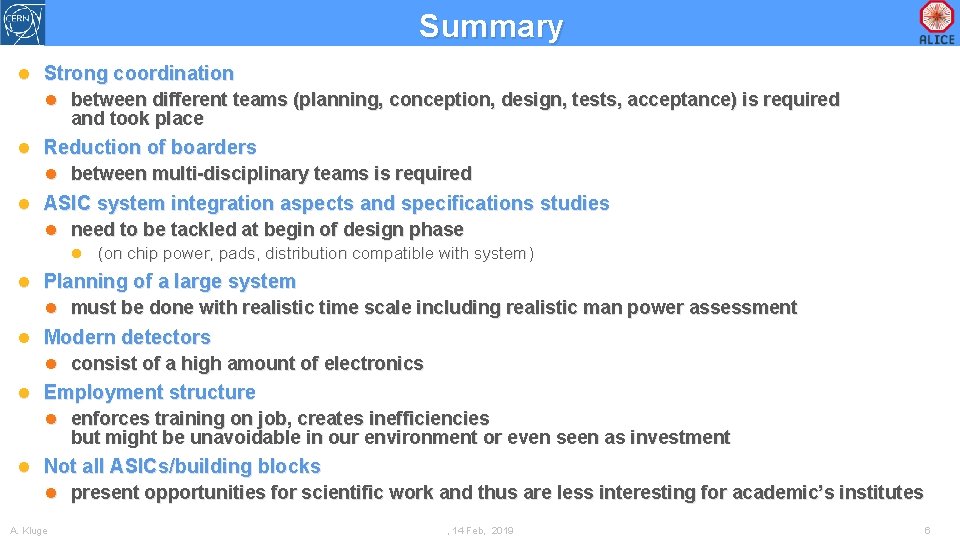

Summary Strong coordination between different teams (planning, conception, design, tests, acceptance) is required and took place Reduction of boarders between multi-disciplinary teams is required ASIC system integration aspects and specifications studies need to be tackled at begin of design phase (on chip power, pads, distribution compatible with system) Planning of a large system must be done with realistic time scale including realistic man power assessment Modern detectors consist of a high amount of electronics Employment structure enforces training on job, creates inefficiencies but might be unavoidable in our environment or even seen as investment Not all ASICs/building blocks present opportunities for scientific work and thus are less interesting for academic’s institutes A. Kluge , 14 Feb, 2019 6

- Slides: 6