AIST ESIP New Observing Strategies NOS Enabling New

AIST & ESIP New Observing Strategies (NOS) Enabling New Observation Strategies Through On-board Computing and System Virtualization Matthew French USC, Information Sciences Institute February 25 th, 2020

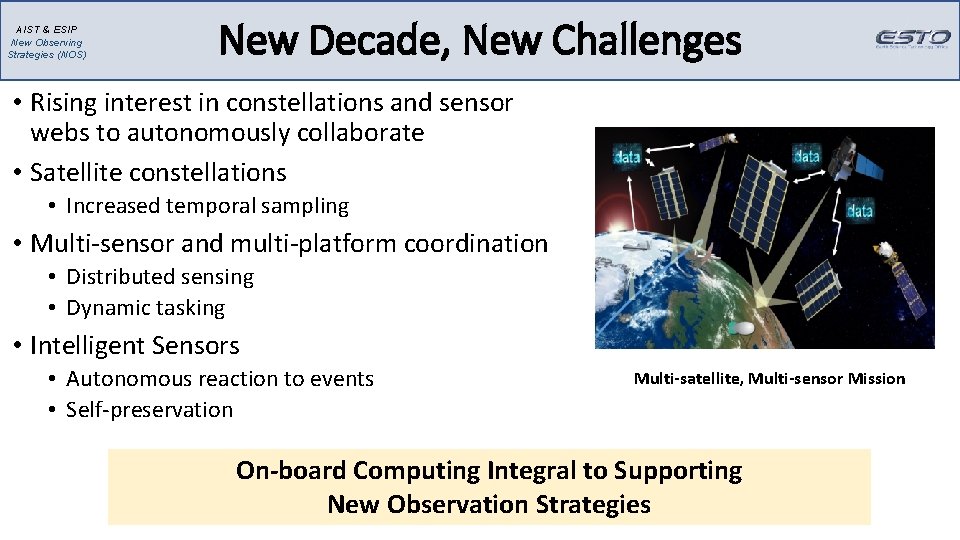

AIST & ESIP New Observing Strategies (NOS) New Decade, New Challenges • Rising interest in constellations and sensor webs to autonomously collaborate • Satellite constellations • Increased temporal sampling • Multi-sensor and multi-platform coordination • Distributed sensing • Dynamic tasking • Intelligent Sensors • Autonomous reaction to events • Self-preservation Multi-satellite, Multi-sensor Mission On-board Computing Integral to Supporting New Observation Strategies

AIST & ESIP New Observing Strategies (NOS) NOS Computing Needs • New on-board computing hardware • Streaming DSP vs Multi-threaded, Multi-core • On-board look ahead data products • New programming models to support heterogeneous hardware • Multiple compilers • FPGA code development time • Portability across platform and processor types • New methodologies for simulating and verifying System of Systems • Scalability to address 10 s to 1, 000 s of platforms

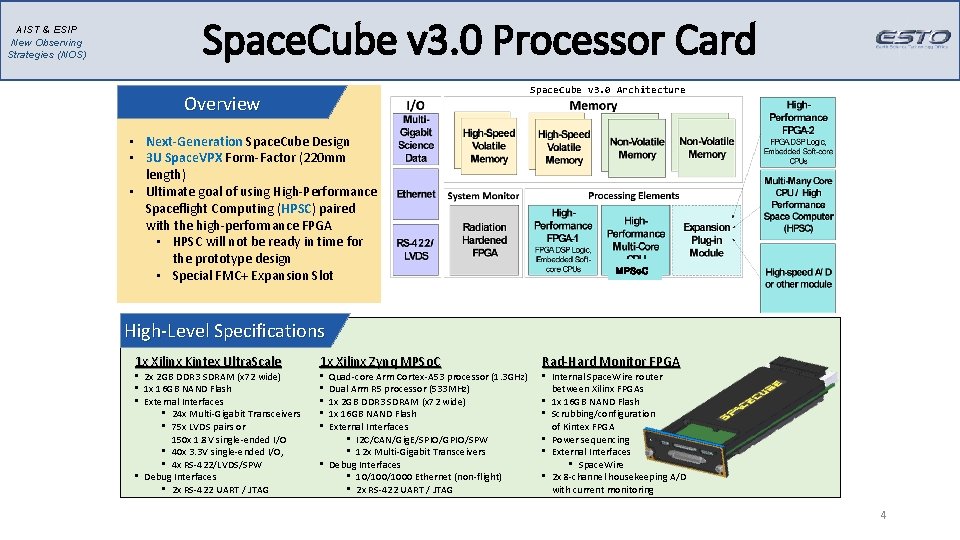

AIST & ESIP New Observing Strategies (NOS) Space. Cube v 3. 0 Processor Card Space. Cube v 3. 0 Architecture Overview • Next-Generation Space. Cube Design • 3 U Space. VPX Form-Factor (220 mm length) • Ultimate goal of using High-Performance Spaceflight Computing (HPSC) paired with the high-performance FPGA • HPSC will not be ready in time for the prototype design • Special FMC+ Expansion Slot MPSo. C High-Level Specifications 1 x Xilinx Kintex Ultra. Scale • 2 x 2 GB DDR 3 SDRAM (x 72 wide) • 1 x 16 GB NAND Flash • External Interfaces • 24 x Multi-Gigabit Transceivers • 75 x LVDS pairs or 150 x 1. 8 V single-ended I/O • 40 x 3. 3 V single-ended I/O, • 4 x RS-422/LVDS/SPW • Debug Interfaces • 2 x RS-422 UART / JTAG 1 x Xilinx Zynq MPSo. C Quad-core Arm Cortex-A 53 processor (1. 3 GHz) Dual Arm R 5 processor (533 MHz) 1 x 2 GB DDR 3 SDRAM (x 72 wide) 1 x 16 GB NAND Flash External Interfaces • I 2 C/CAN/Gig. E/SPIO/GPIO/SPW • 12 x Multi-Gigabit Transceivers • Debug Interfaces • 10/1000 Ethernet (non-flight) • 2 x RS-422 UART / JTAG • • • Rad-Hard Monitor FPGA • Internal Space. Wire router between Xilinx FPGAs • 1 x 16 GB NAND Flash • Scrubbing/configuration of Kintex FPGA • Power sequencing • External Interfaces • Space. Wire • 2 x 8 -channel housekeeping A/D with current monitoring 4

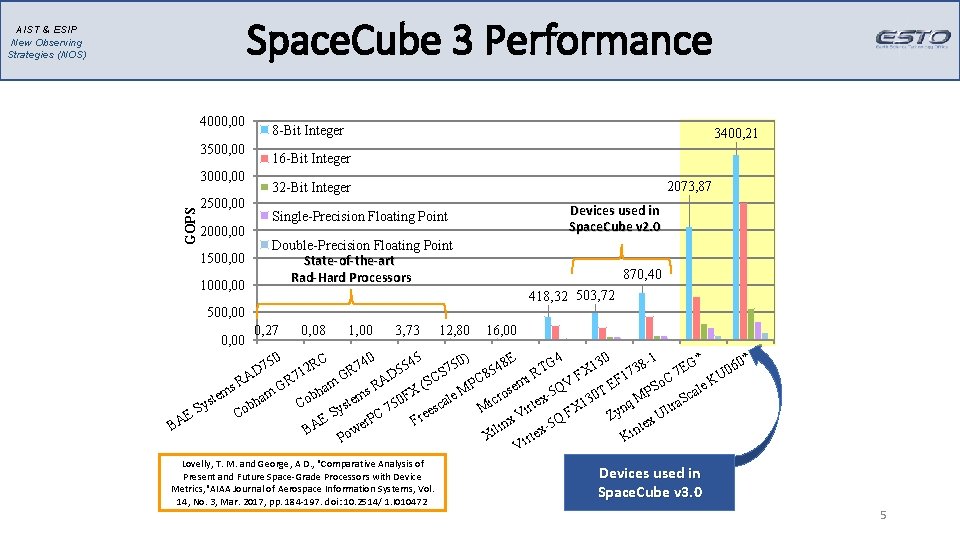

Space. Cube 3 Performance AIST & ESIP New Observing Strategies (NOS) 4000, 00 3500, 00 GOPS 3000, 00 2500, 00 2000, 00 1500, 00 1000, 00 8 -Bit Integer 3400, 21 16 -Bit Integer 2073, 87 32 -Bit Integer Devices used in Space. Cube v 2. 0 Single-Precision Floating Point Double-Precision Floating Point State-of-the-art Rad-Hard Processors 870, 40 418, 32 503, 72 500, 00 0, 27 0, 08 1, 00 3, 73 12, 80 16, 00 ) -1 40 30 45 0* 8 E G* G 4 50 RC 8 7 1 5 6 4 E 7 2 3 T 5 0 5 R 1 7 D FX G i. R CS C 7 e KU C 8 F 1 A R 7 S R o V m P m ( E R G e s a PS cal -5 Q bh 0 T e M icros em FX ms am l M t x o 3 S e 0 s a h t e a 1 q C 75 M X irt ys ltr ob Sy esc yn F S e C V C U E Z r P E x F r tex BA -5 Q lin n i BA we x i e o X K rt P Vi 0 75 D A Lovelly, T. M. and George, A D. , "Comparative Analysis of Present and Future Space-Grade Processors with Device Metrics, "AIAA Journal of Aerospace Information Systems, Vol. 14, No. 3, Mar. 2017, pp. 184 -197. doi: 10. 2514/ 1. I 010472 Devices used in Space. Cube v 3. 0 5

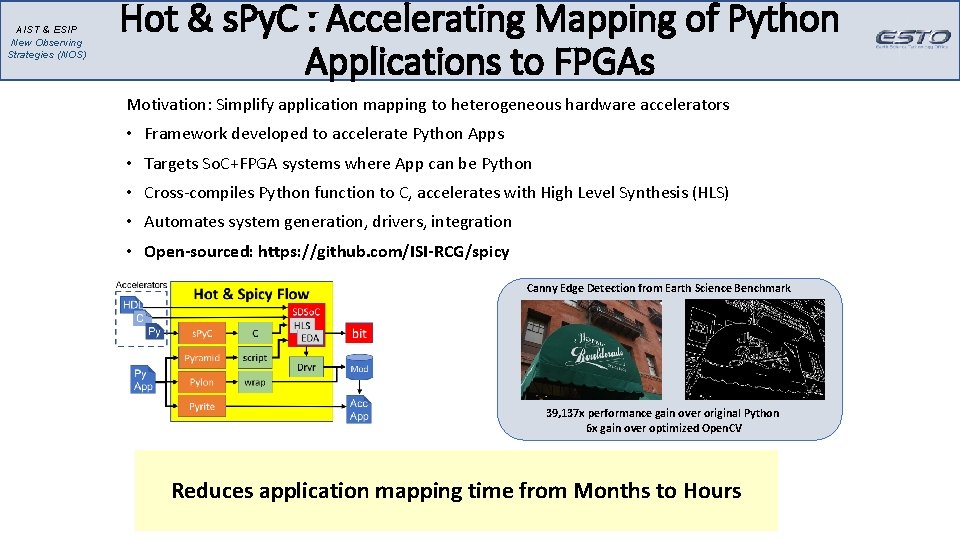

AIST & ESIP New Observing Strategies (NOS) Hot & s. Py. C : Accelerating Mapping of Python Applications to FPGAs Motivation: Simplify application mapping to heterogeneous hardware accelerators • Framework developed to accelerate Python Apps • Targets So. C+FPGA systems where App can be Python • Cross-compiles Python function to C, accelerates with High Level Synthesis (HLS) • Automates system generation, drivers, integration • Open-sourced: https: //github. com/ISI-RCG/spicy Canny Edge Detection from Earth Science Benchmark 39, 137 x performance gain over original Python 6 x gain over optimized Open. CV Reduces application mapping time from Months to Hours

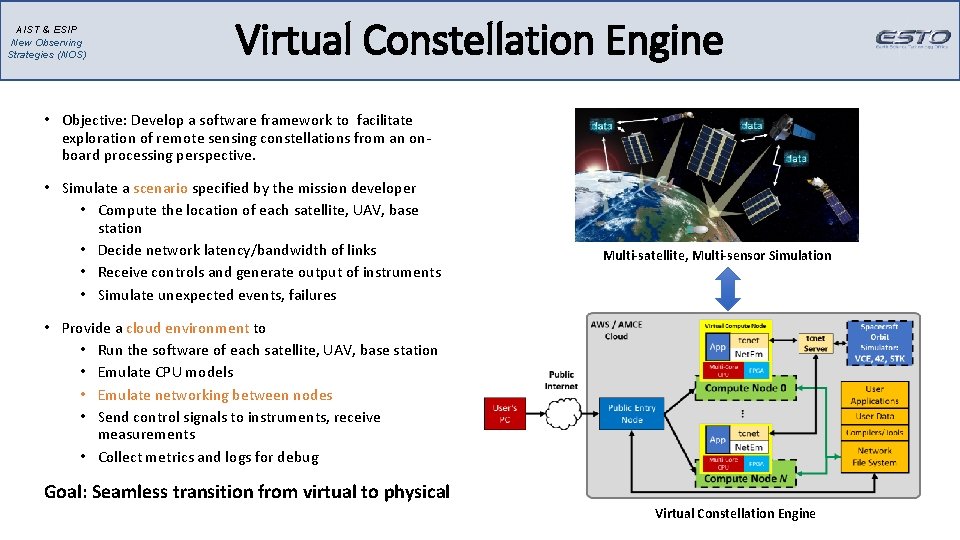

AIST & ESIP New Observing Strategies (NOS) Virtual Constellation Engine • Objective: Develop a software framework to facilitate exploration of remote sensing constellations from an onboard processing perspective. • Simulate a scenario specified by the mission developer • Compute the location of each satellite, UAV, base station • Decide network latency/bandwidth of links • Receive controls and generate output of instruments • Simulate unexpected events, failures Multi-satellite, Multi-sensor Simulation • Provide a cloud environment to • Run the software of each satellite, UAV, base station • Emulate CPU models • Emulate networking between nodes • Send control signals to instruments, receive measurements • Collect metrics and logs for debug Goal: Seamless transition from virtual to physical Virtual Constellation Engine

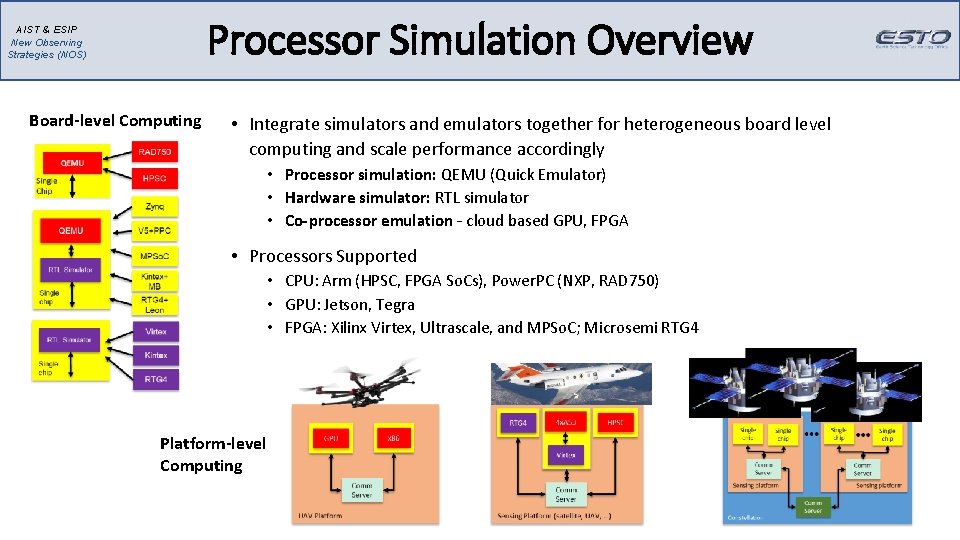

Processor Simulation Overview AIST & ESIP New Observing Strategies (NOS) Board-level Computing • Integrate simulators and emulators together for heterogeneous board level computing and scale performance accordingly • Processor simulation: QEMU (Quick Emulator) • Hardware simulator: RTL simulator • Co-processor emulation – cloud based GPU, FPGA • Processors Supported • CPU: Arm (HPSC, FPGA So. Cs), Power. PC (NXP, RAD 750) • GPU: Jetson, Tegra • FPGA: Xilinx Virtex, Ultrascale, and MPSo. C; Microsemi RTG 4 Platform-level Computing

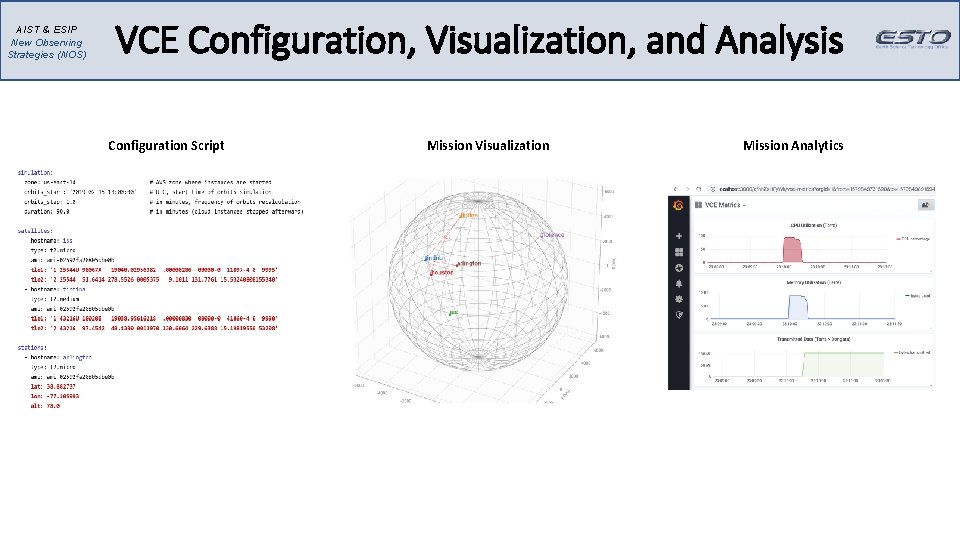

AIST & ESIP New Observing Strategies (NOS) VCE Configuration, Visualization, and Analysis Configuration Script Mission Visualization Mission Analytics

AIST & ESIP New Observing Strategies (NOS) Summary • Advanced onboard processors, compilers, and cloud based constellation emulation are potential cross-cutting enablers for the NOS testbed • Areas of future research and development • Integration with other NOS mission planning tools • Interaction with emerging NOS missions to drive use cases and interfaces Space. Cube 3 Hardware Prototype

- Slides: 10