AIDA Frontend Electronics progress report Mezzanine to FEE

- Slides: 8

AIDA Frontend Electronics progress report. • Mezzanine to FEE 64 connection. • Mezzanine Layout • FEE 64 layout • Digital channel analogue buffering. • Power. PC external memory • Power supply structure • Parts cost 9 th October 2008 AIDA FEE progress report P. J. Coleman-Smith 1

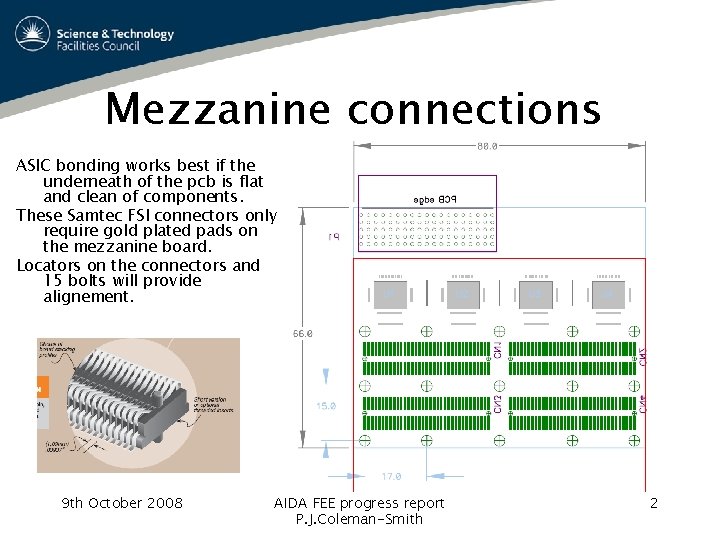

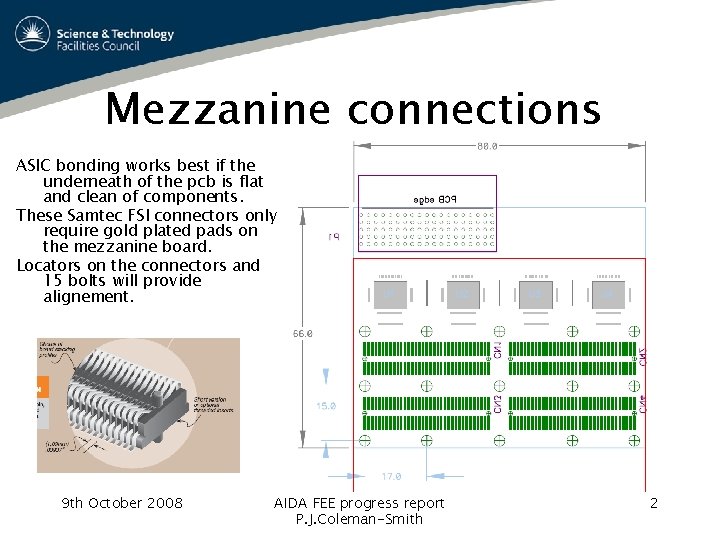

Mezzanine connections ASIC bonding works best if the underneath of the pcb is flat and clean of components. These Samtec FSI connectors only require gold plated pads on the mezzanine board. Locators on the connectors and 15 bolts will provide alignement. 9 th October 2008 AIDA FEE progress report P. J. Coleman-Smith 2

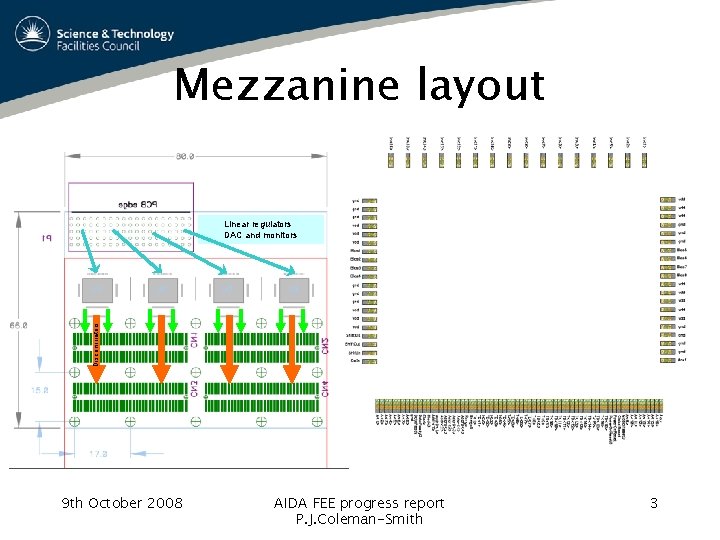

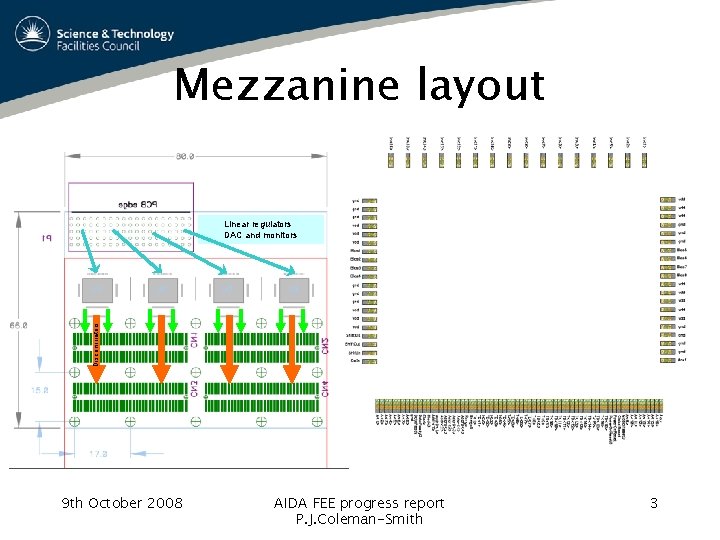

Mezzanine layout Discriminators Linear regulators DAC and monitors 9 th October 2008 AIDA FEE progress report P. J. Coleman-Smith 3

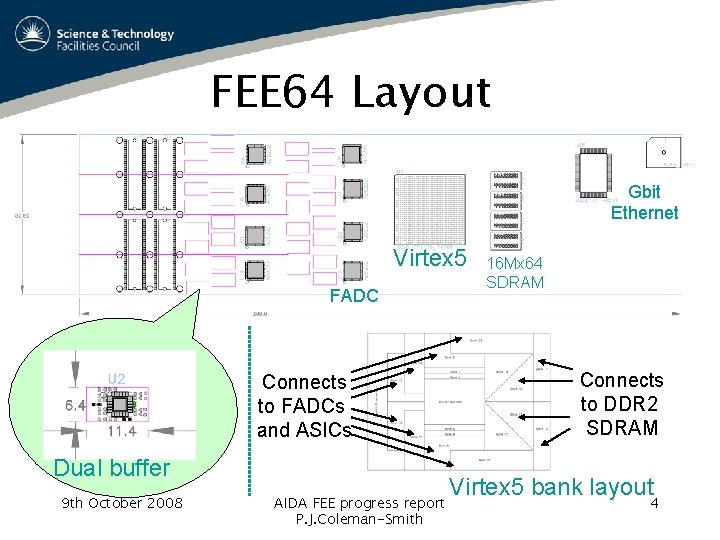

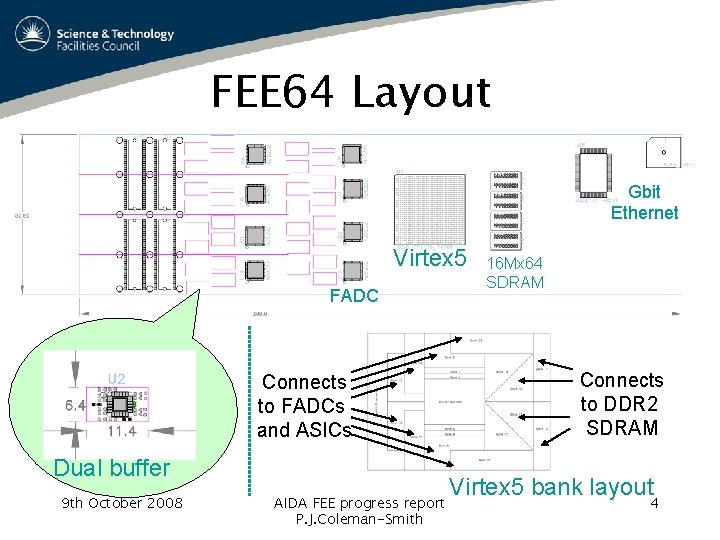

FEE 64 Layout Gbit Ethernet Virtex 5 FADC Connects to FADCs and ASICs Dual buffer 9 th October 2008 AIDA FEE progress report P. J. Coleman-Smith 16 Mx 64 SDRAM Connects to DDR 2 SDRAM Virtex 5 bank layout 4

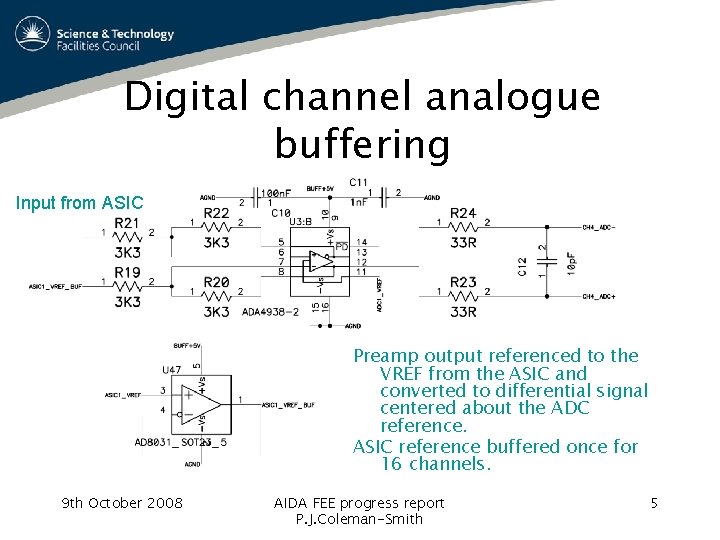

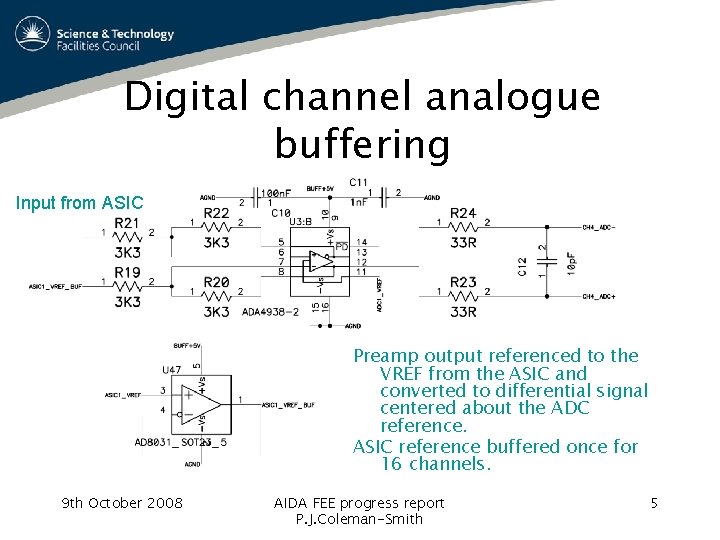

Digital channel analogue buffering Input from ASIC Preamp output referenced to the VREF from the ASIC and converted to differential signal centered about the ADC reference. ASIC reference buffered once for 16 channels. 9 th October 2008 AIDA FEE progress report P. J. Coleman-Smith 5

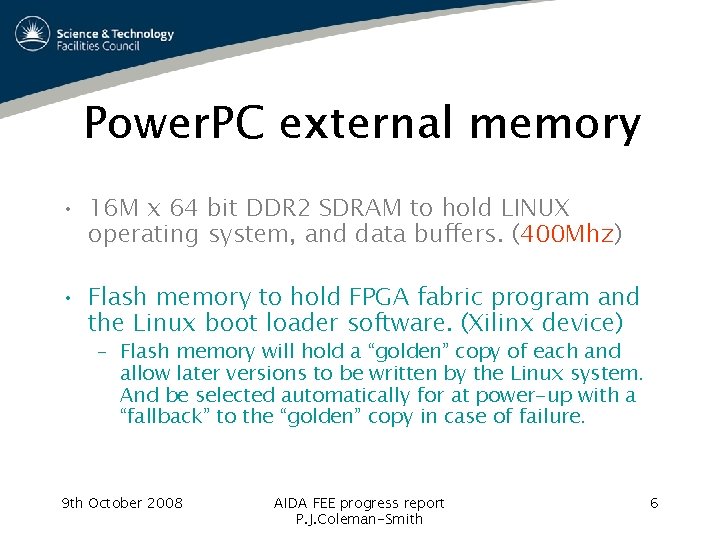

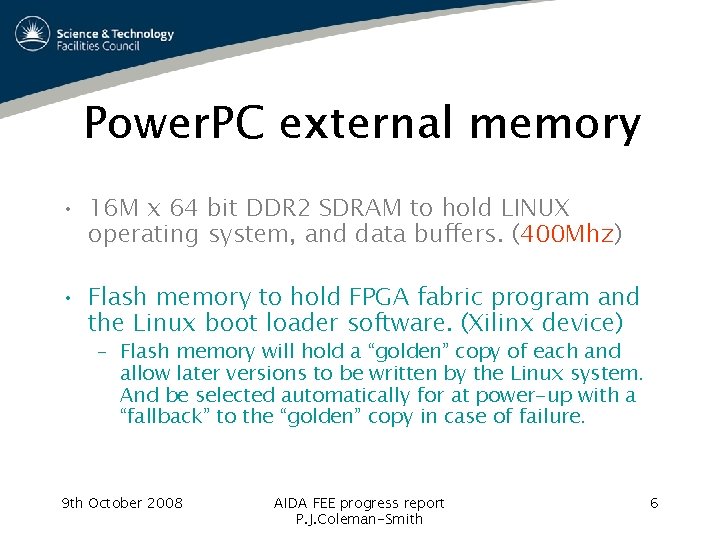

Power. PC external memory • 16 M x 64 bit DDR 2 SDRAM to hold LINUX operating system, and data buffers. (400 Mhz) • Flash memory to hold FPGA fabric program and the Linux boot loader software. (Xilinx device) – Flash memory will hold a “golden” copy of each and allow later versions to be written by the Linux system. And be selected automatically for at power-up with a “fallback” to the “golden” copy in case of failure. 9 th October 2008 AIDA FEE progress report P. J. Coleman-Smith 6

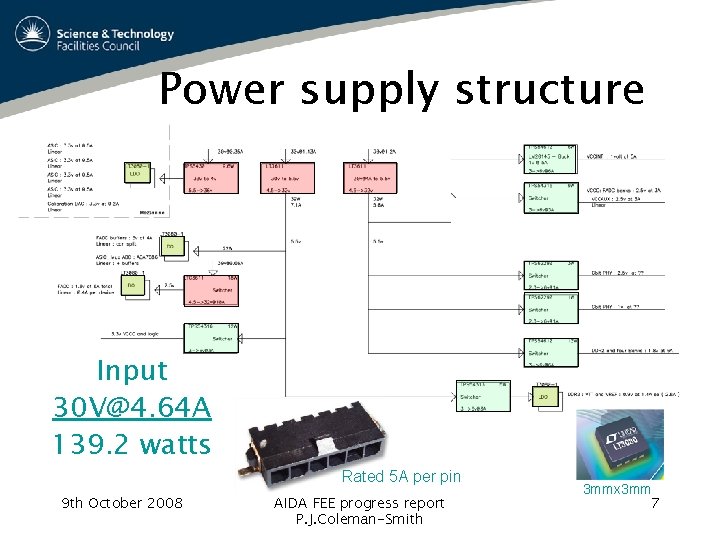

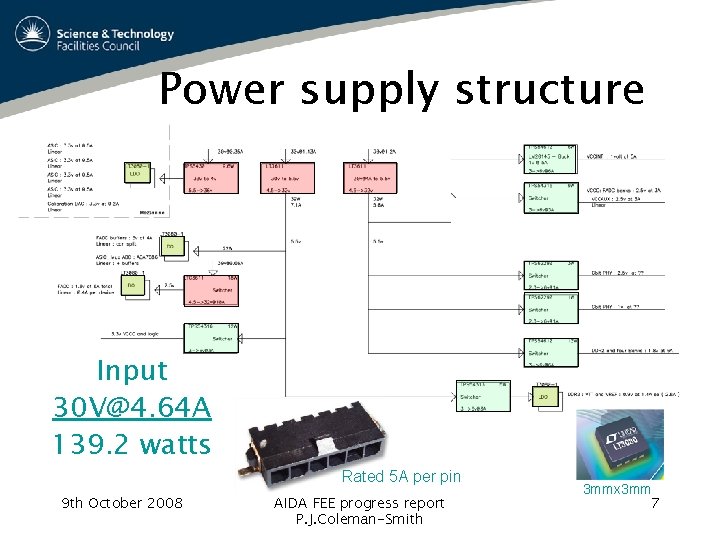

Power supply structure Input 30 V@4. 64 A 139. 2 watts Rated 5 A per pin 9 th October 2008 AIDA FEE progress report P. J. Coleman-Smith 3 mmx 3 mm 7

Parts cost Submitted BOM to assembler. Cost per FEE 64 £ 1300 when making 6 – Includes supported pricing for Xilinx parts. 9 th October 2008 AIDA FEE progress report P. J. Coleman-Smith 8