Agilent Technologies N 5416 A Automated USB 2

Agilent Technologies N 5416 A Automated USB 2. 0 Pre-Compliance Test Solution Technical Presentation

Today’s Schedule ä USB 2. 0 Overview ä USB 2. 0 Compliance Testing ä Examples of Compliance Tests ä Demo of the Agilent Solution ä Q&A

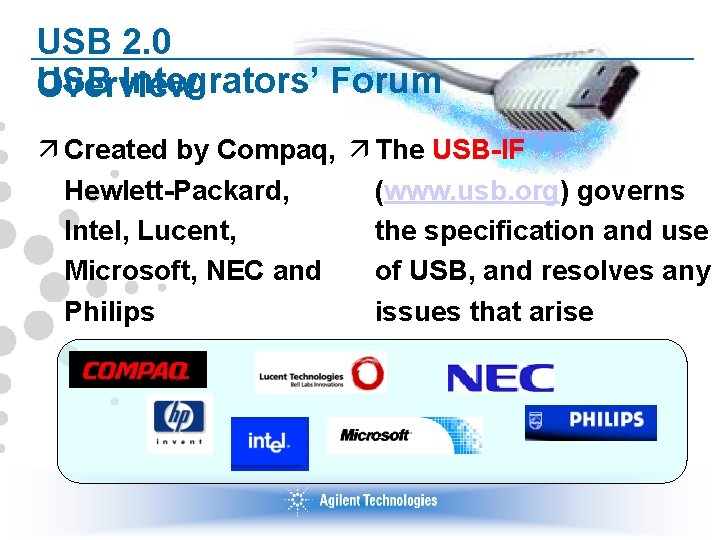

USB 2. 0 USB Integrators’ Forum Overview ä Created by Compaq, ä The USB-IF Hewlett-Packard, (www. usb. org) governs Intel, Lucent, the specification and use Microsoft, NEC and of USB, and resolves any Philips issues that arise

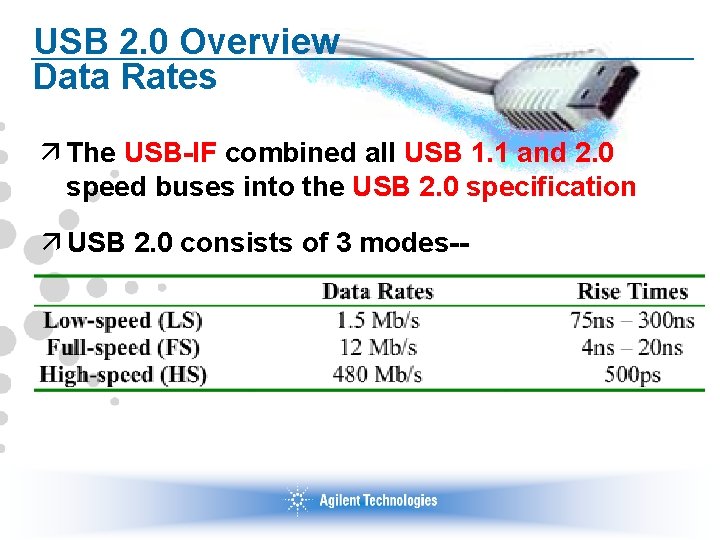

USB 2. 0 Overview Data Rates ä The USB-IF combined all USB 1. 1 and 2. 0 speed buses into the USB 2. 0 specification ä USB 2. 0 consists of 3 modes--

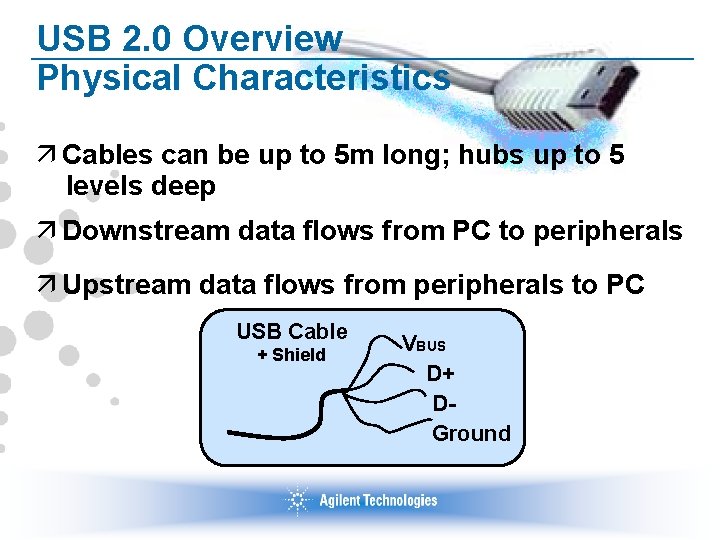

USB 2. 0 Overview Physical Characteristics ä Cables can be up to 5 m long; hubs up to 5 levels deep ä Downstream data flows from PC to peripherals ä Upstream data flows from peripherals to PC USB Cable + Shield VBUS D+ DGround

USB 2. 0 Overview Signal Levels Signal Level Transfer äFull/Low Speed 3. 3 V, 12/1. 5 Mbps äHigh Speed 400 m. V, 480 Mbps Required bandwidth äBW = 0. 35/Tr= ~1 GHz (Tr = ~400 ps)

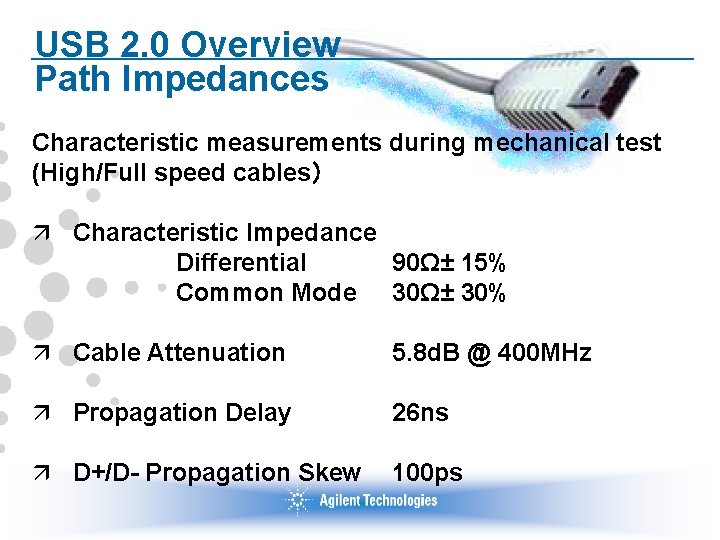

USB 2. 0 Overview Path Impedances Characteristic measurements during mechanical test (High/Full speed cables) ä Characteristic Impedance Differential 90Ω± 15% Common Mode 30Ω± 30% ä Cable Attenuation 5. 8 d. B @ 400 MHz ä Propagation Delay 26 ns ä D+/D- Propagation Skew 100 ps

USB 2. 0 Overview Transmission Modes Full Speed and Low Speed modes are determined by the location of the Rpu resistor (on D+ or D-). The bus starts in full speed mode using the Rpu resistor After Chirp Handshake, if high speed mode is available, the Rpu resistor is disconnected and bus changes to high speed mode.

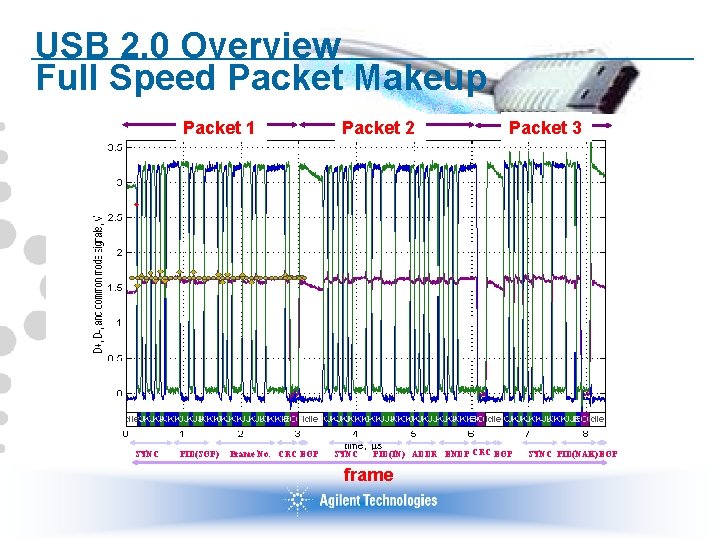

USB 2. 0 Overview Full Speed Packet Makeup Packet 1 SYNC PID(SOF) Frame No. CRC EOP Packet 2 SYNC Packet 3 PID(IN) ADDR ENDP CRC EOP frame SYNC PID(NAK) EOP

USB 2. 0 Overview High Speed Packet Makeup Signal Amplitude 400 m. V SYNC: 32(Minimum 12) bit Idle : SE 0 EOP re-definition: NRZ 01111111 w/o bit stuffing (SOF EOP is 40 bit) SYNC PID(IN) ADDR ENDP CRC EOP

Today’s Schedule ä USB 2. 0 Overview ä USB 2. 0 Compliance Testing ä Examples of Compliance Tests ä Demo of the Agilent Solution ä Conclusion ä Q&A

USB 2. 0 Compliance Testing ä Involves a set of test procedures (available from www. usb. org) performed in a specific order ä The USB 2. 0 HS test procedure (v 1. 0) has been available since December 2001 ä The USB-IF performs the official compliance testing

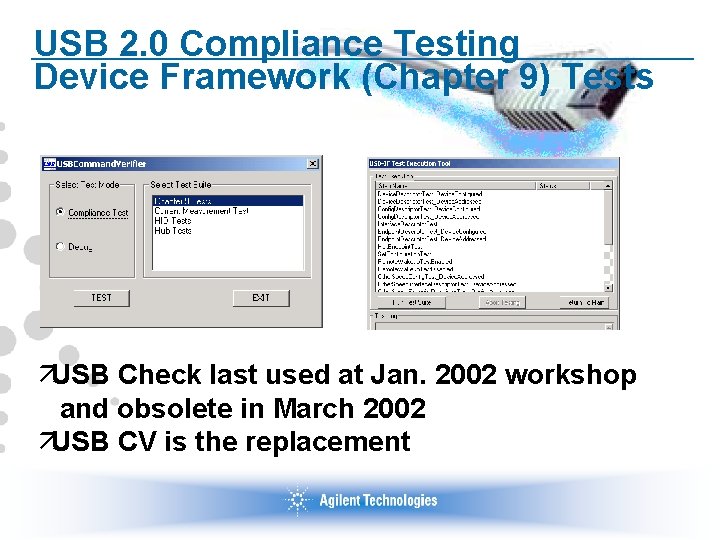

USB 2. 0 Compliance Testing Device Framework (Chapter 9) Tests äUSB Check last used at Jan. 2002 workshop and obsolete in March 2002 äUSB CV is the replacement

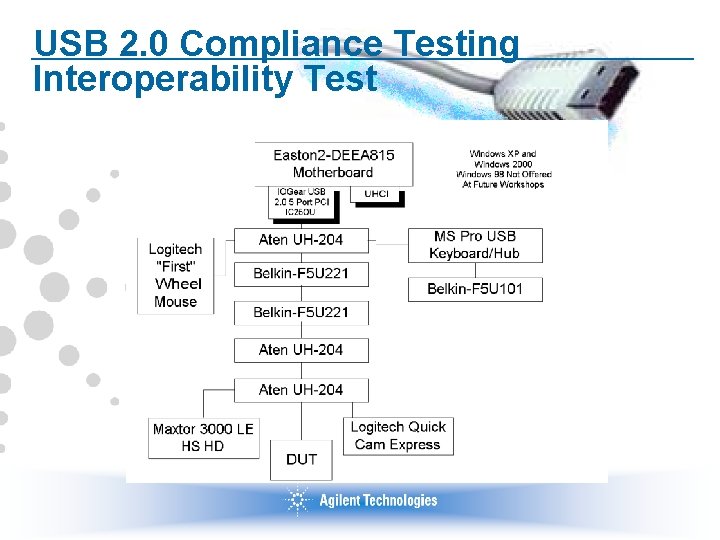

USB 2. 0 Compliance Testing Interoperability Test

USB 2. 0 Compliance Testing Electrical Tests äFull/Low speed signal quality äIn-rush current äDroop/Drop äBackdrive voltage äHigh speed test FS/LS HS

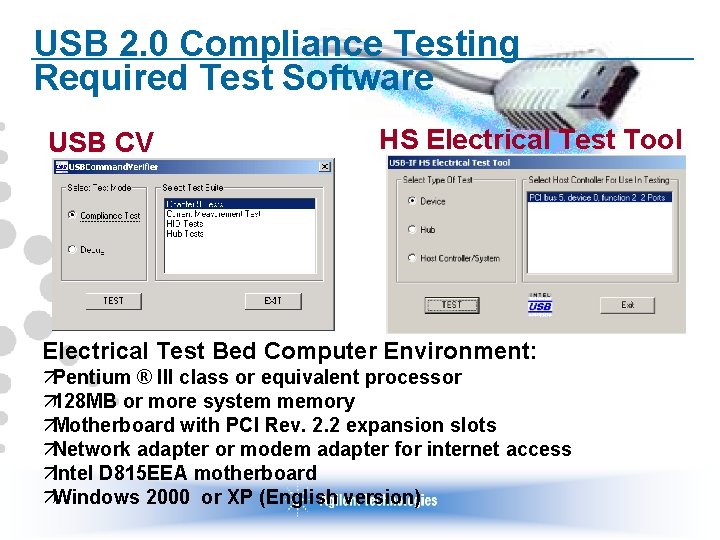

USB 2. 0 Compliance Testing Required Test Software USB CV HS Electrical Test Tool Electrical Test Bed Computer Environment: äPentium ® III class or equivalent processor ä 128 MB or more system memory äMotherboard with PCI Rev. 2. 2 expansion slots äNetwork adapter or modem adapter for internet access äIntel D 815 EEA motherboard äWindows 2000 or XP (English version)

USB 2. 0 Compliance Testing Full/Low Speed Tests äSignal quality äIn-rush current äDroop/Drop äBackdrive voltage

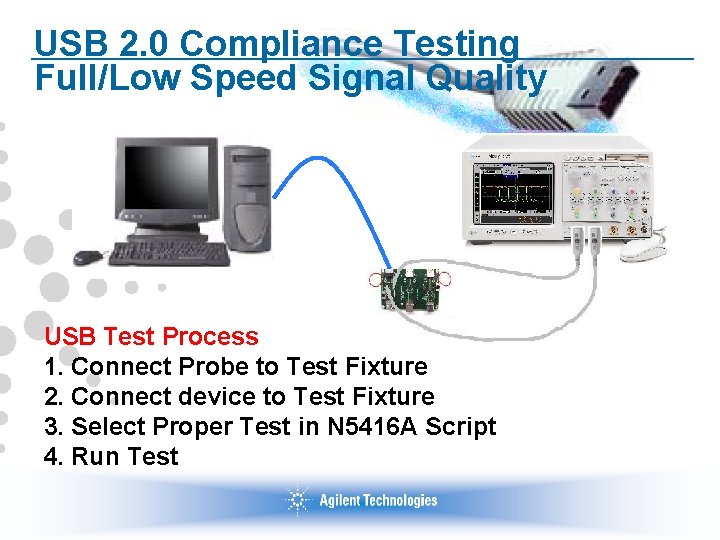

USB 2. 0 Compliance Testing Full/Low Speed Signal Quality USB Test Process 1. Connect Probe to Test Fixture 2. Connect device to Test Fixture 3. Select Proper Test in N 5416 A Script 4. Run Test

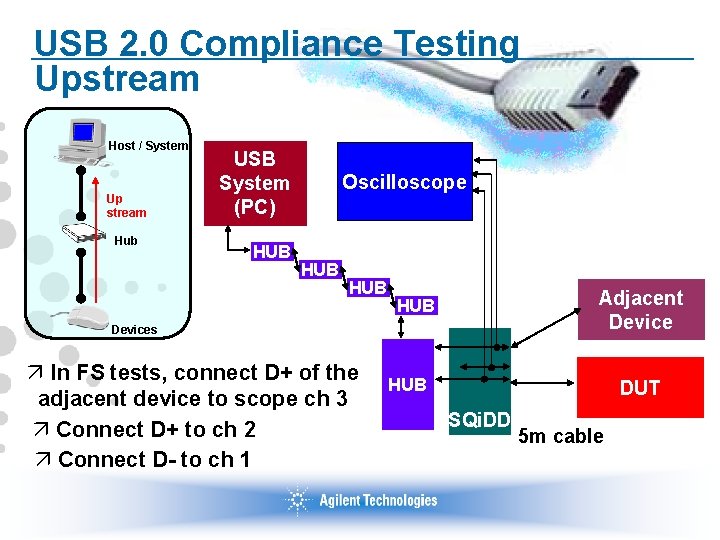

USB 2. 0 Compliance Testing Upstream Host / System Up stream Hub USB System (PC) HUB Oscilloscope HUB Adjacent Device HUB Devices ä In FS tests, connect D+ of the adjacent device to scope ch 3 ä Connect D+ to ch 2 ä Connect D- to ch 1 HUB DUT SQi. DD 5 m cable

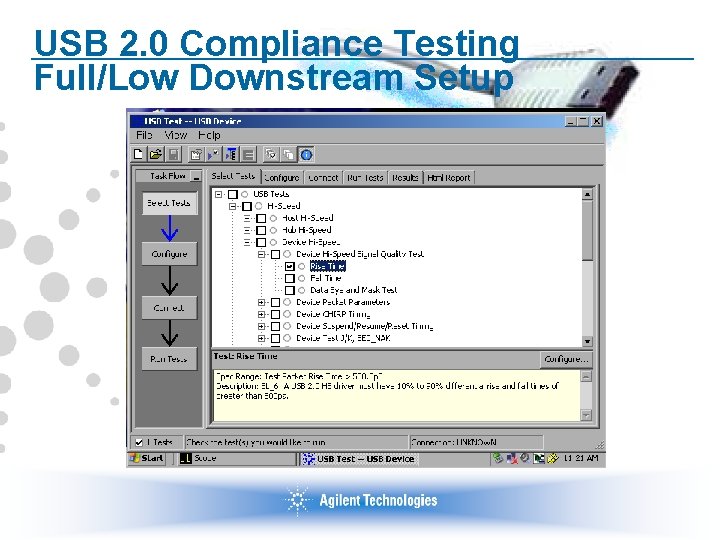

USB 2. 0 Compliance Testing Full/Low Downstream Setup

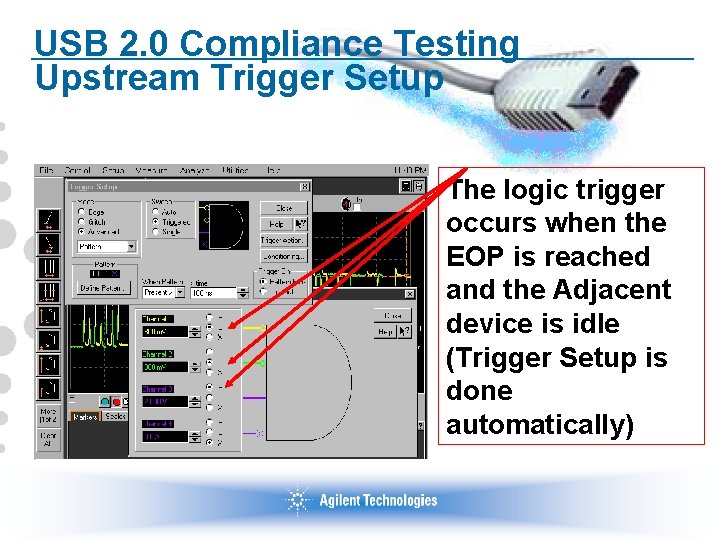

USB 2. 0 Compliance Testing Upstream Trigger Setup The logic trigger occurs when the EOP is reached and the Adjacent device is idle (Trigger Setup is done automatically)

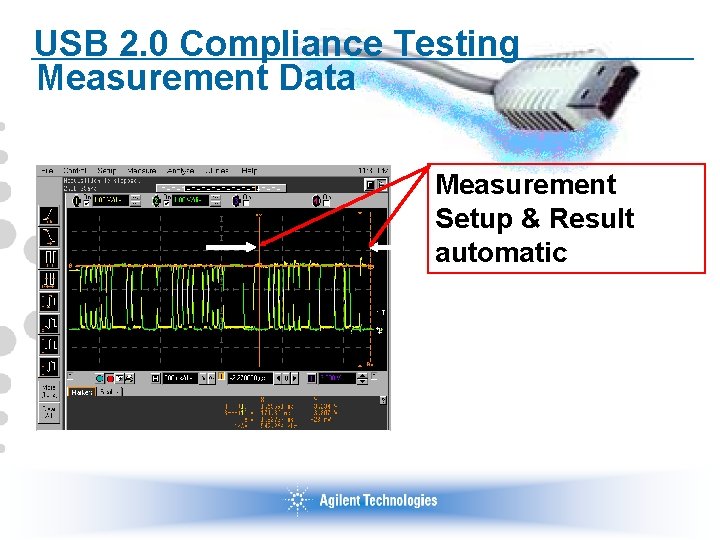

USB 2. 0 Compliance Testing Measurement Data Measurement Setup & Result automatic

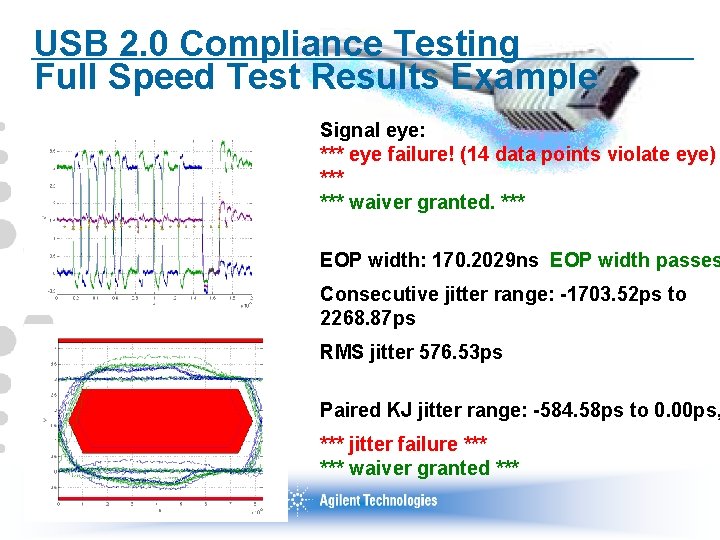

USB 2. 0 Compliance Testing Full Speed Test Results Example Signal eye: *** eye failure! (14 data points violate eye) *** waiver granted. *** EOP width: 170. 2029 ns EOP width passes Consecutive jitter range: -1703. 52 ps to 2268. 87 ps RMS jitter 576. 53 ps Paired KJ jitter range: -584. 58 ps to 0. 00 ps, *** jitter failure *** waiver granted ***

USB 2. 0 Compliance Testing Understanding Full Speed Test Results Measurement Items: D+ Dcommon mode voltage crossover location eye diagram ref. eye violation green blue purple yellow diamond yellow circle red dots

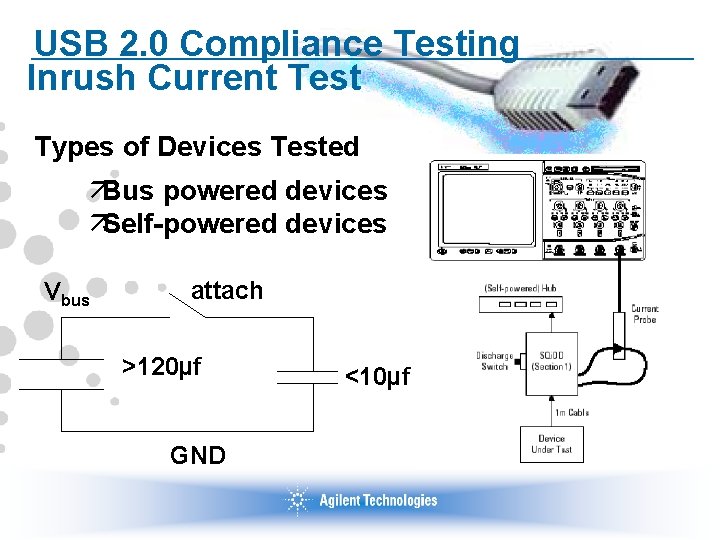

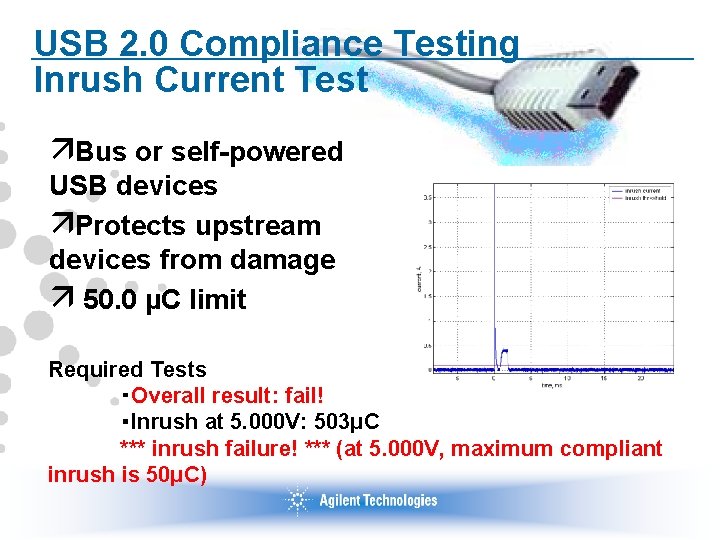

USB 2. 0 Compliance Testing Inrush Current Test Types of Devices Tested äBus powered devices äSelf-powered devices Vbus attach >120µf GND <10µf

USB 2. 0 Compliance Testing Inrush Current Test äBus or self-powered USB devices äProtects upstream devices from damage ä 50. 0 µC limit Required Tests ・Overall result: fail! ・Inrush at 5. 000 V: 503μC *** inrush failure! *** (at 5. 000 V, maximum compliant inrush is 50μC)

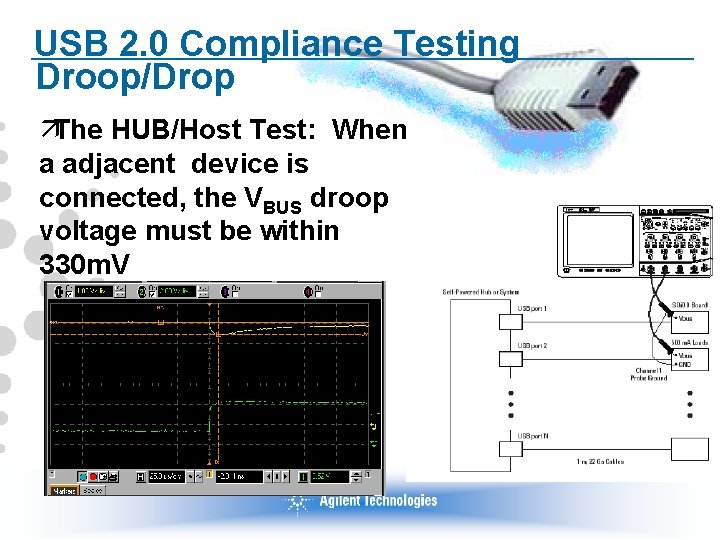

USB 2. 0 Compliance Testing Droop/Drop äThe HUB/Host Test: When a adjacent device is connected, the VBUS droop voltage must be within 330 m. V

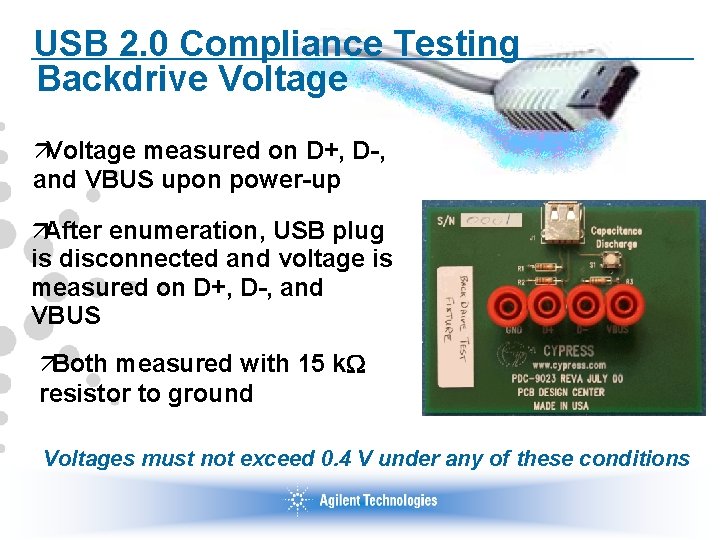

USB 2. 0 Compliance Testing Backdrive Voltage äVoltage measured on D+, D-, and VBUS upon power-up äAfter enumeration, USB plug is disconnected and voltage is measured on D+, D-, and VBUS äBoth measured with 15 k resistor to ground Voltages must not exceed 0. 4 V under any of these conditions

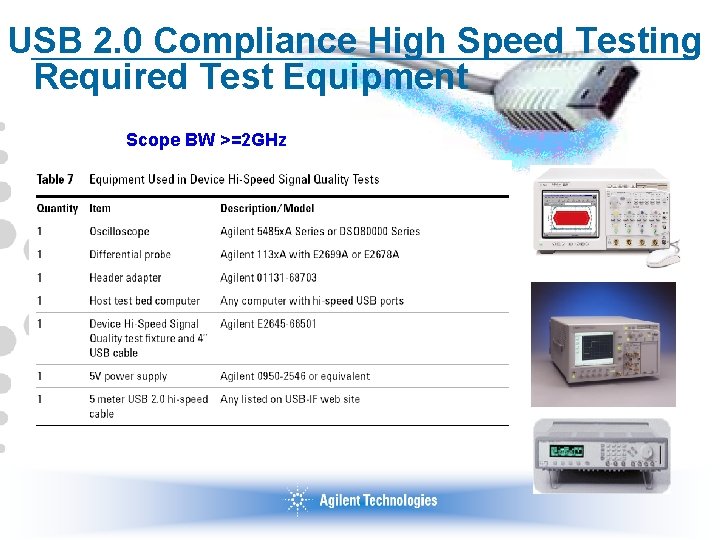

USB 2. 0 Compliance High Speed Testing Required Test Equipment Scope BW >=2 GHz

USB 2. 0 Compliance Testing High Speed Test äHigh Speed Signal Quality äTime Domain Reflectometry( TDR ) äReciever Sensitivity and Squelch äJ and K Voltage äCHIRP äPacket Parameters äSuspend/Resume

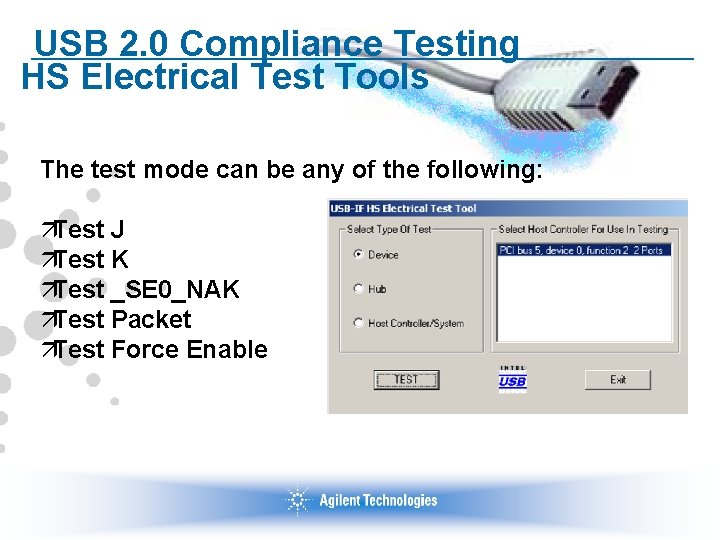

USB 2. 0 Compliance Testing HS Electrical Test Tools The test mode can be any of the following: äTest J äTest K äTest _SE 0_NAK äTest Packet äTest Force Enable

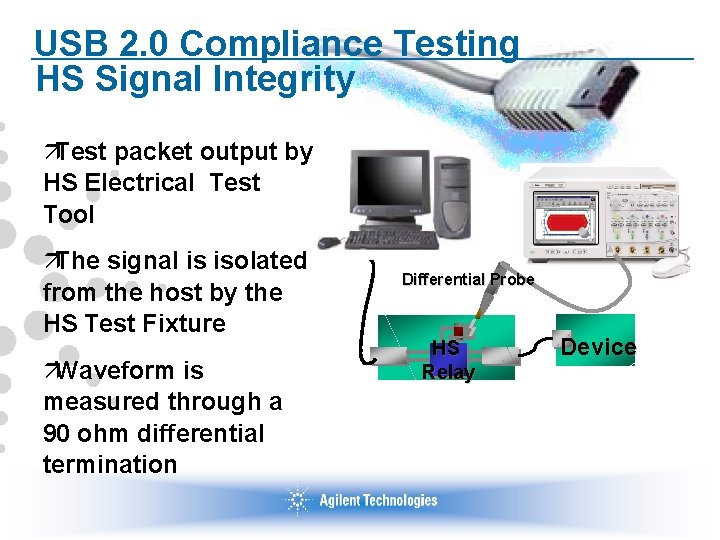

USB 2. 0 Compliance Testing HS Signal Integrity äTest packet output by HS Electrical Test Tool äThe signal is isolated from the host by the HS Test Fixture äWaveform is measured through a 90 ohm differential termination Differential Probe 90 HS Relay Device

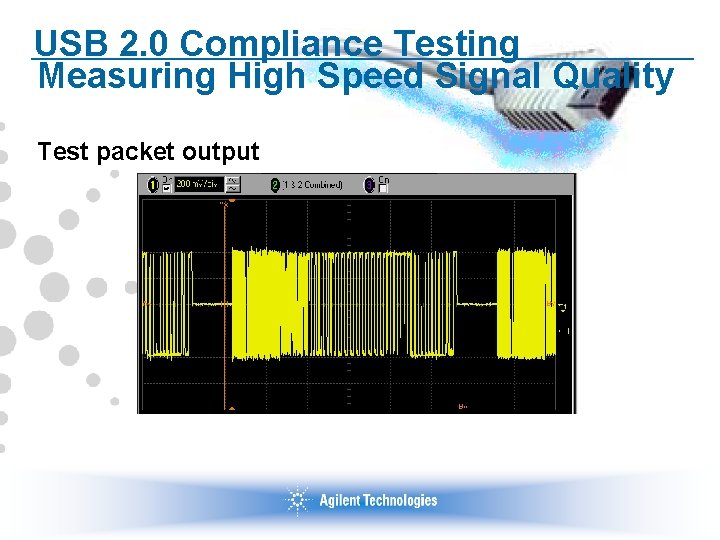

USB 2. 0 Compliance Testing Measuring High Speed Signal Quality Test packet output

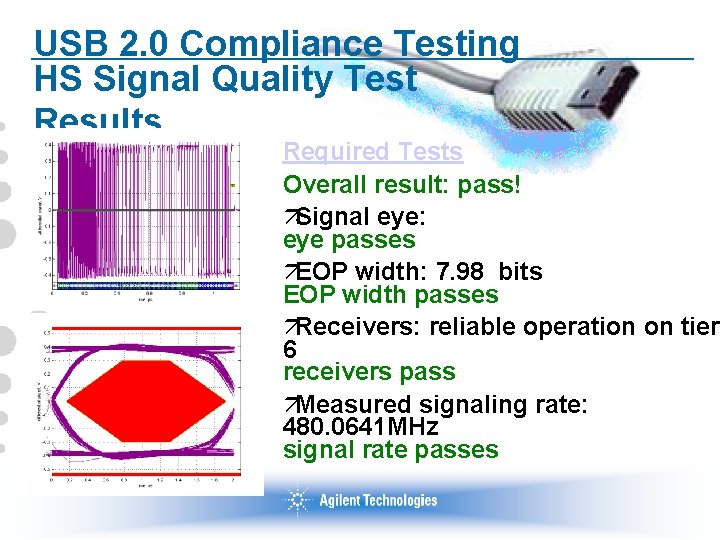

USB 2. 0 Compliance Testing HS Signal Quality Test Results Required Tests Overall result: pass! äSignal eye: eye passes äEOP width: 7. 98 bits EOP width passes äReceivers: reliable operation on tier 6 receivers pass äMeasured signaling rate: 480. 0641 MHz signal rate passes

USB 2. 0 Compliance Testing Device HS Signal Quality äEL_2 Data rate specification (480 Mb/s± 0. 05%) äEL_4 TP 3 eye pattern requirement äEL_5 TP 2 eye pattern requirement (device with captive cable) äEL_6 10 -90% differential rise/fall times (longer than 500 ps) äEL_7 Monotonic data transitions for high speed drivers in the eye pattern template

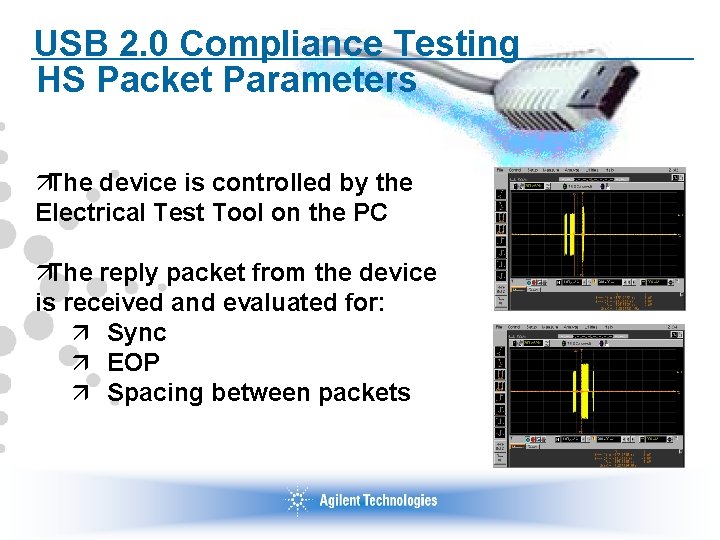

USB 2. 0 Compliance Testing HS Packet Parameters äThe device is controlled by the Electrical Test Tool on the PC äThe reply packet from the device is received and evaluated for: ä Sync ä EOP ä Spacing between packets

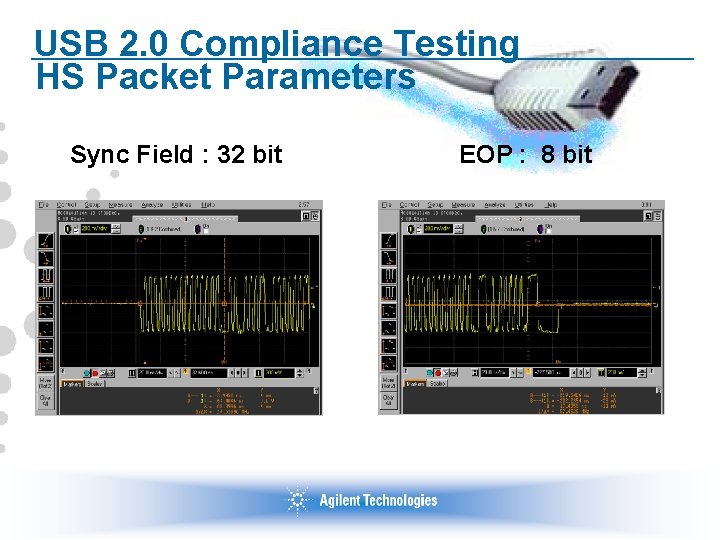

USB 2. 0 Compliance Testing HS Packet Parameters Sync Field : 32 bit EOP : 8 bit

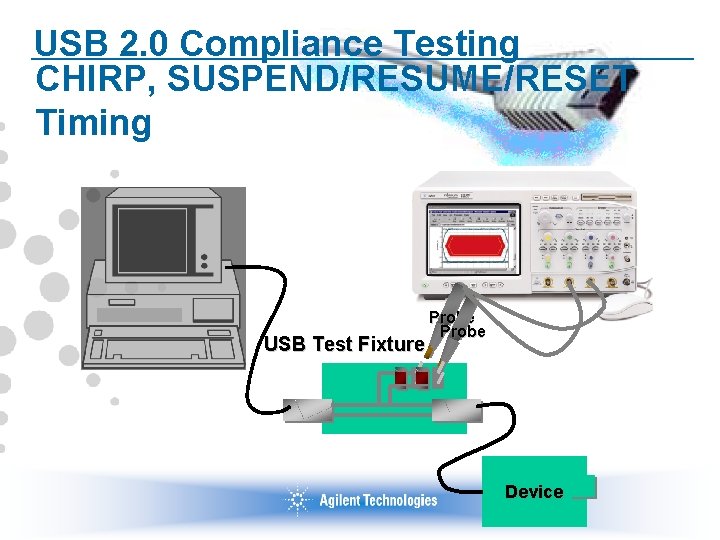

USB 2. 0 Compliance Testing CHIRP, SUSPEND/RESUME/RESET Timing USB Test Fixture Probe 90 Device

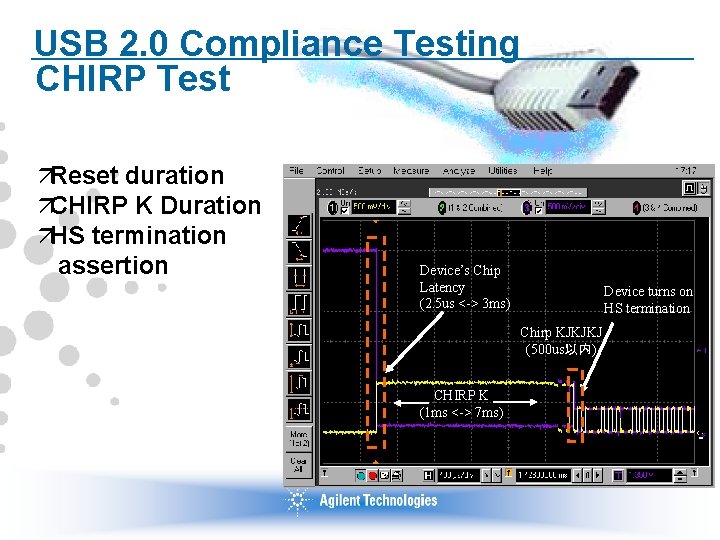

USB 2. 0 Compliance Testing CHIRP Test äReset duration äCHIRP K Duration äHS termination assertion Device’s Chip Latency (2. 5 us <-> 3 ms) Device turns on HS termination Chirp KJKJKJ (500 us以内) CHIRP K (1 ms <-> 7 ms)

USB 2. 0 Compliance Testing CHIRP Test Device’s Chip Latency (2. 5 us <-> 3 ms) Enable High Speed Termination After Chirp KJKJKJ (within 500 us)

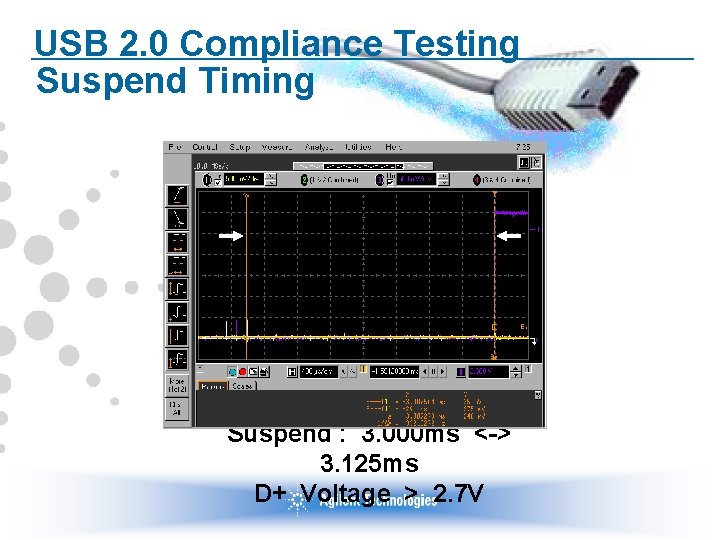

USB 2. 0 Compliance Testing Suspend Timing Suspend : 3. 000 ms <-> 3. 125 ms D+ Voltage > 2. 7 V

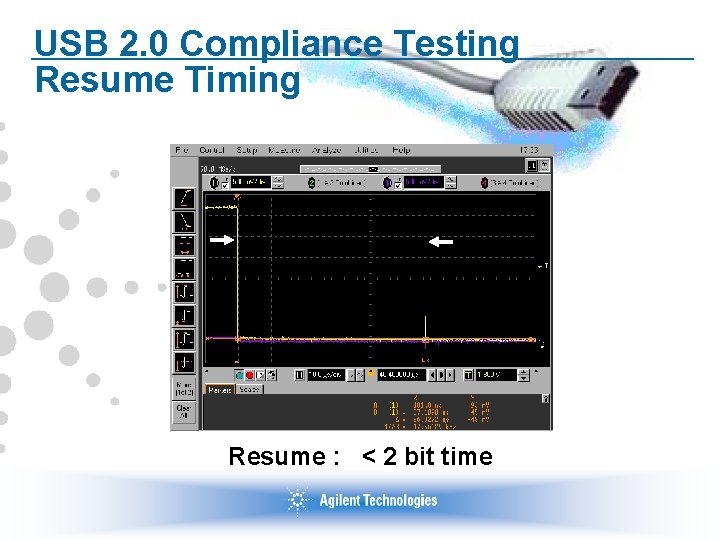

USB 2. 0 Compliance Testing Resume Timing Resume : < 2 bit time

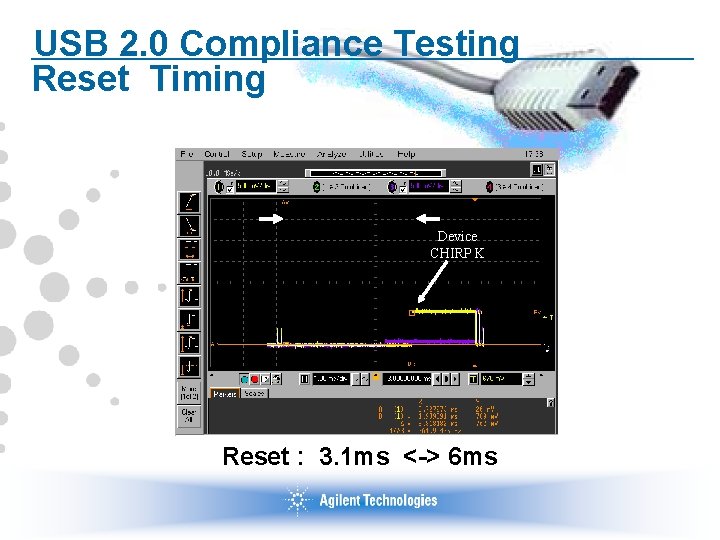

USB 2. 0 Compliance Testing Reset Timing Device CHIRP K Reset : 3. 1 ms <-> 6 ms

USB 2. 0 Compliance Testing Reset Timing Reset from Suspend : 2. 5 us <-> 3. 000 ms

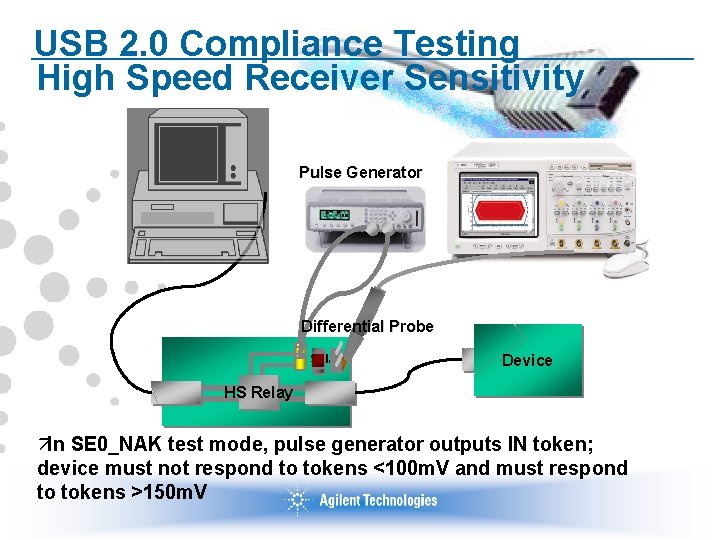

USB 2. 0 Compliance Testing High Speed Receiver Sensitivity Pulse Generator Differential Probe SMA Device HS Relay äIn SE 0_NAK test mode, pulse generator outputs IN token; device must not respond to tokens <100 m. V and must respond to tokens >150 m. V

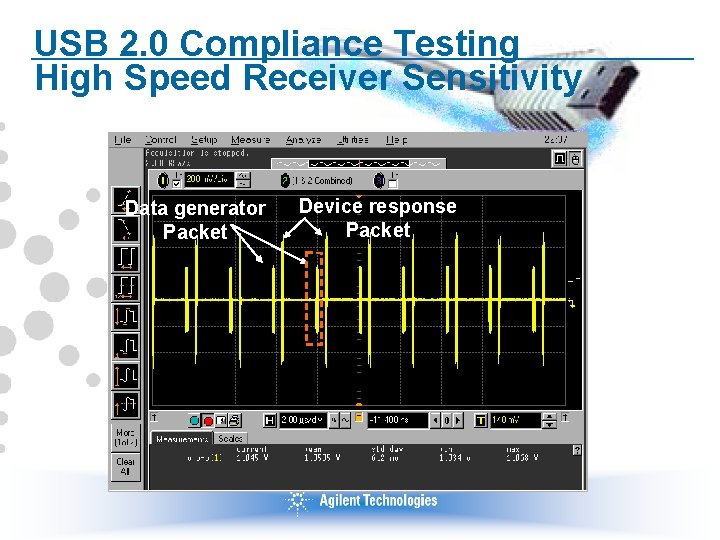

USB 2. 0 Compliance Testing High Speed Receiver Sensitivity Data generator Packet Device response Packet

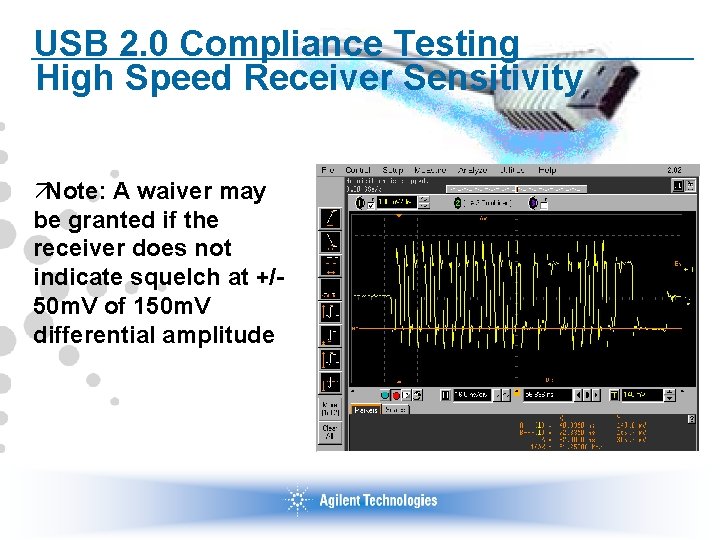

USB 2. 0 Compliance Testing High Speed Receiver Sensitivity äNote: A waiver may be granted if the receiver does not indicate squelch at +/50 m. V of 150 m. V differential amplitude

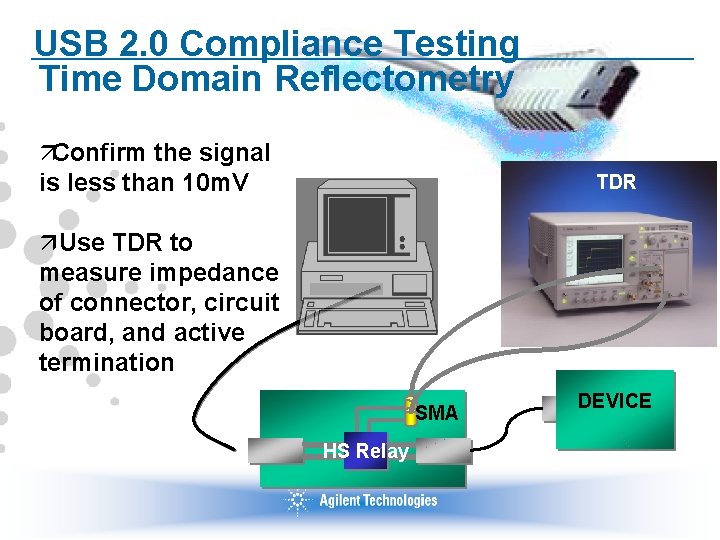

USB 2. 0 Compliance Testing Time Domain Reflectometry äConfirm the signal is less than 10 m. V TDR äUse TDR to measure impedance of connector, circuit board, and active termination SMA HS Relay DEVICE

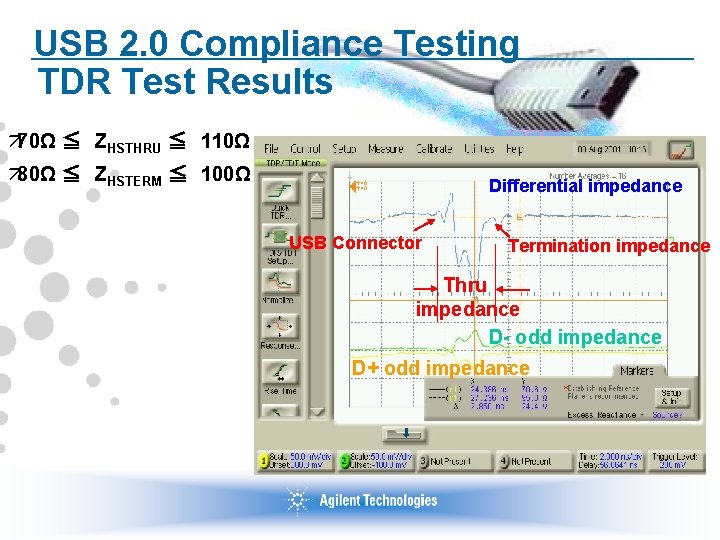

USB 2. 0 Compliance Testing TDR Test Results ä 70Ω ≦ ZHSTHRU ≦ 110Ω ä 80Ω ≦ ZHSTERM ≦ 100Ω Differential impedance USB Connector Termination impedance Thru impedance D- odd impedance D+ odd impedance

Today’s Schedule ä USB 2. 0 Overview ä USB 2. 0 Compliance Testing ä Examples of Compliance Tests ä Demo of the Agilent Solution ä Conclusion ä Q&A

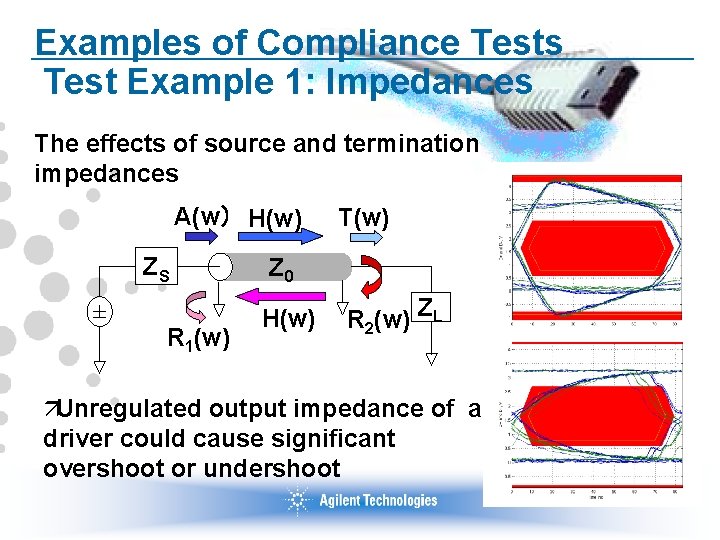

Examples of Compliance Tests Test Example 1: Impedances The effects of source and termination impedances A(w) H(w) ZS ± R 1(w) T(w) Z 0 H(w) R 2(w) ZL äUnregulated output impedance of a driver could cause significant overshoot or undershoot

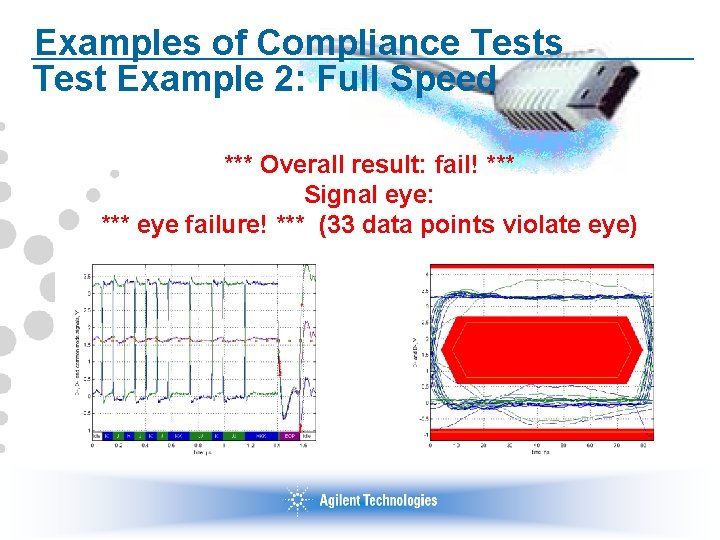

Examples of Compliance Tests Test Example 2: Full Speed *** Overall result: fail! *** Signal eye: *** eye failure! *** (33 data points violate eye)

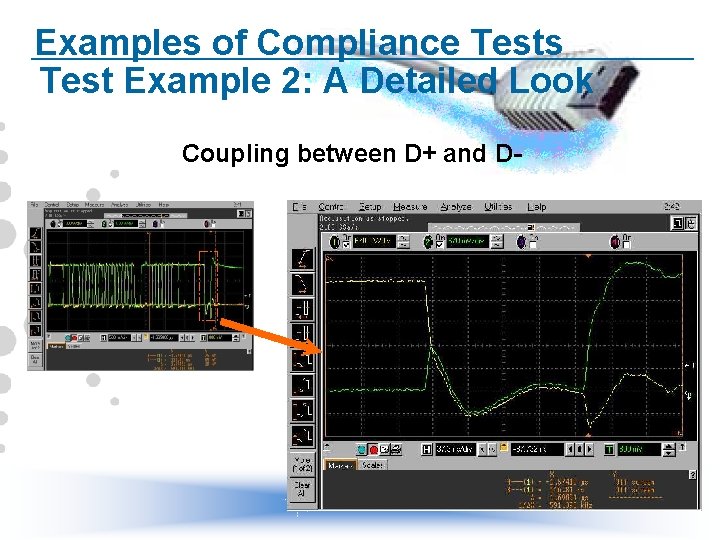

Examples of Compliance Tests Test Example 2: A Detailed Look Coupling between D+ and D-

Examples of Compliance Tests Cautions with USB 2. 0 Measurements äHub quality can affect full/low speed upstream measurements For identical measurements to those in compliance tests, use Intel’s CHUB äFor high speed signal quality measurements, take care in handling low level signals. Be careful of: ①Adjusting the offset and performing calibration ②Effects of fixturing impedance on signal quality ③The bandwidth of the probe

Today’s Schedule ä USB 2. 0 Overview ä USB 2. 0 Compliance Testing ä Examples of Compliance Tests ä Demo of the Agilent Solution ä Conclusion ä Q&A

Today’s Schedule ä USB 2. 0 Overview ä USB 2. 0 Compliance Testing ä Examples of Compliance Tests ä Demo of the Agilent Solution ä Conclusion ä Q&A

Conclusion Summary äCompliance testing is a requirement äCompliance testing involves framework layer evaluation and physical layer evaluation äIn physical layer evaluation, signal quality is influenced by components, circuit layout, and driver circuitry äAn easy-to-use oscilloscope is an important factor in efficiently performing compliance testing

Conclusion Reference Material äUniversal Serial Bus Specification Rev 2. 0 (USB-IF) äUSB-IF Signal Integrity Test Description (USB-IF) äUSB Design by Example (John Hyde, John Wiley & Sons INC) äUniversal Serial Bus System Architecture (Don Anderson, MINDSHARE INC) äUSB 2. 0 High Speed Electrical Test Procedure v 1. 0

Today’s Schedule ä USB 2. 0 Overview ä USB 2. 0 Compliance Testing ä Examples of Compliance Tests ä Demo of the Agilent Solution ä Conclusion ä Q&A

- Slides: 59