Advances in Memory Technology Changhyun Kim Samsung Electronics

- Slides: 27

Advances in Memory Technology Changhyun Kim Samsung Electronics Co. , Ltd. chang. kim@samsung. com C. Kim, 2006 VLDB Conf.

Contents I. Introduction A. Semiconductor Industry Trend B. State-of-the-Art Memory I. II. Memory Technology Trend III. Future Possible Memory Solutions IV. Conclusions C. Kim, 2006 VLDB Conf.

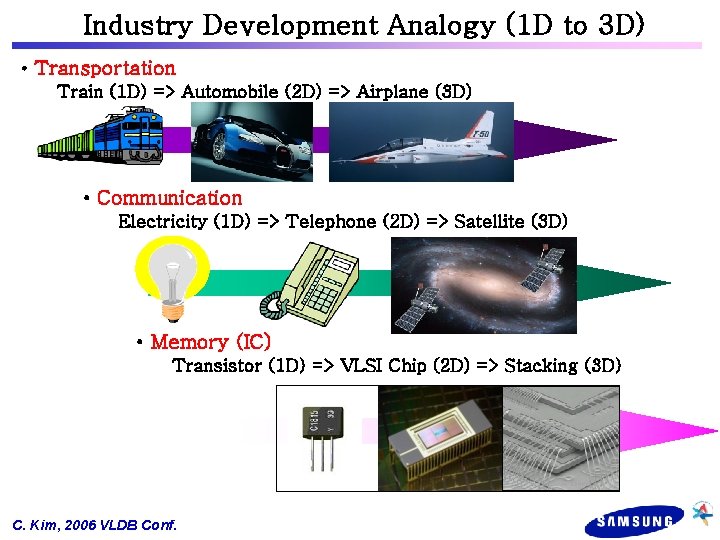

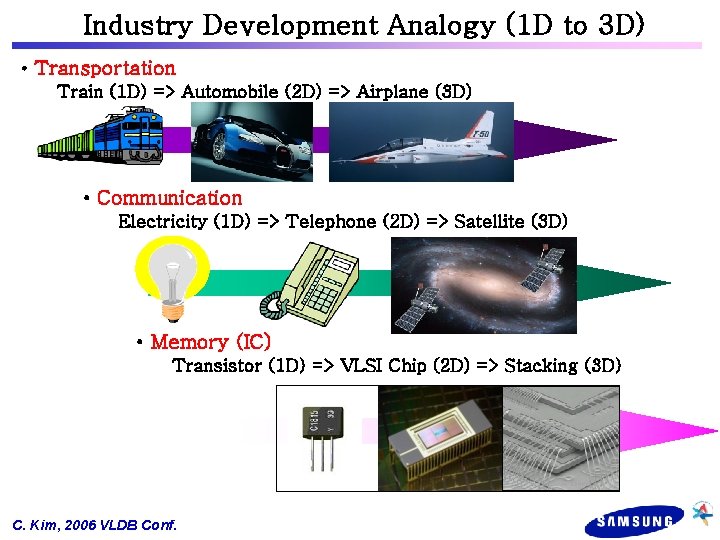

Industry Development Analogy (1 D to 3 D) • Transportation Train (1 D) => Automobile (2 D) => Airplane (3 D) • Communication Electricity (1 D) => Telephone (2 D) => Satellite (3 D) • Memory (IC) Transistor (1 D) => VLSI Chip (2 D) => Stacking (3 D) C. Kim, 2006 VLDB Conf.

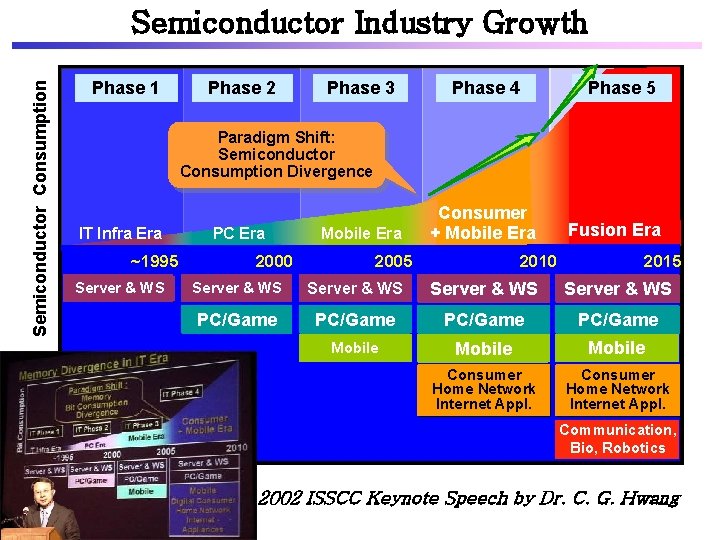

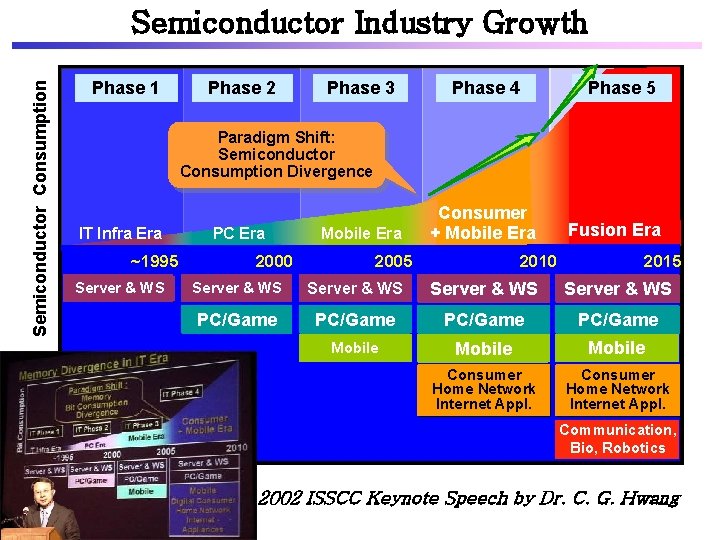

Semiconductor Consumption Semiconductor Industry Growth Phase 1 Phase 2 Phase 3 Phase 4 Phase 5 Paradigm Shift: Semiconductor Consumption Divergence IT Infra Era ~1995 Server & WS PC Era 2000 Mobile Era Consumer + Mobile Era 2005 2010 Fusion Era 2015 Server & WS PC/Game Mobile Consumer Home Network Internet Appl. Communication, Bio, Robotics 2002 ISSCC Keynote Speech by Dr. C. G. Hwang C. Kim, 2006 VLDB Conf.

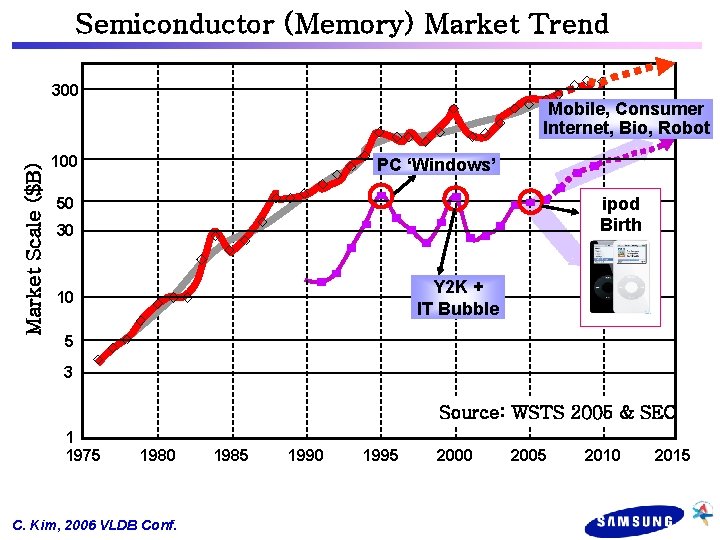

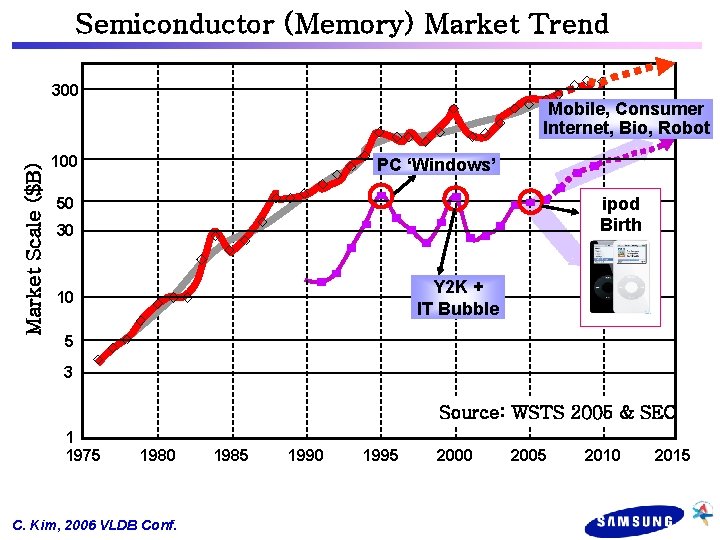

Semiconductor (Memory) Market Trend Market Scale ($B) 300 Mobile, Consumer Internet, Bio, Robot 100 PC ‘Windows’ ipod Birth 50 30 Y 2 K + IT Bubble 10 5 3 Source: WSTS 2005 & SEC 1 1975 1980 C. Kim, 2006 VLDB Conf. 1985 1990 1995 2000 2005 2010 2015

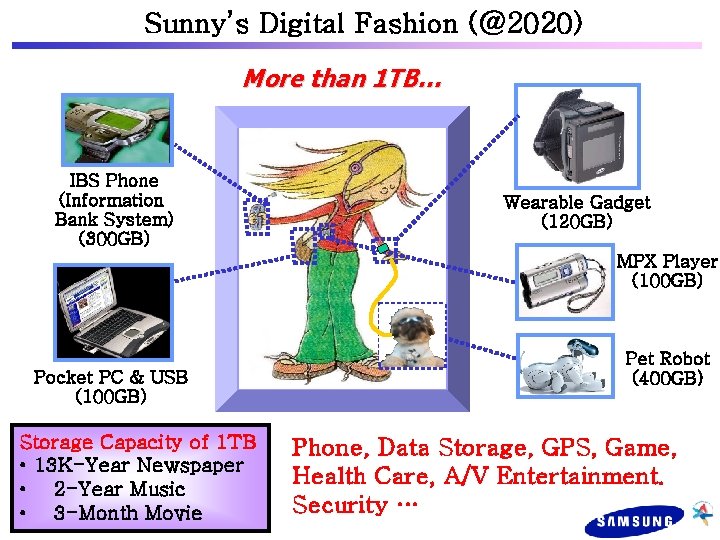

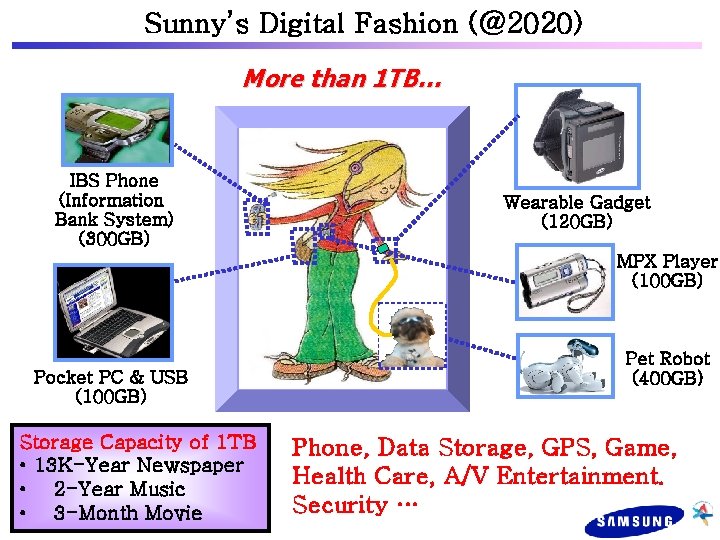

Sunny’s Digital Fashion (@2020) More than 1 TB… IBS Phone (Information Bank System) (300 GB) Wearable Gadget (120 GB) MPX Player (100 GB) Pocket PC & USB (100 GB) Storage Capacity of 1 TB • 13 K-Year Newspaper • 2 -Year Music • 3 -Month Movie C. Kim, 2006 VLDB Conf. Pet Robot (400 GB) Phone, Data Storage, GPS, Game, Health Care, A/V Entertainment. Security …

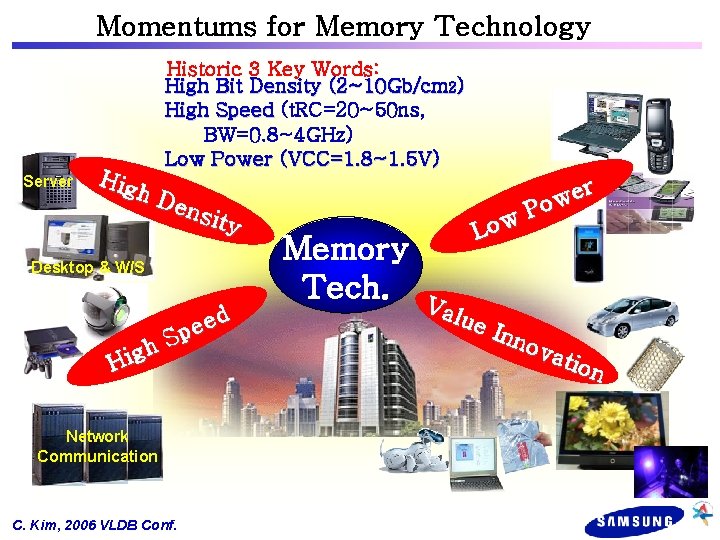

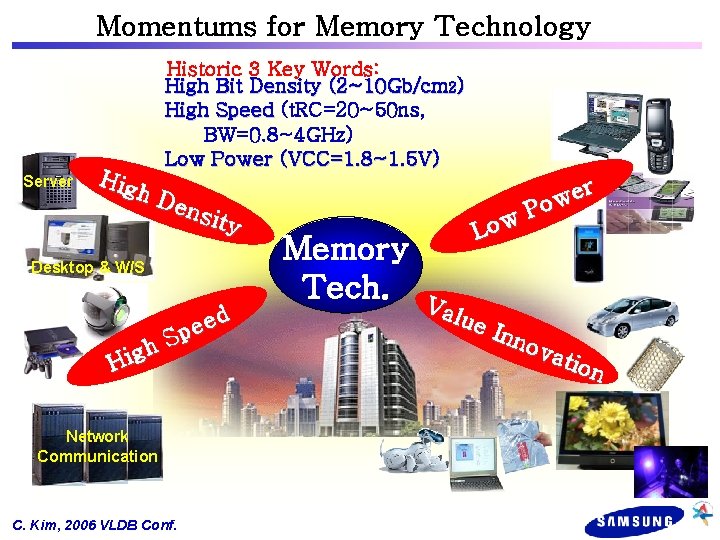

Momentums for Memory Technology Historic 3 Key Words: High Bit Density (2~10 Gb/cm 2) High Speed (t. RC=20~50 ns, BW=0. 8~4 GHz) Low Power (VCC=1. 8~1. 5 V) Server Hig h. D ens ity Desktop & W/S h g i H d e e Sp Network Communication C. Kim, 2006 VLDB Conf. Memory Tech. er w o P Low Val ue Inn ova tion

I. State-of-the-Art Memory • High Density • High Speed • Low Voltage C. Kim, 2006 VLDB Conf.

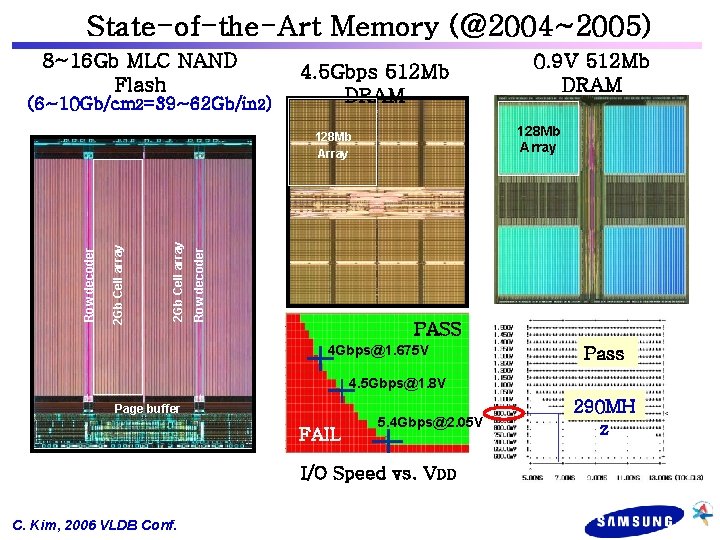

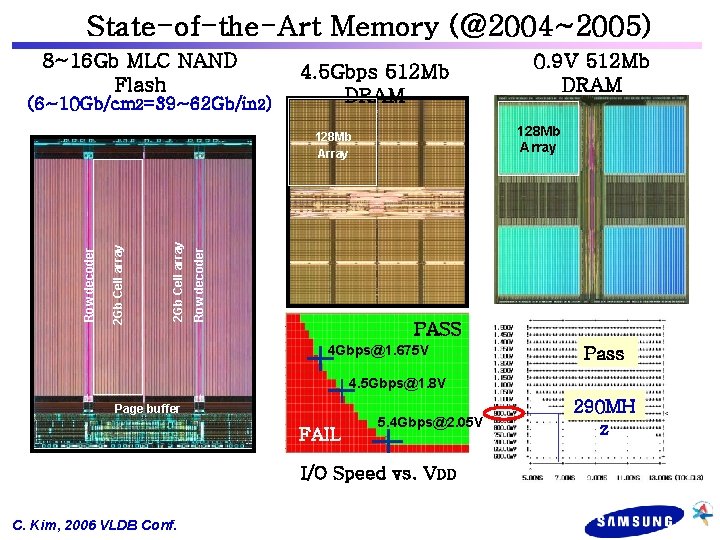

State-of-the-Art Memory (@2004~2005) 8~16 Gb MLC NAND Flash (6~10 Gb/cm 2=39~62 Gb/in 2) 4. 5 Gbps 512 Mb DRAM 128 Mb Array Row decoder 2 Gb Cell array 128 Mb Array Row decoder 0. 9 V 512 Mb DRAM PASS 4 Gbps@1. 675 V Pass 4. 5 Gbps@1. 8 V Page buffer FAIL 5. 4 Gbps@2. 05 V I/O Speed vs. VDD C. Kim, 2006 VLDB Conf. 290 MH z

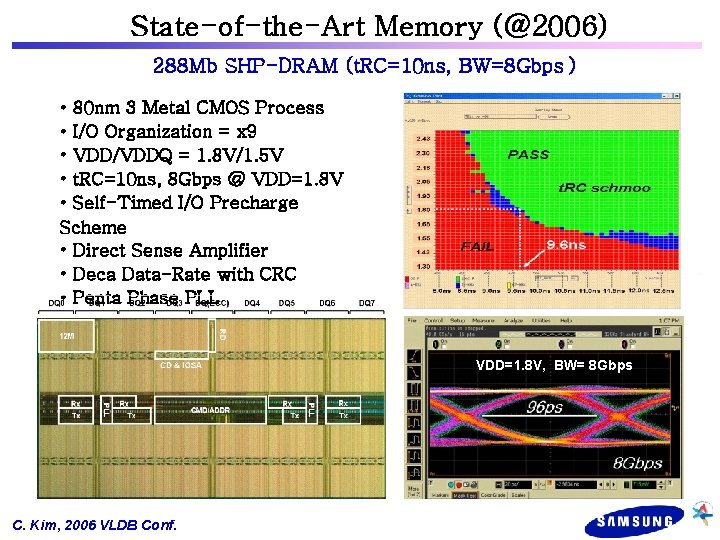

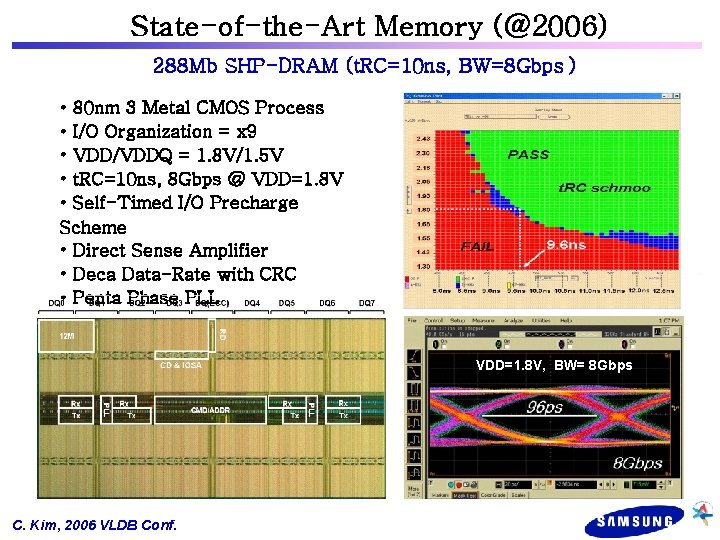

State-of-the-Art Memory (@2006) 288 Mb SHP-DRAM (t. RC=10 ns, BW=8 Gbps ) • 80 nm 3 Metal CMOS Process • I/O Organization = x 9 • VDD/VDDQ = 1. 8 V/1. 5 V • t. RC=10 ns, 8 Gbps @ VDD=1. 8 V • Self-Timed I/O Precharge Scheme • Direct Sense Amplifier • Deca Data-Rate with CRC • Penta Phase PLL VDD=1. 8 V, BW= 8 Gbps C. Kim, 2006 VLDB Conf.

II. Memory Technology Trend C. Kim, 2006 VLDB Conf.

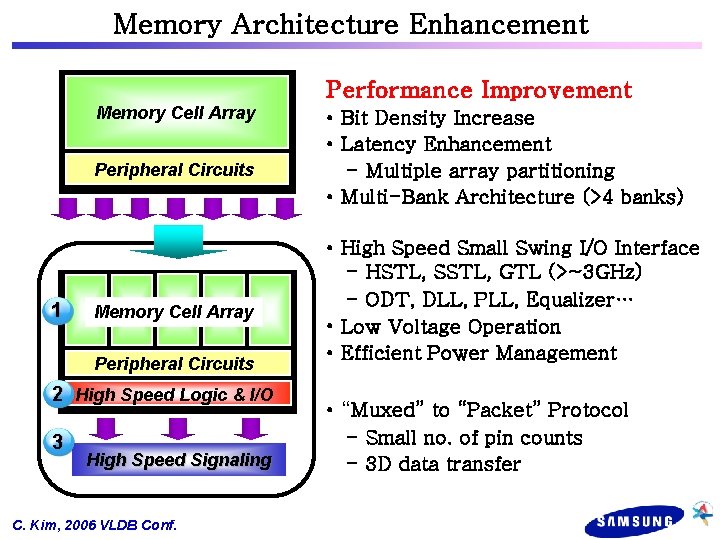

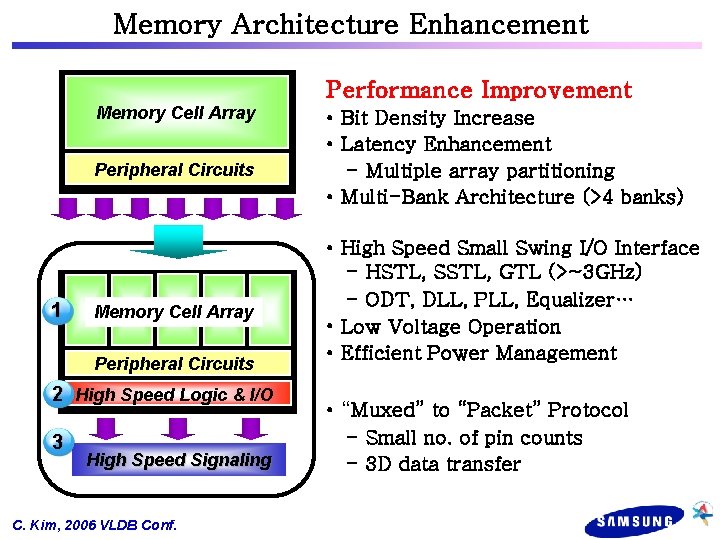

Memory Architecture Enhancement Performance Improvement Memory Cell Array Peripheral Circuits 1 Memory Cell Array Peripheral Circuits 2 High Speed Logic & I/O 3 High Speed Signaling C. Kim, 2006 VLDB Conf. • Bit Density Increase • Latency Enhancement - Multiple array partitioning • Multi-Bank Architecture (>4 banks) • High Speed Small Swing I/O Interface - HSTL, SSTL, GTL (>~3 GHz) - ODT, DLL, PLL, Equalizer… • Low Voltage Operation • Efficient Power Management • “Muxed” to “Packet” Protocol - Small no. of pin counts - 3 D data transfer

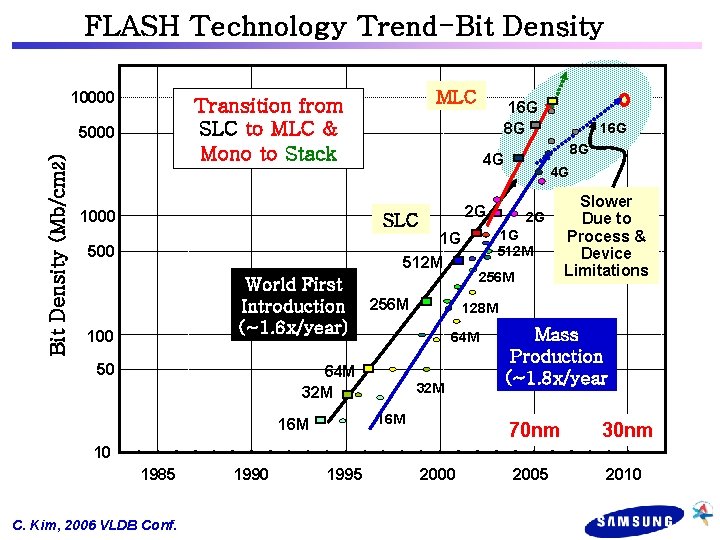

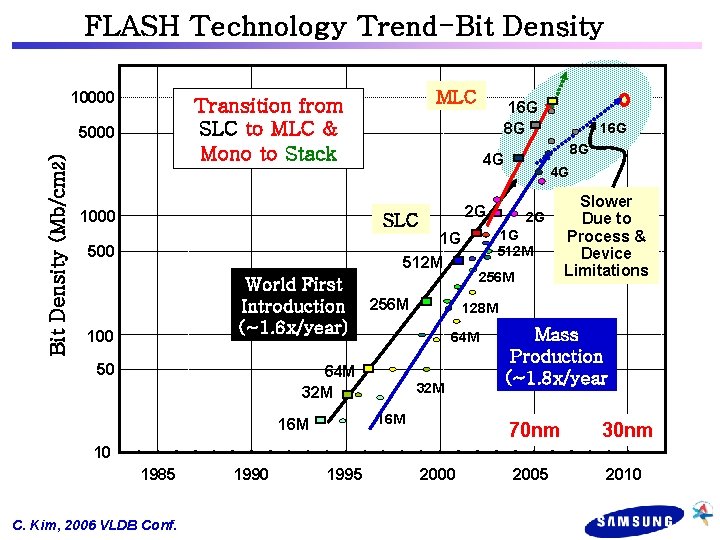

FLASH Technology Trend-Bit Density 10000 5000 Bit Density (Mb/cm 2) MLC Transition from SLC to MLC & Mono to Stack 1000 16 G 8 G 100 50 256 M 32 M 16 M Slower Due to Process & Device Limitations 128 M 64 M 32 M 2 G 1 G 512 M World First Introduction (~1. 6 x/year) 4 G 2 G 1 G 500 8 G 4 G SLC 16 G Mass Production (~1. 8 x/year ) 70 nm 30 nm 2005 2010 10 1985 C. Kim, 2006 VLDB Conf. 1990 1995 2000

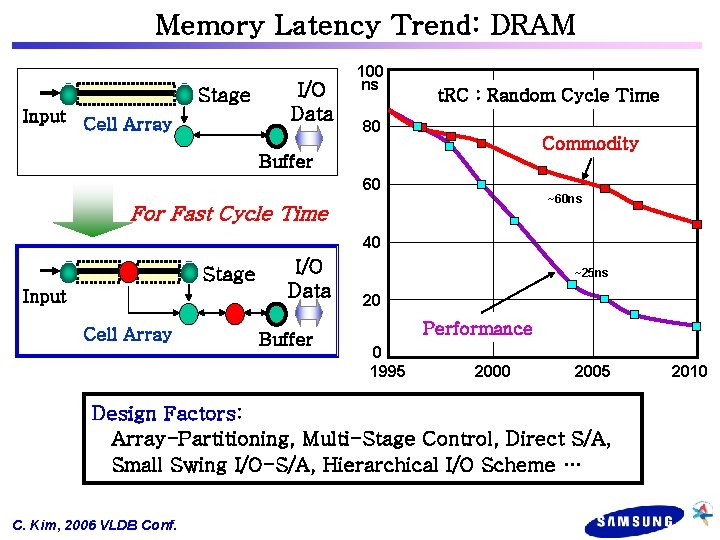

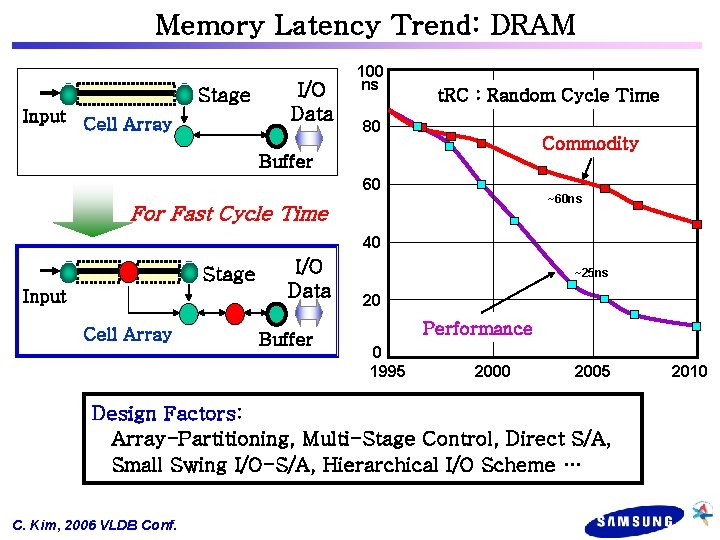

Memory Latency Trend: DRAM Stage Input Cell Array I/O Data 100 ns t. RC : Random Cycle Time 80 Commodity Buffer 60 ~60 ns For Fast Cycle Time 40 Stage Input Cell Array I/O Data Buffer ~25 ns 20 Performance 0 1995 2000 2005 Design Factors: Array-Partitioning, Multi-Stage Control, Direct S/A, Small Swing I/O-S/A, Hierarchical I/O Scheme … C. Kim, 2006 VLDB Conf. 2010

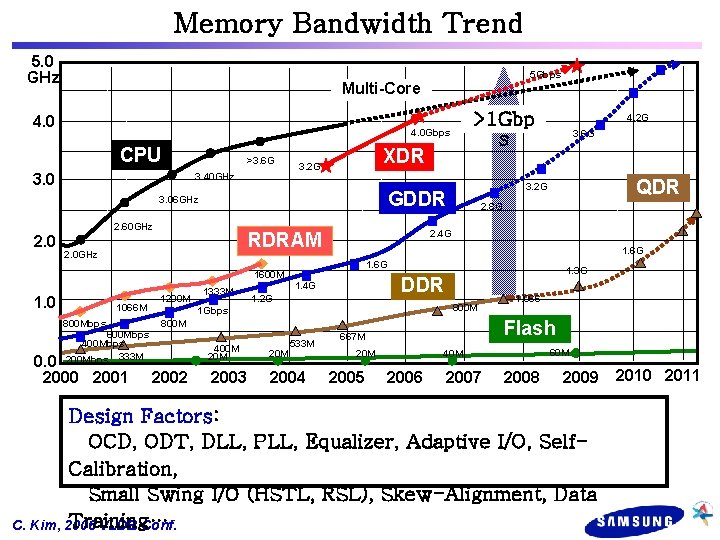

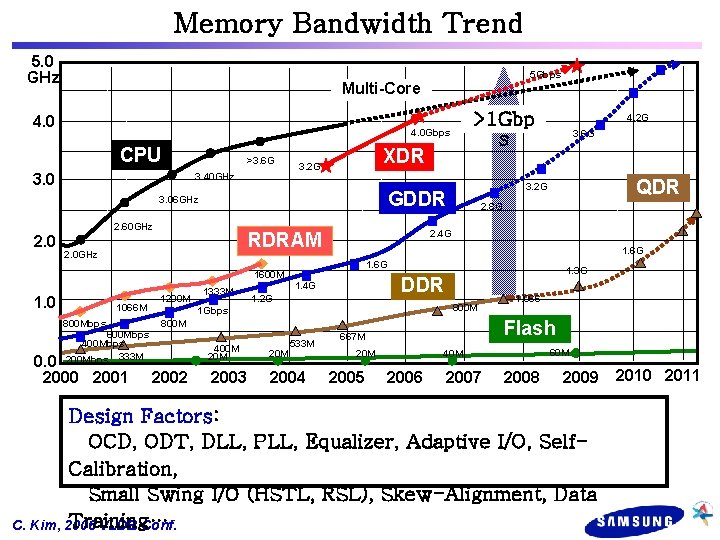

Memory Bandwidth Trend 5. 0 GHz Multi-Core 4. 0 >1 Gbp s 4. 0 Gbps CPU 3. 0 >3. 6 G 3. 40 GHz XDR 3. 2 G 2. 60 GHz 1600 M 1. 0 1066 M 800 Mbps 1200 M 2. 8 G 1. 6 G 1. 3 G DDR 1. 4 G 1. 2 G 800 M 2002 2003 20 M 533 M 2004 667 M 60 M 40 M 2005 1. 066 Flash 800 M 400 M 20 M QDR 1. 6 G 1 Gbps 600 Mbps 400 Mbps 200 Mbps 333 M 0. 0 2001 1333 M 3. 6 G 2. 4 G RDRAM 2. 0 GHz 4. 2 G 3. 2 G GDDR 3. 06 GHz 2. 0 5 Gbps 2006 2007 2008 2009 Design Factors: OCD, ODT, DLL, PLL, Equalizer, Adaptive I/O, Self. Calibration, Small Swing I/O (HSTL, RSL), Skew-Alignment, Data Training… C. Kim, 2006 VLDB Conf. 2010 2011

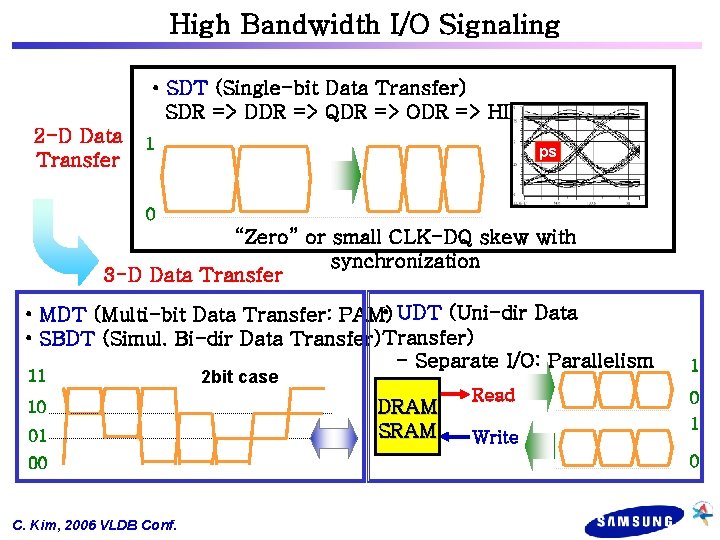

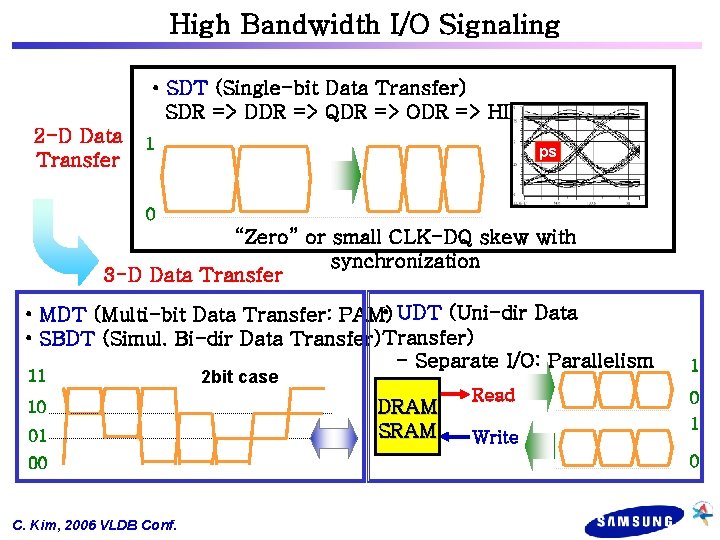

High Bandwidth I/O Signaling • SDT (Single-bit Data Transfer) SDR => DDR => QDR => ODR => HDR 2 -D Data Transfer 1 ps 0 “Zero” or small CLK-DQ skew with synchronization 3 -D Data Transfer • UDT (Uni-dir Data • MDT (Multi-bit Data Transfer: PAM) • SBDT (Simul. Bi-dir Data Transfer) - Separate I/O: Parallelism 11 10 01 00 C. Kim, 2006 VLDB Conf. 2 bit case DRAM SRAM Read Write 1 0

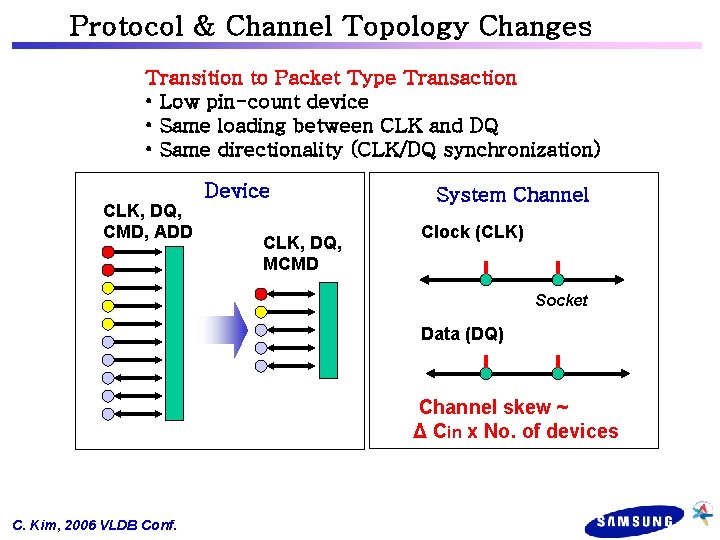

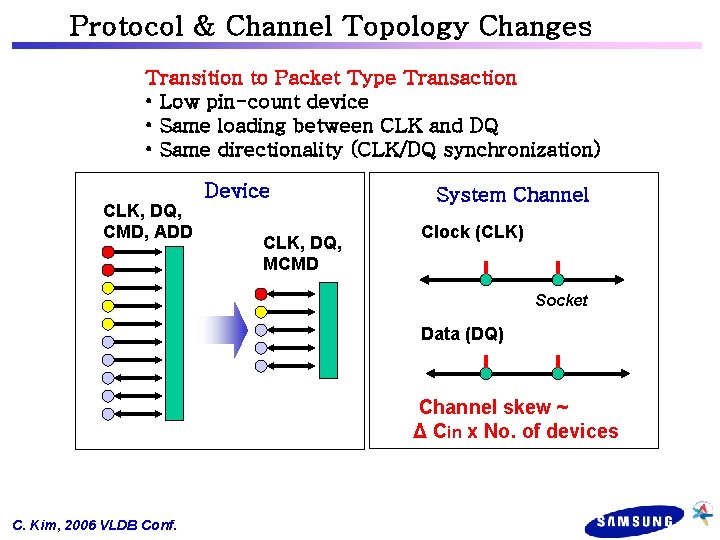

Protocol & Channel Topology Changes Transition to Packet Type Transaction • Low pin-count device • Same loading between CLK and DQ • Same directionality (CLK/DQ synchronization) Device CLK, DQ, CMD, ADD CLK, DQ, MCMD System Channel Clock (CLK) Socket Data (DQ) Channel skew ~ Δ Cin x No. of devices C. Kim, 2006 VLDB Conf.

III. Future Memory Solutions • Industry Trend • Device & Package Aspects • Module & System Aspects C. Kim, 2006 VLDB Conf.

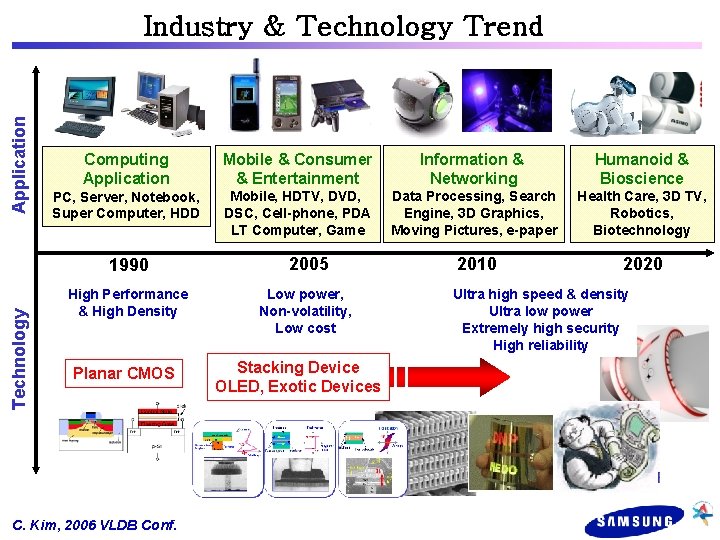

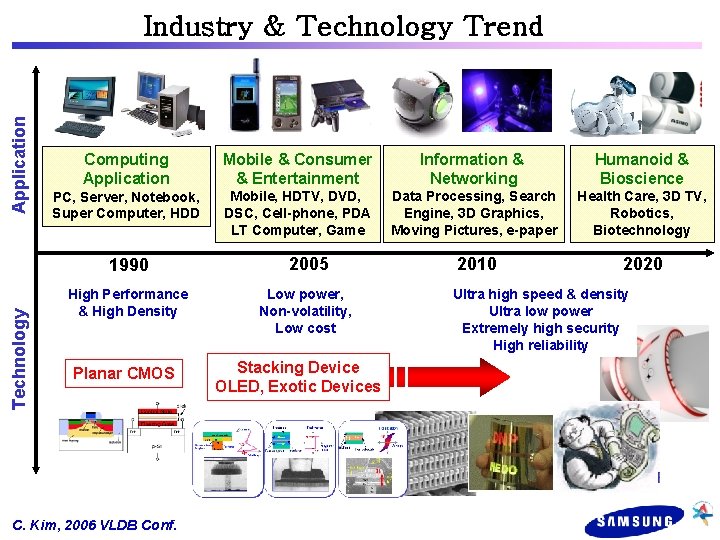

Technology Application Industry & Technology Trend Computing Application Mobile & Consumer & Entertainment Information & Networking Humanoid & Bioscience PC, Server, Notebook, Super Computer, HDD Mobile, HDTV, DVD, DSC, Cell-phone, PDA LT Computer, Game Data Processing, Search Engine, 3 D Graphics, Moving Pictures, e-paper Health Care, 3 D TV, Robotics, Biotechnology 2010 2020 1990 2005 High Performance & High Density Low power, Non-volatility, Low cost Planar CMOS C. Kim, 2006 VLDB Conf. Stacking Device OLED, Exotic Devices Ultra high speed & density Ultra low power Extremely high security High reliability

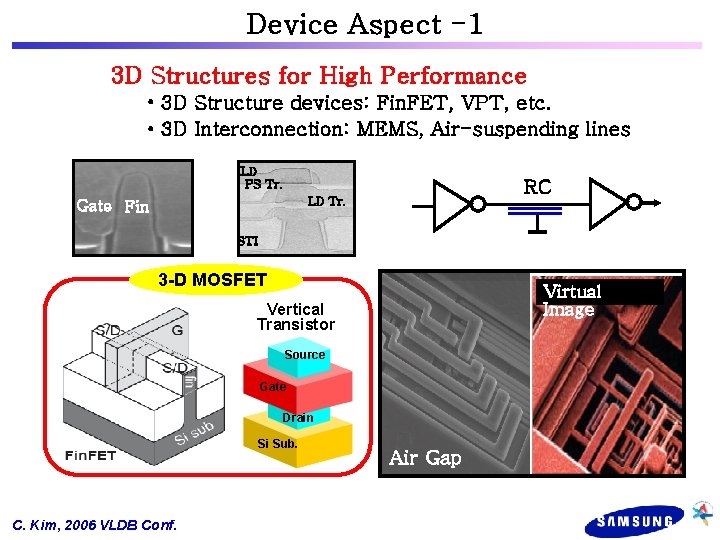

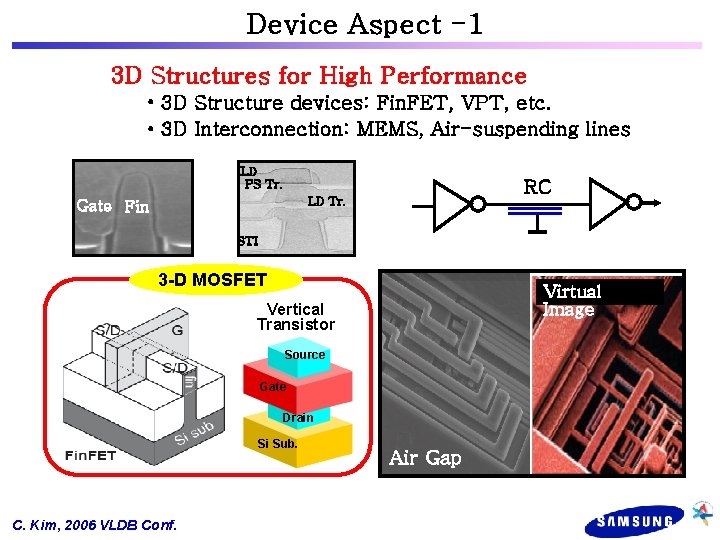

Device Aspect -1 3 D Structures for High Performance • 3 D Structure devices: Fin. FET, VPT, etc. • 3 D Interconnection: MEMS, Air-suspending lines ILD PS Tr. RC LD Tr. Gate Fin STI 3 -D MOSFET Virtual Image Vertical Transistor Source Gate Drain Si Sub. C. Kim, 2006 VLDB Conf. Air Gap

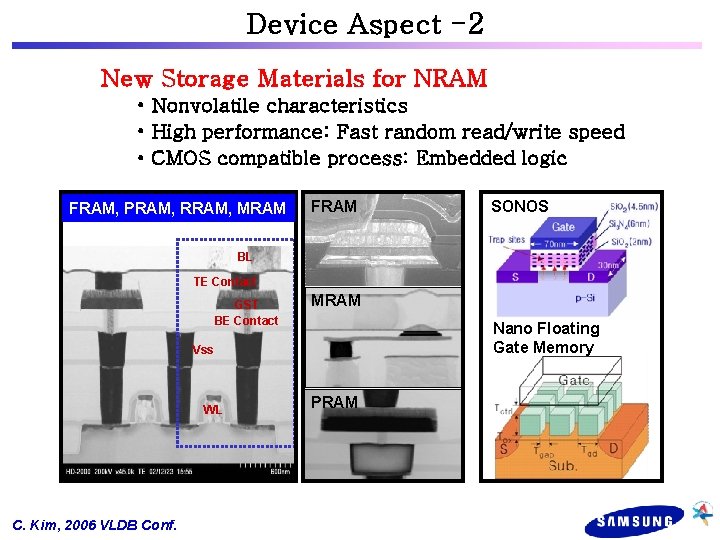

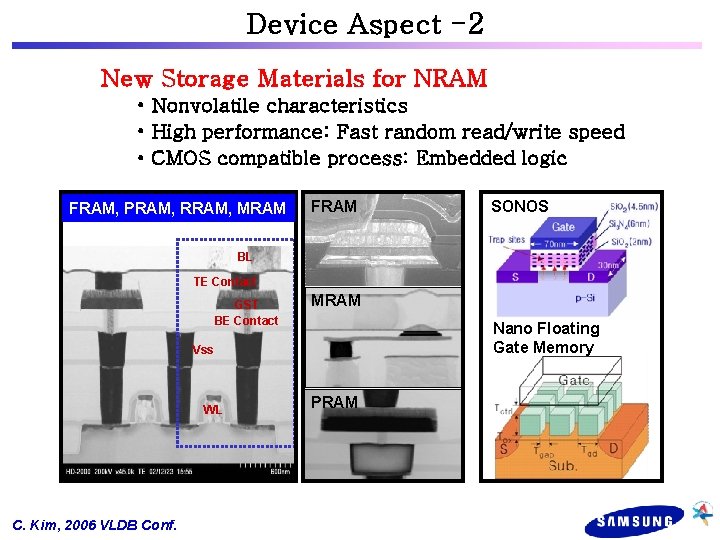

Device Aspect -2 New Storage Materials for NRAM • Nonvolatile characteristics • High performance: Fast random read/write speed • CMOS compatible process: Embedded logic FRAM, PRAM, RRAM, MRAM FRAM SONOS BL TE Contact GST BE Contact MRAM Nano Floating Gate Memory Vss WL C. Kim, 2006 VLDB Conf. PRAM

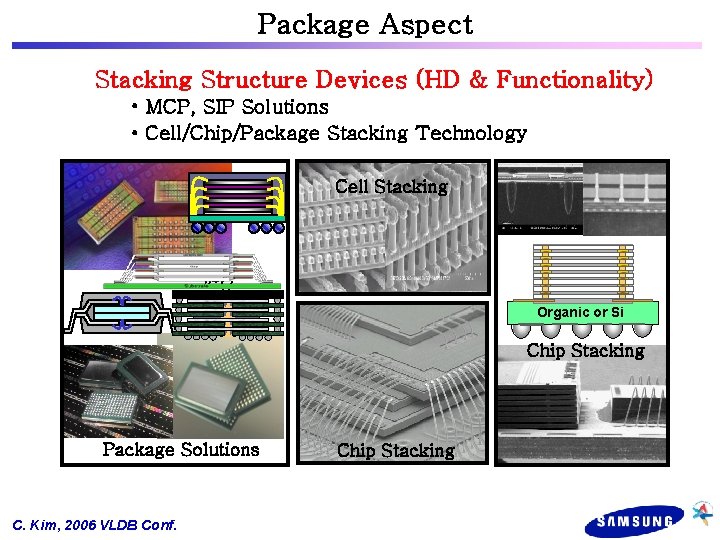

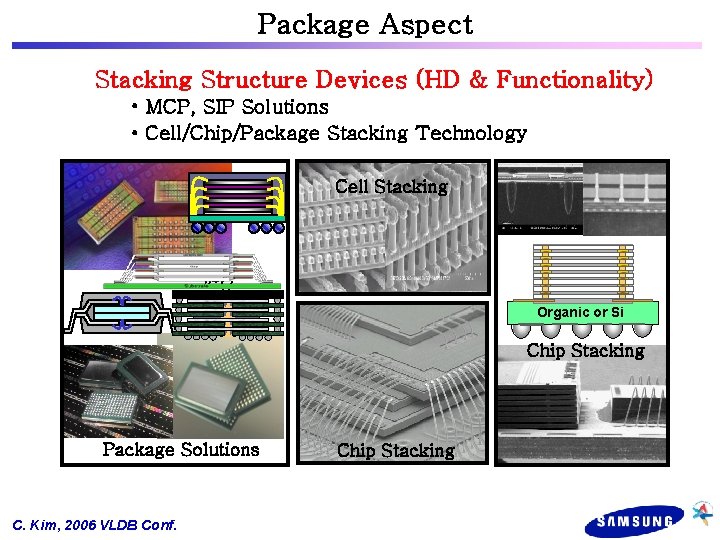

Package Aspect Stacking Structure Devices (HD & Functionality) • MCP, SIP Solutions • Cell/Chip/Package Stacking Technology Cell Stacking MP U Organic or Si Chip Stacking Package Solutions C. Kim, 2006 VLDB Conf. Chip Stacking

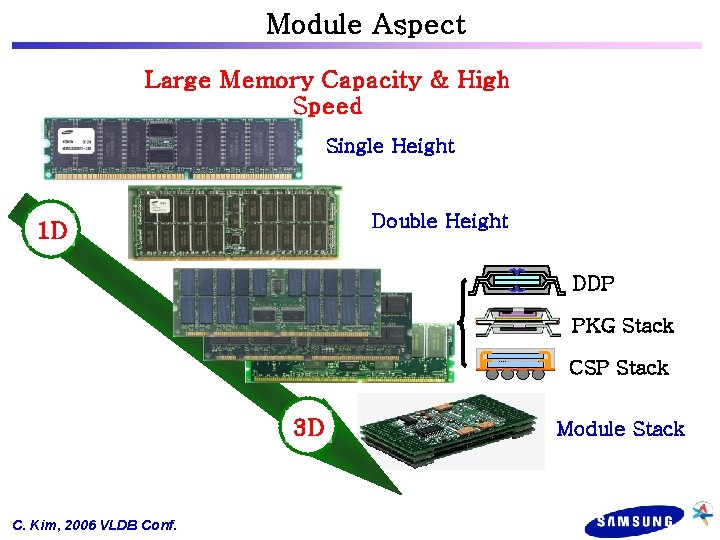

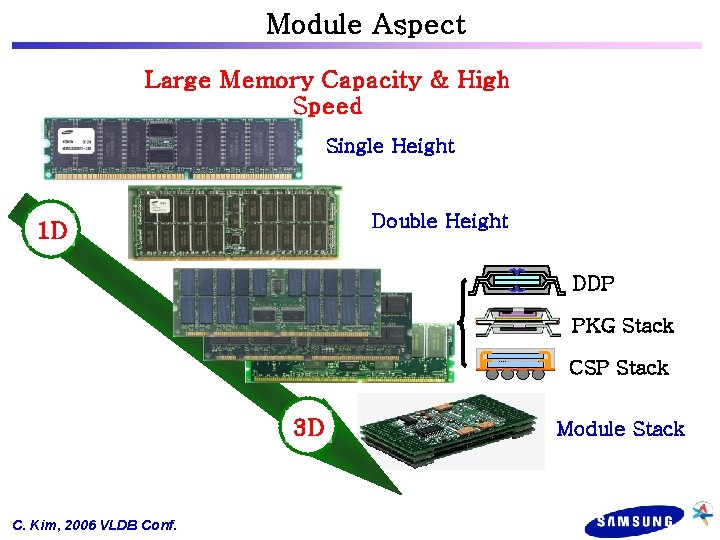

Module Aspect Large Memory Capacity & High Speed Single Height Double Height 1 D DDP PKG Stack CSP Stack 3 D C. Kim, 2006 VLDB Conf. Module Stack

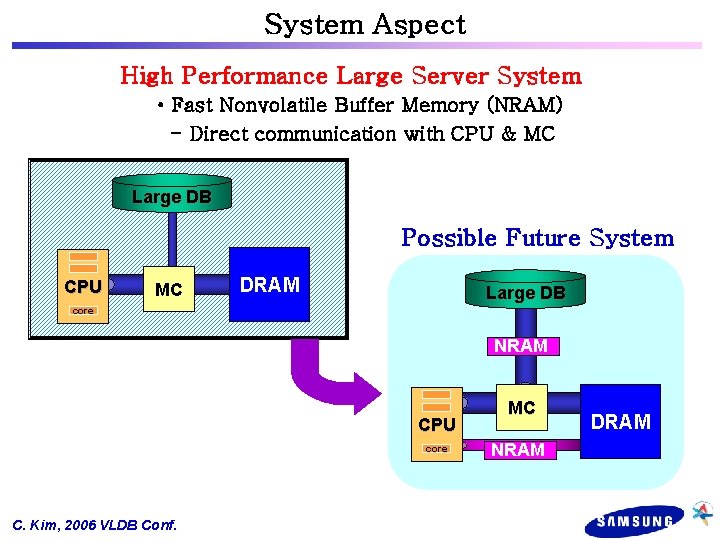

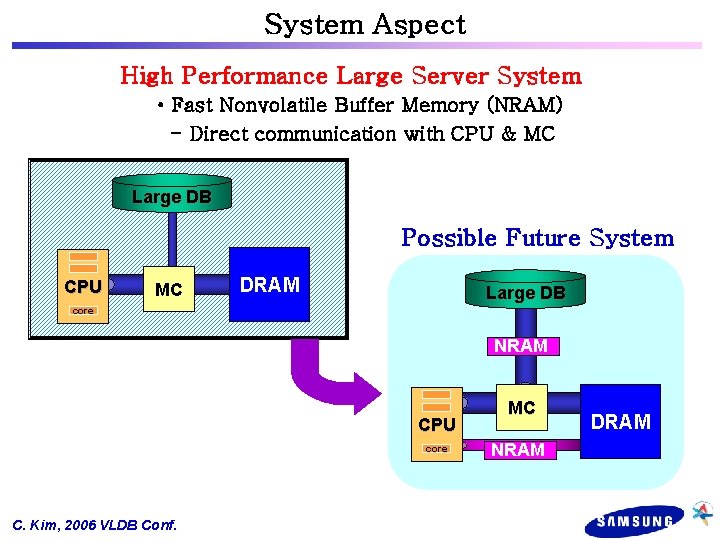

System Aspect High Performance Large Server System • Fast Nonvolatile Buffer Memory (NRAM) - Direct communication with CPU & MC Large DB Possible Future System CPU MC DRAM Large DB core NRAM CPU core C. Kim, 2006 VLDB Conf. MC NRAM DRAM

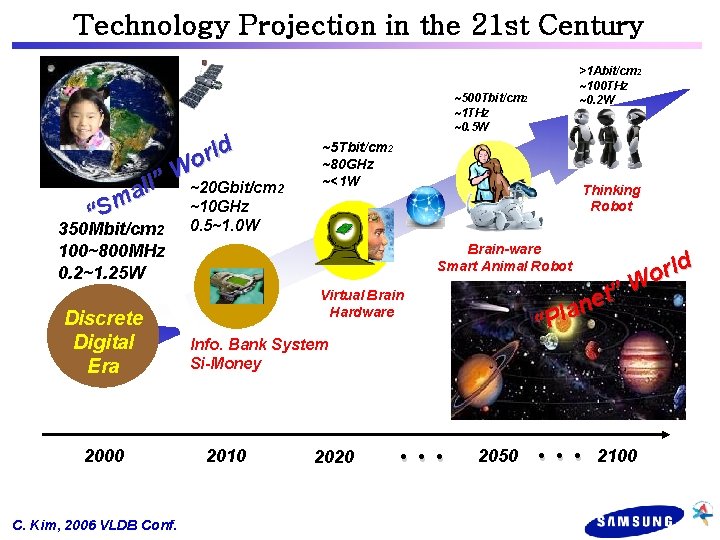

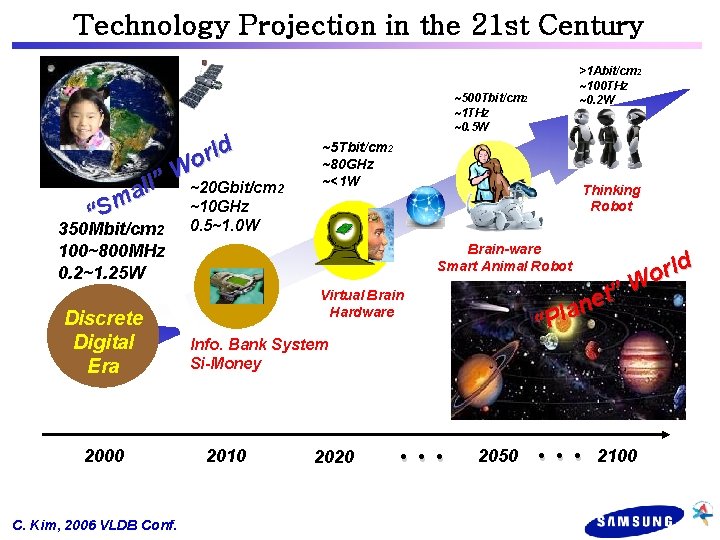

Technology Projection in the 21 st Century ll” a m “S d l r Wo 350 Mbit/cm 2 100~800 MHz 0. 2~1. 25 W Discrete Digital Era 2000 C. Kim, 2006 VLDB Conf. ~20 Gbit/cm 2 ~10 GHz 0. 5~1. 0 W >1 Abit/cm 2 ~100 THz ~0. 2 W ~500 Tbit/cm 2 ~1 THz ~0. 5 W ~5 Tbit/cm 2 ~80 GHz ~<1 W Thinking Robot Brain-ware Smart Animal Robot rld o ”W t e an l P “ Virtual Brain Hardware Info. Bank System Si-Money 2010 2020 … 2050 … 2100

IV. Conclusions C. Kim, 2006 VLDB Conf.

Conclusions • New evolutionary and revolutionary technical innovations of memory will continuously enhance system performance and will meet to satisfy customers’ needs. • The role of memory gets more important and increases than ever to create new paradigm shift including VLDB area. Memory Technology Innovations C. Kim, 2006 VLDB Conf. Creations