Advanced Photodiode Development 7 April 2000 James A

- Slides: 13

Advanced Photodiode Development 7 April, 2000 James A. Burns jab@ ll. mit. edu NU Status-1 JAB 10/29/2021 MIT Lincoln Laboratory

3 D Photodiode Development Snapshot • Goal – Produce high quality photodiodes for visible imaging Standard CMOS processes do not produce image-quality photodiodes Photodiode process must be compatible with 3 D integration • Approach – Review existing Lincoln silicon-photodiode processes – Optimize an existing process to meet the active pixel sensor requirements using Process and device simulation Additional characterization of existing photodiodes • Tasks – Define photodiode requirements – Define photodiode fabrication process – Layout a photodiode test chip – Fabricate and characterize photodiodes 3 runs to optimize device properties 3 D integration and photodiode characterization NU Status-2 JAB 10/29/2021 MIT Lincoln Laboratory

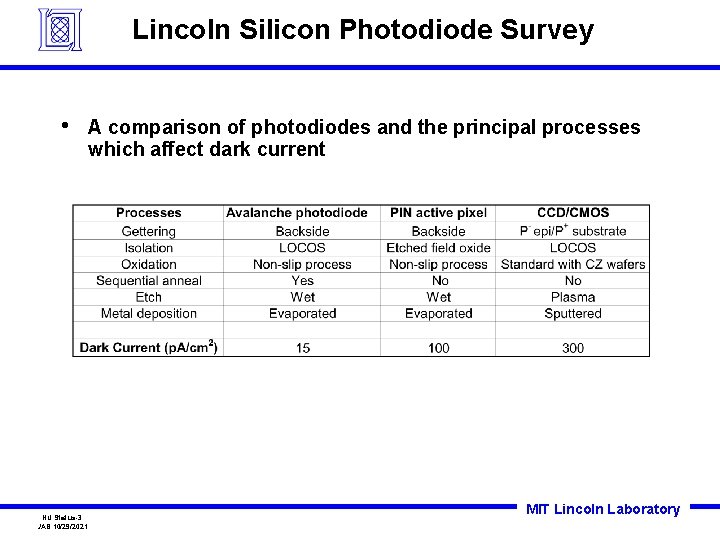

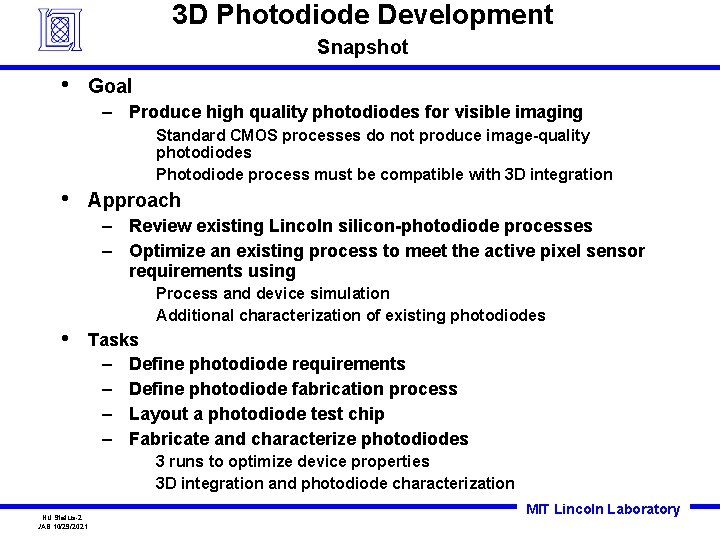

Lincoln Silicon Photodiode Survey • NU Status-3 JAB 10/29/2021 A comparison of photodiodes and the principal processes which affect dark current MIT Lincoln Laboratory

Photodiode Process 1 st Pass • Bulk substrate – 25 -mm epi, 300 -cm – 0. 01 -cm p-type wafer • Process highlights – LOCOS isolation 30 -nm stress-relief oxide 20 -nm Si 3 N 4 – 250 -nm field oxide – Dual N+ implant Phosphorus to obtain a deep junction Arsenic to maintain high C 0 – Extended anneal to repair N+ implant damage • Eight Mask Levels – Six through metal-1, passivation – Deep via and back metal for 3 D integration tests NU Status-4 JAB 10/29/2021 MIT Lincoln Laboratory

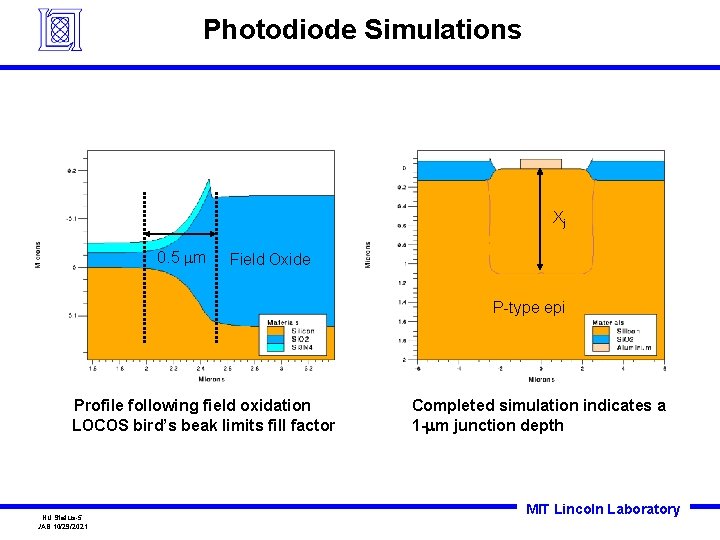

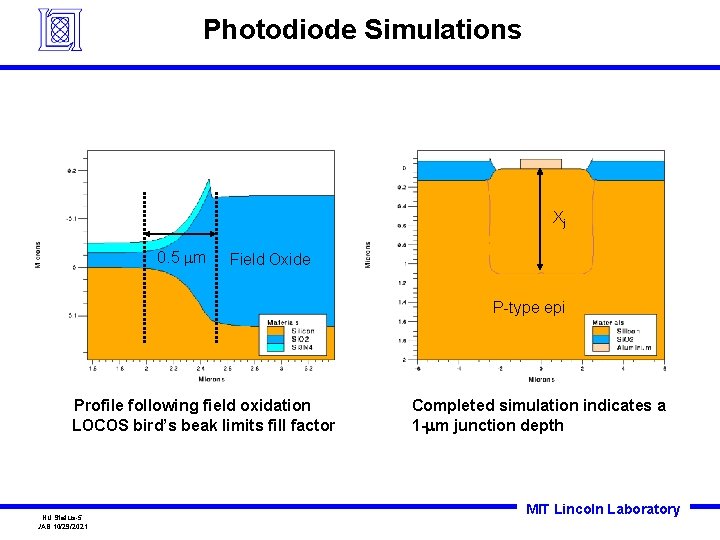

Photodiode Simulations Xj 0. 5 mm Field Oxide P-type epi Profile following field oxidation LOCOS bird’s beak limits fill factor NU Status-5 JAB 10/29/2021 Completed simulation indicates a 1 -mm junction depth MIT Lincoln Laboratory

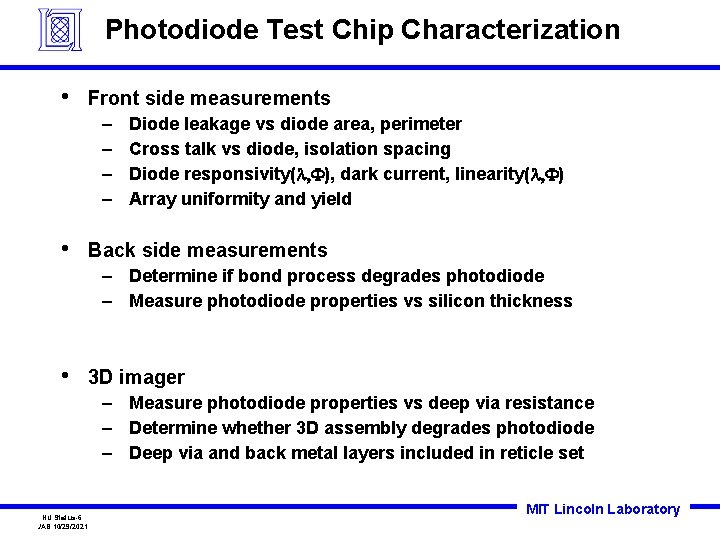

Photodiode Test Chip Characterization • Front side measurements – – • Diode leakage vs diode area, perimeter Cross talk vs diode, isolation spacing Diode responsivity(l, F), dark current, linearity(l, F) Array uniformity and yield Back side measurements – Determine if bond process degrades photodiode – Measure photodiode properties vs silicon thickness • 3 D imager – Measure photodiode properties vs deep via resistance – Determine whether 3 D assembly degrades photodiode – Deep via and back metal layers included in reticle set NU Status-6 JAB 10/29/2021 MIT Lincoln Laboratory

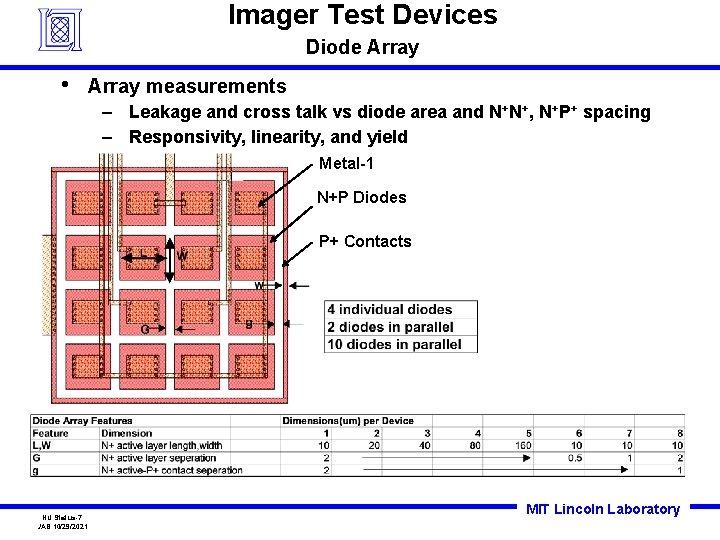

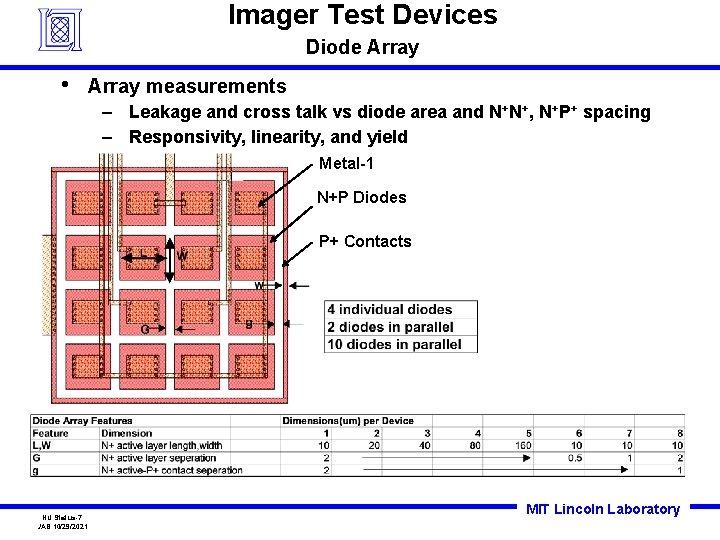

Imager Test Devices Diode Array • Array measurements – Leakage and cross talk vs diode area and N+N+, N+P+ spacing – Responsivity, linearity, and yield Metal-1 N+P Diodes P+ Contacts NU Status-7 JAB 10/29/2021 MIT Lincoln Laboratory

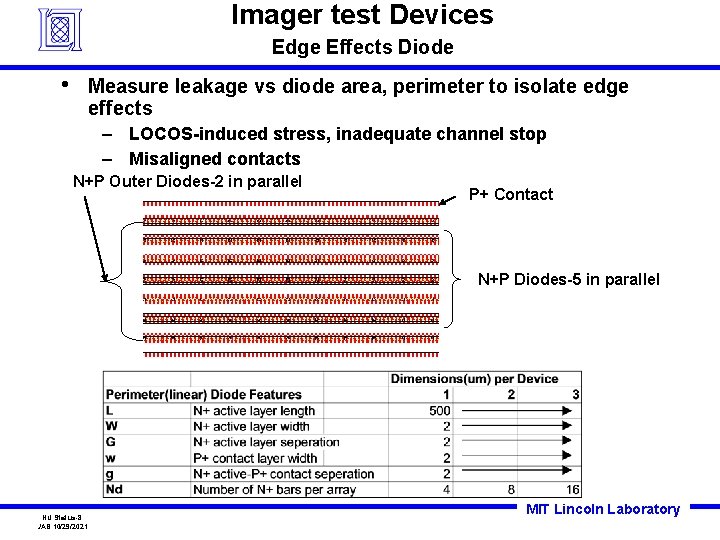

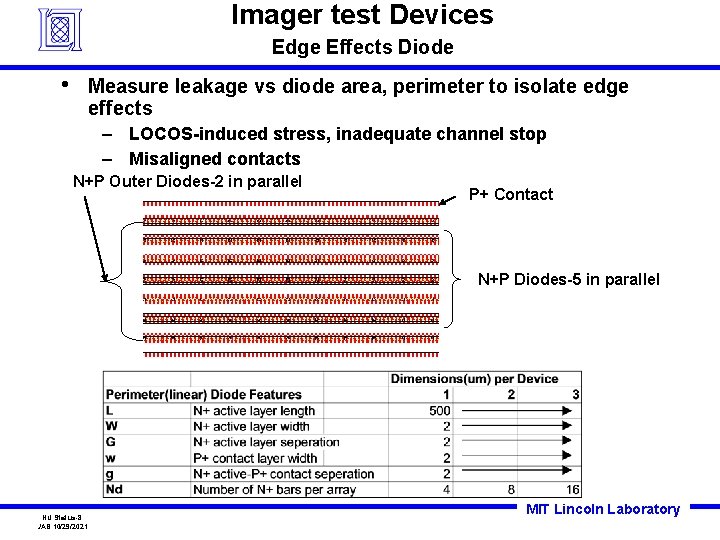

Imager test Devices Edge Effects Diode • Measure leakage vs diode area, perimeter to isolate edge effects – LOCOS-induced stress, inadequate channel stop – Misaligned contacts N+P Outer Diodes-2 in parallel P+ Contact N+P Diodes-5 in parallel NU Status-8 JAB 10/29/2021 MIT Lincoln Laboratory

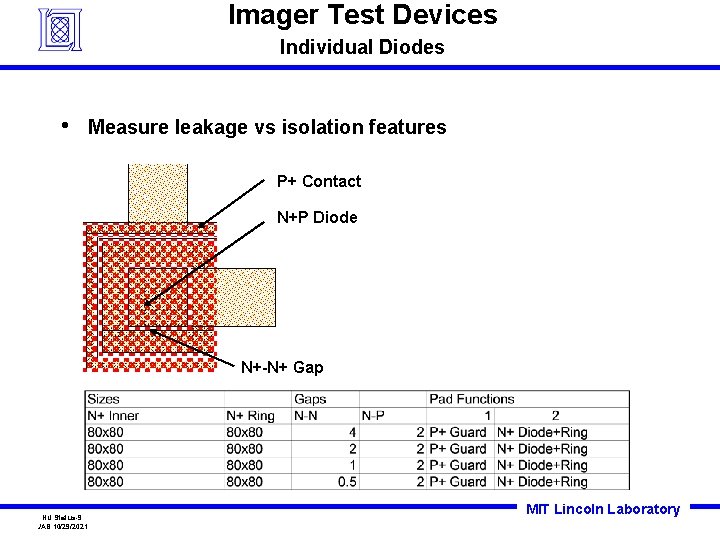

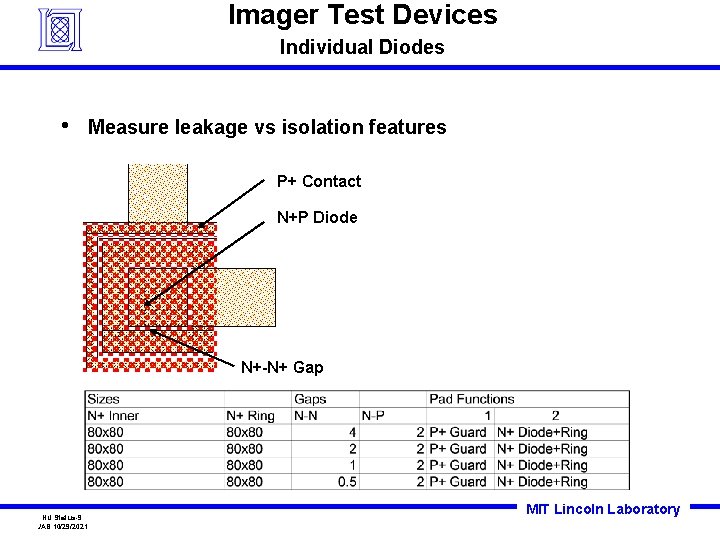

Imager Test Devices Individual Diodes • Measure leakage vs isolation features P+ Contact N+P Diode N+-N+ Gap NU Status-9 JAB 10/29/2021 MIT Lincoln Laboratory

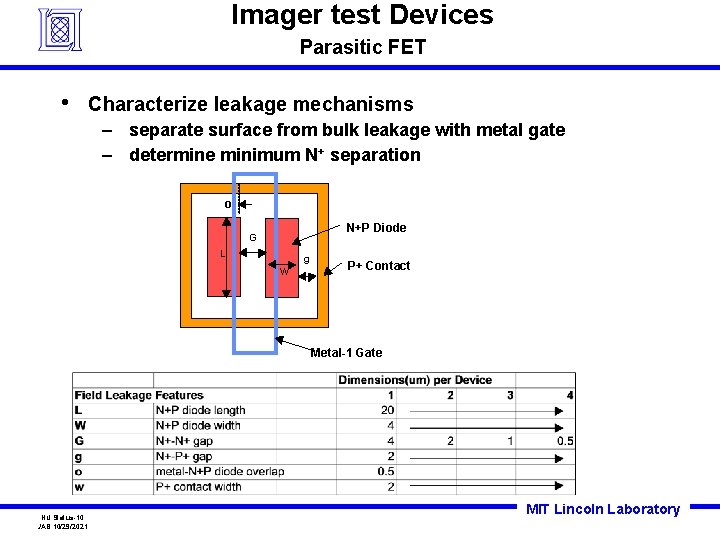

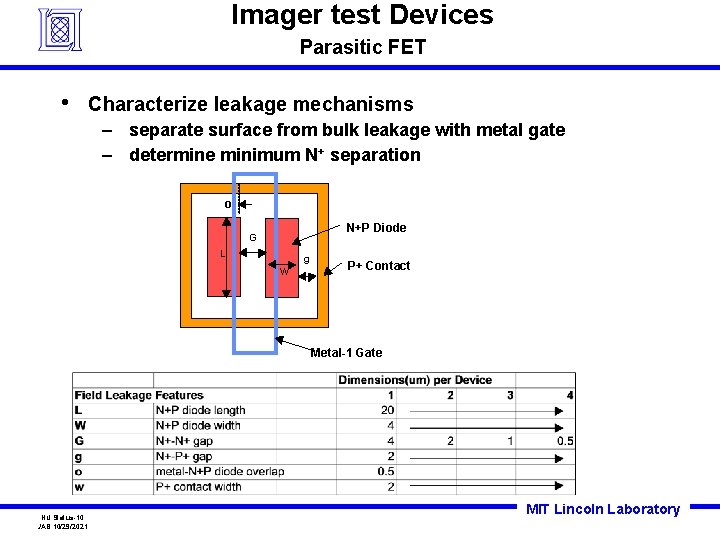

Imager test Devices Parasitic FET • Characterize leakage mechanisms – separate surface from bulk leakage with metal gate – determine minimum N+ separation o N+P Diode G L g W P+ Contact Metal-1 Gate NU Status-10 JAB 10/29/2021 MIT Lincoln Laboratory

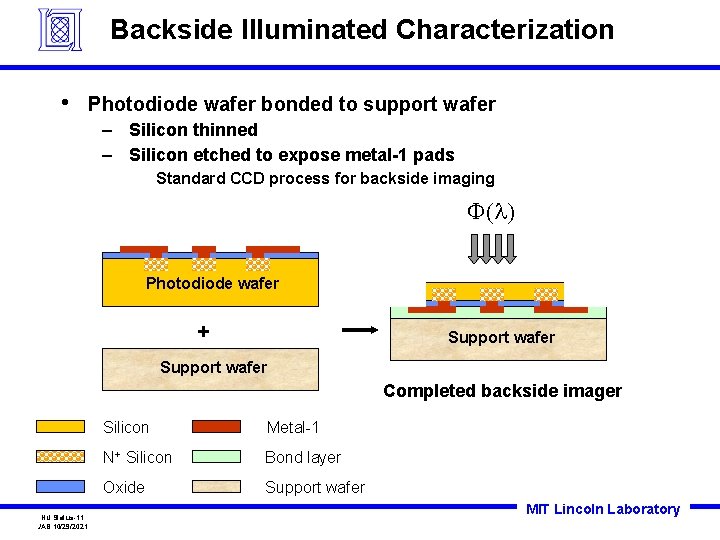

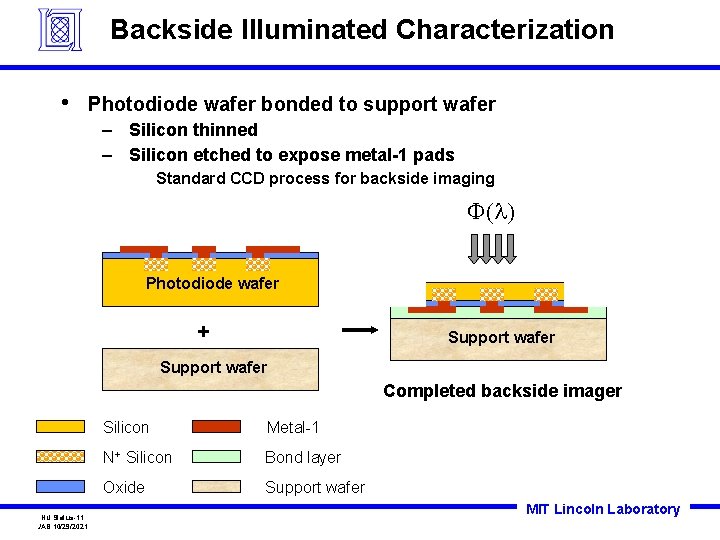

Backside Illuminated Characterization • Photodiode wafer bonded to support wafer – Silicon thinned – Silicon etched to expose metal-1 pads Standard CCD process for backside imaging F(l) Photodiode wafer + Support wafer Completed backside imager NU Status-11 JAB 10/29/2021 Silicon Metal-1 N+ Silicon Bond layer Oxide Support wafer MIT Lincoln Laboratory

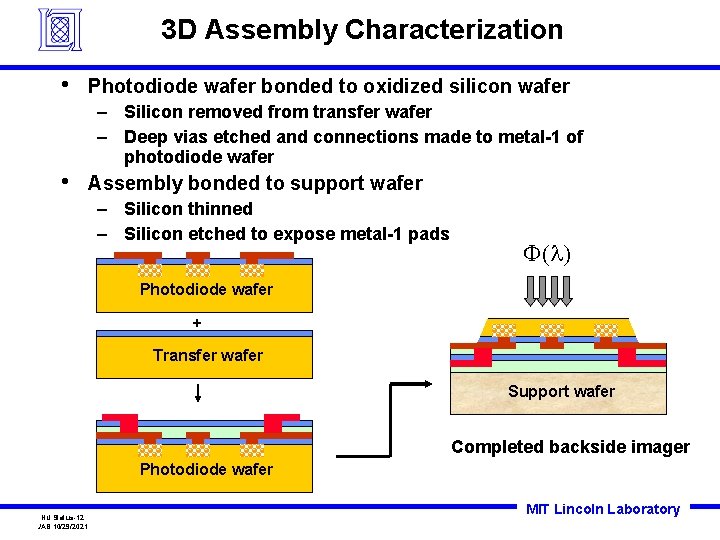

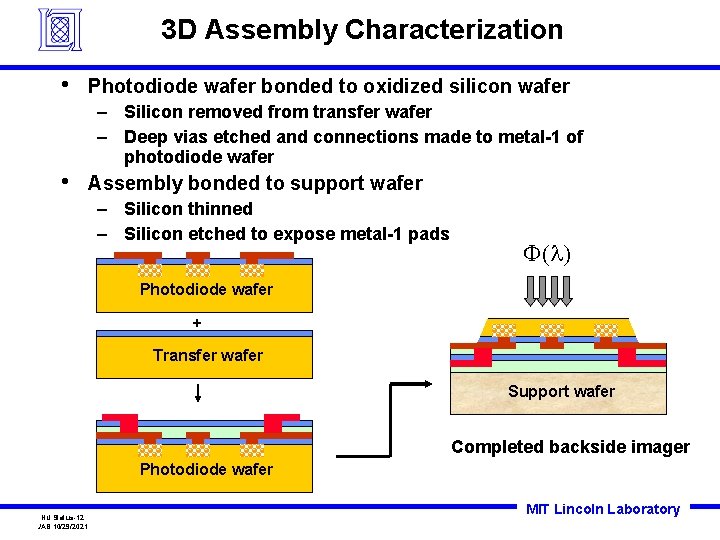

3 D Assembly Characterization • Photodiode wafer bonded to oxidized silicon wafer – Silicon removed from transfer wafer – Deep vias etched and connections made to metal-1 of photodiode wafer • Assembly bonded to support wafer – Silicon thinned – Silicon etched to expose metal-1 pads F(l) Photodiode wafer + Transfer wafer Support wafer Completed backside imager Photodiode wafer NU Status-12 JAB 10/29/2021 MIT Lincoln Laboratory

Photodiode Development Status • Silicon photodiode process survey complete • Initial process defined; optimization via simulation underway • Test devices defined; layout nearly complete NU Status-13 JAB 10/29/2021 MIT Lincoln Laboratory