Advanced Analog IC Design EECT 7326 Fall 2013

- Slides: 11

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu SPICE Simulation of Generalized Return Ratio (GRR) vs. Loop Gain (LG) – 1–

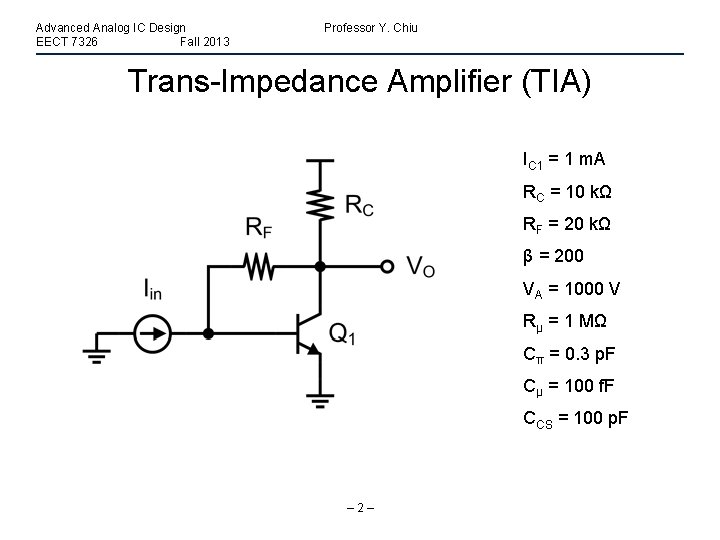

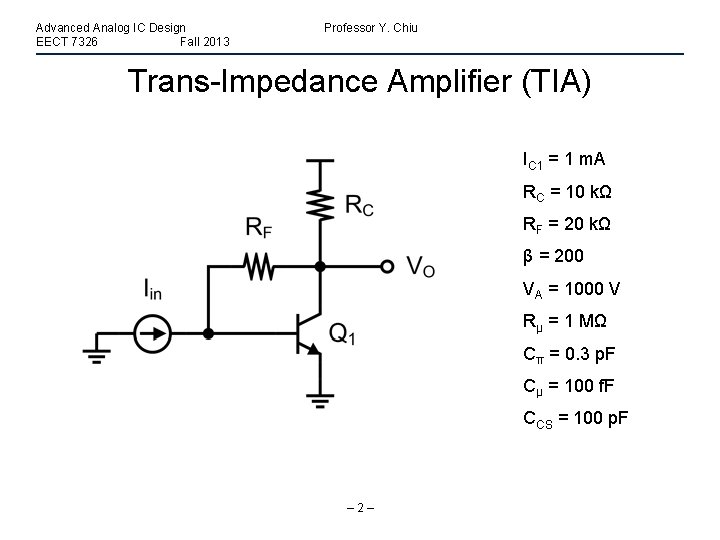

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu Trans-Impedance Amplifier (TIA) IC 1 = 1 m. A RC = 10 kΩ RF = 20 kΩ β = 200 VA = 1000 V Rμ = 1 MΩ Cπ = 0. 3 p. F Cμ = 100 f. F CCS = 100 p. F – 2–

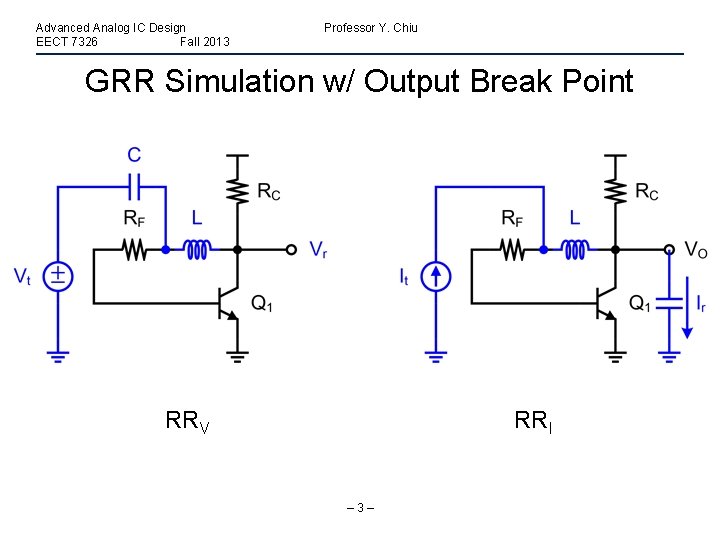

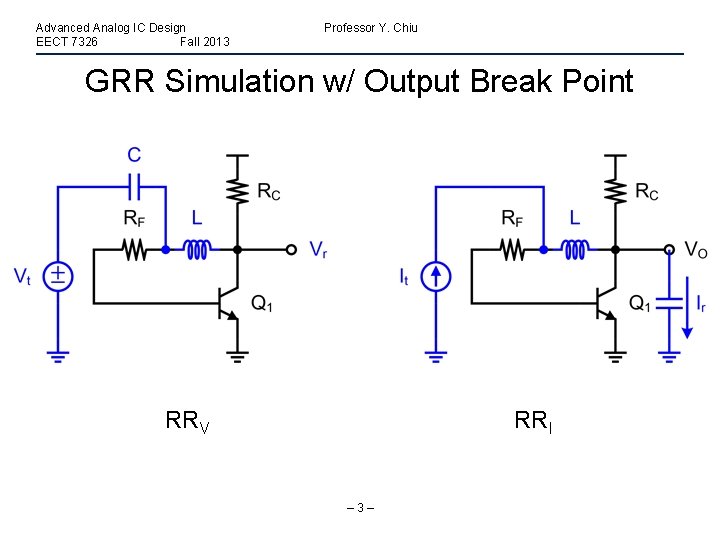

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu GRR Simulation w/ Output Break Point RRV RRI – 3–

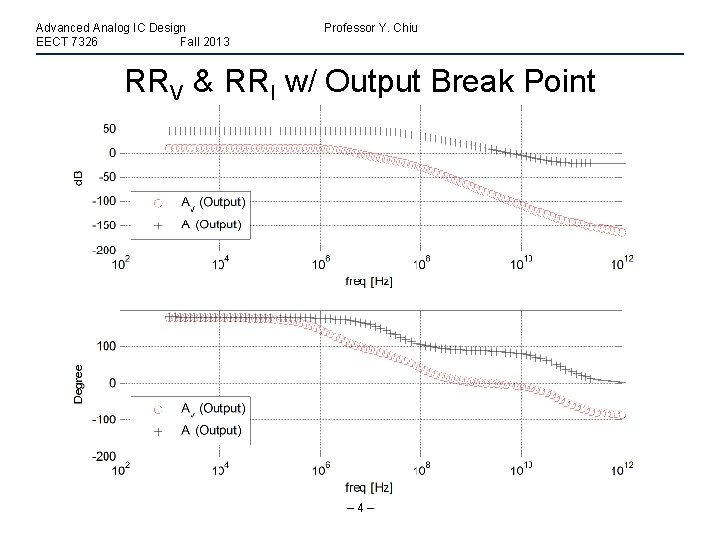

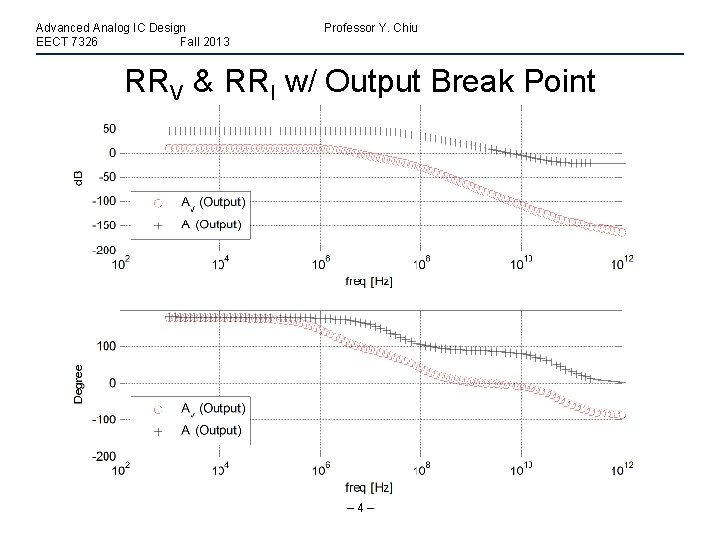

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu RRV & RRI w/ Output Break Point – 4–

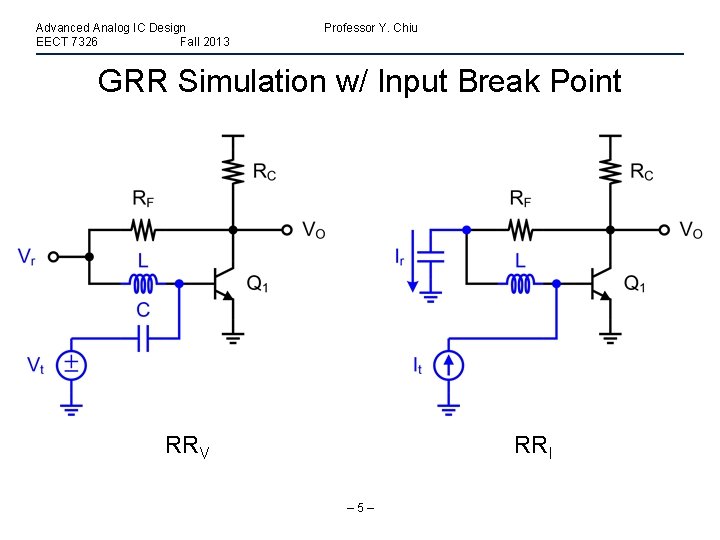

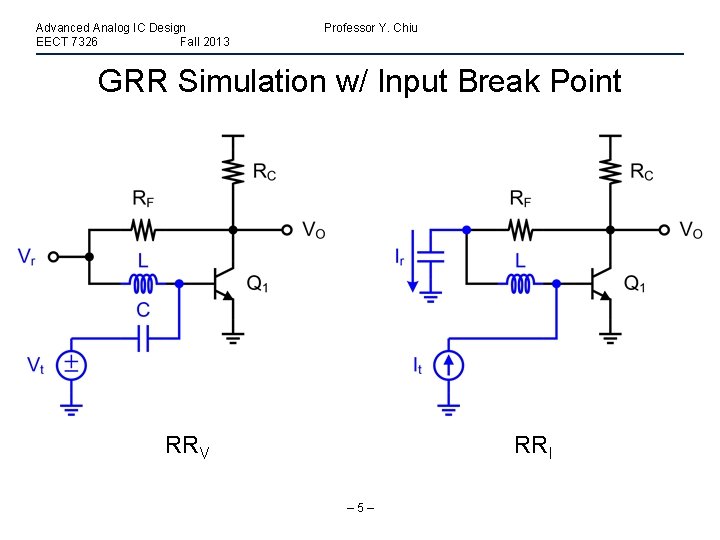

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu GRR Simulation w/ Input Break Point RRV RRI – 5–

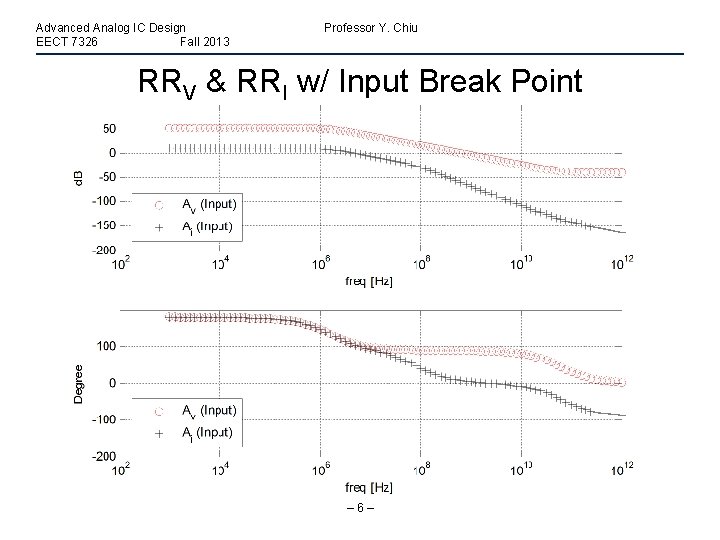

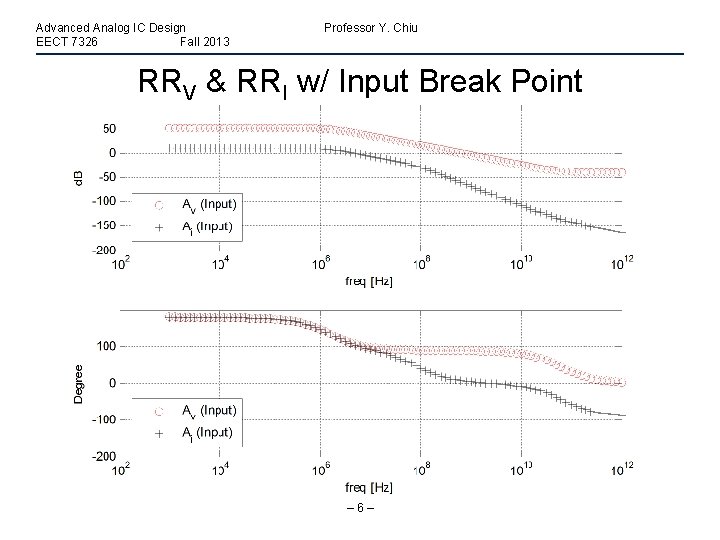

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu RRV & RRI w/ Input Break Point – 6–

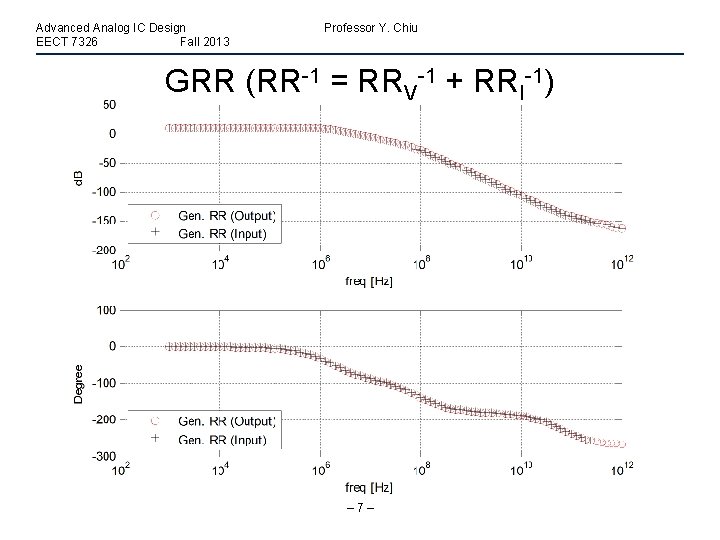

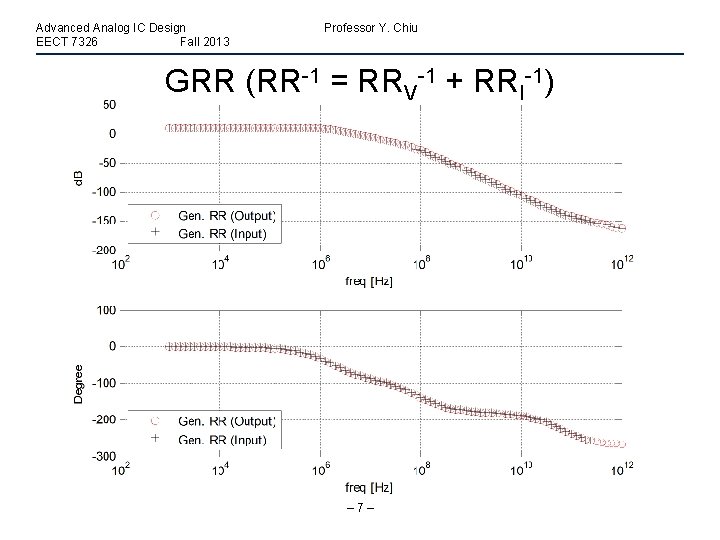

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu GRR (RR-1 = RRV-1 + RRI-1) – 7–

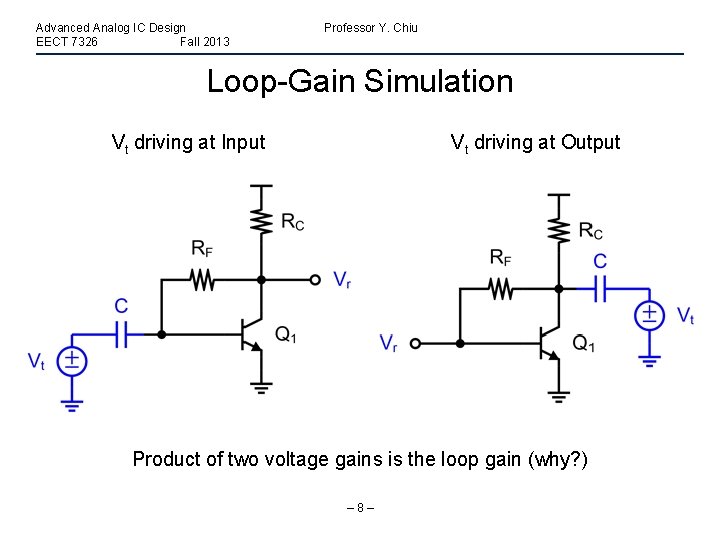

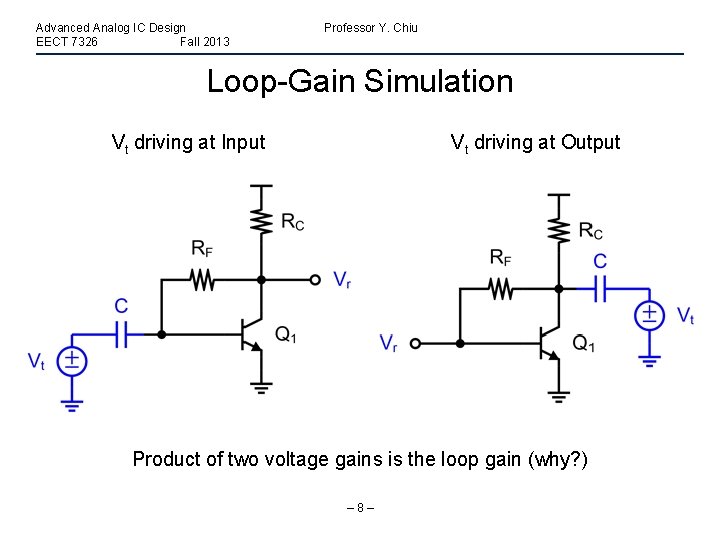

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu Loop-Gain Simulation Vt driving at Input Vt driving at Output Product of two voltage gains is the loop gain (why? ) – 8–

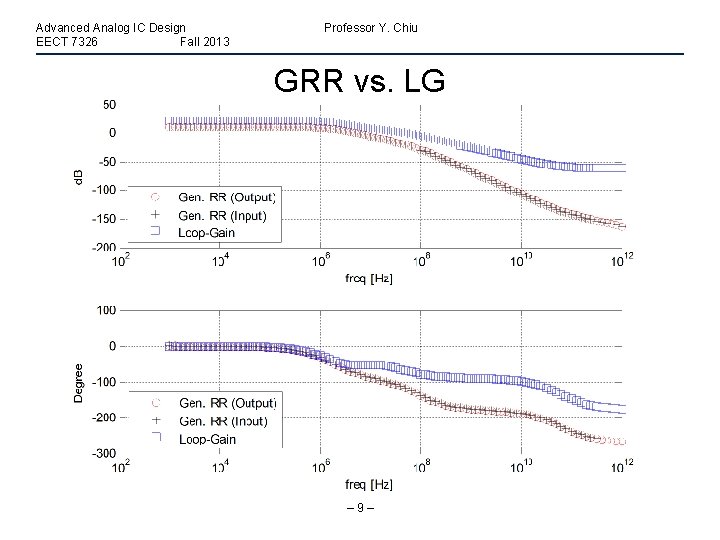

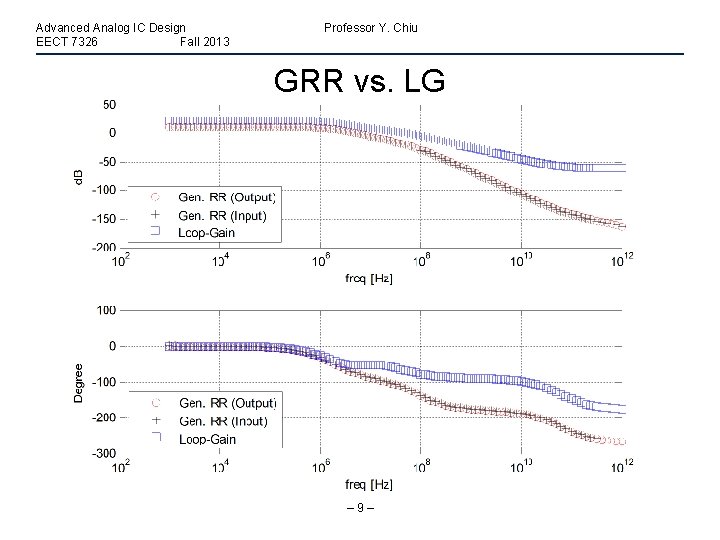

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu GRR vs. LG – 9–

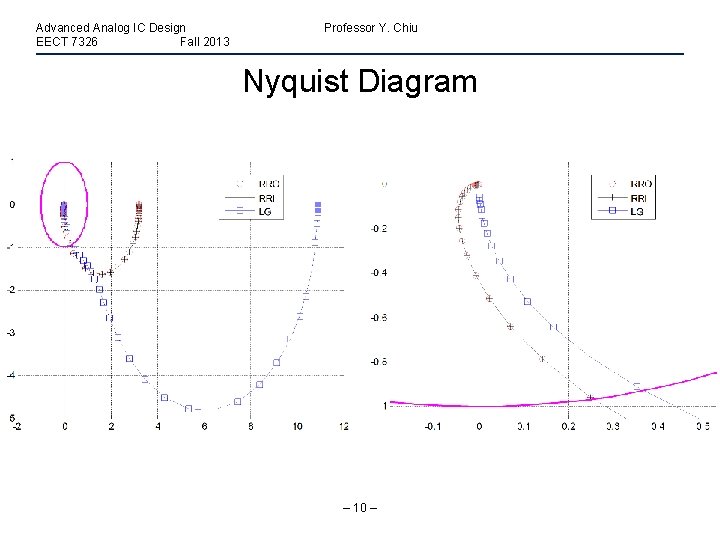

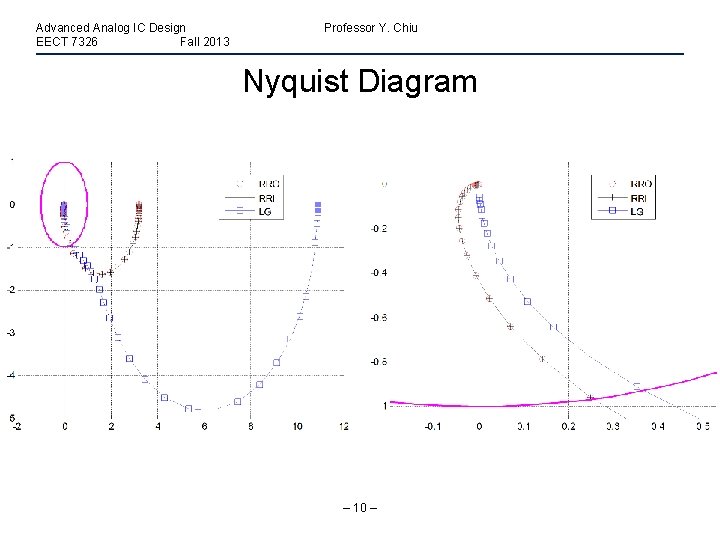

Advanced Analog IC Design EECT 7326 Fall 2013 Professor Y. Chiu Nyquist Diagram – 10 –

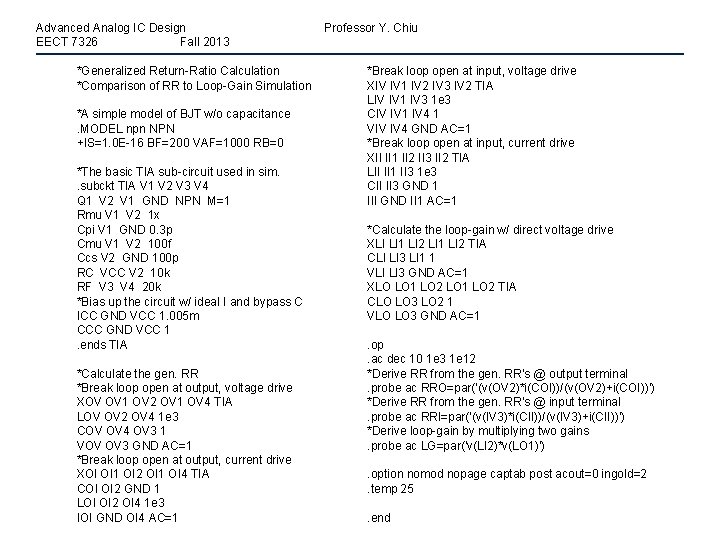

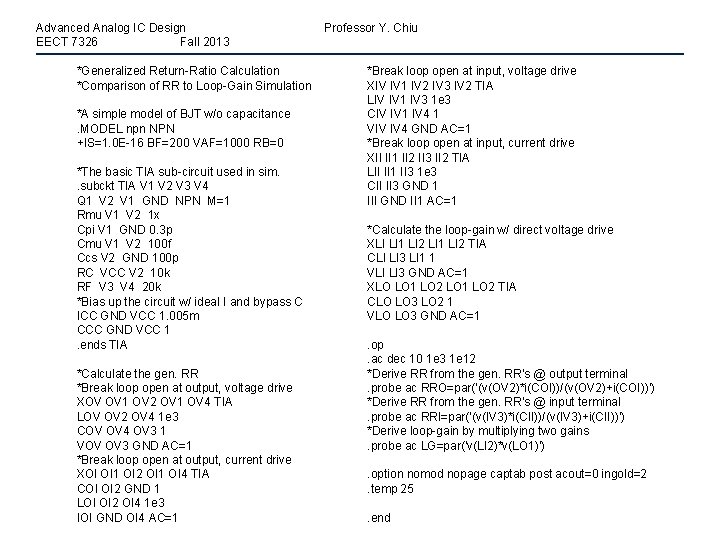

Advanced Analog IC Design EECT 7326 Fall 2013 *Generalized Return-Ratio Calculation *Comparison of RR to Loop-Gain Simulation *A simple model of BJT w/o capacitance. MODEL npn NPN +IS=1. 0 E-16 BF=200 VAF=1000 RB=0 *The basic TIA sub-circuit used in sim. . subckt TIA V 1 V 2 V 3 V 4 Q 1 V 2 V 1 GND NPN M=1 Rmu V 1 V 2 1 x Cpi V 1 GND 0. 3 p Cmu V 1 V 2 100 f Ccs V 2 GND 100 p RC VCC V 2 10 k RF V 3 V 4 20 k *Bias up the circuit w/ ideal I and bypass C ICC GND VCC 1. 005 m CCC GND VCC 1. ends TIA *Calculate the gen. RR *Break loop open at output, voltage drive XOV OV 1 OV 2 OV 1 OV 4 TIA LOV OV 2 OV 4 1 e 3 COV OV 4 OV 3 1 VOV OV 3 GND AC=1 *Break loop open at output, current drive XOI OI 1 OI 2 OI 1 OI 4 TIA COI OI 2 GND 1 LOI OI 2 OI 4 1 e 3 IOI GND OI 4 AC=1 Professor Y. Chiu *Break loop open at input, voltage drive XIV IV 1 IV 2 IV 3 IV 2 TIA LIV IV 1 IV 3 1 e 3 CIV IV 1 IV 4 1 VIV IV 4 GND AC=1 *Break loop open at input, current drive XII II 1 II 2 II 3 II 2 TIA LII II 1 II 3 1 e 3 CII II 3 GND 1 III GND II 1 AC=1 *Calculate the loop-gain w/ direct voltage drive XLI LI 1 LI 2 TIA CLI LI 3 LI 1 1 VLI LI 3 GND AC=1 XLO LO 1 LO 2 TIA CLO LO 3 LO 2 1 VLO LO 3 GND AC=1. op. ac dec 10 1 e 3 1 e 12 *Derive RR from the gen. RR's @ output terminal. probe ac RRO=par('(v(OV 2)*i(COI))/(v(OV 2)+i(COI))') *Derive RR from the gen. RR's @ input terminal. probe ac RRI=par('(v(IV 3)*i(CII))/(v(IV 3)+i(CII))') *Derive loop-gain by multiplying two gains. probe ac LG=par('v(LI 2)*v(LO 1)'). option nomod nopage captab post acout=0 ingold=2. temp 25. end