ADVANCED 8 PIN LOADSHARE CONTROLLER UCC 39002 UCC

- Slides: 24

ADVANCED 8 -PIN LOAD-SHARE CONTROLLER UCC 39002 UCC 29002/1 Jan 2007 1

What is Load Share? v What is Load Share? • Provides equal distribution of the load current among parallel voltage-stabilized power supplies • Why parallel supplies? Ø High current/low voltage applications Ø Redundancy for enhanced reliability Ø Hot Swap capability Ø Distributed heat removal Ø Space and cost Jan 2007 2

Why would you need a Controller? v. Output impedance of power modules < 1 m. W ØWhen connected in parallel, the supply with the highest Vout will supply the majority of the output current. Because the output R is so low, it doesn’t take a large difference in Vout for this to result in large current differences. ü Current-limit mode ü increased stress = decreased reliability Jan 2007 3

The Concept v. Basic concept of load-share controller: supply a voltage feedback loop • Iout of each module is accurately measured then compared to a current share bus • Vout is adjusted so each module delivers an equal amount of output current Jan 2007 4

The Modules Ø Modules must have Ø True remote sense capability or an output voltage adjustment terminal Ø Pre-biased load capability Ø Temporarily disable SR FET so as not to sink current which would discharge Cout during SS resulting in voltage glitching, neg transients, start up oscillations Ø Must source but not sink current Ø Decoupling diode (not ORing FET) Ø Without the diode sourcing modules will pump current into the sinking module. SR acts as booster to pump energy from the common output DC bus to the primary of the module sinking current. Ø Need one load share controller per module Jan 2007 5

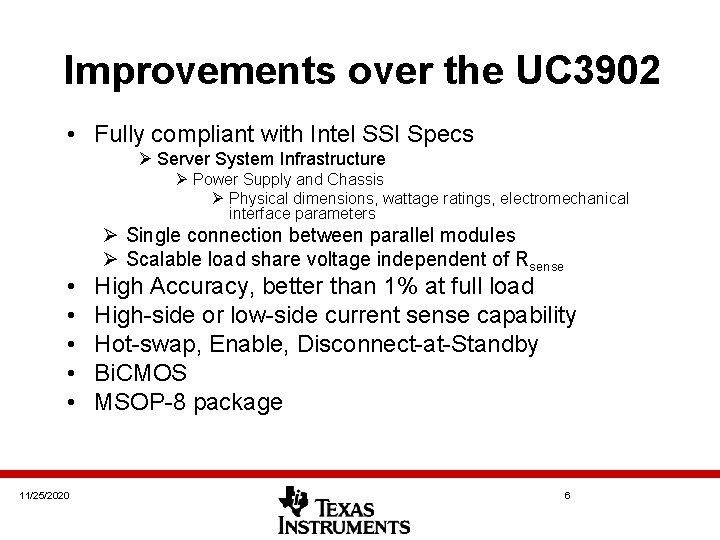

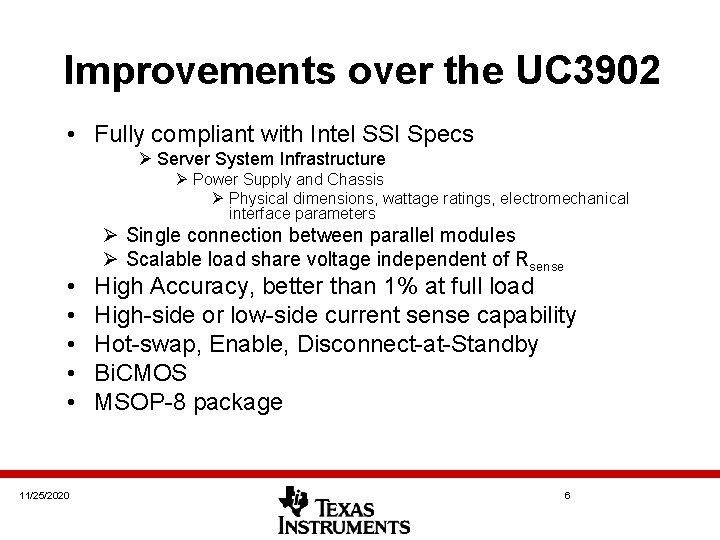

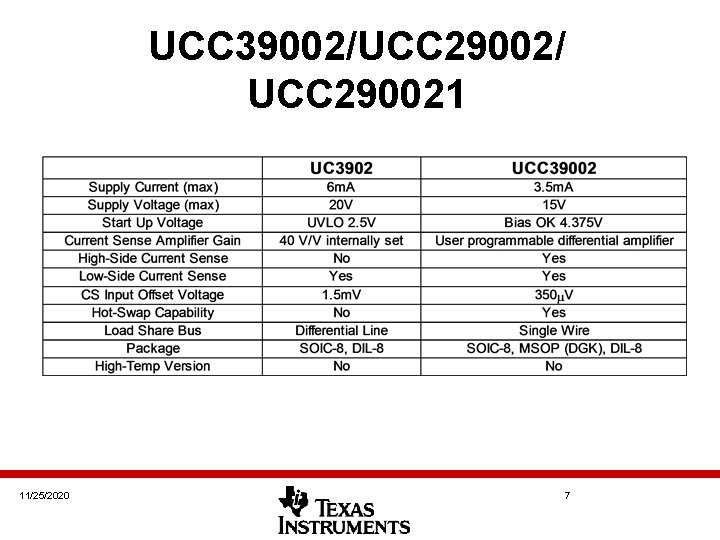

Improvements over the UC 3902 • Fully compliant with Intel SSI Specs Ø Server System Infrastructure Ø Power Supply and Chassis Ø Physical dimensions, wattage ratings, electromechanical interface parameters • • • 11/25/2020 Ø Single connection between parallel modules Ø Scalable load share voltage independent of Rsense High Accuracy, better than 1% at full load High-side or low-side current sense capability Hot-swap, Enable, Disconnect-at-Standby Bi. CMOS MSOP-8 package 6

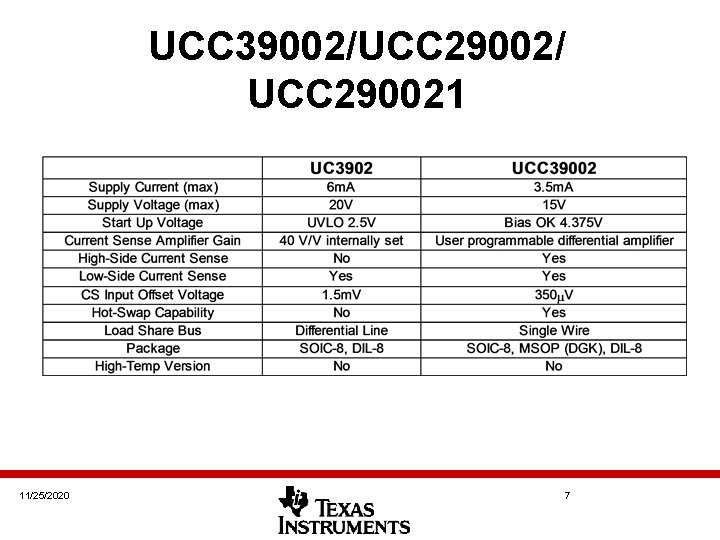

UCC 39002/UCC 29002/ UCC 290021 11/25/2020 7

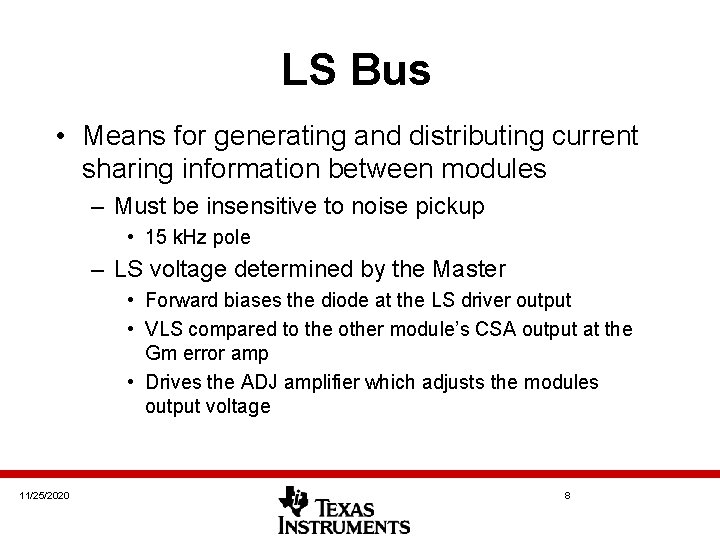

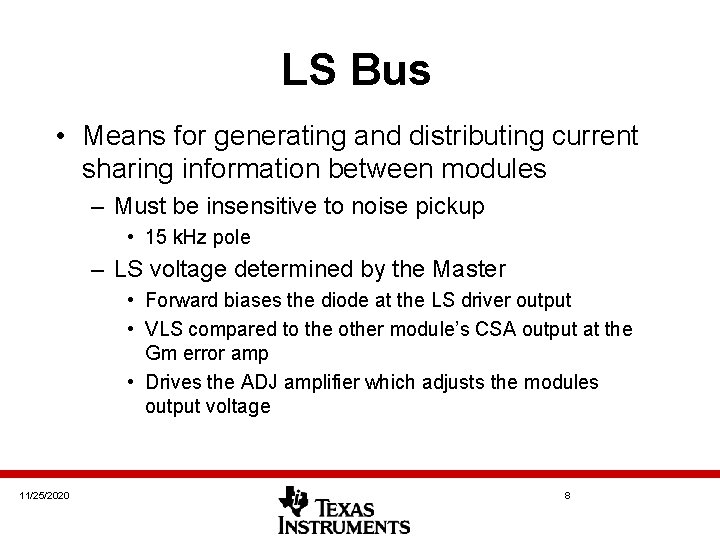

LS Bus • Means for generating and distributing current sharing information between modules – Must be insensitive to noise pickup • 15 k. Hz pole – LS voltage determined by the Master • Forward biases the diode at the LS driver output • VLS compared to the other module’s CSA output at the Gm error amp • Drives the ADJ amplifier which adjusts the modules output voltage 11/25/2020 8

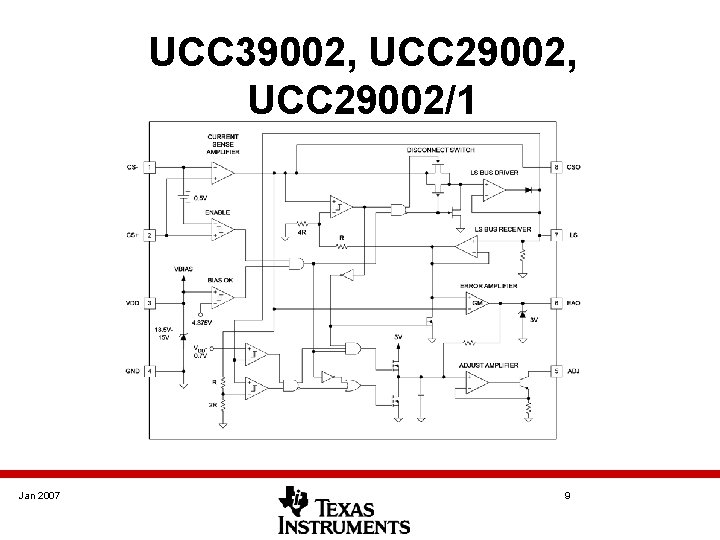

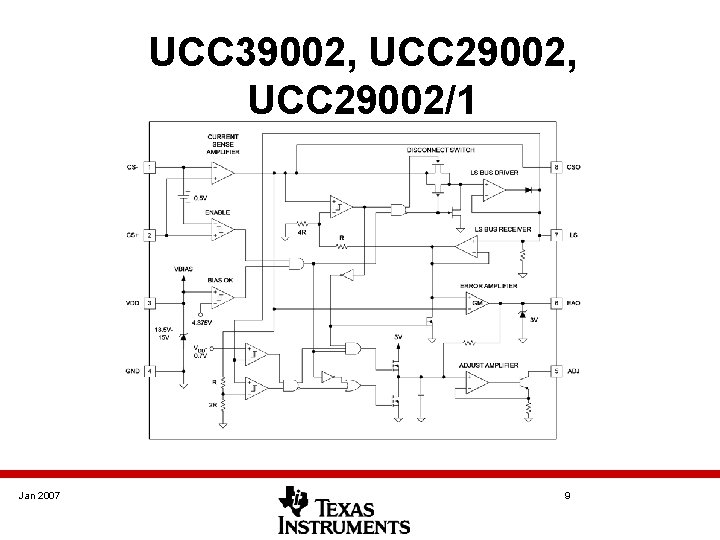

UCC 39002, UCC 29002/1 Jan 2007 9

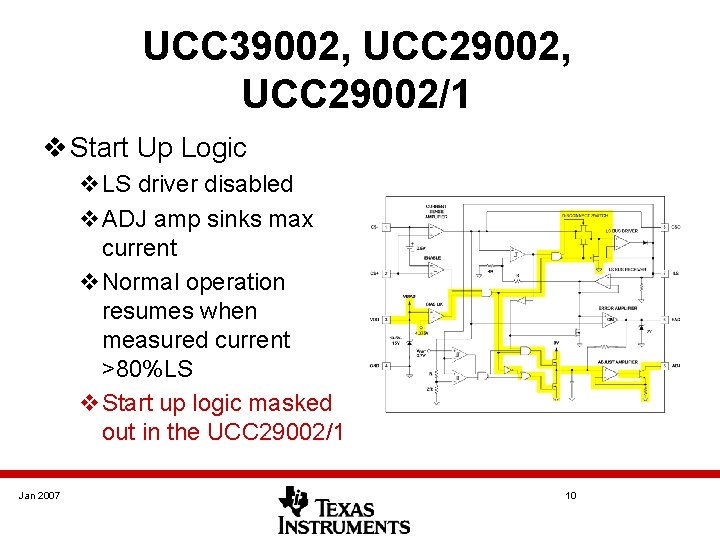

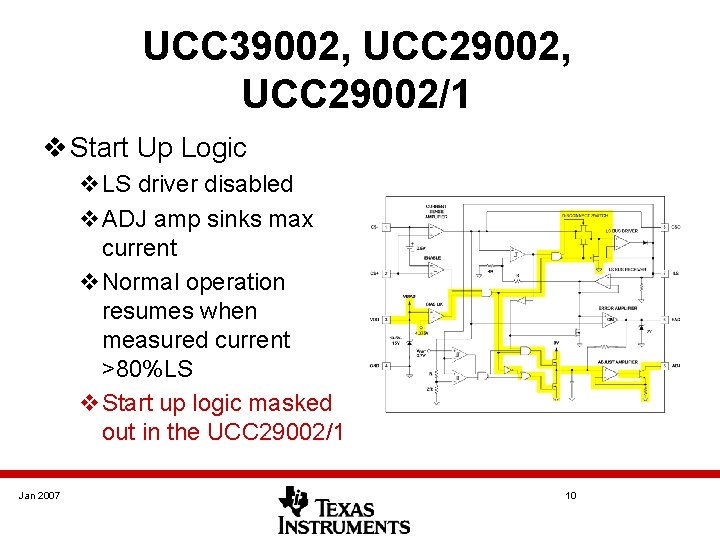

UCC 39002, UCC 29002/1 v Start Up Logic v. LS driver disabled v. ADJ amp sinks max current v. Normal operation resumes when measured current >80%LS v. Start up logic masked out in the UCC 29002/1 Jan 2007 10

What and Why • Original Design (UCC 29002 and UCC 39002) – At start up, LS driver is disabled and ADJ amp is forced to sink MAX current • • Jan 2007 Starts in known state Module forced full on to engage in sharing asap Output of module adjusted high At 80% of LS, ADJ amp reverts to normal 11

What and Why • /1 – Prompted by Cisco – Output oscillating at start up “The difference is the inverter coming from the hysteretic comparator off the CS amplifier is disconnected (it's the one in the center of the block diagram). Since it's disconnected, we ground out the NFET on the positive input of the error amplifier. The inverter also was going into an AND gate at the bottom of the diagram that feeds into an NFET that can pull up the Adjust amplifier's positive input to 3 V. That signal going to the AND gate is now tied to ground, which disables the NFET being able to pull the + input on the Adjust amp to 3 V. ” Jan 2007 12

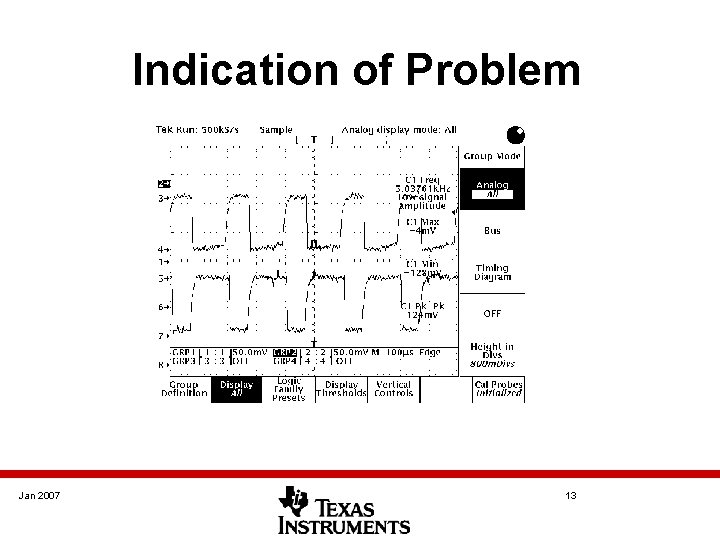

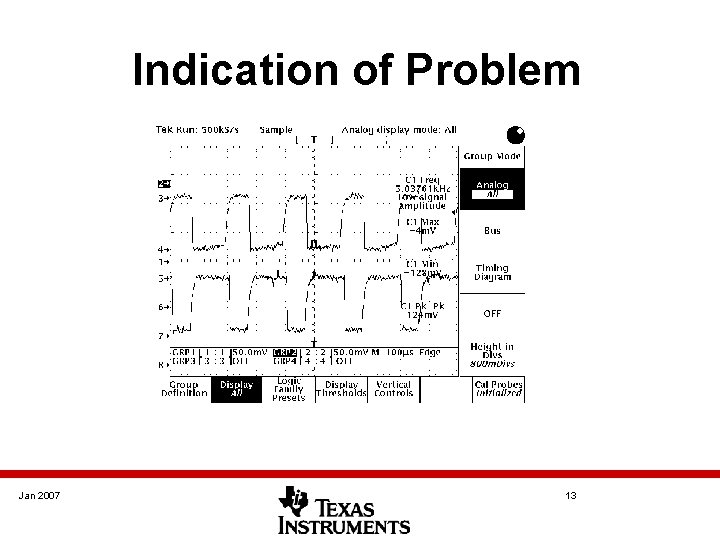

Indication of Problem Jan 2007 13

Indication of Problem • Module output voltages railed at start-up – Some triggered OVP and latched – ADJ sink current much higher than 6 m. A (18 m. A reported) at the instant of start up…it did settle out immediately – Some customers do not want their modules to be set at the max during start up – Oscillations also triggered during large and fast line or load transients Jan 2007 14

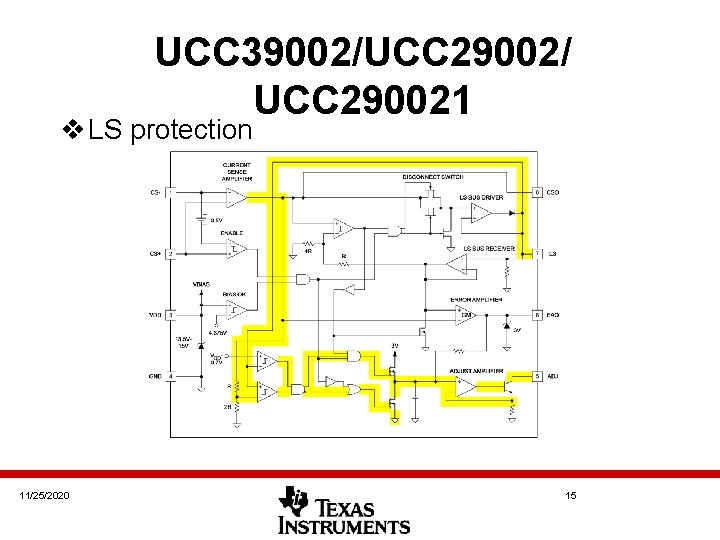

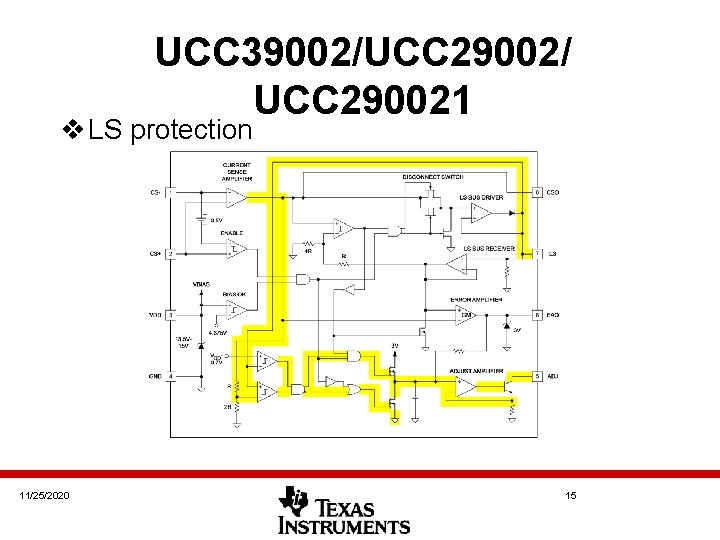

UCC 39002/UCC 29002/ UCC 290021 v LS protection 11/25/2020 15

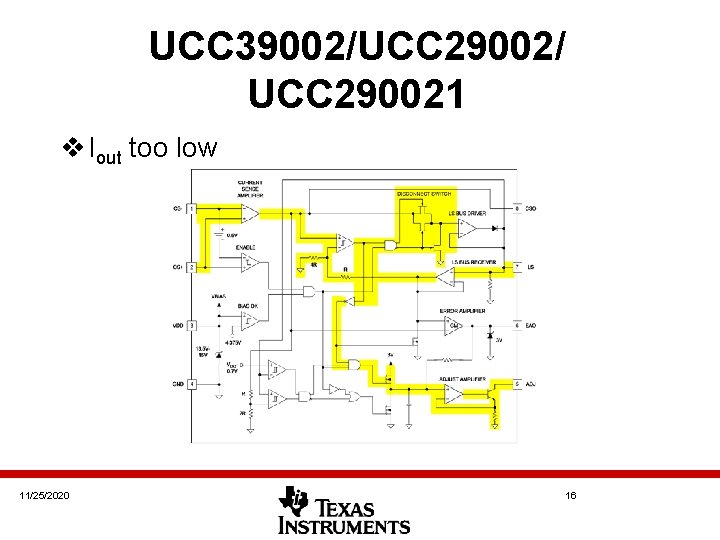

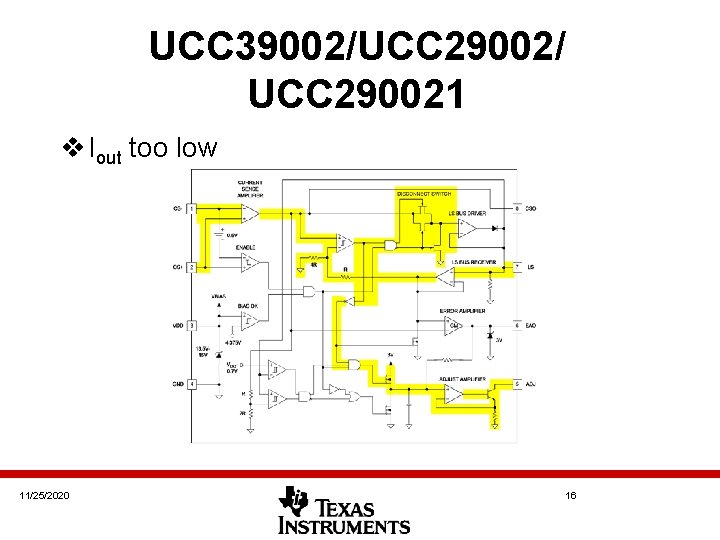

UCC 39002/UCC 29002/ UCC 290021 v Iout too low 11/25/2020 16

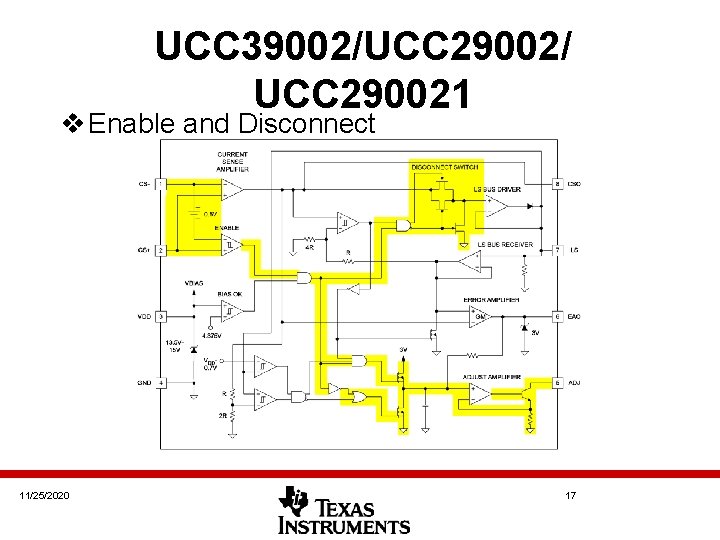

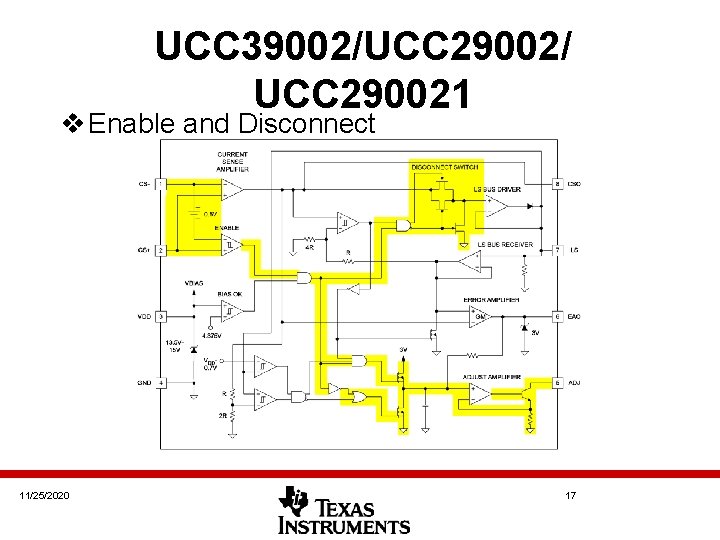

UCC 39002/UCC 29002/ UCC 290021 v Enable and Disconnect 11/25/2020 17

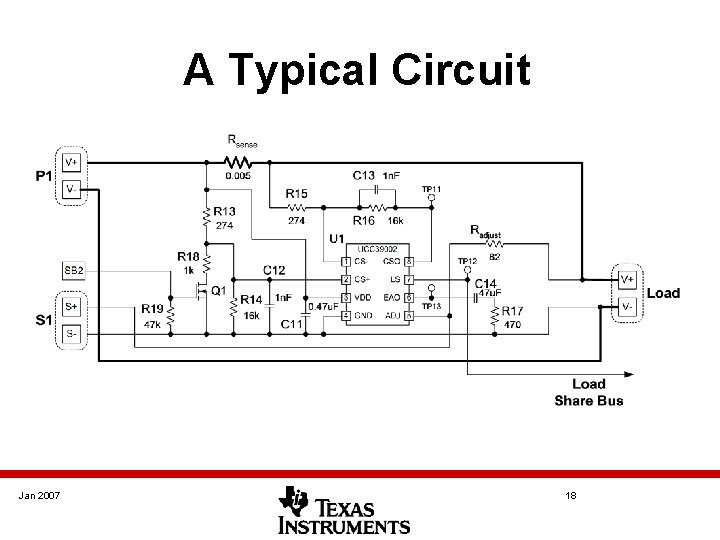

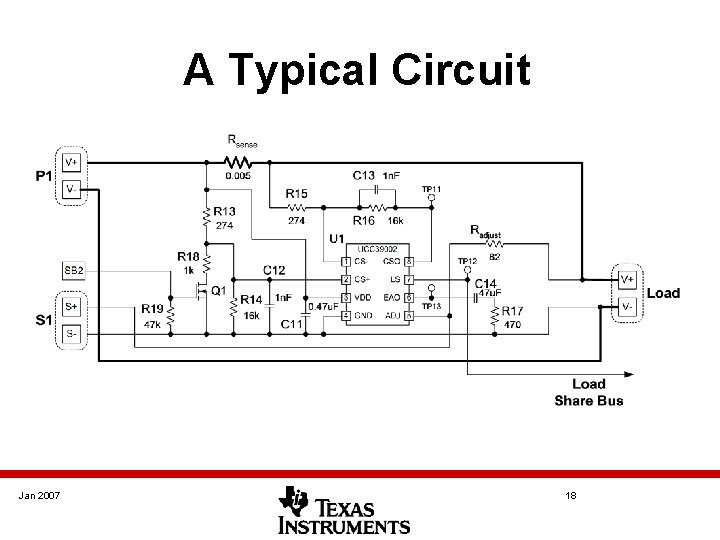

A Typical Circuit Jan 2007 18

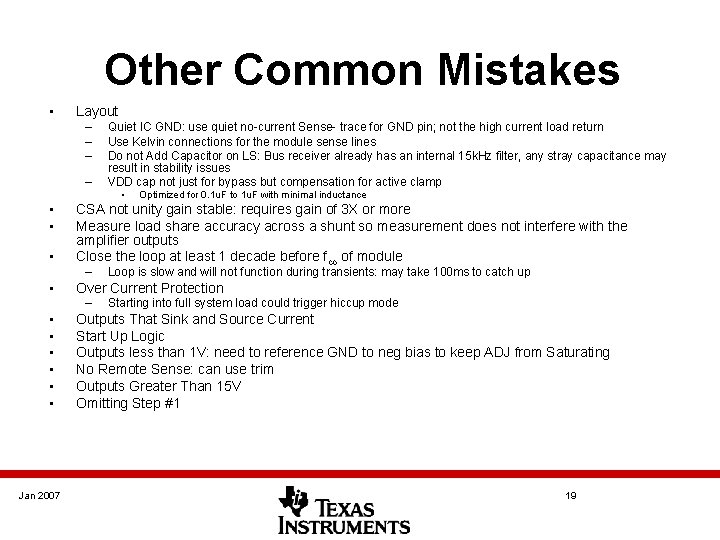

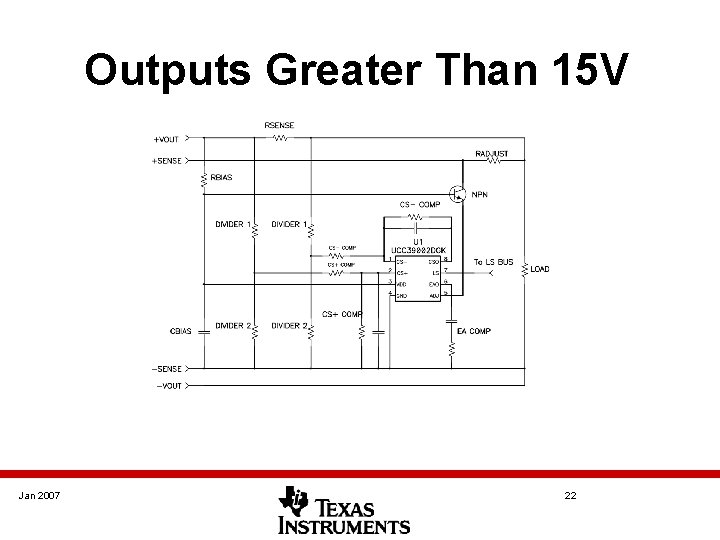

Other Common Mistakes • Layout – – Quiet IC GND: use quiet no-current Sense- trace for GND pin; not the high current load return Use Kelvin connections for the module sense lines Do not Add Capacitor on LS: Bus receiver already has an internal 15 k. Hz filter, any stray capacitance may result in stability issues VDD cap not just for bypass but compensation for active clamp • • CSA not unity gain stable: requires gain of 3 X or more Measure load share accuracy across a shunt so measurement does not interfere with the amplifier outputs Close the loop at least 1 decade before fco of module – • Jan 2007 Loop is slow and will not function during transients: may take 100 ms to catch up Over Current Protection – • • • Optimized for 0. 1 u. F to 1 u. F with minimal inductance Starting into full system load could trigger hiccup mode Outputs That Sink and Source Current Start Up Logic Outputs less than 1 V: need to reference GND to neg bias to keep ADJ from Saturating No Remote Sense: can use trim Outputs Greater Than 15 V Omitting Step #1 19

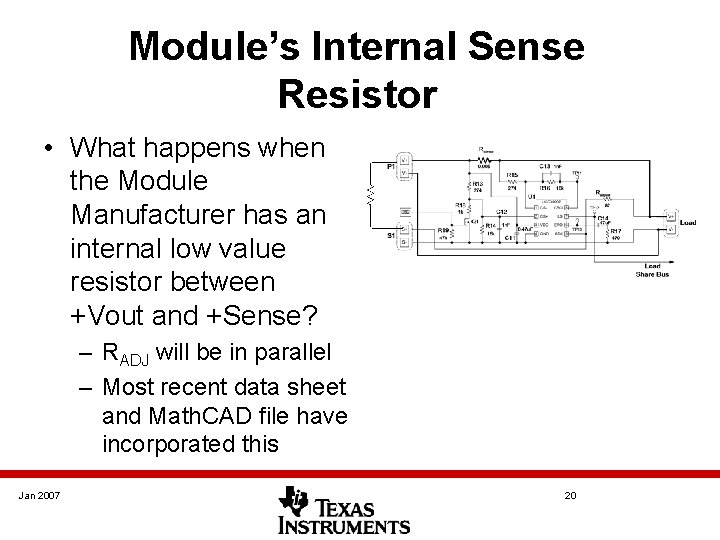

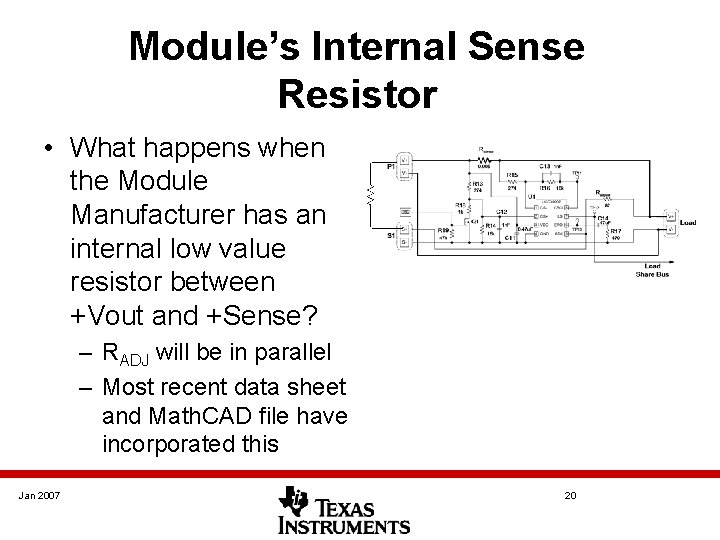

Module’s Internal Sense Resistor • What happens when the Module Manufacturer has an internal low value resistor between +Vout and +Sense? – RADJ will be in parallel – Most recent data sheet and Math. CAD file have incorporated this Jan 2007 20

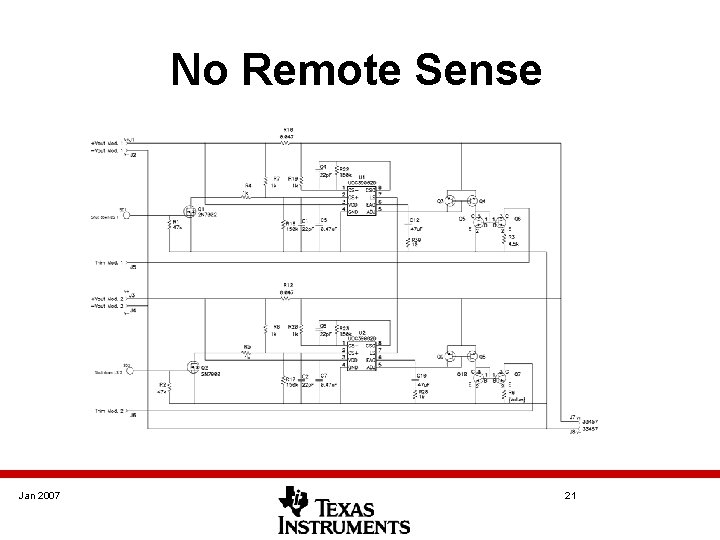

No Remote Sense Jan 2007 21

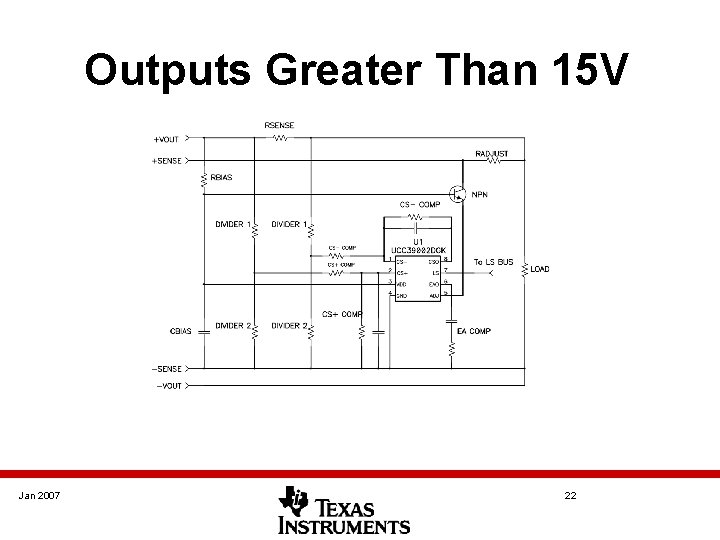

Outputs Greater Than 15 V Jan 2007 22

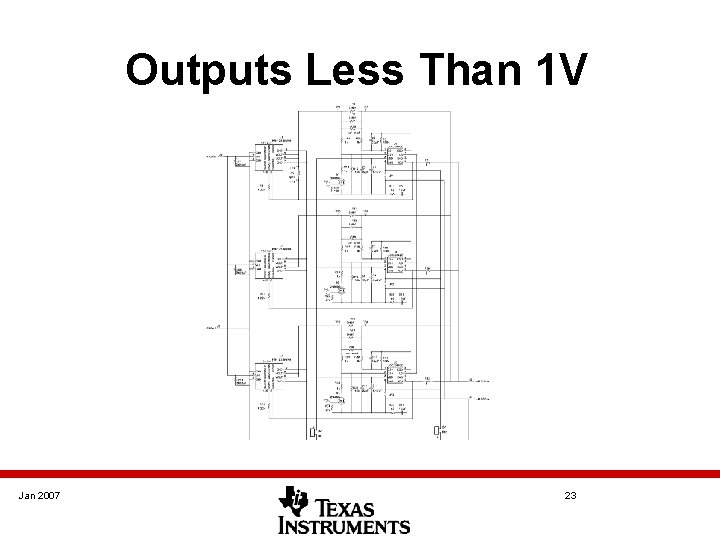

Outputs Less Than 1 V Jan 2007 23

Load Share Resources • EVM: – HPA 027 A • Board has three controllers on it • Reference designators left unpopulated so the Customer can customize for their specific application • Math. CAD File in the Tools and Software Section of the Product Folder • Step by step user-interactive – The Bode plot of the module must be re-created by the user Jan 2007 24