Advance encryption Standard VHDL implementation Florida International University

- Slides: 27

Advance encryption Standard VHDL implementation Florida International University Department of Electrical and Computer Engineering Fall 2003 By Wilson Luengas Richard Zavaleta Luis Gonzalez 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

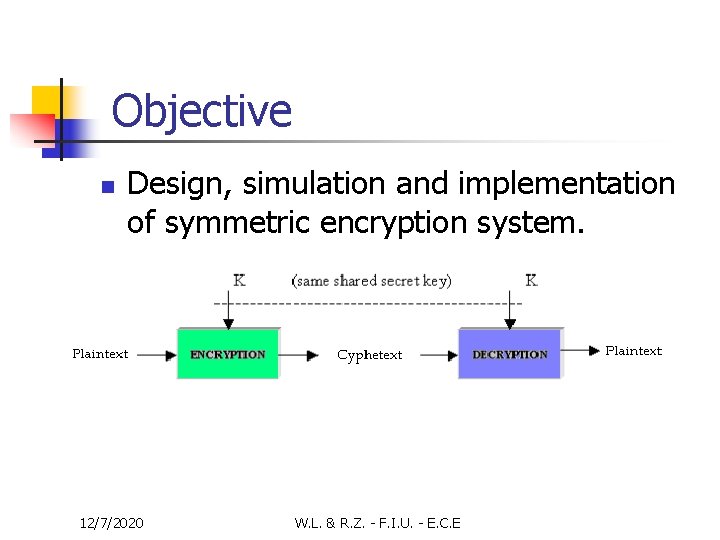

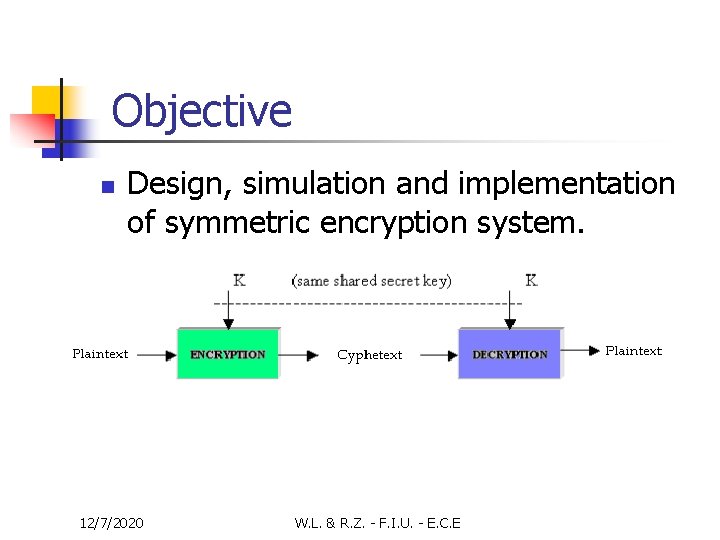

Objective n Design, simulation and implementation of symmetric encryption system. 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

Importance of Data and Network Security n n Interception, modification or destruction of sensitive data may cause great personal and financial distress. Popularity of online transactions and digital storage. 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

Data and network security limitations n There is no 100% secured networks. n n n 12/7/2020 Attackers may be hackers or disgruntled employees. Breach of security may be due to negligence of employees or absence of security policy. New viruses are created all the time. W. L. & R. Z. - F. I. U. - E. C. E

Advance Encryption Standard (AES) n n NIST chose the Rijndael algorithm as its AES standard in 2001 [1]. No known security attacks. It can be implemented in 8 -bits, 64 -bits platforms, and DSP. Low RAM and ROM requirement. 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

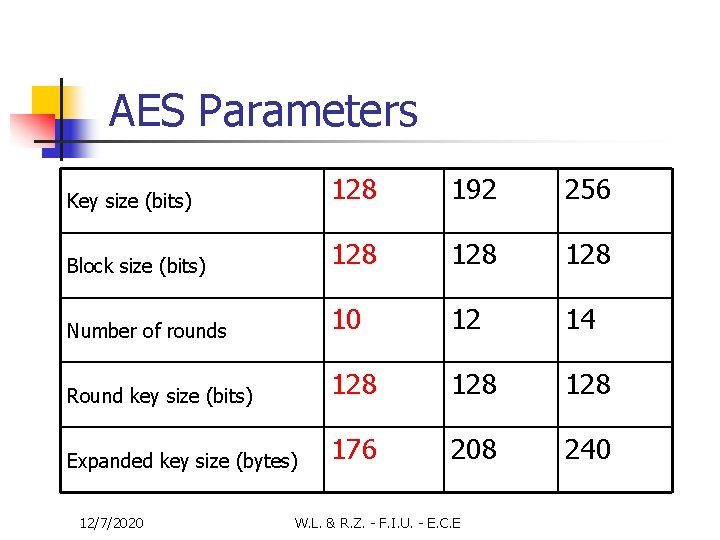

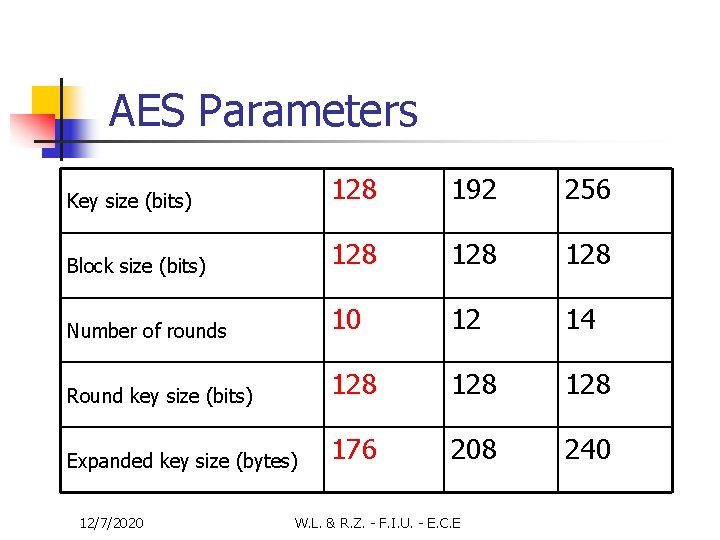

AES Parameters Key size (bits) 128 192 256 Block size (bits) 128 128 Number of rounds 10 12 14 Round key size (bits) 128 128 Expanded key size (bytes) 176 208 240 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

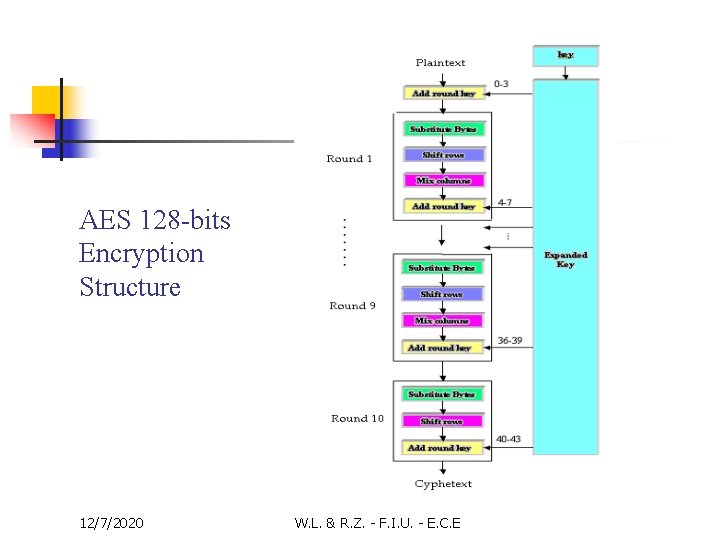

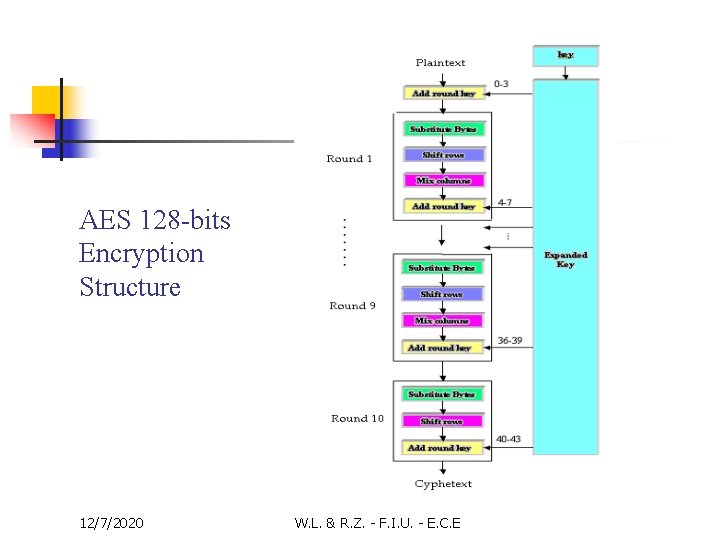

AES 128 -bits Encryption Structure 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

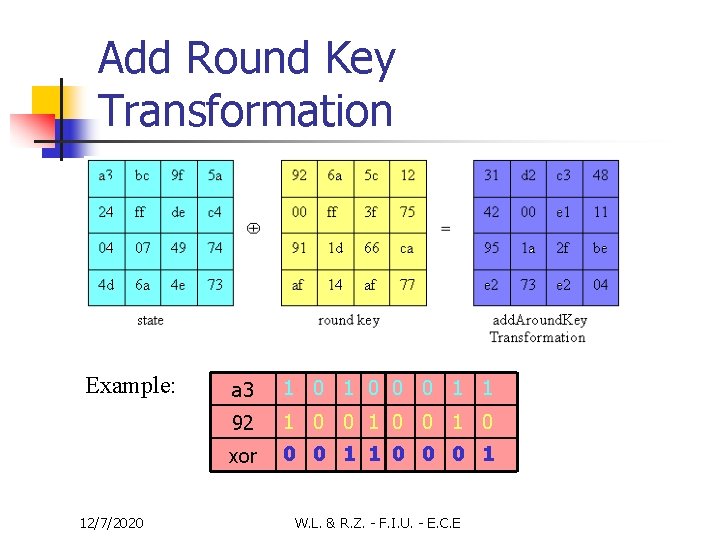

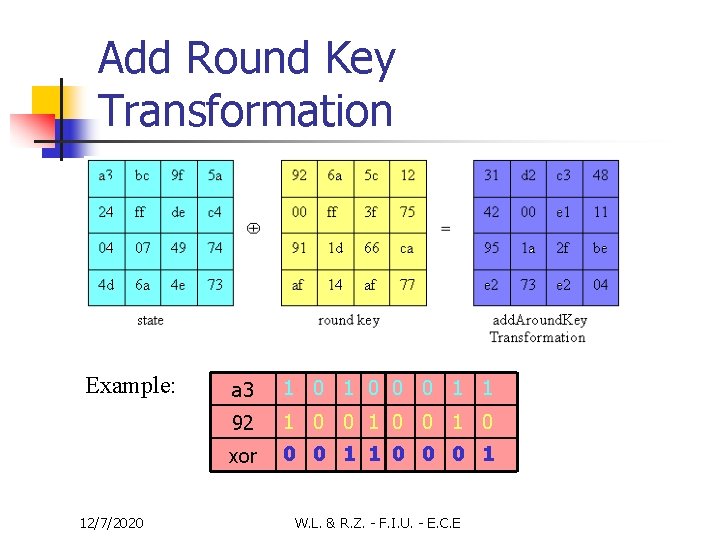

Add Round Key Transformation Example: 12/7/2020 a 3 1 0 0 0 1 1 92 1 0 0 1 0 xor 0 0 1 1 0 0 0 1 W. L. & R. Z. - F. I. U. - E. C. E

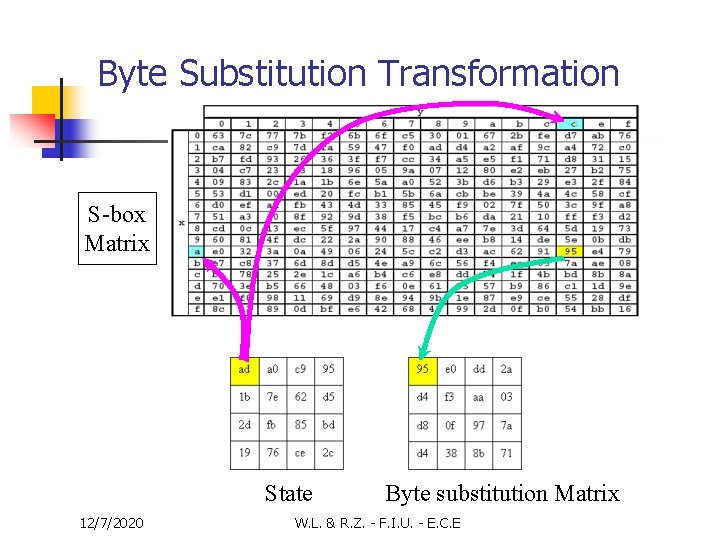

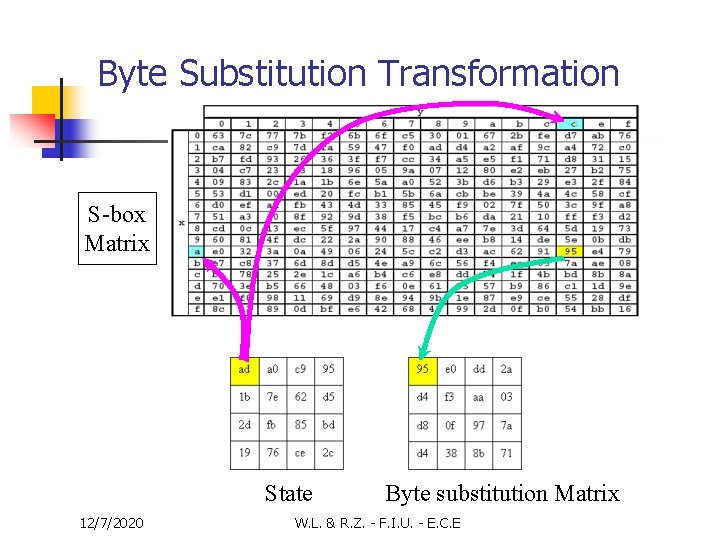

Byte Substitution Transformation S-box Matrix State 12/7/2020 Byte substitution Matrix W. L. & R. Z. - F. I. U. - E. C. E

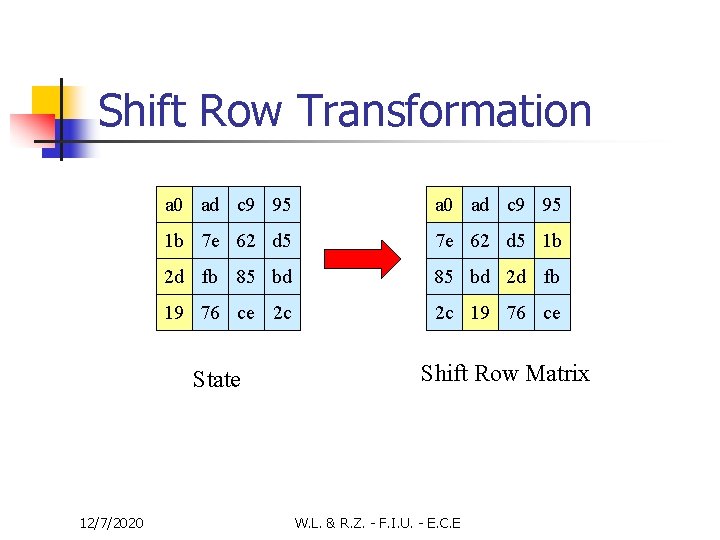

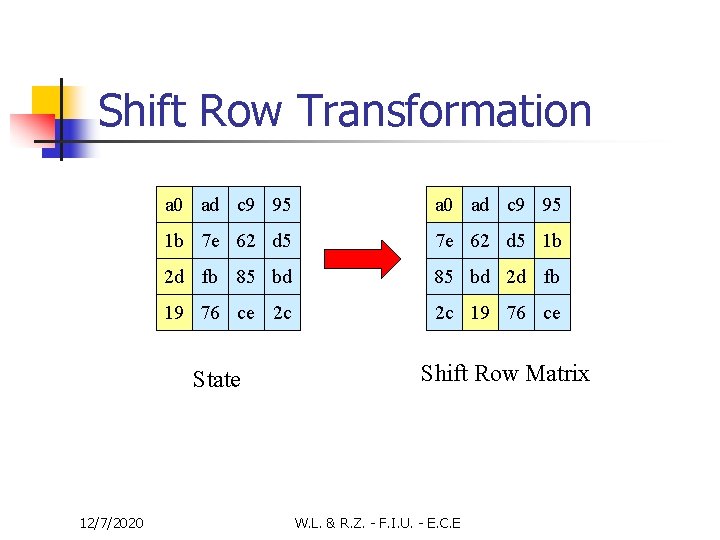

Shift Row Transformation a 0 ad c 9 95 1 b 7 e 62 d 5 1 b 2 d fb 85 bd 2 d fb 19 76 ce 2 c 2 c 19 76 ce State 12/7/2020 Shift Row Matrix W. L. & R. Z. - F. I. U. - E. C. E

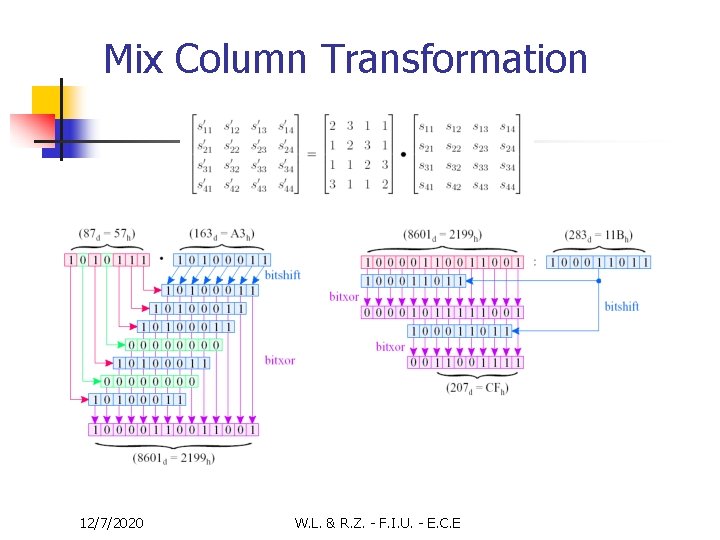

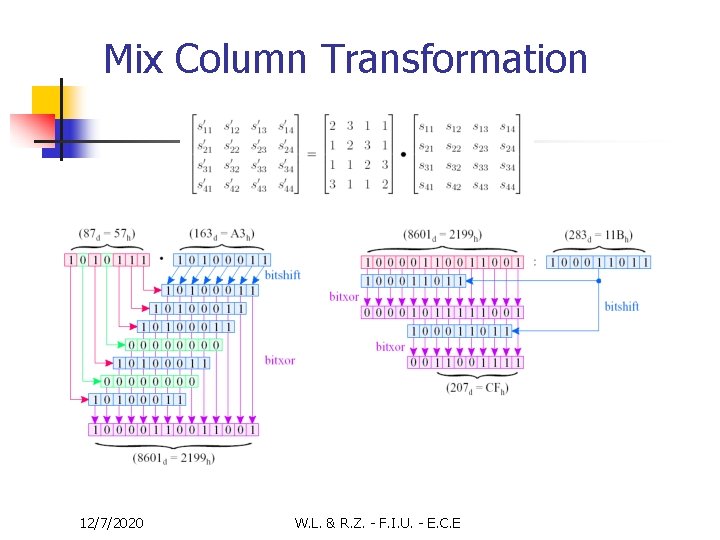

Mix Column Transformation 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

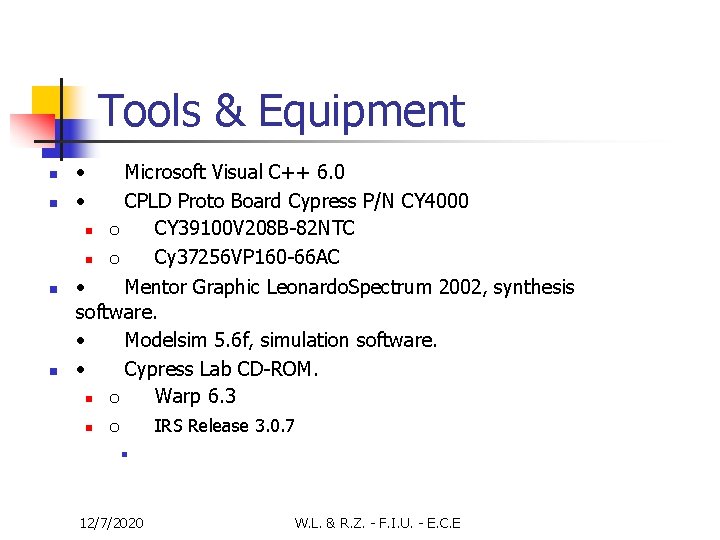

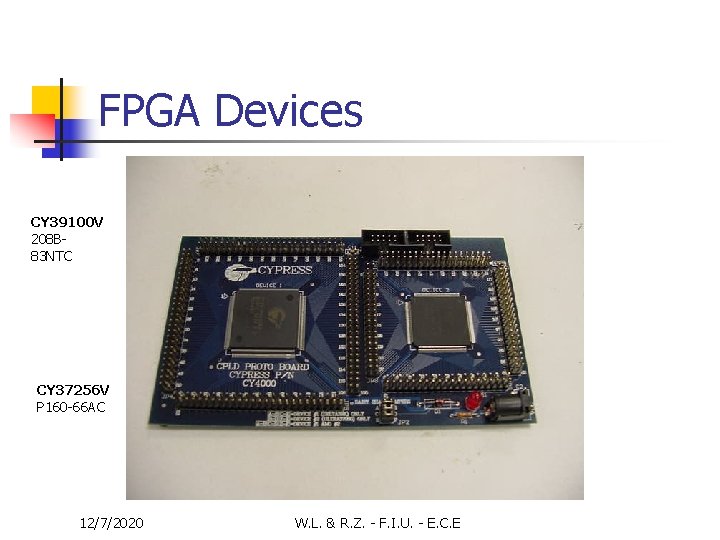

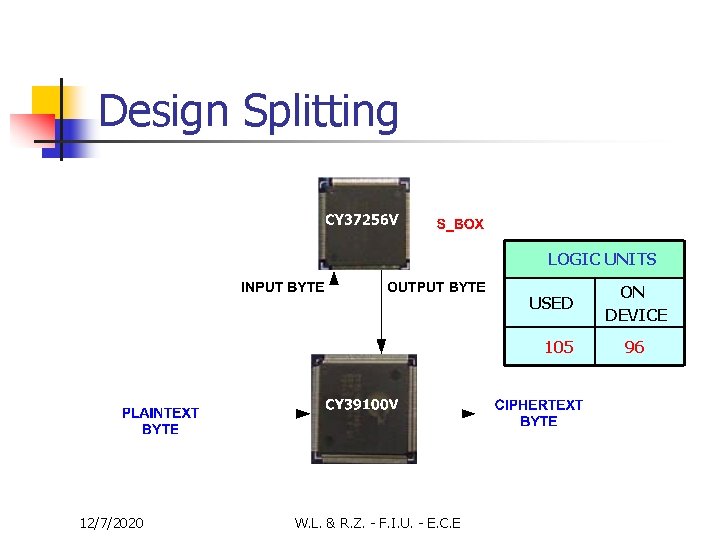

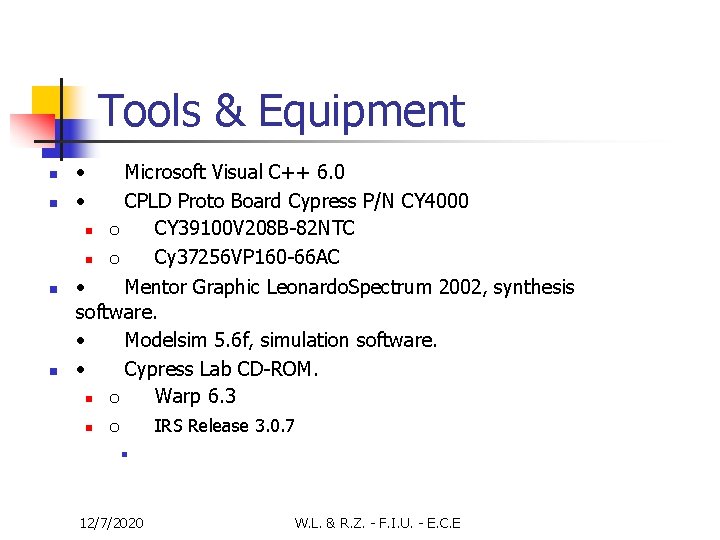

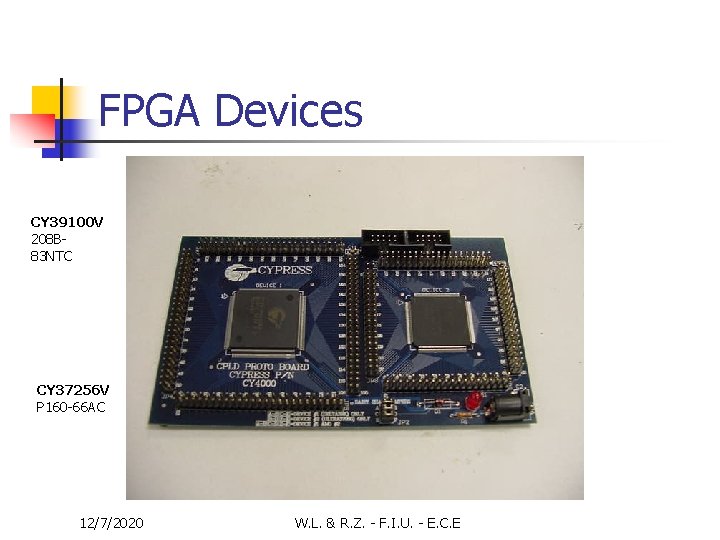

Tools & Equipment n n · Microsoft Visual C++ 6. 0 · CPLD Proto Board Cypress P/N CY 4000 n o CY 39100 V 208 B-82 NTC n o Cy 37256 VP 160 -66 AC · Mentor Graphic Leonardo. Spectrum 2002, synthesis software. · Modelsim 5. 6 f, simulation software. · Cypress Lab CD-ROM. n o Warp 6. 3 n o IRS Release 3. 0. 7 n 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

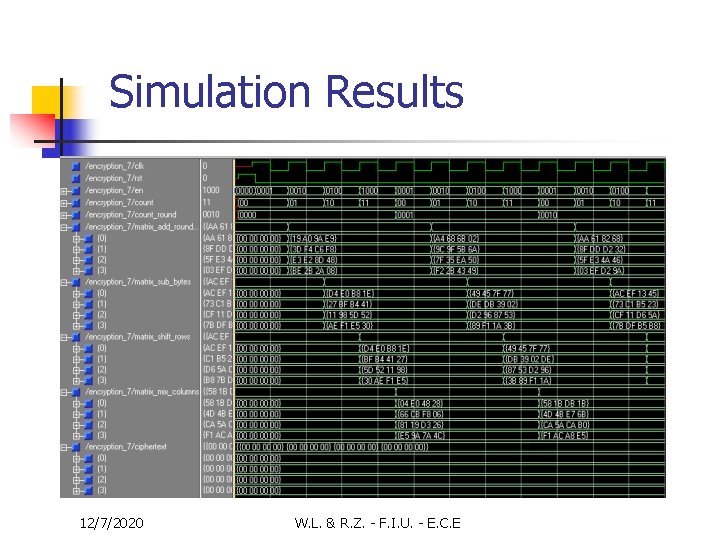

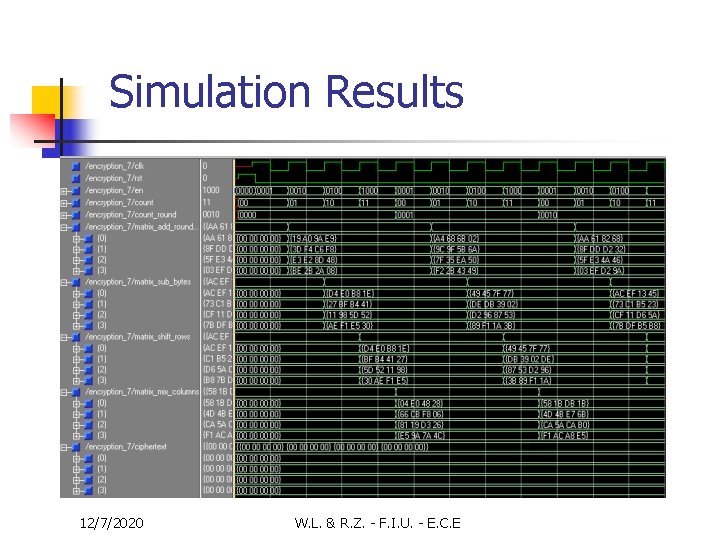

Simulation Results 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

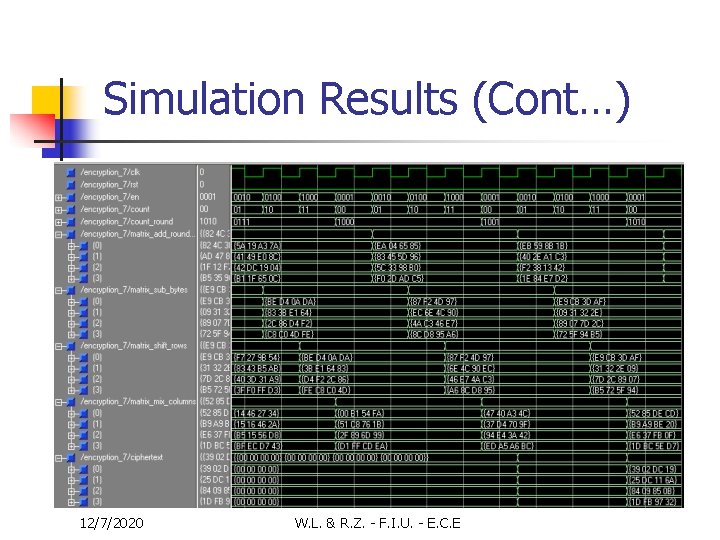

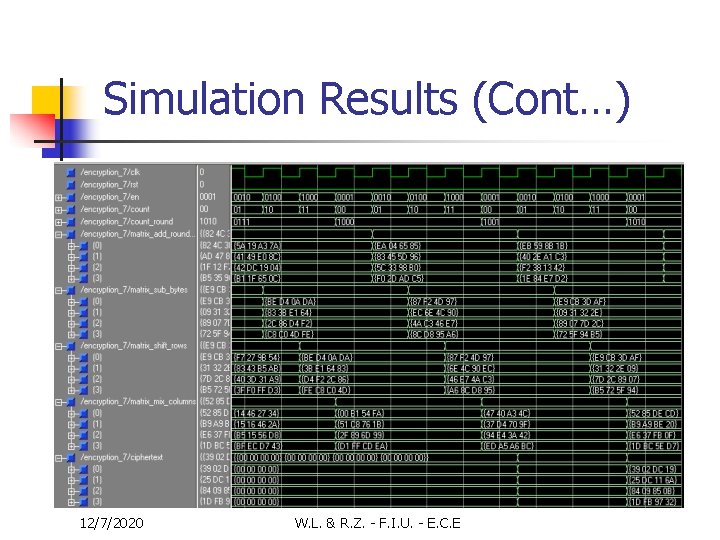

Simulation Results (Cont…) 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

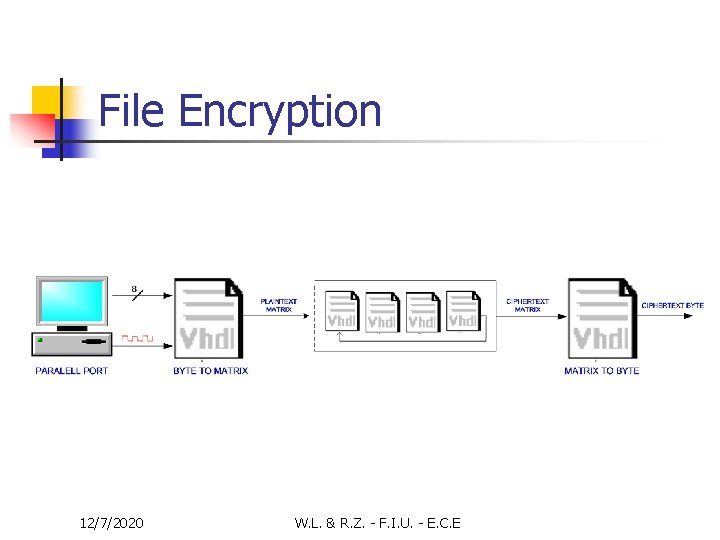

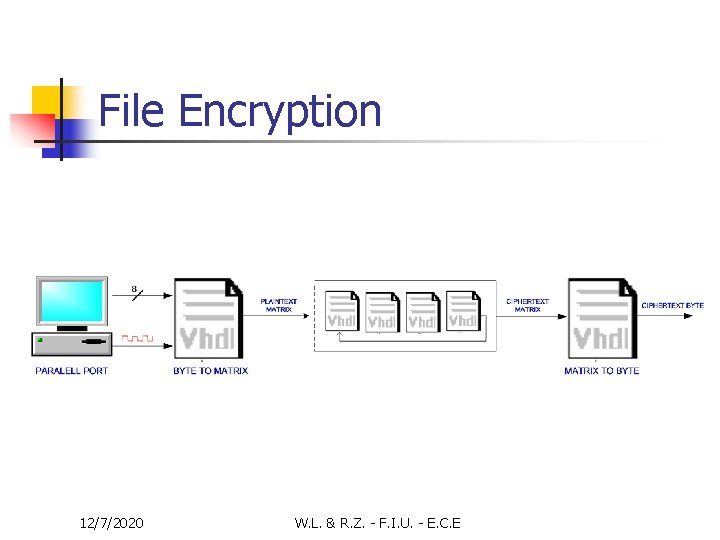

File Encryption 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

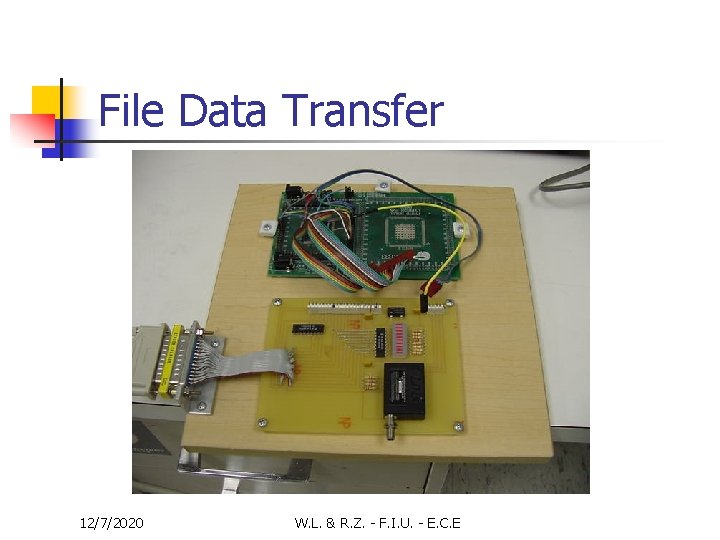

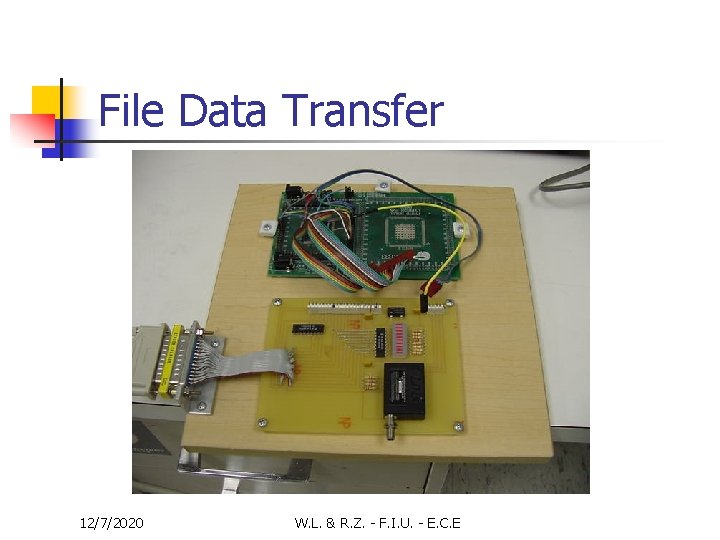

File Data Transfer 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

FPGA Devices CY 39100 V 208 B 83 NTC CY 37256 V P 160 -66 AC 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

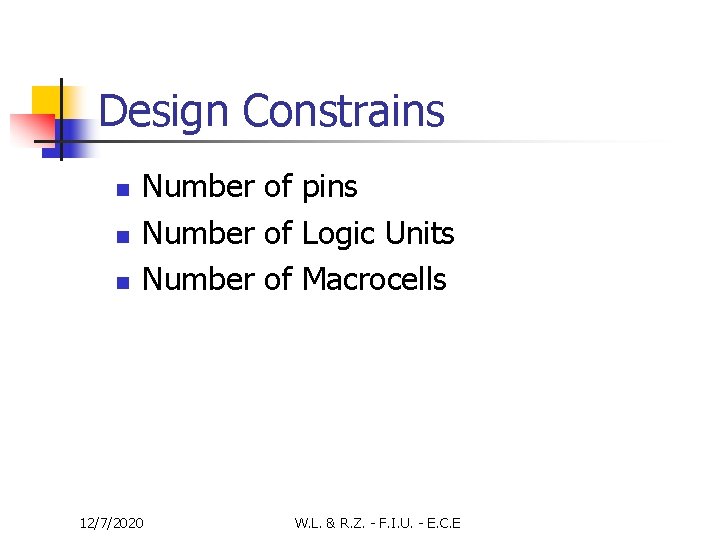

Design Constrains n n n Number of pins Number of Logic Units Number of Macrocells 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

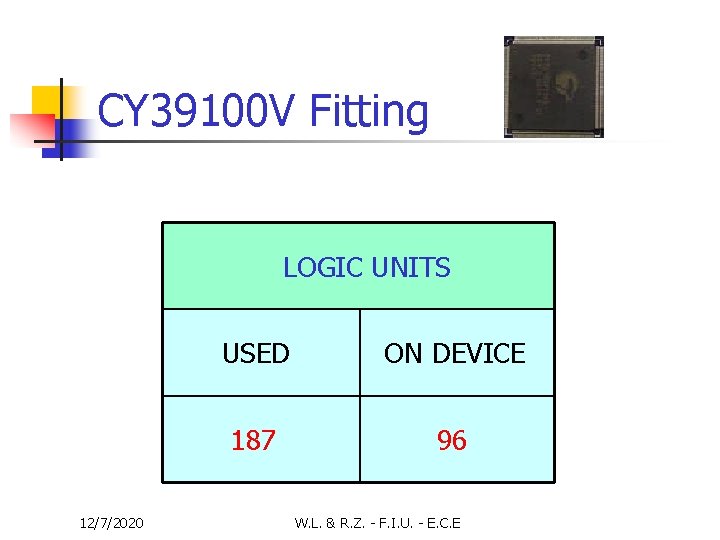

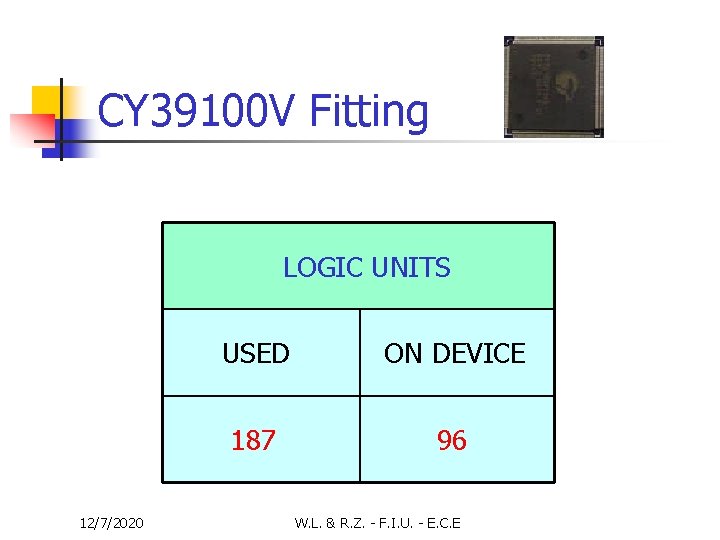

CY 39100 V Fitting LOGIC UNITS 12/7/2020 USED ON DEVICE 187 96 W. L. & R. Z. - F. I. U. - E. C. E

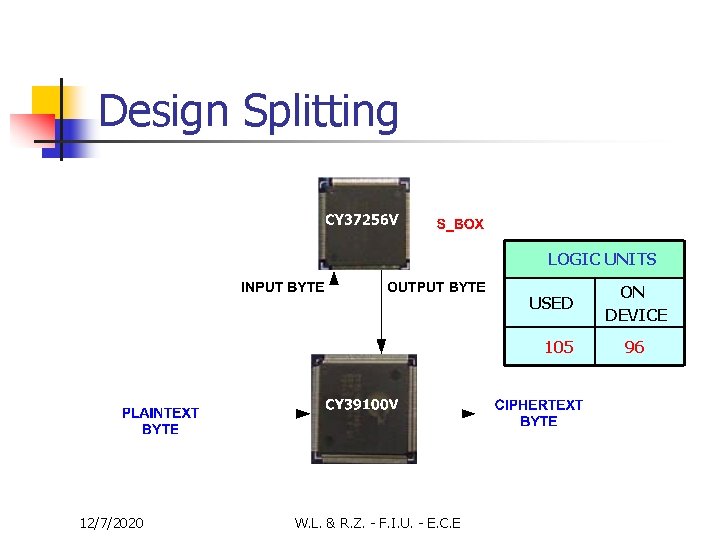

Design Splitting LOGIC UNITS USED 105 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E ON DEVICE 96

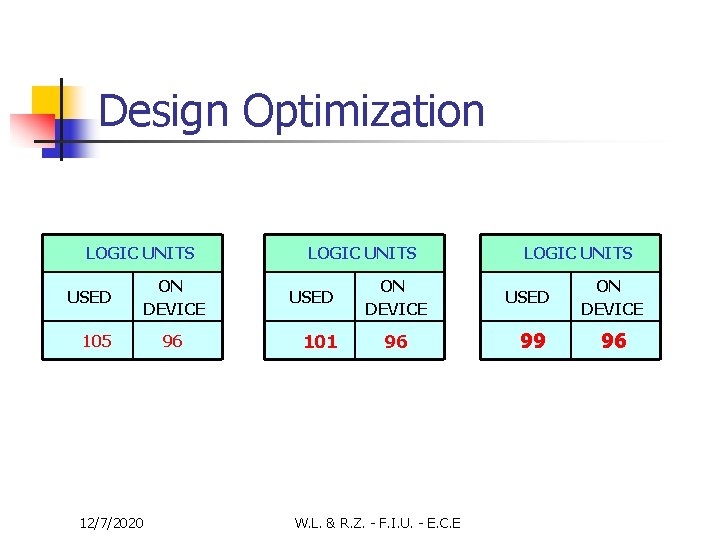

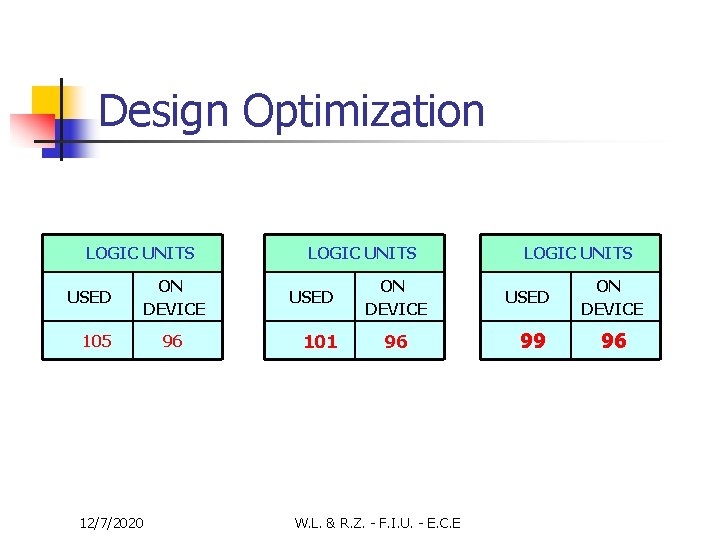

Design Optimization LOGIC UNITS USED 105 12/7/2020 ON DEVICE 96 LOGIC UNITS USED 101 ON DEVICE 96 W. L. & R. Z. - F. I. U. - E. C. E LOGIC UNITS USED 99 ON DEVICE 96

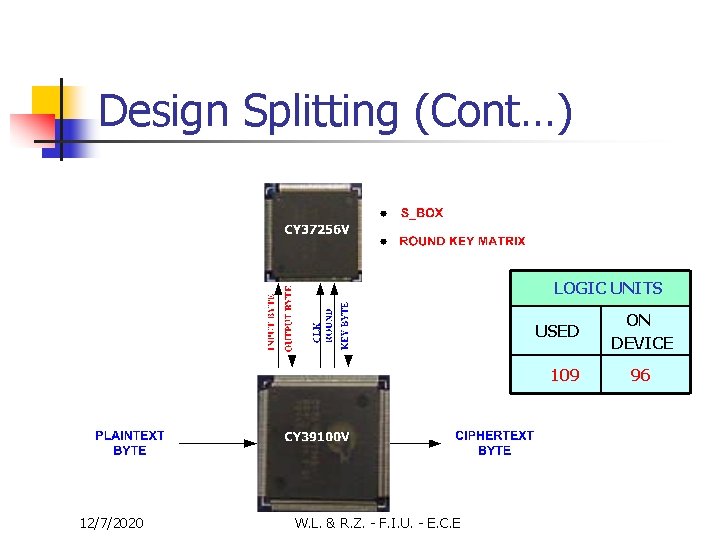

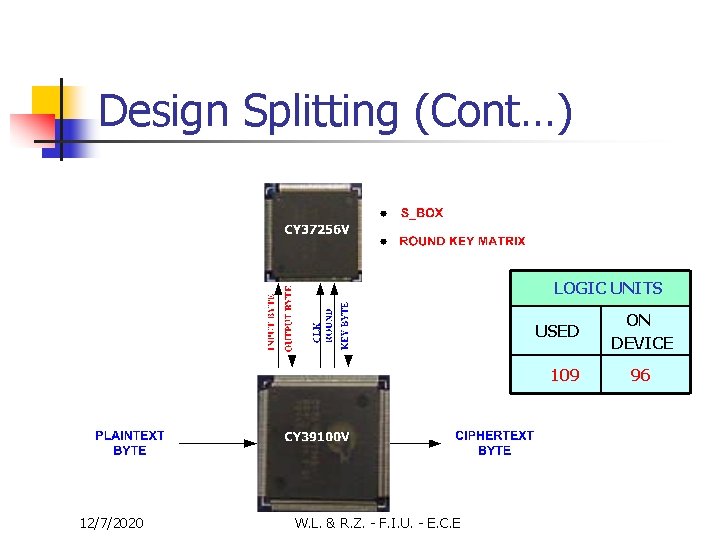

Design Splitting (Cont…) LOGIC UNITS USED 109 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E ON DEVICE 96

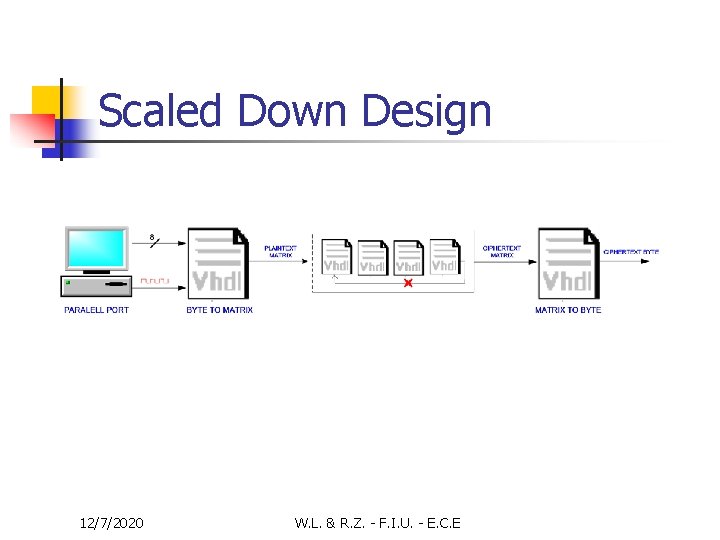

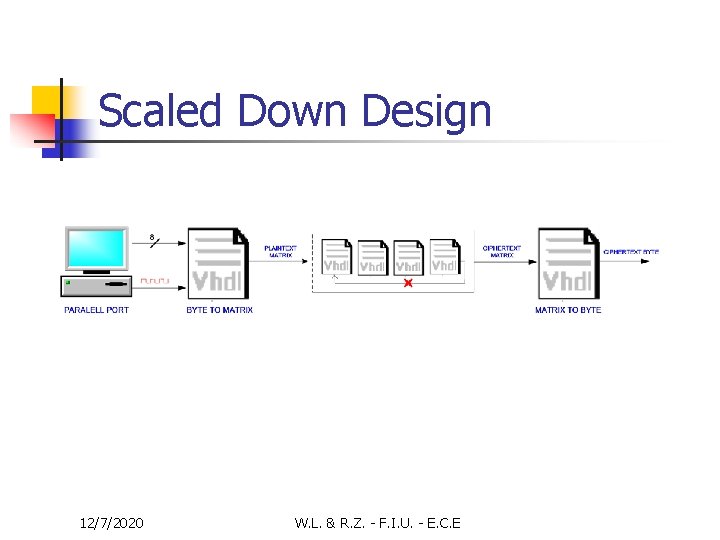

Scaled Down Design 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

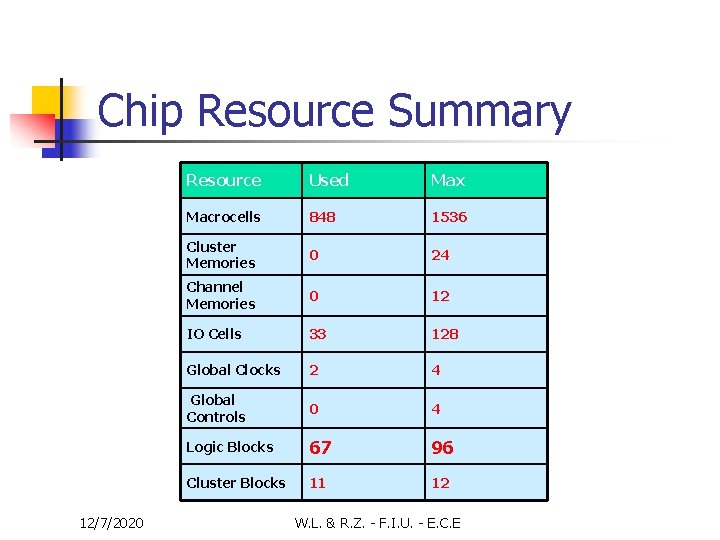

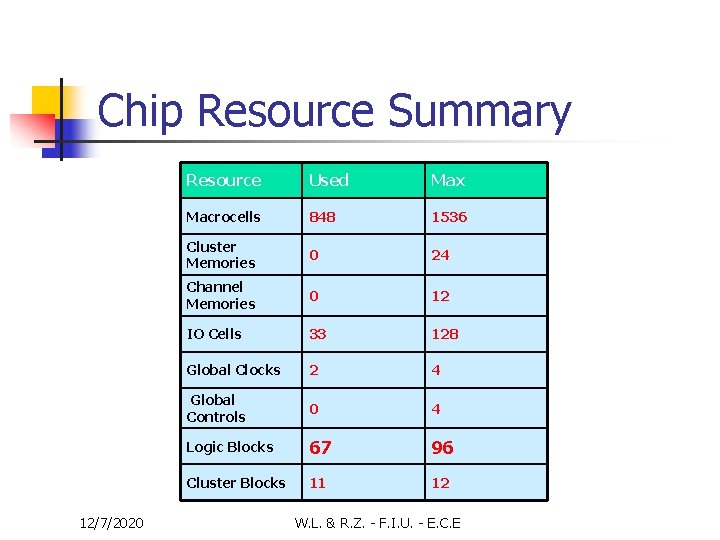

Chip Resource Summary 12/7/2020 Resource Used Max Macrocells 848 1536 Cluster Memories 0 24 Channel Memories 0 12 IO Cells 33 128 Global Clocks 2 4 Global Controls 0 4 Logic Blocks 67 96 Cluster Blocks 11 12 W. L. & R. Z. - F. I. U. - E. C. E

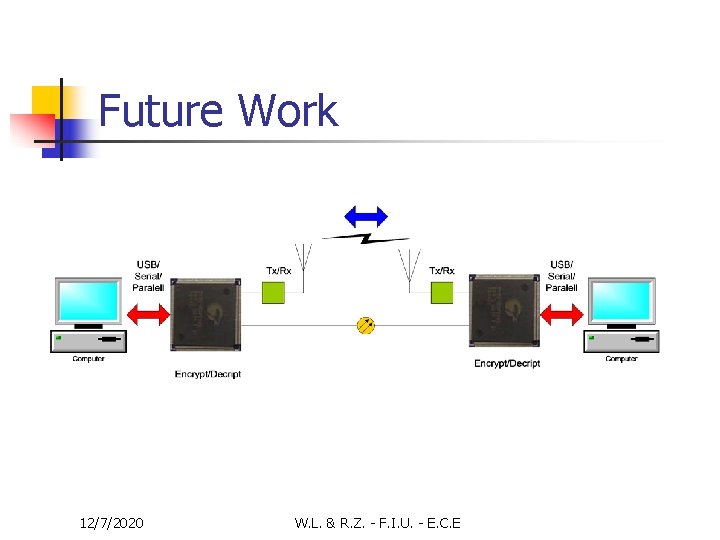

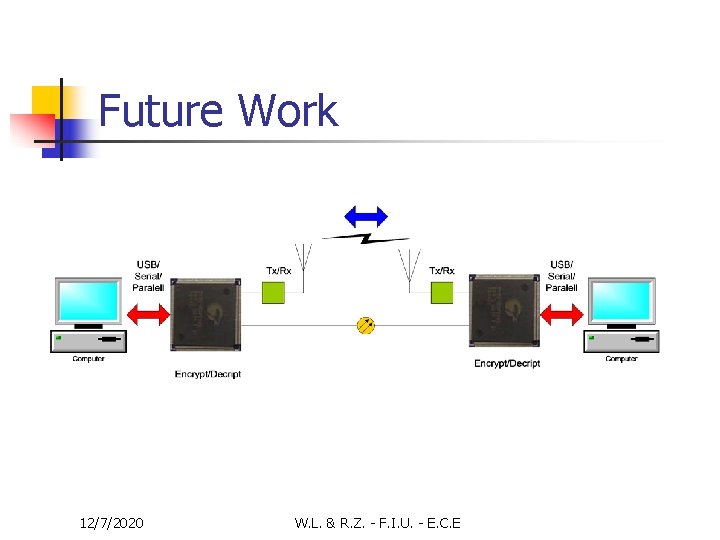

Future Work 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

Conclusions n n n Knowledge of devices resources. Difference between simulation software and synthesis software. Difference between synthesis softwares. Knowledge of synthesis algorithms. Divide and conquer approach. Use full development kit. 12/7/2020 W. L. & R. Z. - F. I. U. - E. C. E

References 1. 2. 12/7/2020 National Institute of Standards and Technology. Specifications for the Advanced Encryption Standard (AES), http: //csrc. nist. gov/publications/fips 97/fips-197. pdf, (2001). J. J. Buchhloz, Advanced Encryption Standard, http: //buchholz. hsbremen. de, Dec. 2001. W. L. & R. Z. - F. I. U. - E. C. E