Addressing mode summary 2152022 Instruction encoding 1 Issues

- Slides: 13

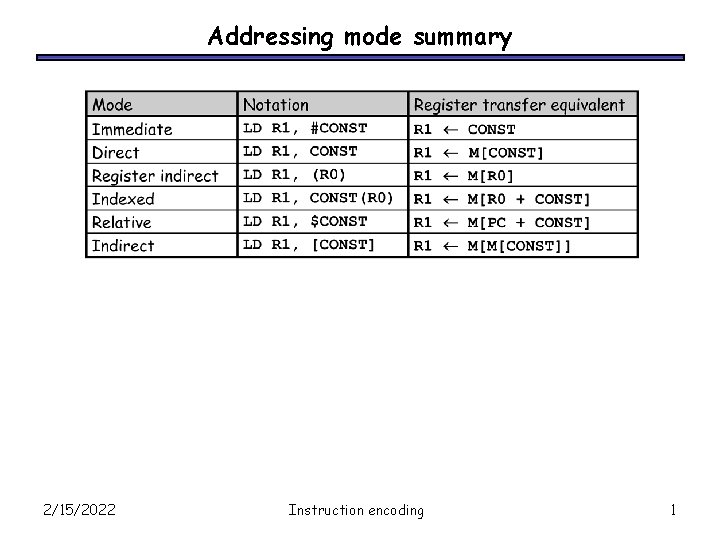

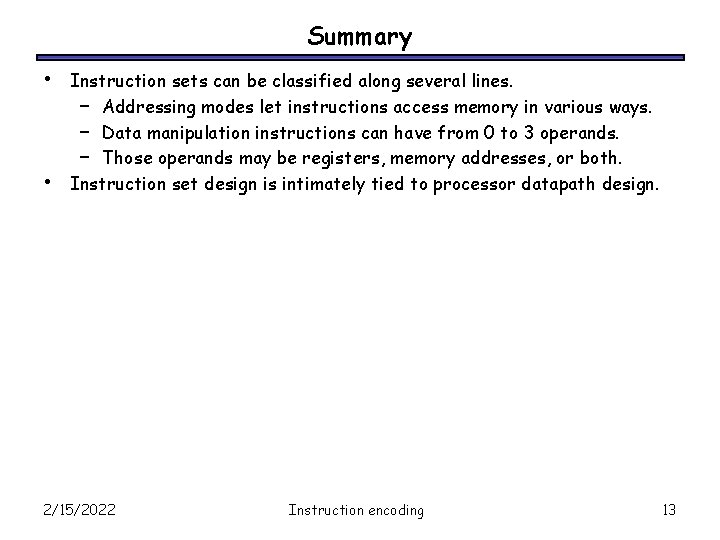

Addressing mode summary 2/15/2022 Instruction encoding 1

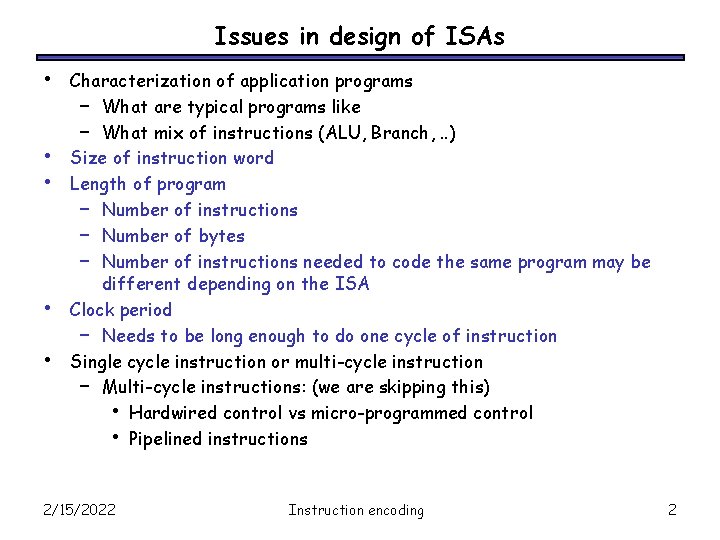

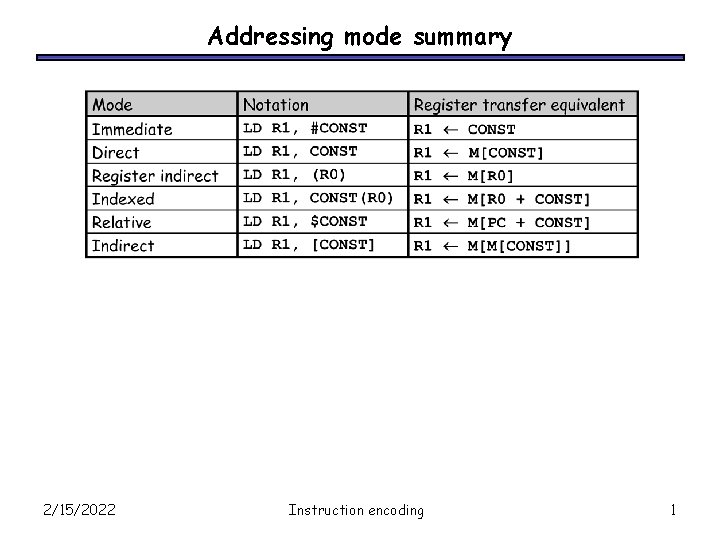

Issues in design of ISAs • • • Characterization of application programs – What are typical programs like – What mix of instructions (ALU, Branch, . . ) Size of instruction word Length of program – Number of instructions – Number of bytes – Number of instructions needed to code the same program may be different depending on the ISA Clock period – Needs to be long enough to do one cycle of instruction Single cycle instruction or multi-cycle instruction – Multi-cycle instructions: (we are skipping this) • Hardwired control vs micro-programmed control • Pipelined instructions 2/15/2022 Instruction encoding 2

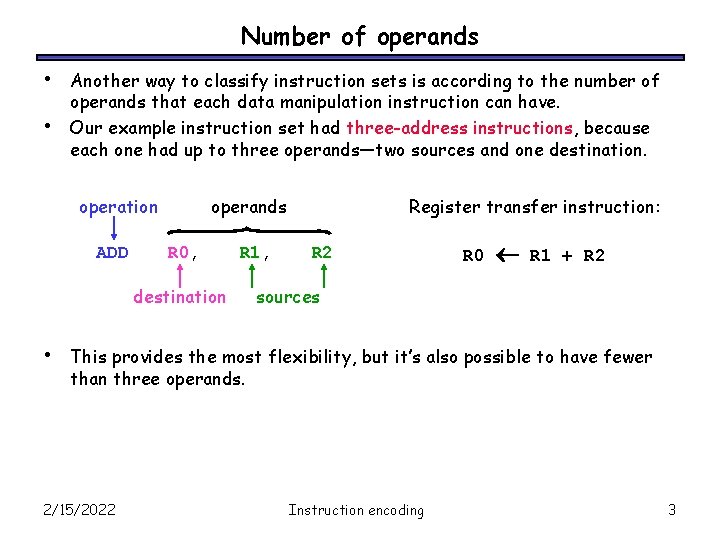

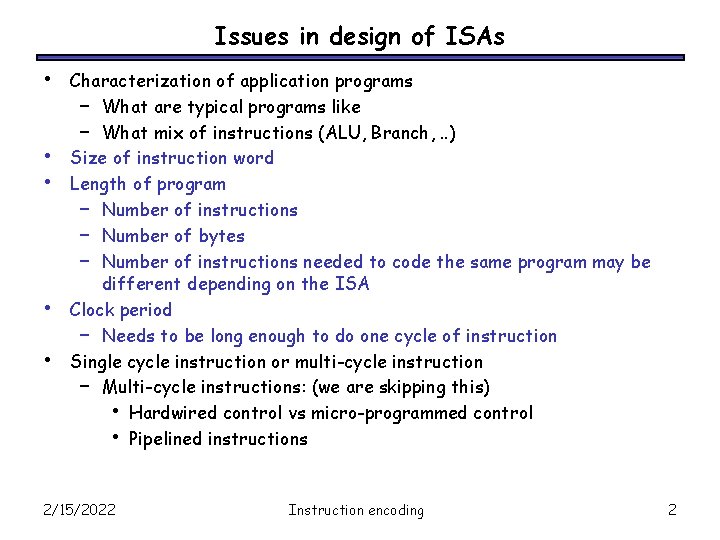

Number of operands • • Another way to classify instruction sets is according to the number of operands that each data manipulation instruction can have. Our example instruction set had three-address instructions, because each one had up to three operands—two sources and one destination. operation ADD operands R 0, destination • R 1, Register transfer instruction: R 2 R 0 R 1 + R 2 sources This provides the most flexibility, but it’s also possible to have fewer than three operands. 2/15/2022 Instruction encoding 3

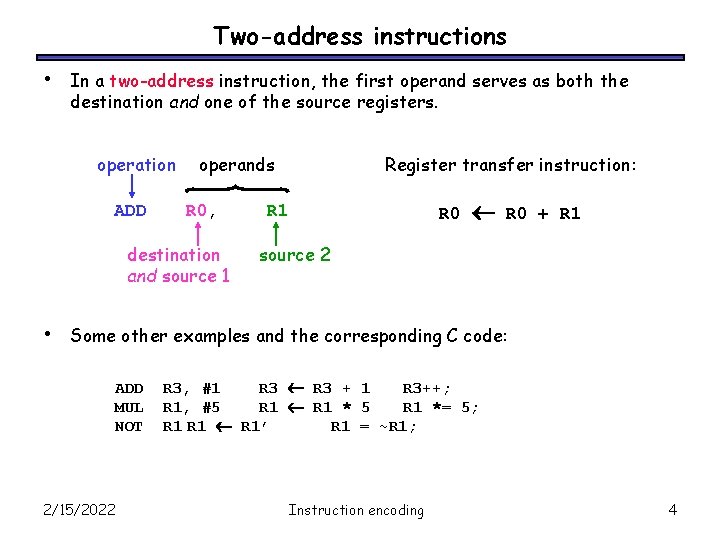

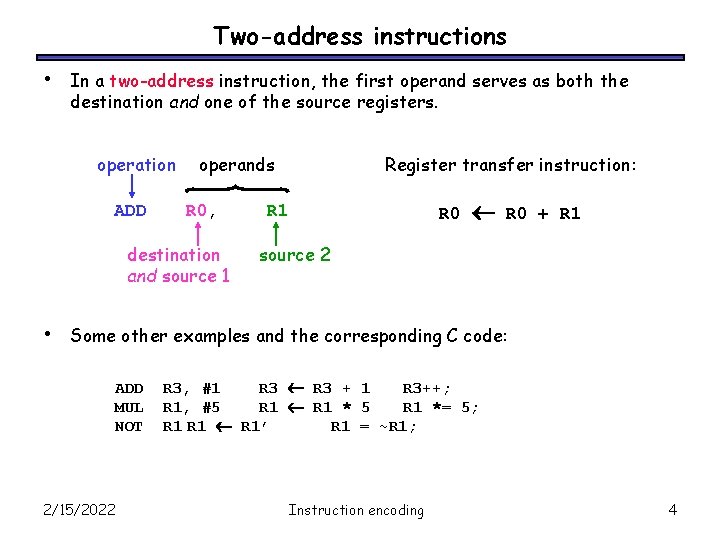

Two-address instructions • In a two-address instruction, the first operand serves as both the destination and one of the source registers. operation ADD operands R 0, destination and source 1 • Register transfer instruction: R 1 R 0 + R 1 source 2 Some other examples and the corresponding C code: ADD MUL NOT 2/15/2022 R 3, #1 R 3 + 1 R 3++; R 1, #5 R 1 *= 5; R 1’ R 1 = ~R 1; Instruction encoding 4

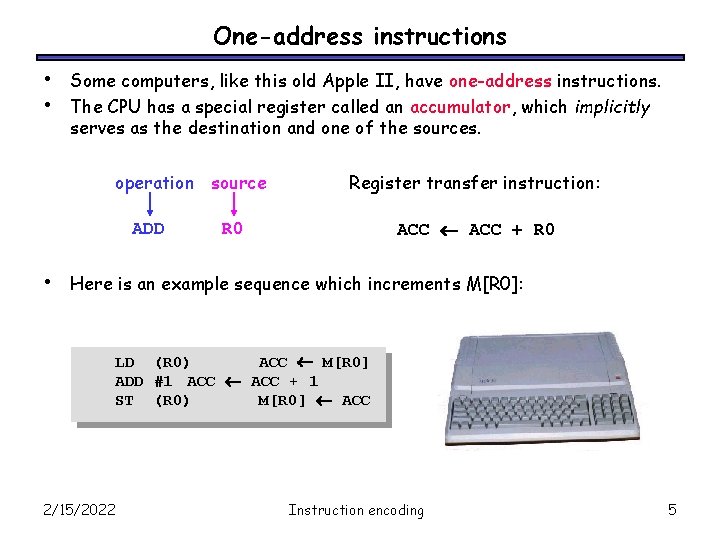

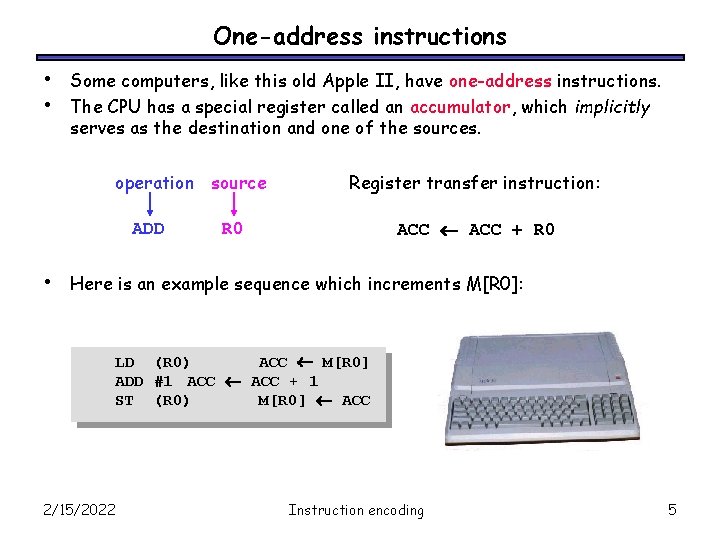

One-address instructions • • Some computers, like this old Apple II, have one-address instructions. The CPU has a special register called an accumulator, which implicitly serves as the destination and one of the sources. operation source ADD • Register transfer instruction: ACC + R 0 Here is an example sequence which increments M[R 0]: LD (R 0) ACC M[R 0] ADD #1 ACC + 1 ST (R 0) M[R 0] ACC 2/15/2022 Instruction encoding 5

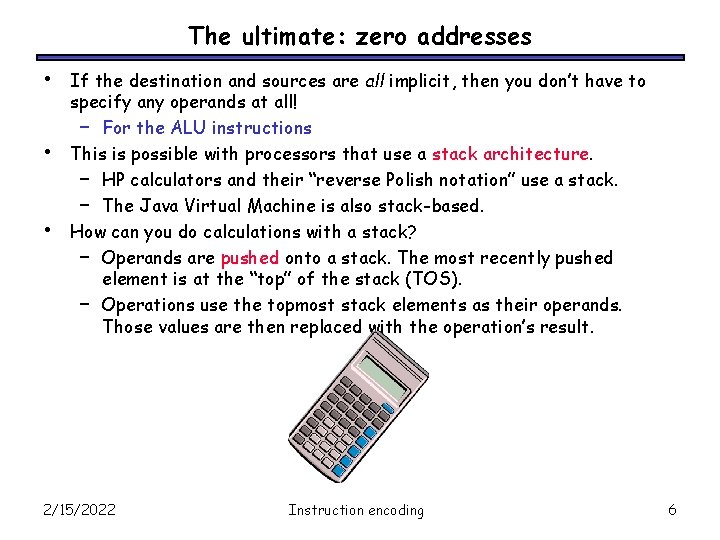

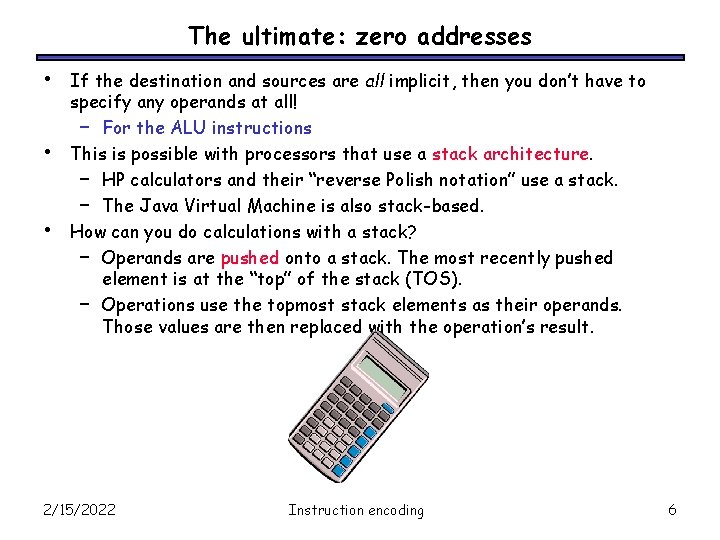

The ultimate: zero addresses • • • If the destination and sources are all implicit, then you don’t have to specify any operands at all! – For the ALU instructions This is possible with processors that use a stack architecture. – HP calculators and their “reverse Polish notation” use a stack. – The Java Virtual Machine is also stack-based. How can you do calculations with a stack? – Operands are pushed onto a stack. The most recently pushed element is at the “top” of the stack (TOS). – Operations use the topmost stack elements as their operands. Those values are then replaced with the operation’s result. 2/15/2022 Instruction encoding 6

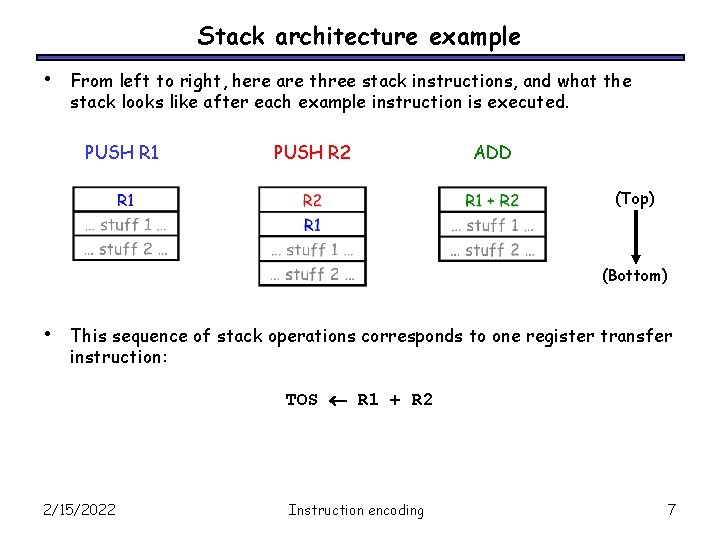

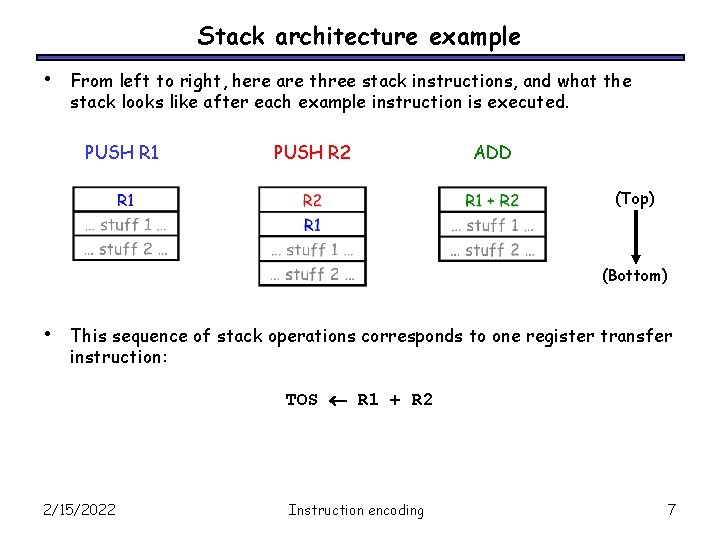

Stack architecture example • From left to right, here are three stack instructions, and what the stack looks like after each example instruction is executed. PUSH R 1 PUSH R 2 ADD (Top) (Bottom) • This sequence of stack operations corresponds to one register transfer instruction: TOS R 1 + R 2 2/15/2022 Instruction encoding 7

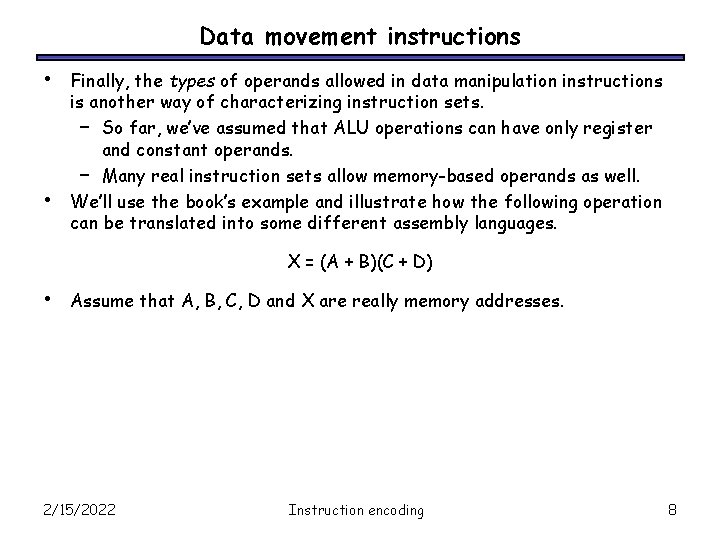

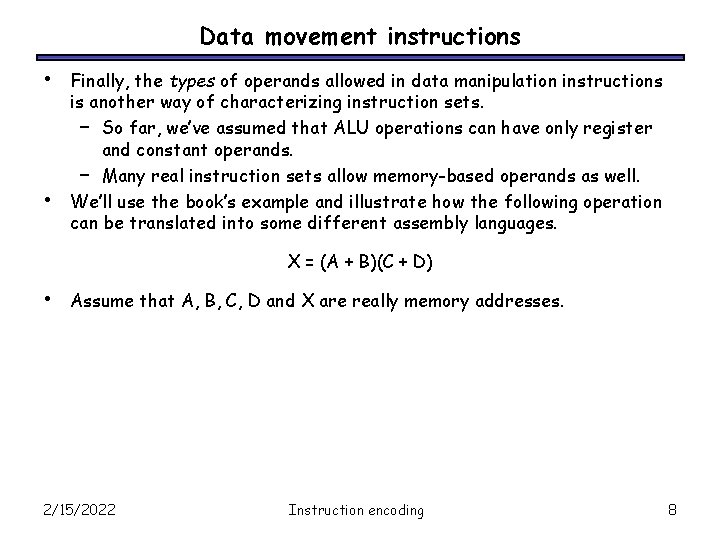

Data movement instructions • • Finally, the types of operands allowed in data manipulation instructions is another way of characterizing instruction sets. – So far, we’ve assumed that ALU operations can have only register and constant operands. – Many real instruction sets allow memory-based operands as well. We’ll use the book’s example and illustrate how the following operation can be translated into some different assembly languages. X = (A + B)(C + D) • Assume that A, B, C, D and X are really memory addresses. 2/15/2022 Instruction encoding 8

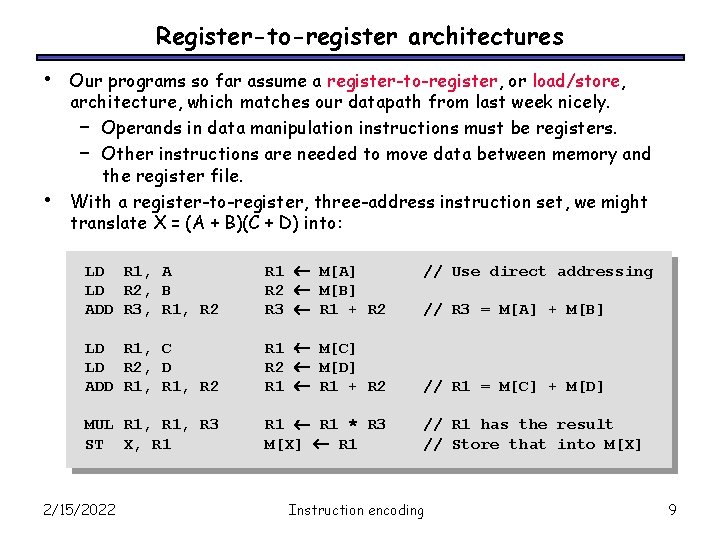

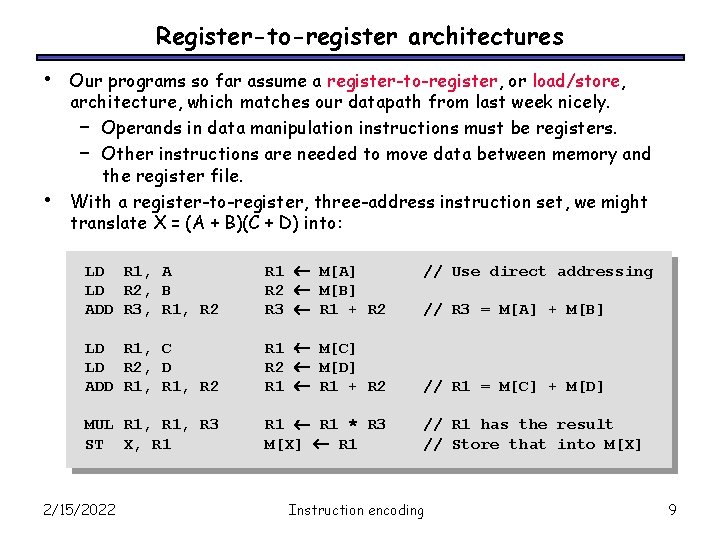

Register-to-register architectures • • Our programs so far assume a register-to-register, or load/store, architecture, which matches our datapath from last week nicely. – Operands in data manipulation instructions must be registers. – Other instructions are needed to move data between memory and the register file. With a register-to-register, three-address instruction set, we might translate X = (A + B)(C + D) into: LD R 1, A LD R 2, B ADD R 3, R 1, R 2 R 1 M[A] R 2 M[B] R 3 R 1 + R 2 LD R 1, C LD R 2, D ADD R 1, R 2 R 1 M[C] R 2 M[D] R 1 + R 2 // R 1 = M[C] + M[D] MUL R 1, R 3 ST X, R 1 * R 3 M[X] R 1 // R 1 has the result // Store that into M[X] 2/15/2022 // Use direct addressing // R 3 = M[A] + M[B] Instruction encoding 9

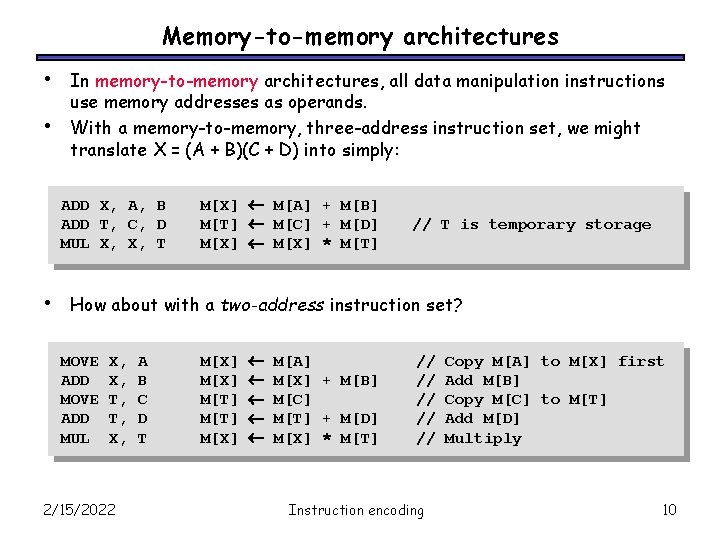

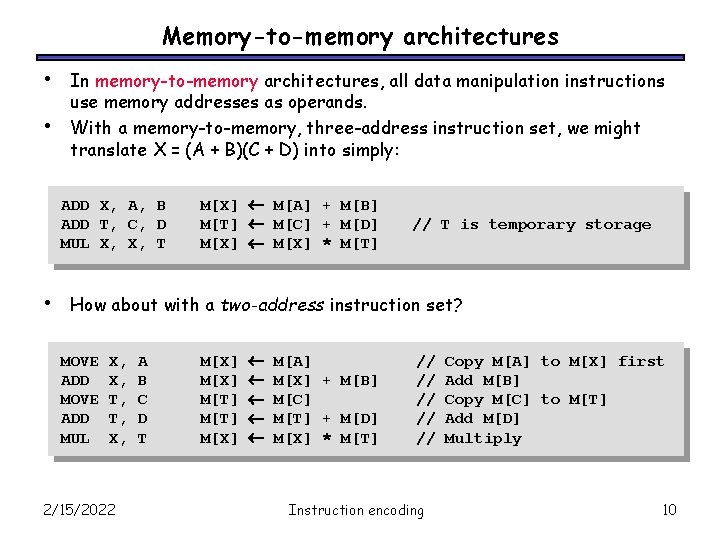

Memory-to-memory architectures • • In memory-to-memory architectures, all data manipulation instructions use memory addresses as operands. With a memory-to-memory, three-address instruction set, we might translate X = (A + B)(C + D) into simply: ADD X, A, B ADD T, C, D MUL X, X, T • M[X] M[A] + M[B] M[T] M[C] + M[D] M[X] * M[T] // T is temporary storage How about with a two-address instruction set? MOVE ADD MUL X, X, T, T, X, 2/15/2022 A B C D T M[X] M[T] M[X] M[A] M[X] + M[B] M[C] M[T] + M[D] M[X] * M[T] // // // Instruction encoding Copy M[A] to M[X] first Add M[B] Copy M[C] to M[T] Add M[D] Multiply 10

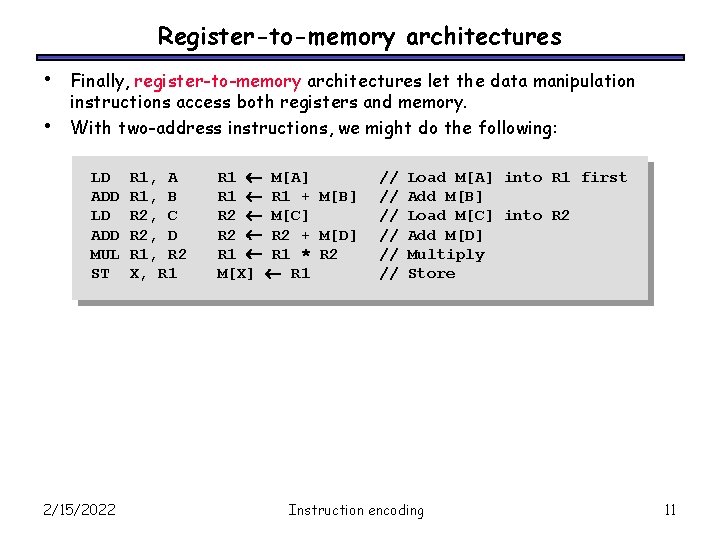

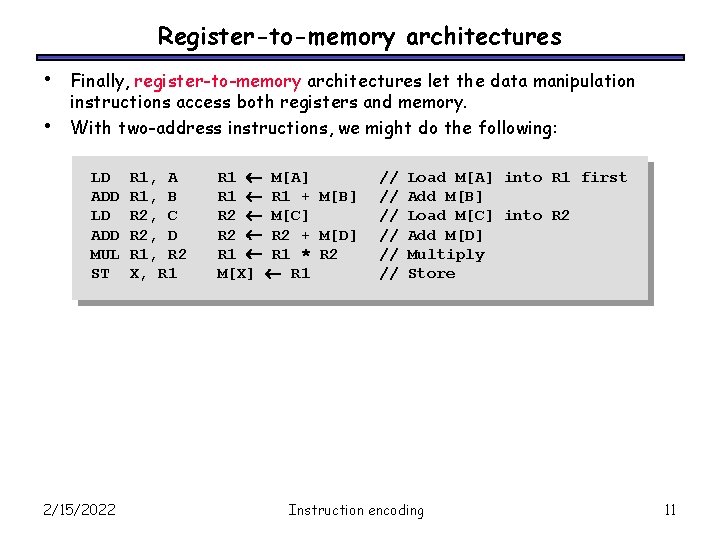

Register-to-memory architectures • • Finally, register-to-memory architectures let the data manipulation instructions access both registers and memory. With two-address instructions, we might do the following: LD ADD MUL ST 2/15/2022 R 1, A R 1, B R 2, C R 2, D R 1, R 2 X, R 1 M[A] R 1 + M[B] R 2 M[C] R 2 + M[D] R 1 * R 2 M[X] R 1 // // // Load M[A] into R 1 first Add M[B] Load M[C] into R 2 Add M[D] Multiply Store Instruction encoding 11

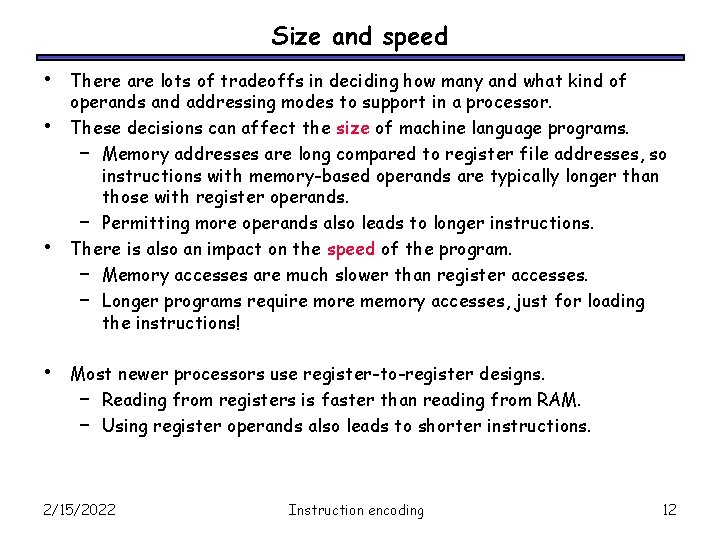

Size and speed • • There are lots of tradeoffs in deciding how many and what kind of operands and addressing modes to support in a processor. These decisions can affect the size of machine language programs. – Memory addresses are long compared to register file addresses, so instructions with memory-based operands are typically longer than those with register operands. – Permitting more operands also leads to longer instructions. There is also an impact on the speed of the program. – Memory accesses are much slower than register accesses. – Longer programs require more memory accesses, just for loading the instructions! Most newer processors use register-to-register designs. – Reading from registers is faster than reading from RAM. – Using register operands also leads to shorter instructions. 2/15/2022 Instruction encoding 12

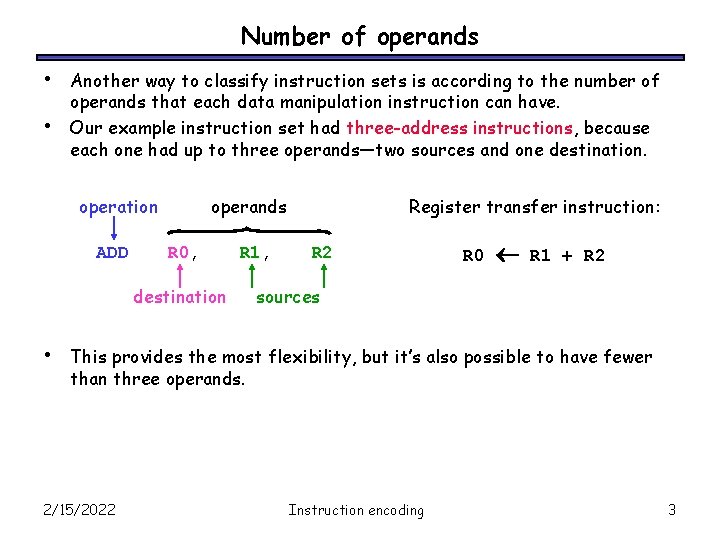

Summary • • Instruction sets can be classified along several lines. – Addressing modes let instructions access memory in various ways. – Data manipulation instructions can have from 0 to 3 operands. – Those operands may be registers, memory addresses, or both. Instruction set design is intimately tied to processor datapath design. 2/15/2022 Instruction encoding 13