Addition and Subtraction with Signed Magnitude Data Mano

Addition and Subtraction with Signed. Magnitude Data (Mano, Section 10 -2) Basics Seminar, CSc 8215 High Performance Computing (2005 Fall) Mary R. Hudachek-Buswell

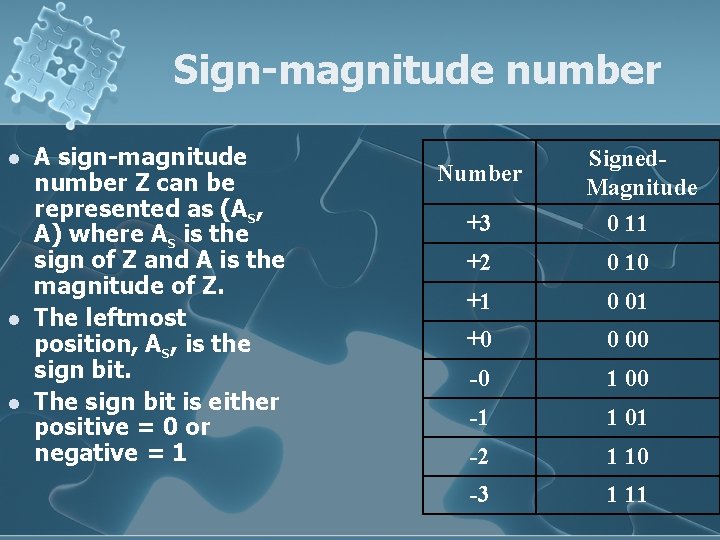

Sign-magnitude number l l l A sign-magnitude number Z can be represented as (As, A) where As is the sign of Z and A is the magnitude of Z. The leftmost position, As, is the sign bit. The sign bit is either positive = 0 or negative = 1 Number Signed. Magnitude +3 0 11 +2 0 10 +1 0 01 +0 0 00 -0 1 00 -1 1 01 -2 1 10 -3 1 11

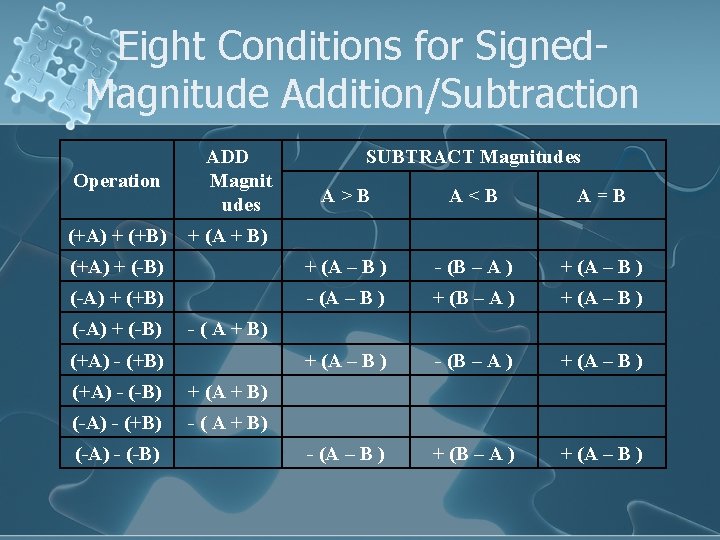

Eight Conditions for Signed. Magnitude Addition/Subtraction Operation ADD Magnit udes (+A) + (+B) + (A + B) SUBTRACT Magnitudes A>B A<B A=B (+A) + (-B) + (A – B ) - (B – A ) + (A – B ) (-A) + (+B) - (A – B ) + (B – A ) + (A – B ) - (A – B ) + (B – A ) + (A – B ) (-A) + (-B) - ( A + B) (+A) - (+B) (+A) - (-B) + (A + B) (-A) - (+B) - ( A + B) (-A) - (-B)

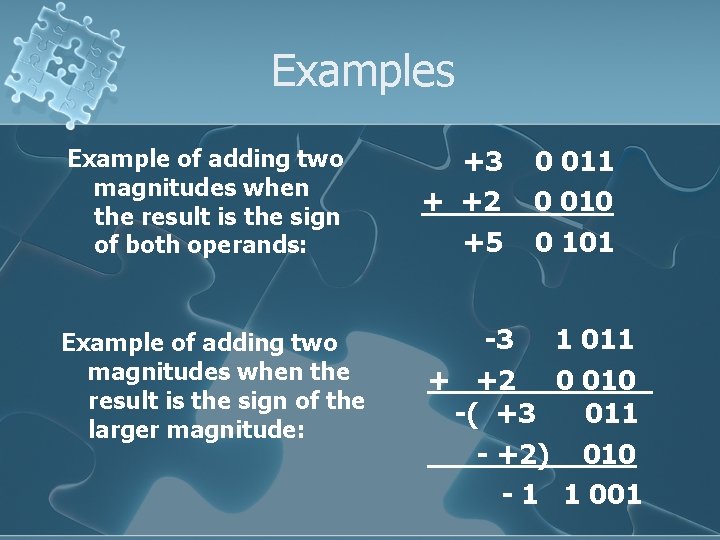

Examples Example of adding two magnitudes when the result is the sign of both operands: +3 + +2 +5 0 011 0 010 0 101 Example of adding two magnitudes when the result is the sign of the larger magnitude: -3 1 011 + +2 0 010 -( +3 011 - +2) 010 - 1 1 001

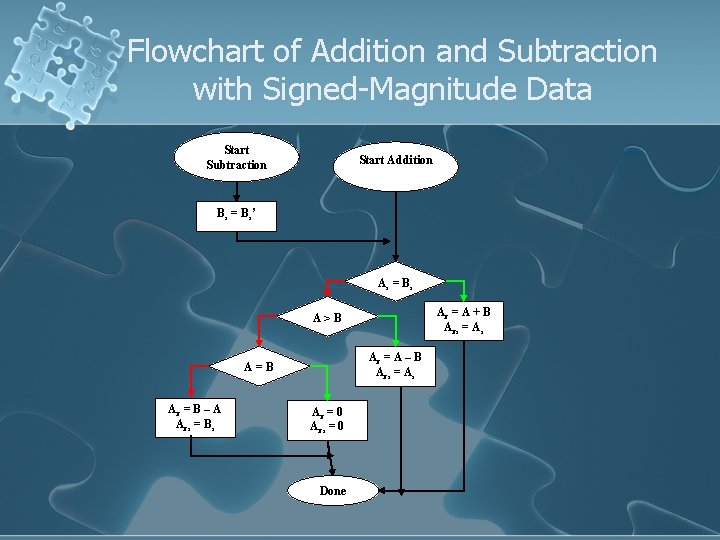

Flowchart of Addition and Subtraction with Signed-Magnitude Data Start Subtraction Start Addition Bs = Bs ’ As = Bs Ar = A + B Ars = As A>B Ar = A – B Ars = As A=B Ar = B – A Ars = Bs Ar = 0 Ars = 0 Done

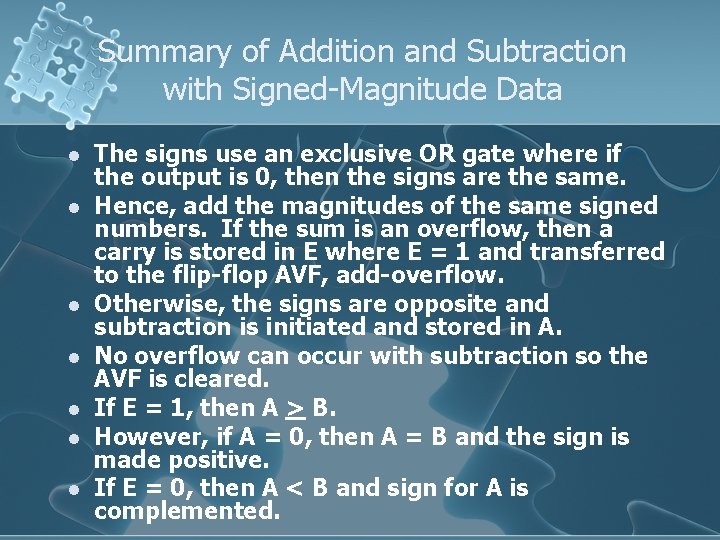

Summary of Addition and Subtraction with Signed-Magnitude Data l l l l The signs use an exclusive OR gate where if the output is 0, then the signs are the same. Hence, add the magnitudes of the same signed numbers. If the sum is an overflow, then a carry is stored in E where E = 1 and transferred to the flip-flop AVF, add-overflow. Otherwise, the signs are opposite and subtraction is initiated and stored in A. No overflow can occur with subtraction so the AVF is cleared. If E = 1, then A > B. However, if A = 0, then A = B and the sign is made positive. If E = 0, then A < B and sign for A is complemented.

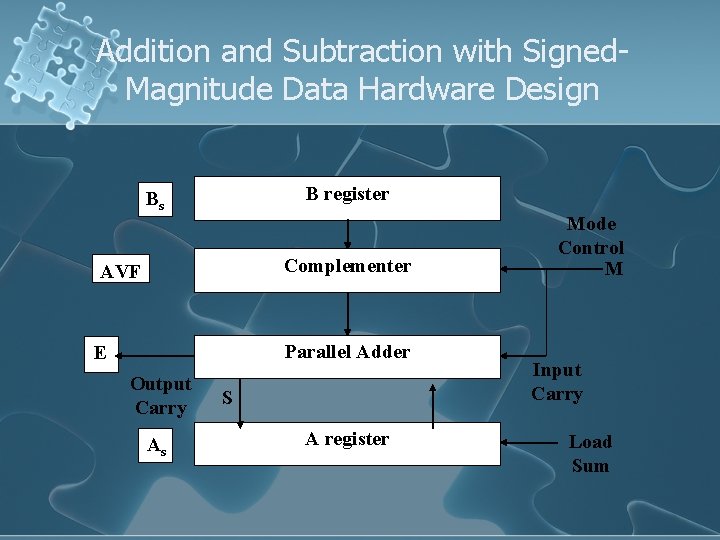

Addition and Subtraction with Signed. Magnitude Data Hardware Design B register Bs Complementer AVF Parallel Adder E Output Carry As S A register Mode Control M Input Carry Load Sum

- Slides: 7