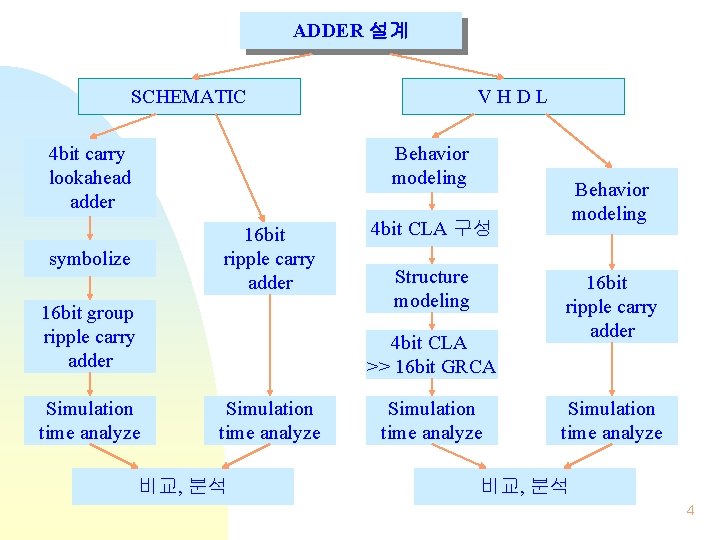

ADDER SCHEMATIC VHDL Behavior modeling 4 bit carry

ADDER 설계 SCHEMATIC VHDL Behavior modeling 4 bit carry lookahead adder 16 bit ripple carry adder symbolize 16 bit group ripple carry adder 4 bit CLA 구성 Structure modeling 4 bit CLA >> 16 bit GRCA Simulation time analyze 비교, 분석 Behavior modeling Simulation time analyze 16 bit ripple carry adder Simulation time analyze 비교, 분석 4

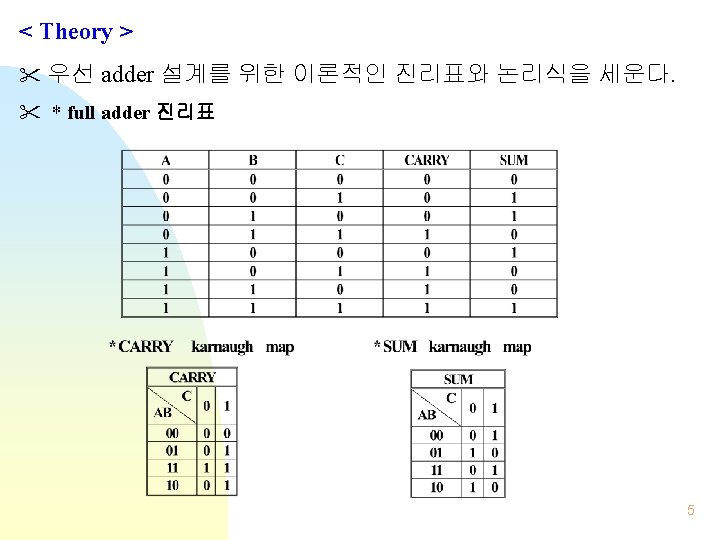

논리식은 Pi = Ai + Bi = Ai xor Bi(propagation 의미상) 6

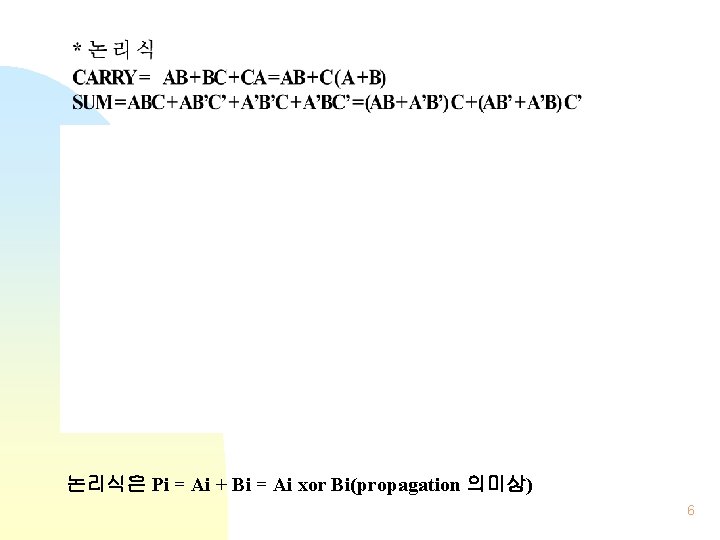

C 3 C 2 C 1 C 0 A= A 3 A 2 A 1 A 0 B= B 3 B 2 B 1 B 0 S 3 S 2 S 1 S 0 C 4 C 3 C 2 C 1 7

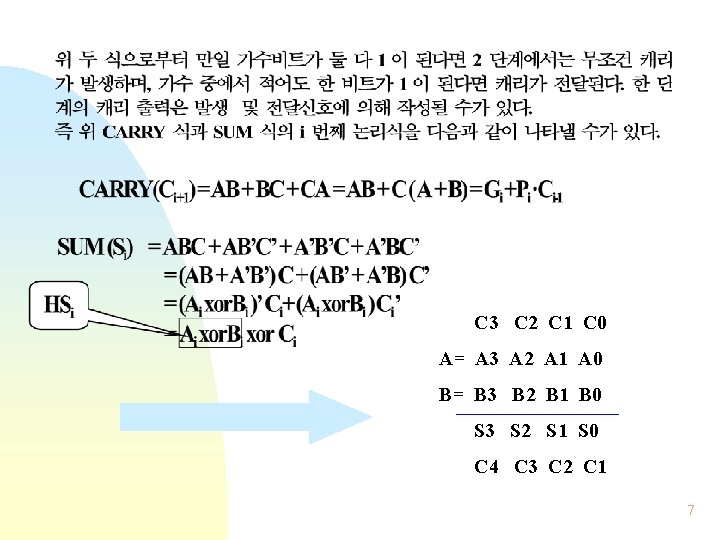

CARRY LOOKAHEAD ADDER 회로도 Ai XOR HSi XOR Bi Si Ci Ai-1 Bi-1 Co 캐리 예측 논리 8

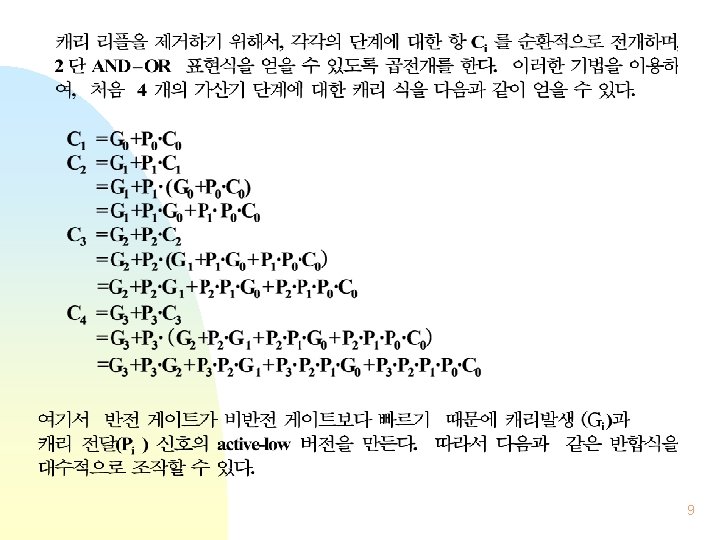

9

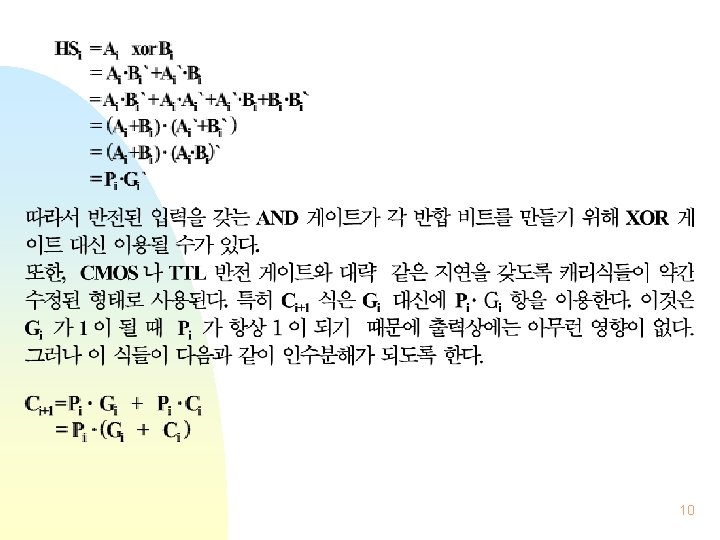

10

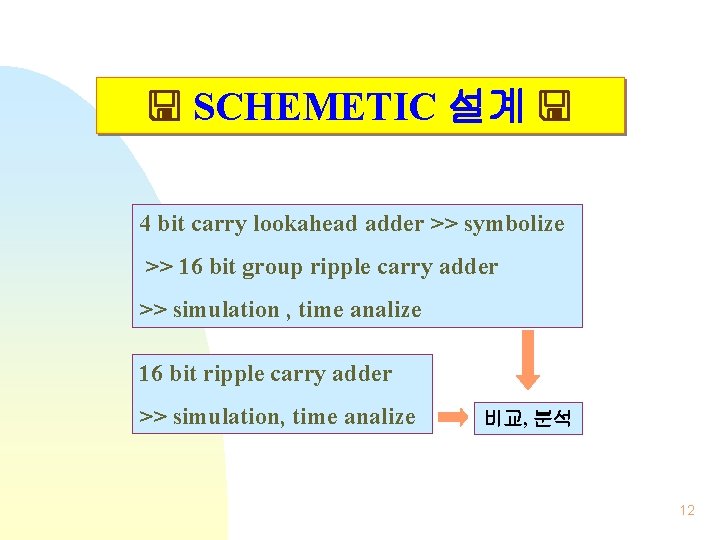

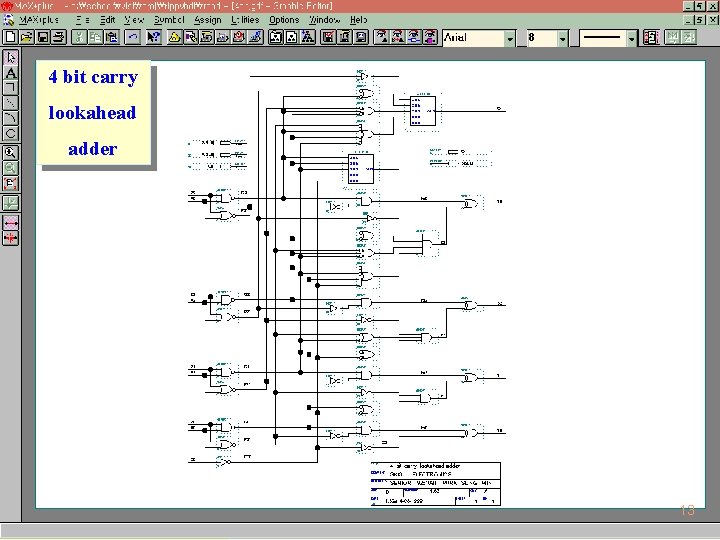

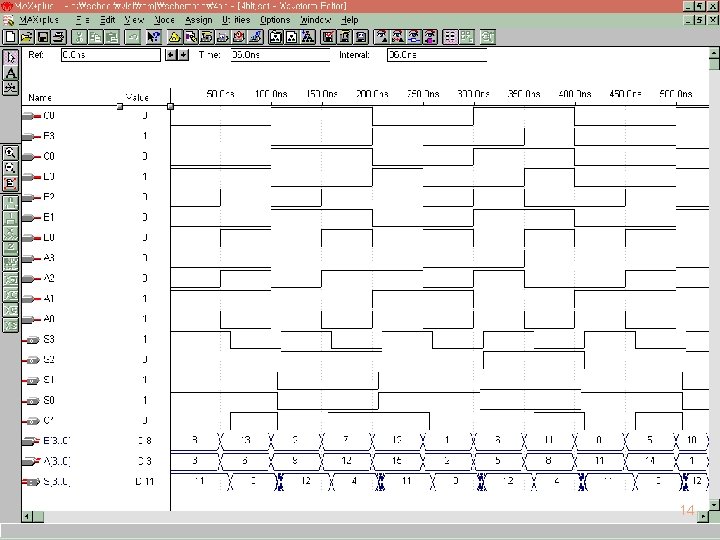

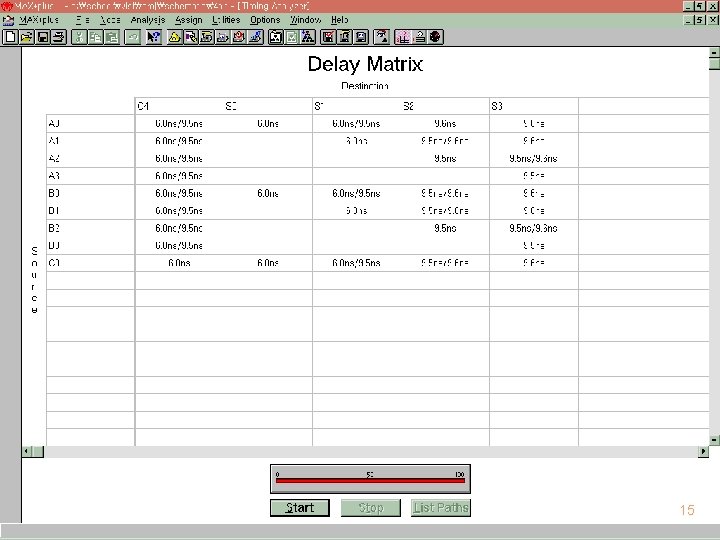

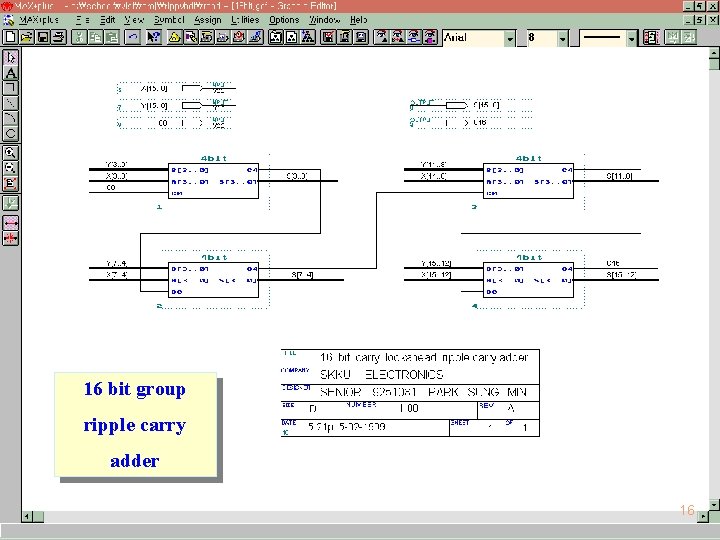

SCHEMETIC 설계 4 bit carry lookahead adder >> symbolize >> 16 bit group ripple carry adder >> simulation , time analize 16 bit ripple carry adder >> simulation, time analize 비교, 분석 12

4 bit carry lookahead adder 13

14

15

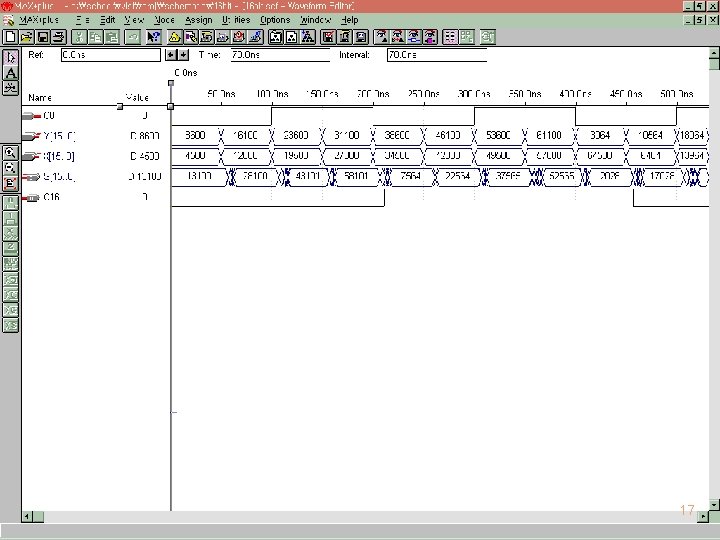

16 bit group ripple carry adder 16

17

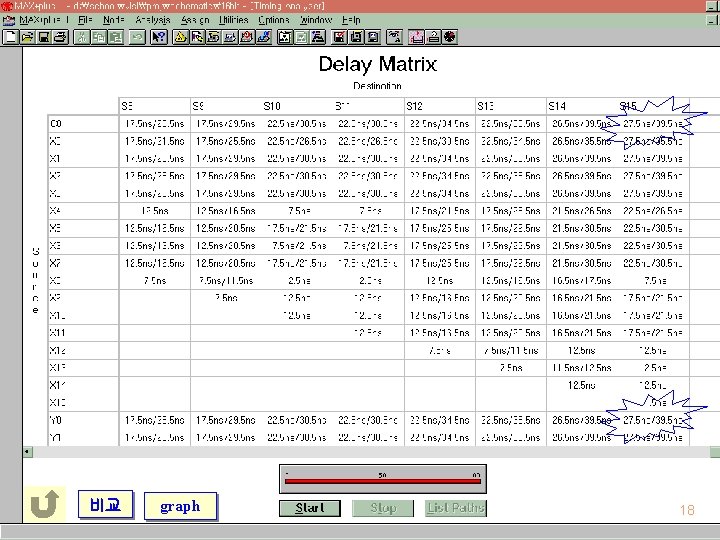

비교 graph 18

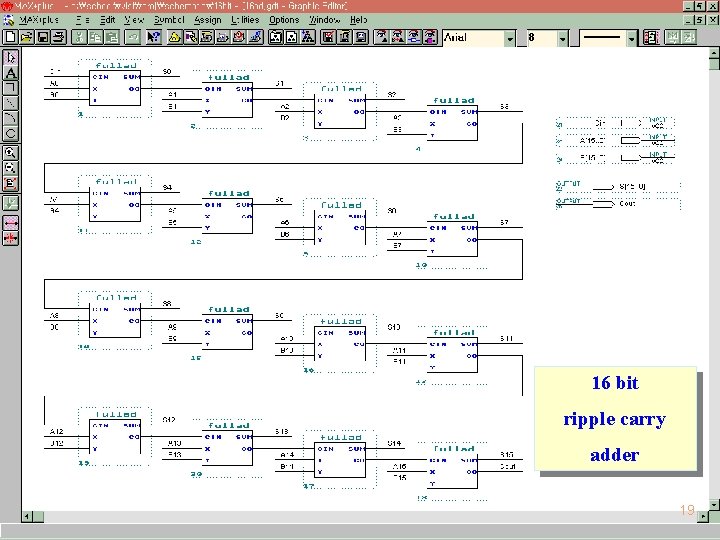

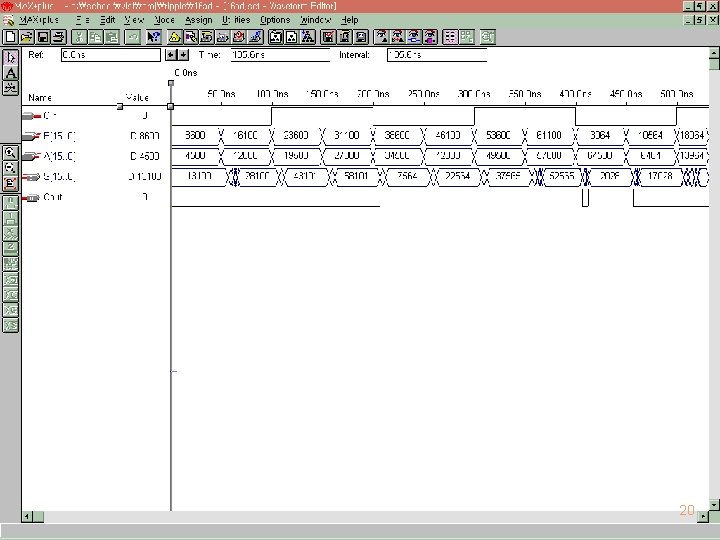

16 bit ripple carry adder 19

20

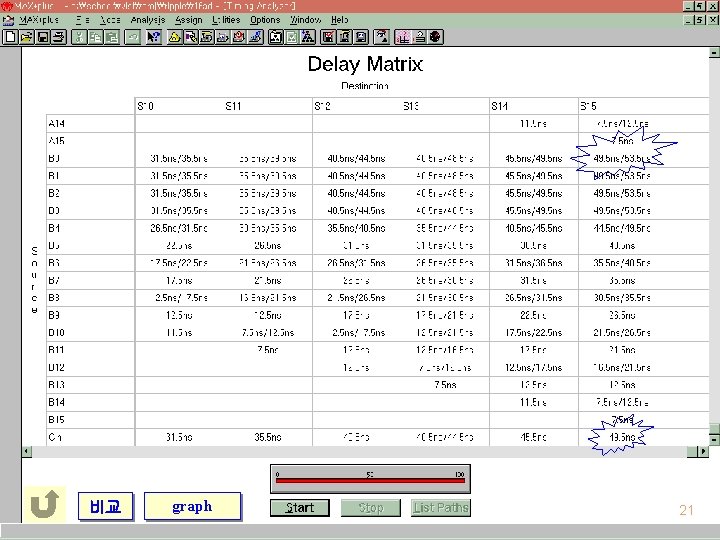

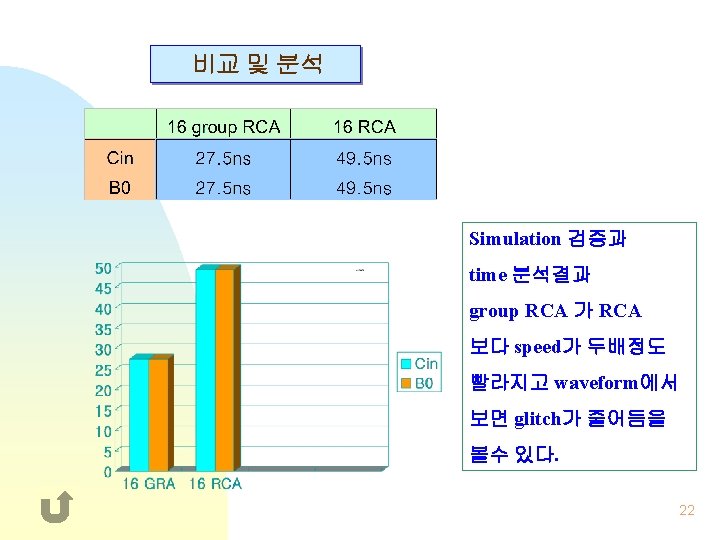

비교 graph 21

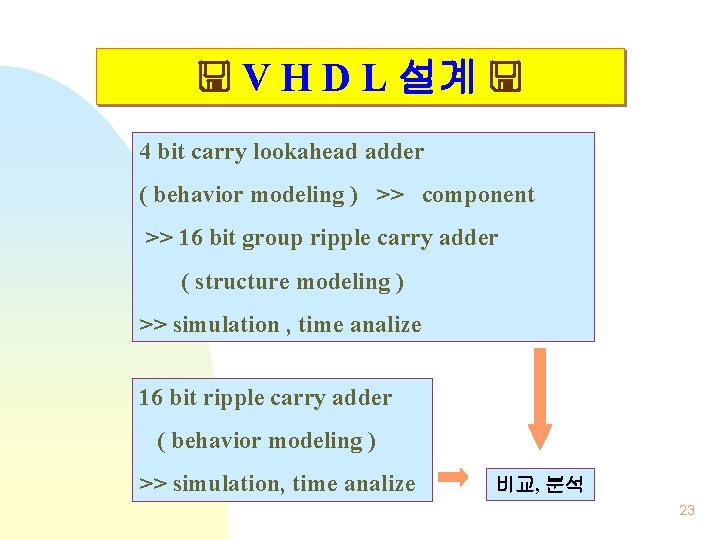

V H D L 설계 4 bit carry lookahead adder ( behavior modeling ) >> component >> 16 bit group ripple carry adder ( structure modeling ) >> simulation , time analize 16 bit ripple carry adder ( behavior modeling ) >> simulation, time analize 비교, 분석 23

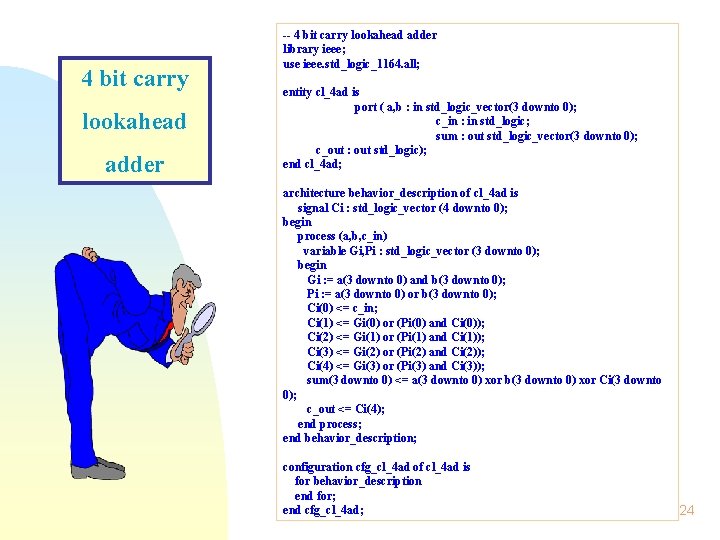

4 bit carry lookahead adder -- 4 bit carry lookahead adder library ieee; use ieee. std_logic_1164. all; entity cl_4 ad is port ( a, b : in std_logic_vector(3 downto 0); c_in : in std_logic; sum : out std_logic_vector(3 downto 0); c_out : out std_logic); end cl_4 ad; architecture behavior_description of cl_4 ad is signal Ci : std_logic_vector (4 downto 0); begin process (a, b, c_in) variable Gi, Pi : std_logic_vector (3 downto 0); begin Gi : = a(3 downto 0) and b(3 downto 0); Pi : = a(3 downto 0) or b(3 downto 0); Ci(0) <= c_in; Ci(1) <= Gi(0) or (Pi(0) and Ci(0)); Ci(2) <= Gi(1) or (Pi(1) and Ci(1)); Ci(3) <= Gi(2) or (Pi(2) and Ci(2)); Ci(4) <= Gi(3) or (Pi(3) and Ci(3)); sum(3 downto 0) <= a(3 downto 0) xor b(3 downto 0) xor Ci(3 downto 0); c_out <= Ci(4); end process; end behavior_description; configuration cfg_cl_4 ad of cl_4 ad is for behavior_description end for; end cfg_cl_4 ad; 24

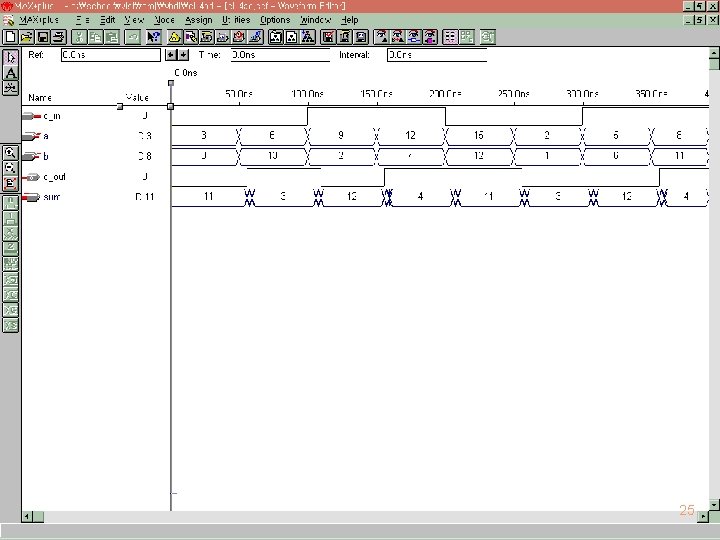

25

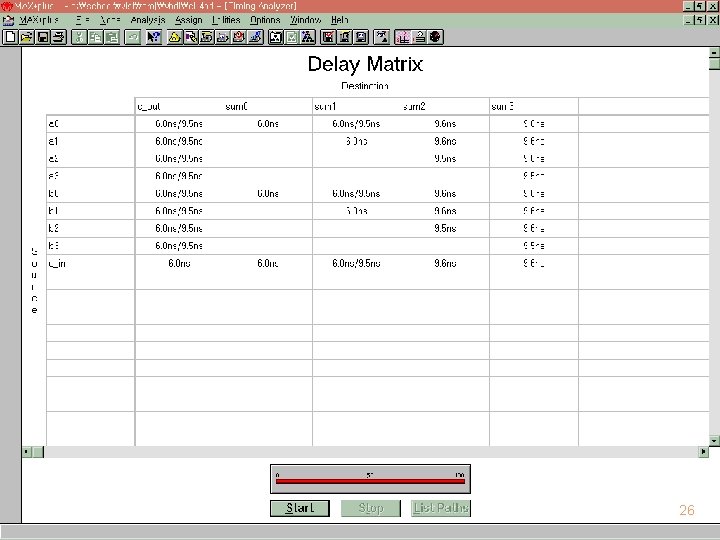

26

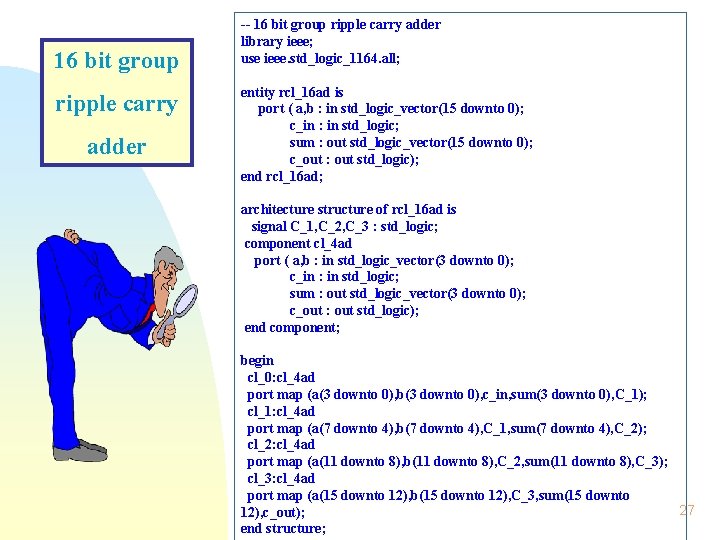

16 bit group ripple carry adder -- 16 bit group ripple carry adder library ieee; use ieee. std_logic_1164. all; entity rcl_16 ad is port ( a, b : in std_logic_vector(15 downto 0); c_in : in std_logic; sum : out std_logic_vector(15 downto 0); c_out : out std_logic); end rcl_16 ad; architecture structure of rcl_16 ad is signal C_1, C_2, C_3 : std_logic; component cl_4 ad port ( a, b : in std_logic_vector(3 downto 0); c_in : in std_logic; sum : out std_logic_vector(3 downto 0); c_out : out std_logic); end component; begin cl_0: cl_4 ad port map (a(3 downto 0), b(3 downto 0), c_in, sum(3 downto 0), C_1); cl_1: cl_4 ad port map (a(7 downto 4), b(7 downto 4), C_1, sum(7 downto 4), C_2); cl_2: cl_4 ad port map (a(11 downto 8), b(11 downto 8), C_2, sum(11 downto 8), C_3); cl_3: cl_4 ad port map (a(15 downto 12), b(15 downto 12), C_3, sum(15 downto 27 12), c_out); end structure;

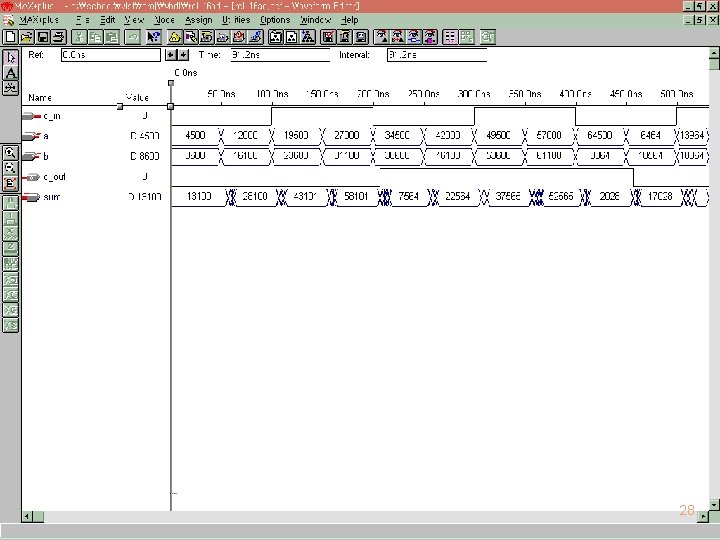

28

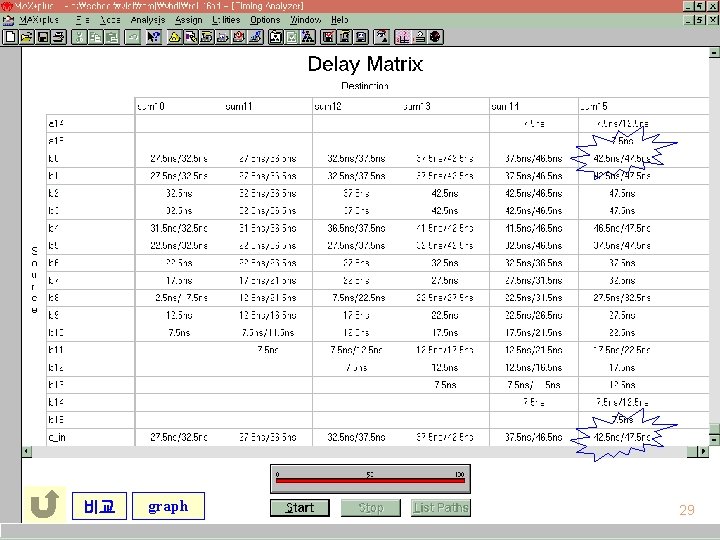

비교 graph 29

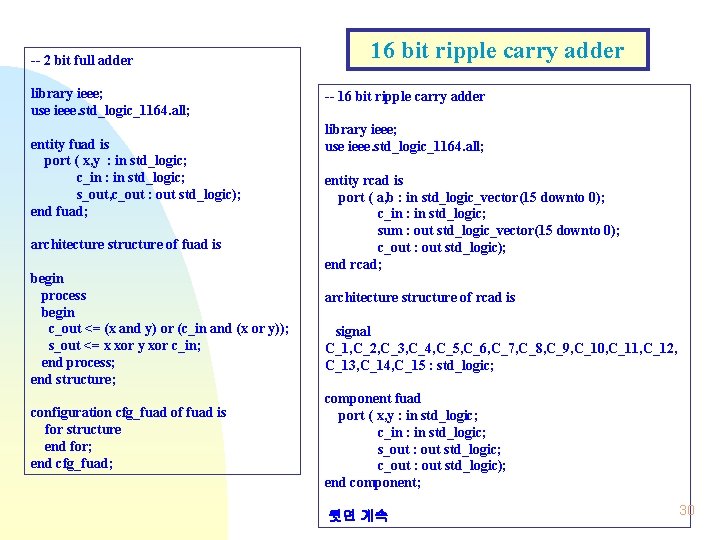

-- 2 bit full adder library ieee; use ieee. std_logic_1164. all; entity fuad is port ( x, y : in std_logic; c_in : in std_logic; s_out, c_out : out std_logic); end fuad; architecture structure of fuad is begin process begin c_out <= (x and y) or (c_in and (x or y)); s_out <= x xor y xor c_in; end process; end structure; configuration cfg_fuad of fuad is for structure end for; end cfg_fuad; 16 bit ripple carry adder -- 16 bit ripple carry adder library ieee; use ieee. std_logic_1164. all; entity rcad is port ( a, b : in std_logic_vector(15 downto 0); c_in : in std_logic; sum : out std_logic_vector(15 downto 0); c_out : out std_logic); end rcad; architecture structure of rcad is signal C_1, C_2, C_3, C_4, C_5, C_6, C_7, C_8, C_9, C_10, C_11, C_12, C_13, C_14, C_15 : std_logic; component fuad port ( x, y : in std_logic; c_in : in std_logic; s_out : out std_logic; c_out : out std_logic); end component; 뒷면 계속 30

begin cl_0: fuad port map (a(0), b(0), c_in, sum(0), C_1); cl_1: fuad port map (a(1), b(1), C_1, sum(1), C_2); cl_2: fuad port map (a(2), b(2), C_2, sum(2), C_3); cl_3: fuad port map (a(3), b(3), C_3, sum(3), C_4); cl_4: fuad port map (a(4), b(4), C_4, sum(4), C_5); cl_5: fuad port map (a(5), b(5), C_5, sum(5), C_6); cl_6: fuad port map (a(6), b(6), C_6, sum(6), C_7); cl_7: fuad port map (a(7), b(7), C_7, sum(7), C_8); cl_8: fuad port map (a(8), b(8), C_8, sum(8), C_9); cl_9: fuad port map (a(9), b(9), C_9, sum(9), C_10); cl_10: fuad port map (a(10), b(10), C_10, sum(10), C_11); cl_11: fuad port map (a(11), b(11), C_11, sum(11), C_12); cl_12: fuad port map (a(12), b(12), C_12, sum(12), C_13); cl_13: fuad port map (a(13), b(13), C_13, sum(13), C_14); cl_14: fuad port map (a(14), b(14), C_14, sum(14), C_15); cl_15: fuad port map (a(15), b(15), C_15, sum(15), c_out); end structure; 31

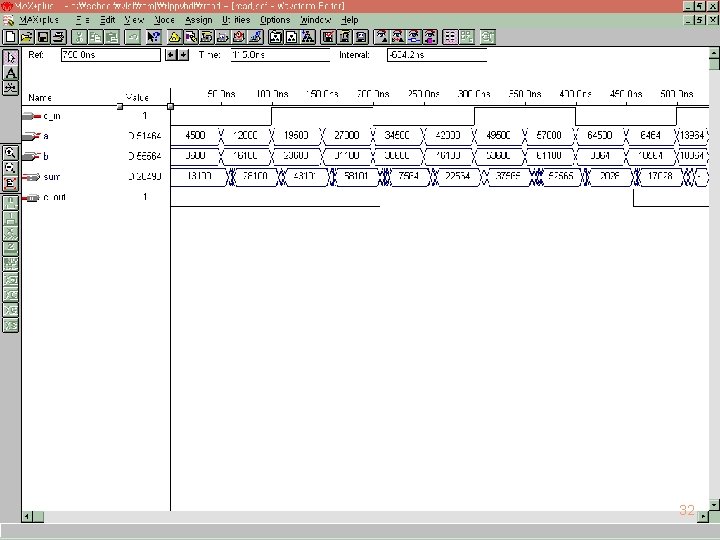

32

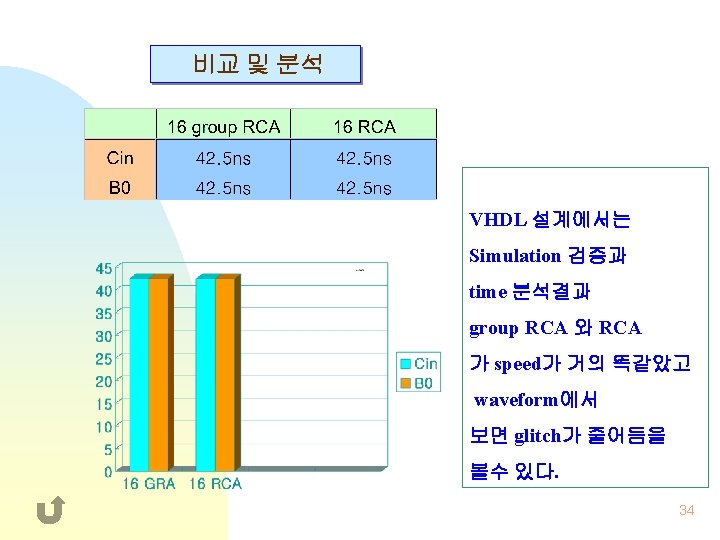

비교 graph 33

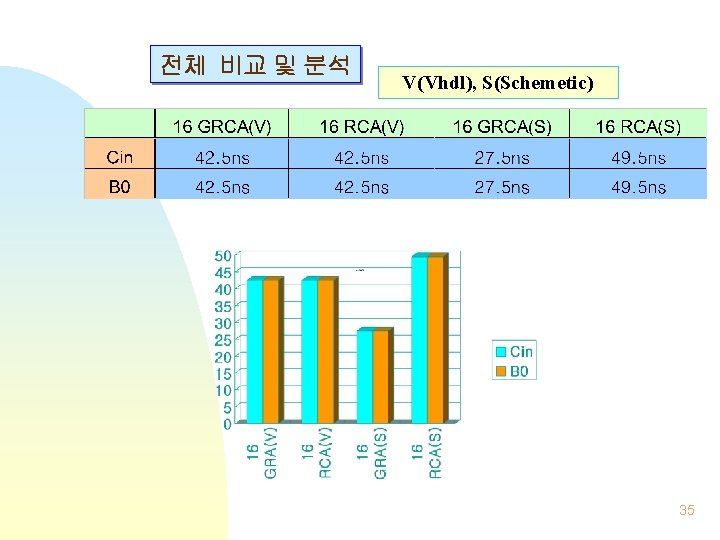

전체 비교 및 분석 V(Vhdl), S(Schemetic) 35

- Slides: 35